Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                          |

|----------------------------|--------------------------------------------------------------------------|

| Product Status             | Active                                                                   |

| Core Processor             | PIC                                                                      |

| Core Size                  | 8-Bit                                                                    |

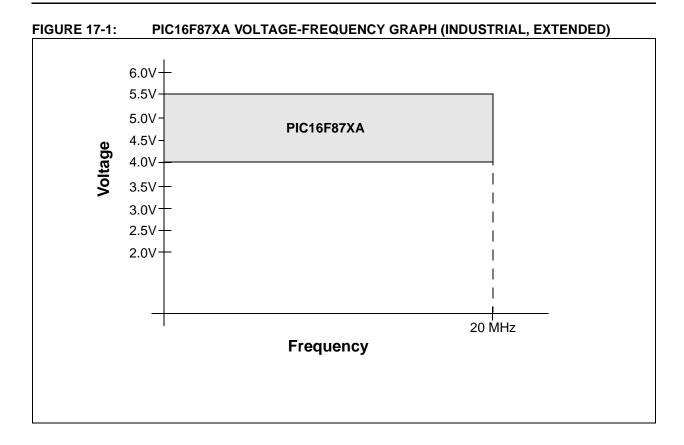

| Speed                      | 20MHz                                                                    |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                        |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                    |

| Number of I/O              | 33                                                                       |

| Program Memory Size        | 7KB (4K x 14)                                                            |

| Program Memory Type        | FLASH                                                                    |

| EEPROM Size                | 128 x 8                                                                  |

| RAM Size                   | 192 x 8                                                                  |

| Voltage - Supply (Vcc/Vdd) | 4V ~ 5.5V                                                                |

| Data Converters            | A/D 8x10b                                                                |

| Oscillator Type            | External                                                                 |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                        |

| Mounting Type              | Surface Mount                                                            |

| Package / Case             | 44-LCC (J-Lead)                                                          |

| Supplier Device Package    | 44-PLCC (16.59x16.59)                                                    |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16f874a-i-l |

|                            |                                                                          |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### 2.2 Data Memory Organization

The data memory is partitioned into multiple banks which contain the General Purpose Registers and the Special Function Registers. Bits RP1 (Status<6>) and RP0 (Status<5>) are the bank select bits.

| RP1:RP0 | Bank |

|---------|------|

| 00      | 0    |

| 01      | 1    |

| 10      | 2    |

| 11      | 3    |

Each bank extends up to 7Fh (128 bytes). The lower locations of each bank are reserved for the Special Function Registers. Above the Special Function Registers are General Purpose Registers, implemented as static RAM. All implemented banks contain Special Function Registers. Some frequently used Special Function Registers from one bank may be mirrored in another bank for code reduction and quicker access.

| Note: | The EEPROM data memory description can |

|-------|----------------------------------------|

|       | be found in Section 3.0 "Data EEPROM   |

|       | and Flash Program Memory" of this data |

|       | sheet.                                 |

#### 2.2.1 GENERAL PURPOSE REGISTER FILE

The register file can be accessed either directly, or indirectly, through the File Select Register (FSR).

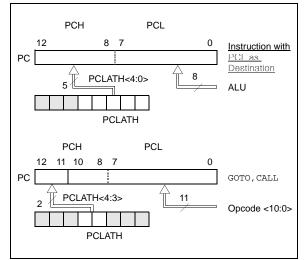

#### 2.3 PCL and PCLATH

The Program Counter (PC) is 13 bits wide. The low byte comes from the PCL register which is a readable and writable register. The upper bits (PC<12:8>) are not readable, but are indirectly writable through the PCLATH register. On any Reset, the upper bits of the PC will be cleared. Figure 2-5 shows the two situations for the loading of the PC. The upper example in the figure shows how the PC is loaded on a write to PCL (PCLATH<4:0>  $\rightarrow$  PCH). The lower example in the figure shows how the PC is loaded during a CALL or GOTO instruction (PCLATH<4:3>  $\rightarrow$  PCH).

#### FIGURE 2-5: LOADING OF PC IN DIFFERENT SITUATIONS

#### 2.3.1 COMPUTED GOTO

A computed GOTO is accomplished by adding an offset to the program counter (ADDWF PCL). When doing a table read using a computed GOTO method, care should be exercised if the table location crosses a PCL memory boundary (each 256-byte block). Refer to the application note, *AN556, "Implementing a Table Read"* (DS00556).

#### 2.3.2 STACK

The PIC16F87XA family has an 8-level deep x 13-bit wide hardware stack. The stack space is not part of either program or data space and the stack pointer is not readable or writable. The PC is PUSHed onto the stack when a CALL instruction is executed, or an interrupt causes a branch. The stack is POP'ed in the event of a RETURN, RETLW or a RETFIE instruction execution. PCLATH is not affected by a PUSH or POP operation.

The stack operates as a circular buffer. This means that after the stack has been PUSHed eight times, the ninth push overwrites the value that was stored from the first push. The tenth push overwrites the second push (and so on).

- **Note 1:** There are no status bits to indicate stack overflow or stack underflow conditions.

- 2: There are no instructions/mnemonics called PUSH or POP. These are actions that occur from the execution of the CALL, RETURN, RETLW and RETFIE instructions or the vectoring to an interrupt address.

### 2.4 Program Memory Paging

All PIC16F87XA devices are capable of addressing a continuous 8K word block of program memory. The CALL and GOTO instructions provide only 11 bits of address to allow branching within any 2K program memory page. When doing a CALL or GOTO instruction, the upper 2 bits of the address are provided by PCLATH<4:3>. When doing a CALL or GOTO instruction, the user must ensure that the page select bits are programmed so that the desired program memory page is addressed. If a return from a CALL instruction (or interrupt) is executed, the entire 13-bit PC is popped off the stack. Therefore, manipulation of the PCLATH<4:3> bits is not required for the RETURN instructions (which POPs the address from the stack).

| Note: | The contents of the PCLATH register are    |

|-------|--------------------------------------------|

|       | unchanged after a RETURN or RETFIE         |

|       | instruction is executed. The user must     |

|       | rewrite the contents of the PCLATH regis-  |

|       | ter for any subsequent subroutine calls or |

|       | GOTO instructions.                         |

Example 2-1 shows the calling of a subroutine in page 1 of the program memory. This example assumes that PCLATH is saved and restored by the Interrupt Service Routine (if interrupts are used).

#### EXAMPLE 2-1: CALL OF A SUBROUTINE IN PAGE 1 FROM PAGE 0

|         | ORG 0x500    |                     |

|---------|--------------|---------------------|

|         | BCF PCLATH,4 |                     |

|         | BSF PCLATH,3 | ;Select page 1      |

|         |              | ; (800h-FFFh)       |

|         | CALL SUB1_P1 | ;Call subroutine in |

|         | :            | ;page 1 (800h-FFFh) |

|         | :            |                     |

|         | ORG 0x900    | ;page 1 (800h-FFFh) |

| SUB1_P1 |              |                     |

|         | :            | ;called subroutine  |

|         |              | ;page 1 (800h-FFFh) |

|         | :            |                     |

|         | RETURN       | ;return to          |

|         |              | ;Call subroutine    |

|         |              | ;in page 0          |

|         |              | ;(000h-7FFh)        |

|         |              |                     |

NOTES:

| Address | Name   | Bit 7 | Bit 6 | Bit 5 | Bit 4   | Bit 3 | Bit 2                     | Bit 1 | Bit 0 | Value on:<br>POR, BOR | Value on<br>all other<br>Resets |

|---------|--------|-------|-------|-------|---------|-------|---------------------------|-------|-------|-----------------------|---------------------------------|

| 09h     | PORTE  | —     | —     | _     | —       |       | RE2                       | RE1   | RE0   | xxx                   | uuu                             |

| 89h     | TRISE  | IBF   | OBF   | IBOV  | PSPMODE | —     | PORTE Data Direction bits |       |       | 0000 -111             | 0000 -111                       |

| 9Fh     | ADCON1 | ADFM  | ADCS2 | _     | —       | PCFG3 | PCFG2                     | PCFG1 | PCFG0 | 00 0000               | 00 0000                         |

#### **TABLE 4-10:** SUMMARY OF REGISTERS ASSOCIATED WITH PORTE

Legend: x = unknown, u = unchanged, - = unimplemented, read as '0'. Shaded cells are not used by PORTE.

#### **REGISTER 4-1: TRISE REGISTER (ADDRESS 89h)**

| R-0   | R-0 | R/W-0 | R/W-0   | U-0 | R/W-1 | R/W-1 | R/W-1 |

|-------|-----|-------|---------|-----|-------|-------|-------|

| IBF   | OBF | IBOV  | PSPMODE | —   | Bit 2 | Bit 1 | Bit 0 |

| bit 7 |     |       |         |     |       |       | bit 0 |

#### Parallel Slave Port Status/Control Bits:

| bit 7 | IBF: Input Buffer Full Stat                           | tus bit                              |                      |                        |

|-------|-------------------------------------------------------|--------------------------------------|----------------------|------------------------|

|       | 1 = A word has been rece                              | eived and is waiting to              | be read by the CPU   |                        |

|       | 0 = No word has been re-                              | ceived                               |                      |                        |

| bit 6 | <b>OBF</b> : Output Buffer Full                       | Status bit                           |                      |                        |

|       | 1 = The output buffer still                           | holds a previously wri               | tten word            |                        |

|       | 0 = The output buffer has                             | been read                            |                      |                        |

| bit 5 | IBOV: Input Buffer Overf                              | low Detect bit (in Micro             | processor mode)      |                        |

|       | <ol> <li>A write occurred wh<br/>software)</li> </ol> | en a previously input                | word has not been re | ad (must be cleared in |

|       | 0 = No overflow occurred                              | b                                    |                      |                        |

| bit 4 | PSPMODE: Parallel Slav                                | e Port Mode Select bit               |                      |                        |

|       | 1 = PORTD functions in F                              | Parallel Slave Port mo               | de                   |                        |

|       | 0 = PORTD functions in g                              | general purpose I/O m                | ode                  |                        |

| bit 3 | Unimplemented: Read a                                 | <b>as</b> '0'                        |                      |                        |

|       | PORTE Data Direction E                                | <u>Bits:</u>                         |                      |                        |

| bit 2 | Bit 2: Direction Control bi                           | it for pin RE2/ $\overline{CS}$ /AN7 |                      |                        |

|       | 1 = Input                                             |                                      |                      |                        |

|       | 0 = Output                                            |                                      |                      |                        |

| bit 1 | Bit 1: Direction Control bi                           | it for pin RE1/WR/AN6                |                      |                        |

|       | 1 = Input                                             |                                      |                      |                        |

|       | 0 = Output                                            |                                      |                      |                        |

| bit 0 | Bit 0: Direction Control bi                           | it for pin RE0/RD/AN5                |                      |                        |

|       | 1 = Input                                             |                                      |                      |                        |

|       | 0 = Output                                            |                                      |                      |                        |

|       |                                                       |                                      |                      |                        |

|       | Legend:                                               |                                      |                      |                        |

|       | R = Readable bit                                      | W = Writable bit                     | U = Unimplemented    | bit, read as '0'       |

|       | - n = Value at POR                                    | '1' = Bit is set                     | '0' = Bit is cleared | x = Bit is unknown     |

|       | L                                                     |                                      |                      |                        |

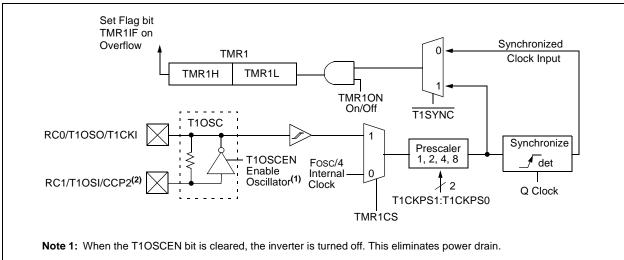

#### 6.1 Timer1 Operation in Timer Mode

Timer mode is selected by clearing the TMR1CS (T1CON<1>) bit. In this mode, the input clock to the timer is FOSC/4. The synchronize control bit, T1SYNC (T1CON<2>), has no effect since the internal clock is always in sync.

#### 6.2 Timer1 Counter Operation

Timer1 may operate in either a Synchronous, or an Asynchronous mode, depending on the setting of the TMR1CS bit.

When Timer1 is being incremented via an external source, increments occur on a rising edge. After Timer1 is enabled in Counter mode, the module must first have a falling edge before the counter begins to increment.

# FIGURE 6-1: TIMER1 INCREMENTING EDGE

#### 6.3 Timer1 Operation in Synchronized Counter Mode

Counter mode is selected by setting bit TMR1CS. In this mode, the timer increments on every rising edge of clock input on pin RC1/T1OSI/CCP2 when bit T1OSCEN is set, or on pin RC0/T1OSO/T1CKI when bit T1OSCEN is cleared.

If  $\overline{\text{T1SYNC}}$  is cleared, then the external clock input is synchronized with internal phase clocks. The synchronization is done after the prescaler stage. The prescaler stage is an asynchronous ripple counter.

In this configuration, during Sleep mode, Timer1 will not increment even if the external clock is present since the synchronization circuit is shut-off. The prescaler, however, will continue to increment.

#### FIGURE 6-2: TIMER1 BLOCK DIAGRAM

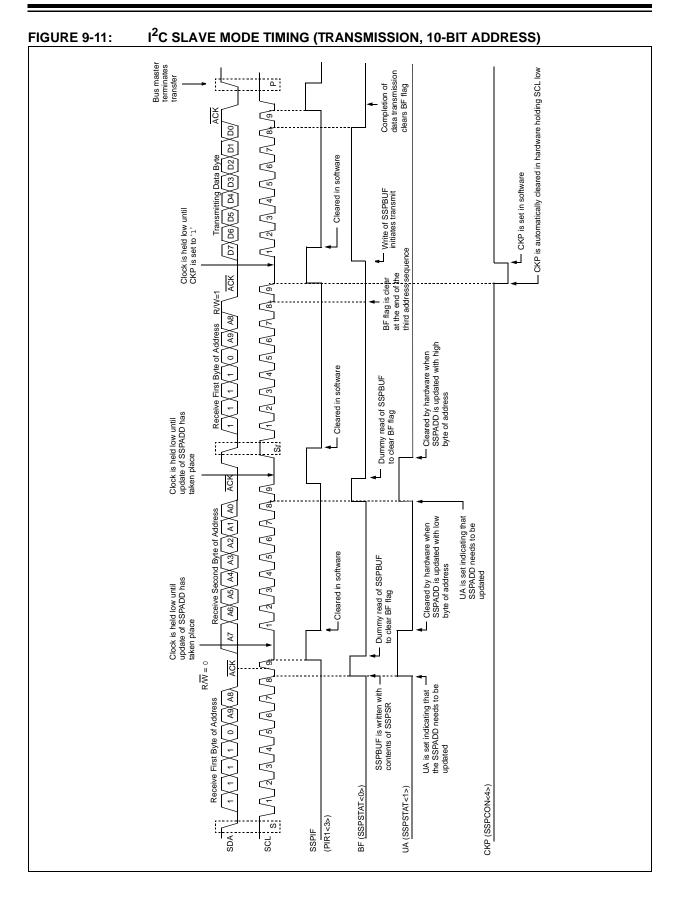

#### 9.4.3.2 Reception

When the  $R/\overline{W}$  bit of the address byte is clear and an address match occurs, the  $R/\overline{W}$  bit of the SSPSTAT register is cleared. The received address is loaded into the SSPBUF register and the SDA line is held low (ACK).

When the address byte overflow condition exists, then the No Acknowledge (ACK) pulse is given. An overflow condition is defined as either bit BF (SSPSTAT<0>) is set or bit SSPOV (SSPCON<6>) is set.

An MSSP interrupt is generated for each data transfer byte. Flag bit SSPIF (PIR1<3>) must be cleared in software. The SSPSTAT register is used to determine the status of the byte.

If SEN is enabled (SSPCON<0> = 1), RC3/SCK/SCL will be held low (clock stretch) following each data transfer. The clock must be released by setting bit CKP (SSPCON<4>). See **Section 9.4.4** "**Clock Stretching**" for more detail.

#### 9.4.3.3 Transmission

When the R/W bit of the incoming address byte is set and an address match occurs, the R/W bit of the SSPSTAT register is set. The received address is loaded into the SSPBUF register. The ACK pulse will be sent on the ninth bit and pin RC3/SCK/SCL is held low regardless of SEN (see **Section 9.4.4 "Clock Stretching"** for more detail). By stretching the clock, the master will be unable to assert another clock pulse until the slave is done preparing the transmit data. The transmit data must be loaded into the SSPBUF register, which also loads the SSPSR register. Then pin RC3/SCK/SCL should be enabled by setting bit CKP (SSPCON<4>). The eight data bits are shifted out on the falling edge of the SCL input. This ensures that the SDA signal is valid during the SCL high time (Figure 9-9).

The ACK pulse from the master-receiver is latched on the rising edge of the ninth SCL input pulse. If the SDA line is high (not ACK), then the data transfer is complete. In this case, when the ACK is latched by the slave, the slave logic is reset (resets SSPSTAT register) and the slave monitors for another occurrence of the Start bit. If the SDA line was low (ACK), the next transmit data must be loaded into the SSPBUF register. Again, pin RC3/SCK/SCL must be enabled by setting bit CKP.

An MSSP interrupt is generated for each data transfer byte. The SSPIF bit must be cleared in software and the SSPSTAT register is used to determine the status of the byte. The SSPIF bit is set on the falling edge of the ninth clock pulse.

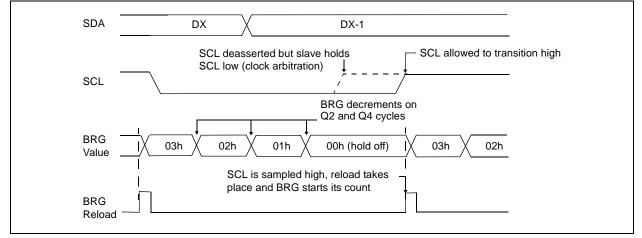

#### 9.4.7.1 Clock Arbitration

Clock arbitration occurs when the master, during any receive, transmit or Repeated Start/Stop condition, deasserts the SCL pin (SCL allowed to float high). When the SCL pin is allowed to float high, the Baud Rate Generator (BRG) is suspended from counting until the SCL pin is actually sampled high. When the

SCL pin is sampled high, the Baud Rate Generator is reloaded with the contents of SSPADD<6:0> and begins counting. This ensures that the SCL high time will always be at least one BRG rollover count, in the event that the clock is held low by an external device (Figure 9-17).

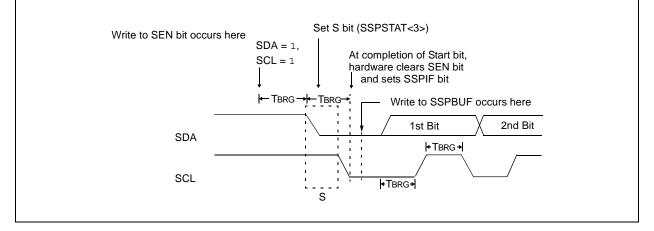

#### 9.4.8 I<sup>2</sup>C MASTER MODE START CONDITION TIMING

To initiate a Start condition, the user sets the Start condition enable bit, SEN (SSPCON2<0>). If the SDA and SCL pins are sampled high, the Baud Rate Generator is reloaded with the contents of SSPADD<6:0> and starts its count. If SCL and SDA are both sampled high when the Baud Rate Generator times out (TBRG), the SDA pin is driven low. The action of the SDA being driven low, while SCL is high, is the Start condition and causes the S bit (SSPSTAT<3>) to be set. Following this, the Baud Rate Generator is reloaded with the contents of SSPADD<6:0> and resumes its count. When the Baud Rate Generator times out (TBRG), the SEN bit (SSPCON2<0>) will be automatically cleared by hardware, the Baud Rate Generator is suspended, leaving the SDA line held low and the Start condition is complete.

**Note:** If at the beginning of the Start condition, the SDA and SCL pins are already sampled low, or if during the Start condition, the SCL line is sampled low before the SDA line is driven low, a bus collision occurs, the Bus Collision Interrupt Flag (BCLIF) is set, the Start condition is aborted and the I<sup>2</sup>C module is reset into its Idle state.

#### 9.4.8.1 WCOL Status Flag

If the user writes the SSPBUF when a Start sequence is in progress, the WCOL is set and the contents of the buffer are unchanged (the write doesn't occur).

Note: Because queueing of events is not allowed, writing to the lower 5 bits of SSPCON2 is disabled until the Start condition is complete.

#### FIGURE 9-19: FIRST START BIT TIMING

|       | SPEN                                                                                                                                               | DVO                        |                                       |               |              |               |               |              |  |  |  |

|-------|----------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------|---------------------------------------|---------------|--------------|---------------|---------------|--------------|--|--|--|

|       |                                                                                                                                                    | RX9                        | SREN                                  | CREN          | ADDEN        | FERR          | OERR          | RX9D         |  |  |  |

|       | bit 7                                                                                                                                              |                            |                                       |               |              |               |               | bit (        |  |  |  |

| bit 7 | SPEN: Ser                                                                                                                                          | ial Port Ena               | ble bit                               |               |              |               |               |              |  |  |  |

|       | -                                                                                                                                                  | ort enabled                |                                       | RC7/RX/D      | T and RC6/T  | X/CK pins a   | as serial por | t pins)      |  |  |  |

| bit 6 | <b>RX9</b> : 9-bit l                                                                                                                               | Receive Ena                | able bit                              |               |              |               |               |              |  |  |  |

|       |                                                                                                                                                    | 9-bit recep<br>8-bit recep |                                       |               |              |               |               |              |  |  |  |

| bit 5 | SREN: Sing                                                                                                                                         | gle Receive                | Enable bit                            |               |              |               |               |              |  |  |  |

|       | <u>Asynchron</u><br>Don't care.                                                                                                                    | ous mode:                  |                                       |               |              |               |               |              |  |  |  |

|       |                                                                                                                                                    | <u>us mode – I</u>         |                                       |               |              |               |               |              |  |  |  |

|       |                                                                                                                                                    | es single rec              |                                       |               |              |               |               |              |  |  |  |

|       |                                                                                                                                                    |                            | reception is                          | s complete.   |              |               |               |              |  |  |  |

|       | <u>Synchrono</u><br>Don't care.                                                                                                                    | <u>us mode – S</u>         | <u>Slave:</u>                         |               |              |               |               |              |  |  |  |

| bit 4 | CREN: Cor                                                                                                                                          | ntinuous Re                | ceive Enable                          | e bit         |              |               |               |              |  |  |  |

|       | Asynchronous mode:                                                                                                                                 |                            |                                       |               |              |               |               |              |  |  |  |

|       | <ul> <li>1 = Enables continuous receive</li> <li>0 = Disables continuous receive</li> </ul>                                                        |                            |                                       |               |              |               |               |              |  |  |  |

|       | Synchronous mode:                                                                                                                                  |                            |                                       |               |              |               |               |              |  |  |  |

|       | <ul> <li>1 = Enables continuous receive until enable bit CREN is cleared (CREN overrides SREN)</li> <li>0 = Disables continuous receive</li> </ul> |                            |                                       |               |              |               |               |              |  |  |  |

| bit 3 | ADDEN: A                                                                                                                                           | ddress Dete                | ect Enable b                          | it            |              |               |               |              |  |  |  |

|       | 1 = Enable                                                                                                                                         |                            | <u>-bit (RX9 = 1</u><br>letection, en |               | upt and load | of the receiv | ve buffer wh  | en RSR<8:    |  |  |  |

|       | is set<br>0 = Disable                                                                                                                              | es address                 | detection, al                         | l bytes are i | received and | ninth bit ca  | n be used a   | s parity bit |  |  |  |

| bit 2 | FERR: Fra                                                                                                                                          |                            |                                       |               |              |               |               |              |  |  |  |

|       |                                                                                                                                                    | g error (can               |                                       | by reading    | RCREG reg    | ister and red | ceive next v  | alid byte)   |  |  |  |

| bit 1 | OERR: Ov                                                                                                                                           | errun Error                | bit                                   |               |              |               |               |              |  |  |  |

|       | 1 = Overru<br>0 = No ove                                                                                                                           |                            | be cleared                            | by clearing   | bit CREN)    |               |               |              |  |  |  |

| bit 0 | <b>RX9D:</b> 9th                                                                                                                                   | bit of Rece                | ived Data (c                          | an be parity  | bit but must | be calculat   | ed by user f  | irmware)     |  |  |  |

| Legend:            |                  |                      |                    |

|--------------------|------------------|----------------------|--------------------|

| R = Readable bit   | W = Writable bit | U = Unimplemented    | bit, read as '0'   |

| - n = Value at POR | '1' = Bit is set | '0' = Bit is cleared | x = Bit is unknown |

#### 10.3.2 USART SYNCHRONOUS MASTER RECEPTION

Once Synchronous mode is selected, reception is enabled by setting either enable bit, SREN (RCSTA<5>), or enable bit, CREN (RCSTA<4>). Data is sampled on the RC7/RX/DT pin on the falling edge of the clock. If enable bit SREN is set, then only a single word is received. If enable bit CREN is set, the reception is continuous until CREN is cleared. If both bits are set, CREN takes precedence. After clocking the last bit, the received data in the Receive Shift Register (RSR) is transferred to the RCREG register (if it is empty). When the transfer is complete, interrupt flag bit, RCIF (PIR1<5>), is set. The actual interrupt can be enabled/ disabled by setting/clearing enable bit, RCIE (PIE1<5>). Flag bit RCIF is a read-only bit which is reset by the hardware. In this case, it is reset when the RCREG register has been read and is empty. The RCREG is a double-buffered register (i.e., it is a twodeep FIFO). It is possible for two bytes of data to be received and transferred to the RCREG FIFO and a third byte to begin shifting into the RSR register. On the clocking of the last bit of the third byte, if the RCREG register is still full, then Overrun Error bit, OERR (RCSTA<1>), is set. The word in the RSR will be lost. The RCREG register can be read twice to retrieve the two bytes in the FIFO. Bit OERR has to be cleared in software (by clearing bit CREN). If bit OERR is set, transfers from the RSR to the RCREG are inhibited so it is essential to clear bit OERR if it is set. The ninth receive bit is buffered the same way as the receive

data. Reading the RCREG register will load bit RX9D with a new value, therefore, it is essential for the user to read the RCSTA register before reading RCREG in order not to lose the old RX9D information.

When setting up a Synchronous Master Reception:

- 1. Initialize the SPBRG register for the appropriate baud rate (Section 10.1 "USART Baud Rate Generator (BRG)").

- 2. Enable the synchronous master serial port by setting bits SYNC, SPEN and CSRC.

- 3. Ensure bits CREN and SREN are clear.

- 4. If interrupts are desired, then set enable bit RCIE.

- 5. If 9-bit reception is desired, then set bit RX9.

- 6. If a single reception is required, set bit SREN. For continuous reception, set bit CREN.

- Interrupt flag bit RCIF will be set when reception is complete and an interrupt will be generated if enable bit RCIE was set.

- 8. Read the RCSTA register to get the ninth bit (if enabled) and determine if any error occurred during reception.

- 9. Read the 8-bit received data by reading the RCREG register.

- 10. If any error occurred, clear the error by clearing bit CREN.

- 11. If using interrupts, ensure that GIE and PEIE (bits 7 and 6) of the INTCON register are set.

| TABLE 10-9. REGISTERS ASSOCIATED WITH STRCHRONOUS MASTER RECEPTION |                                                           |                                                                                                     |                                                                                                          |                                                                                                                                                                                                  |                                                                                                                                                                                              |                                                                                                                                                                                                                                                             |                                                                                                                                                                                                                                                      |                                                                                                                                                                                                                                                                               |                                                                                                                                                                                                                                                                                                            |                                                                                                                                                                                                                                                                                                                                                                                                        |

|--------------------------------------------------------------------|-----------------------------------------------------------|-----------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Name                                                               | Bit 7                                                     | Bit 6                                                                                               | Bit 5                                                                                                    | Bit 4                                                                                                                                                                                            | Bit 3                                                                                                                                                                                        | Bit 2                                                                                                                                                                                                                                                       | Bit 1                                                                                                                                                                                                                                                | Bit 0                                                                                                                                                                                                                                                                         | Value on:<br>POR, BOR                                                                                                                                                                                                                                                                                      | Value on<br>all other<br>Resets                                                                                                                                                                                                                                                                                                                                                                        |

| INTCON                                                             | GIE                                                       | PEIE                                                                                                | TMR0IE                                                                                                   | INTE                                                                                                                                                                                             | RBIE                                                                                                                                                                                         | TMR0IF                                                                                                                                                                                                                                                      | INTF                                                                                                                                                                                                                                                 | R0IF                                                                                                                                                                                                                                                                          | 0000 000x                                                                                                                                                                                                                                                                                                  | 0000 000u                                                                                                                                                                                                                                                                                                                                                                                              |

| PIR1                                                               | PSPIF <sup>(1)</sup>                                      | ADIF                                                                                                | RCIF                                                                                                     | TXIF                                                                                                                                                                                             | SSPIF                                                                                                                                                                                        | CCP1IF                                                                                                                                                                                                                                                      | TMR2IF                                                                                                                                                                                                                                               | TMR1IF                                                                                                                                                                                                                                                                        | 0000 0000                                                                                                                                                                                                                                                                                                  | 0000 0000                                                                                                                                                                                                                                                                                                                                                                                              |

| RCSTA                                                              | SPEN                                                      | RX9                                                                                                 | SREN                                                                                                     | CREN                                                                                                                                                                                             |                                                                                                                                                                                              | FERR                                                                                                                                                                                                                                                        | OERR                                                                                                                                                                                                                                                 | RX9D                                                                                                                                                                                                                                                                          | 0000 -00x                                                                                                                                                                                                                                                                                                  | 0000 -00x                                                                                                                                                                                                                                                                                                                                                                                              |

| RCREG                                                              | USART Re                                                  | JSART Receive Register                                                                              |                                                                                                          |                                                                                                                                                                                                  |                                                                                                                                                                                              |                                                                                                                                                                                                                                                             |                                                                                                                                                                                                                                                      |                                                                                                                                                                                                                                                                               |                                                                                                                                                                                                                                                                                                            | 0000 0000                                                                                                                                                                                                                                                                                                                                                                                              |

| PIE1                                                               | PSPIE <sup>(1)</sup>                                      | ADIE                                                                                                | RCIE                                                                                                     | TXIE                                                                                                                                                                                             | SSPIE                                                                                                                                                                                        | CCP1IE                                                                                                                                                                                                                                                      | TMR2IE                                                                                                                                                                                                                                               | TMR1IE                                                                                                                                                                                                                                                                        | 0000 0000                                                                                                                                                                                                                                                                                                  | 0000 0000                                                                                                                                                                                                                                                                                                                                                                                              |

| TXSTA                                                              | CSRC                                                      | TX9                                                                                                 | TXEN                                                                                                     | SYNC                                                                                                                                                                                             |                                                                                                                                                                                              | BRGH                                                                                                                                                                                                                                                        | TRMT                                                                                                                                                                                                                                                 | TX9D                                                                                                                                                                                                                                                                          | 0000 -010                                                                                                                                                                                                                                                                                                  | 0000 -010                                                                                                                                                                                                                                                                                                                                                                                              |

| SPBRG                                                              | Baud Rate                                                 | Baud Rate Generator Register                                                                        |                                                                                                          |                                                                                                                                                                                                  |                                                                                                                                                                                              |                                                                                                                                                                                                                                                             |                                                                                                                                                                                                                                                      |                                                                                                                                                                                                                                                                               | 0000 0000                                                                                                                                                                                                                                                                                                  | 0000 0000                                                                                                                                                                                                                                                                                                                                                                                              |

|                                                                    | Name<br>INTCON<br>PIR1<br>RCSTA<br>RCREG<br>PIE1<br>TXSTA | NameBit 7INTCONGIEPIR1PSPIF <sup>(1)</sup> RCSTASPENRCREGUSART RePIE1PSPIE <sup>(1)</sup> TXSTACSRC | NameBit 7Bit 6INTCONGIEPEIEPIR1PSPIF(1)ADIFRCSTASPENRX9RCREGUSART Receive RePIE1PSPIE(1)ADIETXSTACSRCTX9 | NameBit 7Bit 6Bit 5INTCONGIEPEIETMR0IEPIR1PSPIF <sup>(1)</sup> ADIFRCIFRCSTASPENRX9SRENRCREGUSART Receive RegisterPIE1PSPIE <sup>(1)</sup> ADIEPIE1PSPIE <sup>(1)</sup> ADIERCIETXSTACSRCTX9TXEN | NameBit 7Bit 6Bit 5Bit 4INTCONGIEPEIETMROIEINTEPIR1PSPIF <sup>(1)</sup> ADIFRCIFTXIFRCSTASPENRX9SRENCRENRCREGUSART Receive RegisterFIE1PSPIE <sup>(1)</sup> ADIERCIETXIETXSTACSRCTX9TXENSYNC | NameBit 7Bit 6Bit 5Bit 4Bit 3INTCONGIEPEIETMROIEINTERBIEPIR1PSPIF <sup>(1)</sup> ADIFRCIFTXIFSSPIFRCSTASPENRX9SRENCREN—RCREGUSART Receive RegisterFIE1PSPIE <sup>(1)</sup> ADIERCIETXIESSPIEPIE1PSPIE <sup>(1)</sup> ADIERCIETXIESSPIETXSTACSRCTX9TXENSYNC— | NameBit 7Bit 6Bit 5Bit 4Bit 3Bit 2INTCONGIEPEIETMR0IEINTERBIETMR0IFPIR1PSPIF <sup>(1)</sup> ADIFRCIFTXIFSSPIFCCP1IFRCSTASPENRX9SRENCREN—FERRRCREGUSART Receive RegisterFFFFPIE1PSPIE <sup>(1)</sup> ADIERCIETXIESSPIECCP1IETXSTACSRCTX9TXENSYNC—BRGH | NameBit 7Bit 6Bit 5Bit 4Bit 3Bit 2Bit 1INTCONGIEPEIETMROIEINTERBIETMROIFINTFPIR1PSPIF <sup>(1)</sup> ADIFRCIFTXIFSSPIFCCP1IFTMR2IFRCSTASPENRX9SRENCREN—FERROERRRCREGUSART Receive RegisterFIE1PSPIE <sup>(1)</sup> ADIERCIETXIESSPIECCP1IETMR2IETXSTACSRCTX9TXENSYNC—BRGHTRMT | NameBit 7Bit 6Bit 5Bit 4Bit 3Bit 2Bit 1Bit 0INTCONGIEPEIETMROIEINTERBIETMROIFINTFROIFPIR1PSPIF <sup>(1)</sup> ADIFRCIFTXIFSSPIFCCP1IFTMR2IFTMR1IFRCSTASPENRX9SRENCREN—FERROERRRX9DRCREGUSART Receive RegisterFIE1PSPIE <sup>(1)</sup> ADIERCIETXIESSPIECCP1IETMR2IETMR1IETXSTACSRCTX9TXENSYNC—BRGHTRMTTX9D | NameBit 7Bit 6Bit 5Bit 4Bit 3Bit 2Bit 1Bit 0Value on:<br>POR, BORINTCONGIEPEIETMROIEINTERBIETMROIFINTFROIF0000000xPIR1PSPIF <sup>(1)</sup> ADIFRCIFTXIFSSPIFCCP1IFTMR2IFTMR1IF00000000RCSTASPENRX9SRENCREN—FERROERRRX9D0000-00xRCREGUSART Receive RegisterSYPIECCP1IETMR2IETMR1IE00000000PIE1PSPIE <sup>(1)</sup> ADIERCIETXIESSPIECCP1IETMR2IETMR1IE00000000TXSTACSRCTX9TXENSYNC—BRGHTRMTTX9D0000-011 |

#### TABLE 10-9: REGISTERS ASSOCIATED WITH SYNCHRONOUS MASTER RECEPTION

Legend: x = unknown, - = unimplemented, read as '0'. Shaded cells are not used for synchronous master reception. Note 1: Bits PSPIE and PSPIF are reserved on 28-pin devices; always maintain these bits clear.

#### 11.4 A/D Conversions

Clearing the GO/DONE bit during a conversion will abort the current conversion. The A/D Result register pair will NOT be updated with the partially completed A/D conversion sample. That is, the ADRESH:ADRESL registers will continue to contain the value of the last completed conversion (or the last value written to the ADRESH:ADRESL registers). After the A/D conversion

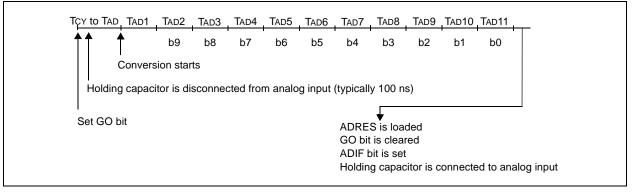

FIGURE 11-3: A/D CONVERSION TAD CYCLES

is aborted, the next acquisition on the selected channel is automatically started. The GO/DONE bit can then be set to start the conversion.

In Figure 11-3, after the GO bit is set, the first time segment has a minimum of TCY and a maximum of TAD.

**Note:** The GO/DONE bit should **NOT** be set in the same instruction that turns on the A/D.

#### 11.4.1 A/D RESULT REGISTERS

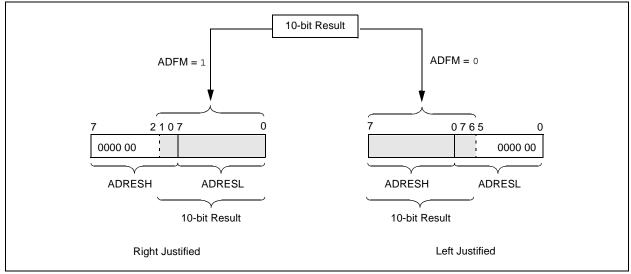

The ADRESH:ADRESL register pair is the location where the 10-bit A/D result is loaded at the completion of the A/D conversion. This register pair is 16 bits wide. The A/D module gives the flexibility to left or right justify the 10-bit result in the 16-bit result register. The A/D Format Select bit (ADFM) controls this justification. Figure 11-4 shows the operation of the A/D result justification. The extra bits are loaded with '0's. When an A/D result will not overwrite these locations (A/D disable), these registers may be used as two general purpose 8-bit registers.

#### FIGURE 11-4: A/D RESULT JUSTIFICATION

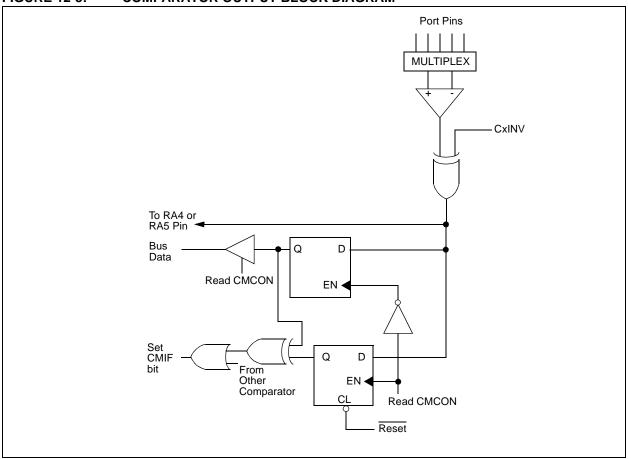

#### 12.6 Comparator Interrupts

The comparator interrupt flag is set whenever there is a change in the output value of either comparator. Software will need to maintain information about the status of the output bits, as read from CMCON<7:6>, to determine the actual change that occurred. The CMIF bit (PIR registers) is the Comparator Interrupt Flag. The CMIF bit must be reset by clearing it ('0'). Since it is also possible to write a '1' to this register, a simulated interrupt may be initiated.

The CMIE bit (PIE registers) and the PEIE bit (INTCON register) must be set to enable the interrupt. In addition, the GIE bit must also be set. If any of these bits are clear, the interrupt is not enabled, though the CMIF bit will still be set if an interrupt condition occurs.

Note: If a change in the CMCON register (C1OUT or C2OUT) should occur when a read operation is being executed (start of the Q2 cycle), then the CMIF (PIR registers) interrupt flag may not get set.

The user, in the Interrupt Service Routine, can clear the interrupt in the following manner:

- a) Any read or write of CMCON will end the mismatch condition.

- b) Clear flag bit CMIF.

A mismatch condition will continue to set flag bit CMIF. Reading CMCON will end the mismatch condition and allow flag bit CMIF to be cleared.

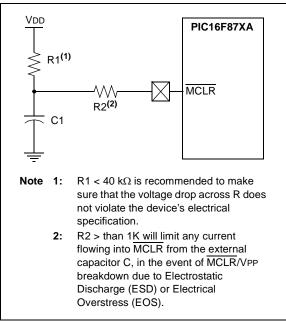

#### 14.4 MCLR

PIC16F87XA devices have a noise filter in the MCLR Reset path. The filter will detect and ignore small pulses.

It should be noted that a WDT Reset does not drive  $\overline{\text{MCLR}}$  pin low.

The behavior of the ESD protection on the MCLR pin differs from previous devices of this family. Voltages applied to the pin that exceed its specification can result in both Resets and current consumption outside of device specification during the Reset event. For this reason, Microchip recommends that the MCLR pin no longer be tied directly to VDD. The use of an RCR network, as shown in Figure 14-5, is suggested.

FIGURE 14-5: RECOMMENDED MCLR CIRCUIT

#### 14.5 Power-on Reset (POR)

A Power-on Reset pulse is generated on-chip when VDD rise is detected (in the range of <u>1.2V-1.7V</u>). To take advantage of the POR, tie the MCLR pin to VDD through an RC network, as described in **Section 14.4** "**MCLR**". A maximum rise time for VDD is specified. See **Section 17.0** "**Electrical Characteristics**" for details.

When the device starts normal operation (exits the Reset condition), device operating parameters (voltage, frequency, temperature, etc.) must be met to ensure operation. If these conditions are not met, the device must be held in Reset until the operating conditions are met. Brown-out Reset may be used to meet the start-up conditions. For additional information, refer to application note, *AN607, "Power-up Trouble Shooting*" (DS00607).

#### 14.6 Power-up Timer (PWRT)

The Power-up Timer provides a fixed 72 ms nominal time-out on power-up only from the POR. The Power-up Timer operates on an internal RC oscillator. The chip is kept in Reset as long as the PWRT is active. The PWRT's time delay allows VDD to rise to an acceptable level. A configuration bit is provided to enable or disable the PWRT.

The power-up time delay will vary from chip to chip due to VDD, temperature and process variation. See **Section 17.0 "Electrical Characteristics"** for details (TPWRT, parameter #33).

### 14.7 Oscillator Start-up Timer (OST)

The Oscillator Start-up Timer (OST) provides a delay of 1024 oscillator cycles (from OSC1 input) after the PWRT delay is over (if PWRT is enabled). This helps to ensure that the crystal oscillator or resonator has started and stabilized.

The OST time-out is invoked only for XT, LP and HS modes and only on Power-on Reset or wake-up from Sleep.

#### 14.8 Brown-out Reset (BOR)

The configuration bit, BODEN, can enable or disable the Brown-out Reset circuit. If VDD falls below VBOR (parameter D005, about 4V) for longer than TBOR (parameter #35, about 100  $\mu$ S), the brown-out situation will reset the device. If VDD falls below VBOR for less than TBOR, a Reset may not occur.

Once the brown-out occurs, the device will remain in Brown-out Reset until VDD rises above VBOR. The Power-up Timer then keeps the device in Reset for TPWRT (parameter #33, about 72 mS). If VDD should fall below VBOR during TPWRT, the Brown-out Reset process will restart when VDD rises above VBOR with the Power-up Timer Reset. The Power-up Timer is always enabled when the Brown-out Reset circuit is enabled, regardless of the state of the PWRT configuration bit.

#### 14.9 Time-out Sequence

On power-up, the time-out sequence is as follows: the PWRT delay starts (if enabled) when a POR Reset occurs. Then, OST starts counting 1024 oscillator cycles when PWRT ends (LP, XT, HS). When the OST ends, the device comes out of Reset.

If MCLR is kept low long enough, the time-outs will expire. Bringing MCLR high will begin execution immediately. This is useful for testing purposes or to synchronize more than one PIC16F87XA device operating in parallel.

Table 14-5 shows the Reset conditions for the Status, PCON and PC registers, while Table 14-6 shows the Reset conditions for all the registers.

#### 14.11.1 INT INTERRUPT

External interrupt on the RB0/INT pin is edge triggered, either rising if bit INTEDG (OPTION\_REG<6>) is set or falling if the INTEDG bit is clear. When a valid edge appears on the RB0/INT pin, flag bit, INTF (INTCON<1>), is set. This interrupt can be disabled by clearing enable bit, INTE (INTCON<4>). Flag bit INTF must be cleared in software in the Interrupt Service Routine before re-enabling this interrupt. The INT interrupt can wake-up the processor from Sleep if bit INTE was set prior to going into Sleep. The status of global interrupt enable bit, GIE, decides whether or not the processor branches to the interrupt vector following wake-up. See Section 14.14 "Power-down Mode (Sleep)" for details on Sleep mode.

#### 14.11.2 TMR0 INTERRUPT

An overflow (FFh  $\rightarrow$  00h) in the TMR0 register will set flag bit, TMR0IF (INTCON<2>). The interrupt can be enabled/disabled by setting/clearing enable bit, TMR0IE (INTCON<5>). See **Section 5.0 "Timer0 Module"**.

#### 14.11.3 PORTB INTCON CHANGE

An input change on PORTB<7:4> sets flag bit, RBIF (INTCON<0>). The interrupt can be enabled/disabled by setting/clearing enable bit, RBIE (INTCON<4>). See Section 4.2 "PORTB and the TRISB Register".

#### 14.12 Context Saving During Interrupts

During an interrupt, only the return PC value is saved on the stack. Typically, users may wish to save key registers during an interrupt (i.e., W register and Status register). This will have to be implemented in software.

For the PIC16F873A/874A devices, the register W\_TEMP must be defined in both Banks 0 and 1 and must be defined at the same offset from the bank base address (i.e., If W\_TEMP is defined at 0x20 in Bank 0, it must also be defined at 0xA0 in Bank 1). The registers, PCLATH\_TEMP and STATUS\_TEMP, are only defined in Bank 0.

Since the upper 16 bytes of each bank are common in the PIC16F876A/877A devices, temporary holding registers, W\_TEMP, STATUS\_TEMP and PCLATH\_TEMP, should be placed in here. These 16 locations don't require banking and therefore, make it easier for context save and restore. The same code shown in Example 14-1 can be used.

| EXAMPLE 14-1: | SAVING STATUS, W AND PCLATH REGISTERS IN RAM |   |

|---------------|----------------------------------------------|---|

|               |                                              | 1 |

| MOVWF  | W_TEMP         | ;Copy W to TEMP register                                |

|--------|----------------|---------------------------------------------------------|

| SWAPF  | STATUS,W       | ;Swap status to be saved into W                         |

| CLRF   | STATUS         | ;bank 0, regardless of current bank, Clears IRP,RP1,RP0 |

| MOVWF  | STATUS_TEMP    | ;Save status to bank zero STATUS_TEMP register          |

| MOVF   | PCLATH, W      | ;Only required if using pages 1, 2 and/or 3             |

| MOVWF  | PCLATH_TEMP    | ;Save PCLATH into W                                     |

| CLRF   | PCLATH         | ;Page zero, regardless of current page                  |

| :      |                |                                                         |

| :(ISR) |                | ;(Insert user code here)                                |

| :      |                |                                                         |

| MOVF   | PCLATH TEMP, W | ;Restore PCLATH                                         |

| MOVWF  | PCLATH         | ;Move W into PCLATH                                     |

| SWAPF  | STATUS TEMP,W  | ;Swap STATUS TEMP register into W                       |

|        | _              | ;(sets bank to original state)                          |

| MOVWF  | STATUS         | ;Move W into STATUS register                            |

| SWAPF  | W TEMP,F       | ;Swap W TEMP                                            |

| SWAPF  | W TEMP,W       | ;Swap W TEMP into W                                     |

|        |                |                                                         |

| 15.2 | Instruction | Descriptions |

|------|-------------|--------------|

|------|-------------|--------------|

| ADDLW            | Add Literal and W                                                                                                          |  |

|------------------|----------------------------------------------------------------------------------------------------------------------------|--|

| Syntax:          | [ <i>label</i> ] ADDLW k                                                                                                   |  |

| Operands:        | $0 \leq k \leq 255$                                                                                                        |  |

| Operation:       | $(W) + k \to (W)$                                                                                                          |  |

| Status Affected: | C, DC, Z                                                                                                                   |  |

| Description:     | The contents of the W register<br>are added to the eight-bit literal 'k'<br>and the result is placed in the W<br>register. |  |

|                  | register.                                                                                                                                                      |

|------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ADDWF            | Add W and f                                                                                                                                                    |

| Syntax:          | [label] ADDWF f,d                                                                                                                                              |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ d \in [0,1] \end{array}$                                                                                                |

| Operation:       | (W) + (f) $\rightarrow$ (destination)                                                                                                                          |

| Status Affected: | C, DC, Z                                                                                                                                                       |

| Description:     | Add the contents of the W register<br>with register 'f'. If 'd' is '0', the<br>result is stored in the W register. If<br>'d' is '1', the result is stored back |

| BCF              | Bit Clear f                                                         |

|------------------|---------------------------------------------------------------------|

| Syntax:          | [label]BCF f,b                                                      |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ 0 \leq b \leq 7 \end{array}$ |

| Operation:       | $0 \rightarrow (f < b >)$                                           |

| Status Affected: | None                                                                |

| Description:     | Bit 'b' in register 'f' is cleared.                                 |

| BSF              | Bit Set f                                                           |

|------------------|---------------------------------------------------------------------|

| Syntax:          | [ <i>label</i> ] BSF f,b                                            |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ 0 \leq b \leq 7 \end{array}$ |

| Operation:       | $1 \rightarrow (f < b >)$                                           |

| Status Affected: | None                                                                |

| Description:     | Bit 'b' in register 'f' is set.                                     |

| ANDLW            | AND Literal with W                                                                                                     |

|------------------|------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [ <i>label</i> ] ANDLW k                                                                                               |

| Operands:        | $0 \leq k \leq 255$                                                                                                    |

| Operation:       | (W) .AND. (k) $\rightarrow$ (W)                                                                                        |

| Status Affected: | Z                                                                                                                      |

| Description:     | The contents of W register are<br>AND'ed with the eight-bit literal<br>'k'. The result is placed in the W<br>register. |

in register 'f'.

| BTFSS            | Bit Test f, Skip if Set                                                                                                                                                                                         |

|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [ label ] BTFSS f,b                                                                                                                                                                                             |

| Operands:        | $0 \le f \le 127$<br>$0 \le b < 7$                                                                                                                                                                              |

| Operation:       | skip if (f <b>) = 1</b>                                                                                                                                                                                         |

| Status Affected: | None                                                                                                                                                                                                            |

| Description:     | If bit 'b' in register 'f' is '0', the next<br>instruction is executed.<br>If bit 'b' is '1', then the next instruc-<br>tion is discarded and a NOP is<br>executed instead, making this a<br>2 TCY instruction. |

| ANDWF            | AND W with f                                                                                                                                                    |  |

|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Syntax:          | [label] ANDWF f,d                                                                                                                                               |  |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ d \in [0,1] \end{array}$                                                                                                 |  |

| Operation:       | (W) .AND. (f) $\rightarrow$ (destination)                                                                                                                       |  |

| Status Affected: | Z                                                                                                                                                               |  |

| Description:     | AND the W register with register<br>'f'. If 'd' is '0', the result is stored in<br>the W register. If 'd' is '1', the<br>result is stored back in register 'f'. |  |

| BTFSC            | Bit Test, Skip if Clear                                                                                                                                                                                      |  |

|------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Syntax:          | [ label ] BTFSC f,b                                                                                                                                                                                          |  |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ 0 \leq b \leq 7 \end{array}$                                                                                                                                          |  |

| Operation:       | skip if (f <b>) = <math>0</math></b>                                                                                                                                                                         |  |

| Status Affected: | None                                                                                                                                                                                                         |  |

| Description:     | If bit 'b' in register 'f' is '1', the next instruction is executed.<br>If bit 'b' in register 'f' is '0', the next instruction is discarded and a NOP is executed instead, making this a 2 TCY instruction. |  |

## 16.0 DEVELOPMENT SUPPORT

The PIC<sup>®</sup> microcontrollers are supported with a full range of hardware and software development tools:

- Integrated Development Environment

- MPLAB<sup>®</sup> IDE Software

- Assemblers/Compilers/Linkers

- MPASM<sup>™</sup> Assembler

- MPLAB C17 and MPLAB C18 C Compilers

- MPLINK<sup>™</sup> Object Linker/

- MPLIB<sup>™</sup> Object Librarian

- MPLAB C30 C Compiler

- MPLAB ASM30 Assembler/Linker/Library

- Simulators

- MPLAB SIM Software Simulator

- MPLAB dsPIC30 Software Simulator

- Emulators

- MPLAB ICE 2000 In-Circuit Emulator

- MPLAB ICE 4000 In-Circuit Emulator

- In-Circuit Debugger

- MPLAB ICD 2

- Device Programmers

- PRO MATE<sup>®</sup> II Universal Device Programmer

- PICSTART<sup>®</sup> Plus Development Programmer

- Low Cost Demonstration Boards

- PICDEM<sup>™</sup> 1 Demonstration Board

- PICDEM.net<sup>™</sup> Demonstration Board

- PICDEM 2 Plus Demonstration Board

- PICDEM 3 Demonstration Board

- PICDEM 4 Demonstration Board

- PICDEM 17 Demonstration Board

- PICDEM 18R Demonstration Board

- PICDEM LIN Demonstration Board

- PICDEM USB Demonstration Board

- Evaluation Kits

- KEELOQ<sup>®</sup>

- PICDEM MSC

- microID<sup>®</sup>

- CAN

- PowerSmart<sup>®</sup>

- Analog

#### 16.1 MPLAB Integrated Development Environment Software