#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

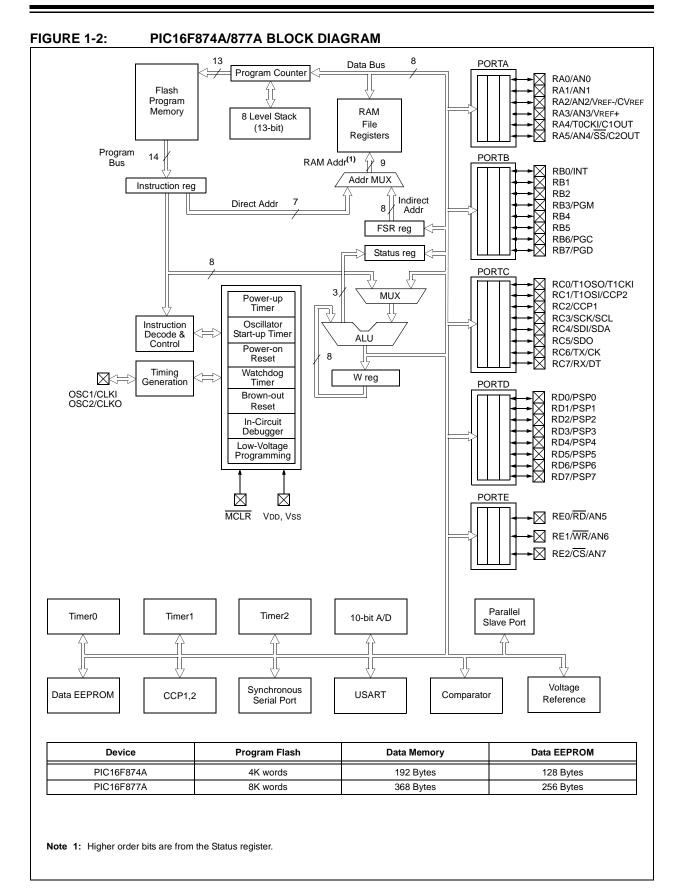

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

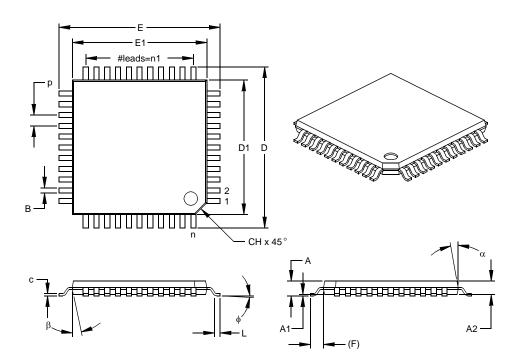

| Product Status             | Active                                                                   |

|----------------------------|--------------------------------------------------------------------------|

| Core Processor             | PIC                                                                      |

| Core Size                  | 8-Bit                                                                    |

| Speed                      | 20MHz                                                                    |

| Connectivity               | I²C, SPI, UART/USART                                                     |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                    |

| Number of I/O              | 33                                                                       |

| Program Memory Size        | 7KB (4K x 14)                                                            |

| Program Memory Type        | FLASH                                                                    |

| EEPROM Size                | 128 x 8                                                                  |

| RAM Size                   | 192 x 8                                                                  |

| Voltage - Supply (Vcc/Vdd) | 4V ~ 5.5V                                                                |

| Data Converters            | A/D 8x10b                                                                |

| Oscillator Type            | External                                                                 |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                        |

| Mounting Type              | Through Hole                                                             |

| Package / Case             | 40-DIP (0.600", 15.24mm)                                                 |

| Supplier Device Package    | 40-PDIP                                                                  |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16f874a-i-p |

|                            |                                                                          |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| 1 1 4 1 | սու | 2-3: |  |

|---------|-----|------|--|

#### PIC16F876A/877A REGISTER FILE MAP

| Indirect addr.(*)    | 00h         | Indirect addr.(*)             |           | Indirect addr.(*)   | 100h          | Indirect addr.(*)       | 10 |

|----------------------|-------------|-------------------------------|-----------|---------------------|---------------|-------------------------|----|

| TMR0                 | 00n<br>01h  | OPTION REG                    | 80h       | TMR0                | 100h          | OPTION_REG              | 18 |

| PCL                  | 01h<br>02h  |                               | 81h       | PCL                 | 10111<br>102h |                         | 18 |

|                      | 02n<br>03h  | PCL<br>STATUS                 | 82h       | STATUS              | 10211<br>103h | PCL<br>STATUS           | 18 |

| STATUS               | 03n<br>04h  |                               | 83h       | FSR                 | 103n<br>104h  |                         | 18 |

| FSR                  |             | FSR                           | 84h       | FSR                 | 1041<br>105h  | FSR                     | 18 |

| PORTA                | 05h<br>06h  | TRISA                         | 85h       | DODTD               | 105h          | TRISB                   | 18 |

| PORTB                |             | TRISB                         | 86h       | PORTB               | 106n<br>107h  | TRISB                   | 18 |

|                      | 07h         | TRISC<br>TRISD <sup>(1)</sup> | 87h       |                     | 1071<br>108h  |                         | 18 |

| PORTD <sup>(1)</sup> | 08h         | TRISD <sup>(1)</sup>          | 88h       |                     | 109h          |                         | 18 |

| PORTE <sup>(1)</sup> | 09h         |                               | 89h       | PCLATH              | 1091<br>10Ah  | PCLATH                  | 18 |

| PCLATH               | 0Ah         | PCLATH                        | 8Ah       |                     | 10An<br>10Bh  | INTCON                  | 18 |

| INTCON               | 0Bh         | INTCON                        | 8Bh       | INTCON              | 10Bn<br>10Ch  | EECON1                  | 18 |

| PIR1                 | 0Ch         | PIE1                          | 8Ch       | EEDATA              |               |                         | 18 |

| PIR2                 | 0Dh         | PIE2                          | 8Dh       | EEADR               | 10Dh          | EECON2                  | 18 |

| TMR1L                | 0Eh         | PCON                          | 8Eh       | EEDATH              | 10Eh          | Reserved <sup>(2)</sup> | 18 |

| TMR1H                | 0Fh         |                               | 8Fh       | EEADRH              | 10Fh          | Reserved <sup>(2)</sup> | 18 |

| T1CON                | 10h         |                               | 90h       |                     | 110h          |                         | 19 |

| TMR2                 | 11h         | SSPCON2                       | 91h       |                     | 111h          |                         | 19 |

| T2CON                | 12h         | PR2                           | 92h       |                     | 112h          |                         | 19 |

| SSPBUF               | 13h         | SSPADD                        | 93h       |                     | 113h          |                         | 19 |

| SSPCON               | 14h         | SSPSTAT                       | 94h       |                     | 114h          |                         | 19 |

| CCPR1L               | 15h         |                               | 95h       |                     | 115h          |                         | 19 |

| CCPR1H               | 16h         |                               | 96h       | Conorol             | 116h          | Conorol                 | 19 |

| CCP1CON              | 17h         |                               | 97h       | General<br>Purpose  | 117h          | General<br>Purpose      | 19 |

| RCSTA                | 18h         | TXSTA                         | 98h       | Register            | 118h          | Register                | 19 |

| TXREG                | 19h         | SPBRG                         | 99h       | 16 Bytes            | 119h          | 16 Bytes                | 19 |

| RCREG                | 1Ah         |                               | 9Ah       |                     | 11Ah          |                         | 19 |

| CCPR2L               | 1Bh         |                               | 9Bh       |                     | 11Bh          |                         | 19 |

| CCPR2H               | 1Ch         | CMCON                         | 9Ch       |                     | 11Ch          |                         | 19 |

| CCP2CON              | 1Dh         | CVRCON                        | 9Dh       |                     | 11Dh          |                         | 19 |

| ADRESH               | 1Eh         | ADRESL                        | 9Eh       |                     | 11Eh          |                         | 19 |

| ADCON0               | 1Fh         | ADCON1                        | 9Fh       |                     | 11Fh          |                         | 19 |

|                      | 20h         |                               | A0h       |                     | 120h          |                         | 1A |

|                      |             | General                       |           | General             |               | General                 |    |

| General              |             | Purpose                       |           | Purpose             |               | Purpose                 |    |

| Purpose              |             | Register                      |           | Register            |               | Register                |    |

| Register             |             | 80 Bytes                      |           | 80 Bytes            |               | 80 Bytes                |    |

| 96 Bytes             |             |                               | EFh       |                     | 16Fh          |                         | 1E |

|                      |             | accesses                      | F0h       | 200005005           | 170h          | accesses                | 1F |

|                      |             | 70h-7Fh                       |           | accesses<br>70h-7Fh |               | 70h - 7Fh               |    |

| <b>_</b>             | 7Fh         |                               | FFh       |                     | 17Fh          |                         | 1F |

| Bank 0               |             | Bank 1                        |           | Bank 2              |               | Bank 3                  |    |

| Unimple              | mented d    | ata memory locati             | ons. read | <b>as</b> '0'.      |               |                         |    |

|                      | iysical reg | -                             |           |                     |               |                         |    |

An example of the complete four-word write sequence is shown in Example 3-4. The initial address is loaded into the EEADRH:EEADR register pair; the four words of data are loaded using indirect addressing.

#### EXAMPLE 3-4: WRITING TO FLASH PROGRAM MEMORY

; This write routine assumes the following: ; 1. A valid starting address (the least significant bits = '00') is loaded in ADDRH:ADDRL ; 2. The 8 bytes of data are loaded, starting at the address in DATADDR ; 3. ADDRH, ADDRL and DATADDR are all located in shared data memory 0x70 - 0x7f ; BSF STATUS, RP1 ; ; Bank 2 BCF STATUS, RPO ; Load initial address MOVF ADDRH,W MOVWF EEADRH MOVF ADDRL,W ; MOVWF EEADR MOVF DATAADDR,W ; Load initial data address MOVWF FSR ; Load first data byte into lower LOOP MOVF INDF,W MOVWF EEDATA ; INCF FSR,F ; Next byte INDF,W MOVE ; Load second data byte into upper MOVWF EEDATH : INCF FSR,F ; ; Bank 3 STATUS, RPO BSF EECON1, EEPGD BSF ; Point to program memory ; Enable writes BSF EECON1,WREN BCF INTCON,GIE ; Disable interrupts (if using) MOVLW 55h ; Start of required write sequence: MOVWF EECON2 ; Write 55h MOVLW AAh ; Write AAh MOVWF EECON2 BSF EECON1,WR ; Set WR bit to begin write NOP ; Any instructions here are ignored as processor ; halts to begin write sequence NOP ; processor will stop here and wait for write complete ; after write processor continues with 3rd instruction EECON1,WREN BCF ; Disable writes INTCON, GIE ; Enable interrupts (if using) BSF BCF STATUS, RPO ; Bank 2 INCE EEADR, F ; Increment address ; Check if lower two bits of address are `00' MOVF EEADR,W ANDLW ; Indicates when four words have been programmed 0x03 XORLW 0x03 ; BTFSC STATUS,Z ; Exit if more than four words, GOTO ; Continue if less than four words LOOP

# 3.7 Protection Against Spurious Write

There are conditions when the device should not write to the data EEPROM or Flash program memory. To protect against spurious writes, various mechanisms have been built-in. On power-up, WREN is cleared. Also, the Power-up Timer (72 ms duration) prevents an EEPROM write.

The write initiate sequence and the WREN bit together help prevent an accidental write during brown-out, power glitch or software malfunction.

# 3.8 Operation During Code-Protect

When the data EEPROM is code-protected, the microcontroller can read and write to the EEPROM normally. However, all external access to the EEPROM is disabled. External write access to the program memory is also disabled.

When program memory is code-protected, the microcontroller can read and write to program memory normally, as well as execute instructions. Writes by the device may be selectively inhibited to regions of the memory depending on the setting of bits WR1:WR0 of the configuration word (see **Section 14.1 "Configuration Bits"** for additional information). External access to the memory is also disabled.

# TABLE 3-1:REGISTERS/BITS ASSOCIATED WITH DATA EEPROM AND<br/>FLASH PROGRAM MEMORIES

| Address | Name                                            | Bit 7  | Bit 6                                              | Bit 5    | Bit 4                   | Bit 3       | Bit 2      | Bit 1        | Bit 0  | Value on<br>Power-on<br>Reset | Value on<br>all other<br>Resets |

|---------|-------------------------------------------------|--------|----------------------------------------------------|----------|-------------------------|-------------|------------|--------------|--------|-------------------------------|---------------------------------|

| 10Ch    | 10Ch EEDATA EEPROM/Flash Data Register Low Byte |        |                                                    |          |                         |             |            |              |        |                               | uuuu uuuu                       |

| 10Dh    | EEADR                                           | EEPRON | 1/Flash A                                          | ddress R | egister L               | ow Byte     |            |              |        | xxxx xxxx                     | uuuu uuuu                       |

| 10Eh    | EEDATH                                          | _      | _                                                  | EEPRO    | M/Flash [               | Data Regist | er High By | te           |        | xxxx xxxx                     | 0 q000                          |

| 10Fh    | EEADRH                                          | _      | _                                                  | _        | EEPRO                   | M/Flash Ad  | dress Reg  | ister High B | yte    | xxxx xxxx                     |                                 |

| 18Ch    | EECON1                                          | EEPGD  | _                                                  | —        | —                       | WRERR       | WREN       | WR           | RD     | x x000                        | 0 q000                          |

| 18Dh    | EECON2                                          | EEPRON | EPROM Control Register 2 (not a physical register) |          |                         |             |            |              |        |                               |                                 |

| 0Dh     | PIR2                                            | _      | CMIF                                               | —        | – EEIF BCLIF – – CCP2IF |             |            |              |        | -0-0 00                       | -0-0 00                         |

| 8Dh     | PIE2                                            | _      | CMIE                                               | _        | EEIE                    | BCLIE       | _          | _            | CCP2IE | -0-0 00                       | -0-0 00                         |

Legend: x = unknown, u = unchanged, - = unimplemented, read as '0', q = value depends upon condition. Shaded cells are not used by data EEPROM or Flash program memory.

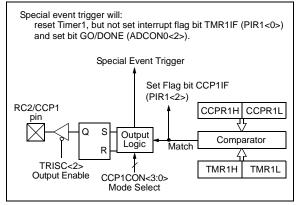

# 8.2 Compare Mode

In Compare mode, the 16-bit CCPR1 register value is constantly compared against the TMR1 register pair value. When a match occurs, the RC2/CCP1 pin is:

- Driven high

- Driven low

- Remains unchanged

The action on the pin is based on the value of control bits, CCP1M3:CCP1M0 (CCP1CON<3:0>). At the same time, interrupt flag bit CCP1IF is set.

#### FIGURE 8-2: COMPARE MODE OPERATION BLOCK DIAGRAM

# 8.2.1 CCP PIN CONFIGURATION

The user must configure the RC2/CCP1 pin as an output by clearing the TRISC<2> bit.

| Note: | Clearing the CCP1CON register will force |

|-------|------------------------------------------|

|       | the RC2/CCP1 compare output latch to     |

|       | the default low level. This is not the   |

|       | PORTC I/O data latch.                    |

### 8.2.2 TIMER1 MODE SELECTION

Timer1 must be running in Timer mode, or Synchronized Counter mode, if the CCP module is using the compare feature. In Asynchronous Counter mode, the compare operation may not work.

#### 8.2.3 SOFTWARE INTERRUPT MODE

When Generate Software Interrupt mode is chosen, the CCP1 pin is not affected. The CCPIF bit is set, causing a CCP interrupt (if enabled).

#### 8.2.4 SPECIAL EVENT TRIGGER

In this mode, an internal hardware trigger is generated which may be used to initiate an action.

The special event trigger output of CCP1 resets the TMR1 register pair. This allows the CCPR1 register to effectively be a 16-bit programmable period register for Timer1.

The special event trigger output of CCP2 resets the TMR1 register pair and starts an A/D conversion (if the A/D module is enabled).

### 9.3.1 REGISTERS

The MSSP module has four registers for SPI mode operation. These are:

- MSSP Control Register (SSPCON)

- MSSP Status Register (SSPSTAT)

- Serial Receive/Transmit Buffer Register (SSPBUF)

- MSSP Shift Register (SSPSR) Not directly accessible

SSPCON and SSPSTAT are the control and status registers in SPI mode operation. The SSPCON register is readable and writable. The lower six bits of the SSPSTAT are read-only. The upper two bits of the SSPSTAT are read/write. SSPSR is the shift register used for shifting data in or out. SSPBUF is the buffer register to which data bytes are written to or read from.

In receive operations, SSPSR and SSPBUF together create a double-buffered receiver. When SSPSR receives a complete byte, it is transferred to SSPBUF and the SSPIF interrupt is set.

During transmission, the SSPBUF is not doublebuffered. A write to SSPBUF will write to both SSPBUF and SSPSR.

# REGISTER 9-1: SSPSTAT: MSSP STATUS REGISTER (SPI MODE) (ADDRESS 94h)

|       | R/W-0                    | R/W-0           | R-0             | R-0          | R-0           | R-0           | R-0          | R-0           |

|-------|--------------------------|-----------------|-----------------|--------------|---------------|---------------|--------------|---------------|

|       | SMP                      | CKE             | D/A             | Р            | S             | R/W           | UA           | BF            |

|       | bit 7                    |                 |                 |              |               |               |              | bit 0         |

| bit 7 | SMP: Sam                 | ple bit         |                 |              |               |               |              |               |

|       | SPI Master               |                 |                 |              |               |               |              |               |

|       |                          | ata sampled     |                 |              |               |               |              |               |

|       |                          | ata sampled     | at middle o     | r data outpu | tume          |               |              |               |

|       | SMP must                 | be cleared v    | when SPI is     | used in Slav | ve mode       |               |              |               |

| bit 6 |                          | Clock Select    |                 |              | o modo.       |               |              |               |

|       | 1 = Transm               | nit occurs on   | transition fr   | om active to | ldle clock s  | state         |              |               |

|       | 0 = Transm               | nit occurs on   | transition fr   | om Idle to a | ctive clock s | state         |              |               |

|       | Note:                    | Polarity of o   | clock state is  | s set by the | CKP bit (SS   | PCON1<4>      | ).           |               |

| bit 5 | D/A: Data/               | Address bit     |                 |              |               |               |              |               |

|       | Used in I <sup>2</sup> C | c mode only.    |                 |              |               |               |              |               |

| bit 4 | P: Stop bit              |                 |                 |              |               |               |              |               |

|       | Used in I <sup>2</sup> C | mode only.      | This bit is cle | ared when t  | he MSSP me    | odule is disa | bled, SSPEI  | N is cleared. |

| bit 3 | S: Start bit             |                 |                 |              |               |               |              |               |

|       | Used in I <sup>2</sup> C | c mode only.    |                 |              |               |               |              |               |

| bit 2 | R/W: Read                | I/Write bit inf | ormation        |              |               |               |              |               |

|       | Used in I <sup>2</sup> C | c mode only.    |                 |              |               |               |              |               |

| bit 1 | UA: Update               | e Address b     | it              |              |               |               |              |               |

|       | Used in I <sup>2</sup> C | c mode only.    |                 |              |               |               |              |               |

| bit 0 | BF: Buffer               | Full Status b   | oit (Receive    | mode only)   |               |               |              |               |

|       | 1 = Receiv               | e complete,     | SSPBUF is       | full         |               |               |              |               |

|       | 0 = Receiv               | e not comple    | ete, SSPBU      | F is empty   |               |               |              |               |

|       | Legend:                  |                 |                 |              |               |               |              |               |

|       | R = Reada                | ble bit         | W = W           | ritable bit  | U = Unim      | plemented     | bit, read as | '0'           |

|       | - n = Value              | at POR          | '1' = B         | it is set    | '0' = Bit i   | s cleared     | x = Bit is ι | Inknown       |

| ER 9-2: | SSPCON1: MSSP CONTROL REGISTER 1 (SPI MODE) (ADDRESS 14h) |                                                                                 |                                                               |                                                |                             |               |               |               |  |  |  |  |

|---------|-----------------------------------------------------------|---------------------------------------------------------------------------------|---------------------------------------------------------------|------------------------------------------------|-----------------------------|---------------|---------------|---------------|--|--|--|--|

|         | R/W-0                                                     | R/W-0                                                                           | R/W-0                                                         | R/W-0                                          | R/W-0                       | R/W-0         | R/W-0         | R/W-0         |  |  |  |  |

|         | WCOL                                                      | SSPOV                                                                           | SSPEN                                                         | CKP                                            | SSPM3                       | SSPM2         | SSPM1         | SSPM0         |  |  |  |  |

|         | bit 7                                                     |                                                                                 |                                                               |                                                |                             |               |               | bit 0         |  |  |  |  |

| bit 7   |                                                           | /rite Collision                                                                 | -                                                             |                                                |                             |               |               |               |  |  |  |  |

|         |                                                           | SSPBUF reg<br>ed in software<br>ollision                                        |                                                               | en while it i                                  | s still transm              | nitting the p | revious wor   | d. (Must be   |  |  |  |  |

| bit 6   | SSPOV: R                                                  | Receive Over                                                                    | flow Indicato                                                 | or bit                                         |                             |               |               |               |  |  |  |  |

|         | <u>SPI Slave</u>                                          | mode:                                                                           |                                                               |                                                |                             |               |               |               |  |  |  |  |

|         | of ove<br>must<br>cleare                                  | v byte is rece<br>erflow, the da<br>read the SSI<br>ed in software              | ata in SSPSF<br>PBUF, even                                    | R is lost. Ov                                  | verflow can o               | only occur in | Slave mod     | e. The user   |  |  |  |  |

|         | 0 = No ov                                                 | 0 = No overflow                                                                 |                                                               |                                                |                             |               |               |               |  |  |  |  |

|         | Note:                                                     |                                                                                 |                                                               |                                                | t is not set<br>to the SSPE |               |               | eption (and   |  |  |  |  |

| bit 5   | SSPEN: S                                                  | Synchronous                                                                     | Serial Port E                                                 | Enable bit                                     |                             |               |               |               |  |  |  |  |

|         |                                                           | es serial port<br>les serial por                                                |                                                               |                                                |                             |               | ial port pins |               |  |  |  |  |

|         | Note:                                                     | When enal                                                                       | oled, these p                                                 | oins must be                                   | e properly co               | nfigured as   | input or out  | put.          |  |  |  |  |

| bit 4   | CKP: Cloo                                                 | ck Polarity Se                                                                  | elect bit                                                     |                                                |                             |               |               |               |  |  |  |  |

|         |                                                           | ate for clock<br>ate for clock                                                  | •                                                             |                                                |                             |               |               |               |  |  |  |  |

| bit 3-0 | SSPM3:S                                                   | SPM0: Sync                                                                      | hronous Ser                                                   | ial Port Mod                                   | de Select bits              | 5             |               |               |  |  |  |  |

|         | 0100 = SF<br>0011 = SF<br>0010 = SF<br>0001 = SF          | PI Slave mod<br>PI Slave mod<br>PI Master mod<br>PI Master mod<br>PI Master mod | le, clock = S<br>ode, clock =<br>ode, clock =<br>ode, clock = | CK pin. SS<br>TMR2 outpu<br>Fosc/64<br>Fosc/16 | pin control e               |               | can be usec   | l as I/O pin. |  |  |  |  |

|         |                                                           | PI Master mo                                                                    |                                                               |                                                |                             |               |               |               |  |  |  |  |

|         | Note:                                                     | Bit combin<br>I <sup>2</sup> C mode o                                           |                                                               | becifically lis                                | sted here are               | either rese   | rved or imp   | lemented in   |  |  |  |  |

|         |                                                           |                                                                                 |                                                               |                                                |                             |               |               |               |  |  |  |  |

|         | I a manual.                                               |                                                                                 |                                                               |                                                |                             |               |               |               |  |  |  |  |

| Legend:            |                  |                      |                    |

|--------------------|------------------|----------------------|--------------------|

| R = Readable bit   | W = Writable bit | U = Unimplemented    | bit, read as '0'   |

| - n = Value at POR | '1' = Bit is set | '0' = Bit is cleared | x = Bit is unknown |

# REGISTER 9-2: SSPCON1: MSSP CONTROL REGISTER 1 (SPI MODE) (ADDRESS 14h)

# 9.3.8 SLEEP OPERATION

In Master mode, all module clocks are halted and the transmission/reception will remain in that state until the device wakes from Sleep. After the device returns to normal mode, the module will continue to transmit/ receive data.

In Slave mode, the SPI Transmit/Receive Shift register operates asynchronously to the device. This allows the device to be placed in Sleep mode and data to be shifted into the SPI Transmit/Receive Shift register. When all 8 bits have been received, the MSSP interrupt flag bit will be set and if enabled, will wake the device from Sleep.

#### 9.3.9 EFFECTS OF A RESET

A Reset disables the MSSP module and terminates the current transfer.

#### 9.3.10 BUS MODE COMPATIBILITY

Table 9-1 shows the compatibility between the standard SPI modes and the states of the CKP and CKE control bits.

#### TABLE 9-1: SPI BUS MODES

| Standard SPI Mode | Control E | Bits State |

|-------------------|-----------|------------|

| Terminology       | СКР       | CKE        |

| 0, 0              | 0         | 1          |

| 0, 1              | 0         | 0          |

| 1, 0              | 1         | 1          |

| 1, 1              | 1         | 0          |

There is also a SMP bit which controls when the data is sampled.

| Name    | Bit 7                | Bit 6                         | Bit 5      | Bit 4      | Bit 3       | Bit 2    | Bit 1  | Bit 0  | Valu<br>POR, | e on<br>BOR | Valu<br>all o<br>Res | ther |

|---------|----------------------|-------------------------------|------------|------------|-------------|----------|--------|--------|--------------|-------------|----------------------|------|

| INTCON  | GIE/<br>GIEH         | PEIE/<br>GIEL                 | TMR0IE     | INTOIE     | RBIE        | TMR0IF   | INTOIF | RBIF   | 0000         | 000x        | 0000                 | 000u |

| PIR1    | PSPIF <sup>(1)</sup> | ADIF                          | RCIF       | TXIF       | SSPIF       | CCP1IF   | TMR2IF | TMR1IF | 0000         | 0000        | 0000                 | 0000 |

| PIE1    | PSPIE <sup>(1)</sup> | ADIE                          | RCIE       | TXIE       | SSPIE       | CCP1IE   | TMR2IE | TMR1IE | 0000         | 0000        | 0000                 | 0000 |

| TRISC   | PORTC D              | ata Direc                     | tion Regis | ter        |             |          |        |        | 1111         | 1111        | 1111                 | 1111 |

| SSPBUF  | Synchron             | ous Seria                     | I Port Rec | eive Buffe | er/Transmit | Register |        |        | xxxx         | xxxx        | uuuu                 | uuuu |

| SSPCON  | WCOL                 | SSPOV                         | SSPEN      | CKP        | SSPM3       | SSPM2    | SSPM1  | SSPM0  | 0000         | 0000        | 0000                 | 0000 |

| TRISA   | —                    | PORTA Data Direction Register |            |            |             |          |        |        |              | 1111        | 11                   | 1111 |

| SSPSTAT | SMP                  | CKE                           | D/Ā        | Р          | S           | R/W      | UA     | BF     | 0000         | 0000        | 0000                 | 0000 |

#### TABLE 9-2: REGISTERS ASSOCIATED WITH SPI OPERATION

Legend: x = unknown, u = unchanged, - = unimplemented, read as '0'. Shaded cells are not used by the MSSP in SPI mode.

Note 1: The PSPIF, PSPIE and PSPIP bits are reserved on 28-pin devices; always maintain these bits clear.

|       | R/W-0                                                                                                                                                        | R/W-0                                                                                                                                                 | R/W-0                    | R/W-0          | R/W-0         | R/W-0        | R/W-0        | R/W-0       |  |  |  |

|-------|--------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------|----------------|---------------|--------------|--------------|-------------|--|--|--|

|       | GCEN                                                                                                                                                         | ACKSTAT                                                                                                                                               | ACKDT                    | ACKEN          | RCEN          | PEN          | RSEN         | SEN         |  |  |  |

|       | bit 7                                                                                                                                                        | 1                                                                                                                                                     |                          | I              |               | I            | I            | bit 0       |  |  |  |

| bit 7 |                                                                                                                                                              | eneral Call En                                                                                                                                        |                          | -              | -             |              |              |             |  |  |  |

|       |                                                                                                                                                              | e interrupt whe<br>ral call address                                                                                                                   |                          | call address   | (0000h) is    | received in  | the SSPSF    | 2           |  |  |  |

| bit 6 | ACKSTA                                                                                                                                                       | <b>f:</b> Acknowledg                                                                                                                                  | e Status bit             | (Master Tran   | smit mode o   | only)        |              |             |  |  |  |

|       |                                                                                                                                                              | ACKSTAT: Acknowledge Status bit (Master Transmit mode only)<br>1 = Acknowledge was not received from slave<br>0 = Acknowledge was received from slave |                          |                |               |              |              |             |  |  |  |

| bit 5 | ACKDT: A                                                                                                                                                     | Acknowledge [                                                                                                                                         | Data bit (Mas            | ster Receive   | mode only)    |              |              |             |  |  |  |

|       | 1 = Not A<br>0 = Ackno                                                                                                                                       | cknowledge<br>wledge                                                                                                                                  |                          |                |               |              |              |             |  |  |  |

|       | Note:                                                                                                                                                        | Value that w the end of a                                                                                                                             |                          | itted when th  | e user initia | tes an Ackr  | nowledge se  | equence at  |  |  |  |

| bit 4 | ACKEN:                                                                                                                                                       | Acknowledge                                                                                                                                           | Sequence E               | nable bit (Ma  | ster Receiv   | e mode on    | ly)          |             |  |  |  |

|       | 1 = Initiat<br>Autor                                                                                                                                         | e Acknowledg<br>matically cleare<br>owledge seque                                                                                                     | e sequence<br>d by hardw | e on SDA ar    |               |              |              | T data bit. |  |  |  |

| bit 3 | RCEN: R                                                                                                                                                      | eceive Enable                                                                                                                                         | bit (Master i            | mode only)     |               |              |              |             |  |  |  |

|       | 1 = Enabl<br>0 = Recei                                                                                                                                       | es Receive mo<br>ve Idle                                                                                                                              | ode for I <sup>2</sup> C |                |               |              |              |             |  |  |  |

| bit 2 | PEN: Stop                                                                                                                                                    | o Condition En                                                                                                                                        | able bit (Ma             | ster mode or   | nly)          |              |              |             |  |  |  |

|       |                                                                                                                                                              | e Stop conditio                                                                                                                                       | n on SDA a               | nd SCL pins.   | Automatica    | ally cleared | by hardwa    | re.         |  |  |  |

| bit 1 | RSEN: Re                                                                                                                                                     | epeated Start (                                                                                                                                       | Condition Er             | nabled bit (Ma | aster mode    | only)        |              |             |  |  |  |

|       | <ul> <li>1 = Initiate Repeated Start condition on SDA and SCL pins. Automatically cleared by hardware.</li> <li>0 = Repeated Start condition Idle</li> </ul> |                                                                                                                                                       |                          |                |               |              |              |             |  |  |  |

| bit 0 | SEN: Start Condition Enabled/Stretch Enabled bit                                                                                                             |                                                                                                                                                       |                          |                |               |              |              |             |  |  |  |

|       | In Master mode:<br>1 = Initiate Start condition on SDA and SCL pins. Automatically cleared by hardware.<br>0 = Start condition Idle                          |                                                                                                                                                       |                          |                |               |              |              |             |  |  |  |

|       |                                                                                                                                                              | <u>node:</u><br>stretching is e<br>stretching is e                                                                                                    |                          |                |               |              |              | nabled)     |  |  |  |

|       | Legend:                                                                                                                                                      |                                                                                                                                                       |                          |                |               |              |              |             |  |  |  |

|       | R = Read                                                                                                                                                     |                                                                                                                                                       |                          | itable bit     | -             |              | bit, read as |             |  |  |  |

|       | - n = Valu                                                                                                                                                   | e at POR                                                                                                                                              | '1' = Bit                | is set         | '0' = Bit is  | cleared      | x = Bit is ι | unknown     |  |  |  |

**Note:** For bits ACKEN, RCEN, PEN, RSEN, SEN: If the I<sup>2</sup>C module is not in the Idle mode, this bit may not be set (no spooling) and the SSPBUF may not be written (or writes to the SSPBUF are disabled).

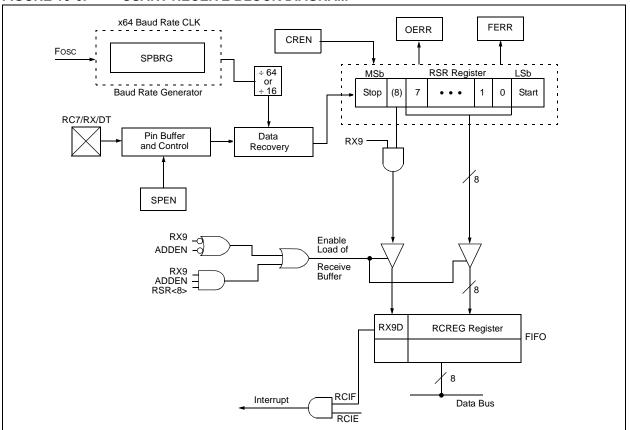

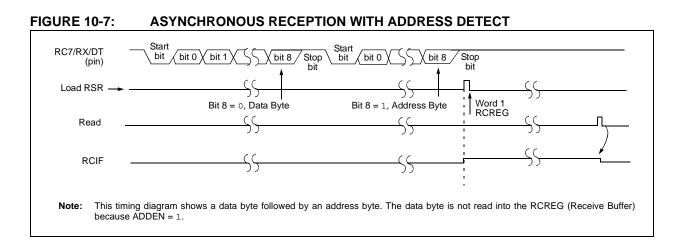

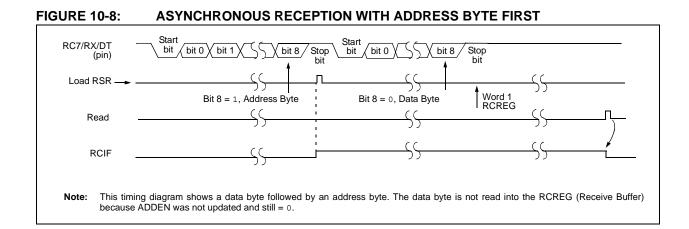

# 10.2.3 SETTING UP 9-BIT MODE WITH ADDRESS DETECT

When setting up an Asynchronous Reception with address detect enabled:

- Initialize the SPBRG register for the appropriate baud rate. If a high-speed baud rate is desired, set bit BRGH.

- Enable the asynchronous serial port by clearing bit SYNC and setting bit SPEN.

- If interrupts are desired, then set enable bit RCIE.

- Set bit RX9 to enable 9-bit reception.

- Set ADDEN to enable address detect.

- Enable the reception by setting enable bit CREN.

- Flag bit RCIF will be set when reception is complete, and an interrupt will be generated if enable bit RCIE was set.

- Read the RCSTA register to get the ninth bit and determine if any error occurred during reception.

- Read the 8-bit received data by reading the RCREG register to determine if the device is being addressed.

- If any error occurred, clear the error by clearing enable bit CREN.

- If the device has been addressed, clear the ADDEN bit to allow data bytes and address bytes to be read into the receive buffer and interrupt the CPU.

# FIGURE 10-6: USART RECEIVE BLOCK DIAGRAM

| Address                | Name   | Bit 7                | Bit 6                        | Bit 5  | Bit 4 | Bit 3 | Bit 2  | Bit 1  | Bit 0  | Value on:<br>POR, BOR | Value on<br>all other<br>Resets |

|------------------------|--------|----------------------|------------------------------|--------|-------|-------|--------|--------|--------|-----------------------|---------------------------------|

| 0Bh, 8Bh,<br>10Bh,18Bh | INTCON | GIE                  | PEIE                         | TMR0IE | INTE  | RBIE  | TMR0IF | INTF   | R0IF   | 0000 000x             | 0000 000u                       |

| 0Ch                    | PIR1   | PSPIF <sup>(1)</sup> | ADIF                         | RCIF   | TXIF  | SSPIF | CCP1IF | TMR2IF | TMR1IF | 0000 0000             | 0000 0000                       |

| 18h                    | RCSTA  | SPEN                 | RX9                          | SREN   | CREN  | ADDEN | FERR   | OERR   | RX9D   | 0000 000x             | 0000 000x                       |

| 1Ah                    | RCREG  | USART Red            | ceive Reg                    | gister |       |       |        |        |        | 0000 0000             | 0000 0000                       |

| 8Ch                    | PIE1   | PSPIE <sup>(1)</sup> | ADIE                         | RCIE   | TXIE  | SSPIE | CCP1IE | TMR2IE | TMR1IE | 0000 0000             | 0000 0000                       |

| 98h                    | TXSTA  | CSRC                 | TX9                          | TXEN   | SYNC  | —     | BRGH   | TRMT   | TX9D   | 0000 -010             | 0000 -010                       |

| 99h                    | SPBRG  | Baud Rate            | Baud Rate Generator Register |        |       |       |        |        |        |                       | 0000 0000                       |

Legend: x = unknown, - = unimplemented locations read as '0'. Shaded cells are not used for asynchronous reception.

Note 1: Bits PSPIE and PSPIF are reserved on 28-pin devices; always maintain these bits clear.

#### 10.3.2 USART SYNCHRONOUS MASTER RECEPTION

Once Synchronous mode is selected, reception is enabled by setting either enable bit, SREN (RCSTA<5>), or enable bit, CREN (RCSTA<4>). Data is sampled on the RC7/RX/DT pin on the falling edge of the clock. If enable bit SREN is set, then only a single word is received. If enable bit CREN is set, the reception is continuous until CREN is cleared. If both bits are set, CREN takes precedence. After clocking the last bit, the received data in the Receive Shift Register (RSR) is transferred to the RCREG register (if it is empty). When the transfer is complete, interrupt flag bit, RCIF (PIR1<5>), is set. The actual interrupt can be enabled/ disabled by setting/clearing enable bit, RCIE (PIE1<5>). Flag bit RCIF is a read-only bit which is reset by the hardware. In this case, it is reset when the RCREG register has been read and is empty. The RCREG is a double-buffered register (i.e., it is a twodeep FIFO). It is possible for two bytes of data to be received and transferred to the RCREG FIFO and a third byte to begin shifting into the RSR register. On the clocking of the last bit of the third byte, if the RCREG register is still full, then Overrun Error bit, OERR (RCSTA<1>), is set. The word in the RSR will be lost. The RCREG register can be read twice to retrieve the two bytes in the FIFO. Bit OERR has to be cleared in software (by clearing bit CREN). If bit OERR is set, transfers from the RSR to the RCREG are inhibited so it is essential to clear bit OERR if it is set. The ninth receive bit is buffered the same way as the receive

data. Reading the RCREG register will load bit RX9D with a new value, therefore, it is essential for the user to read the RCSTA register before reading RCREG in order not to lose the old RX9D information.

When setting up a Synchronous Master Reception:

- 1. Initialize the SPBRG register for the appropriate baud rate (Section 10.1 "USART Baud Rate Generator (BRG)").

- 2. Enable the synchronous master serial port by setting bits SYNC, SPEN and CSRC.

- 3. Ensure bits CREN and SREN are clear.

- 4. If interrupts are desired, then set enable bit RCIE.

- 5. If 9-bit reception is desired, then set bit RX9.

- 6. If a single reception is required, set bit SREN. For continuous reception, set bit CREN.

- Interrupt flag bit RCIF will be set when reception is complete and an interrupt will be generated if enable bit RCIE was set.

- 8. Read the RCSTA register to get the ninth bit (if enabled) and determine if any error occurred during reception.

- 9. Read the 8-bit received data by reading the RCREG register.

- 10. If any error occurred, clear the error by clearing bit CREN.

- 11. If using interrupts, ensure that GIE and PEIE (bits 7 and 6) of the INTCON register are set.

| TABLE 10-9. REGISTERS ASSOCIATED WITTSTRETIKOROOS MASTER RECEPTION |                                                           |                                                                                                     |                                                                                                          |                                                                                                                                                                                                  |                                                                                                                                                                                              |                                                                                                                                                                                                                                                             |                                                                                                                                                                                                                                                      |                                                                                                                                                                                                                                                                               |                                                                                                                                                                                                                                                                                                            |                                                                                                                                                                                                                                                                                                                                                                                                        |  |

|--------------------------------------------------------------------|-----------------------------------------------------------|-----------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Name                                                               | Bit 7                                                     | Bit 6                                                                                               | Bit 5                                                                                                    | Bit 4                                                                                                                                                                                            | Bit 3                                                                                                                                                                                        | Bit 2                                                                                                                                                                                                                                                       | Bit 1                                                                                                                                                                                                                                                | Bit 0                                                                                                                                                                                                                                                                         | Value on:<br>POR, BOR                                                                                                                                                                                                                                                                                      | Value on<br>all other<br>Resets                                                                                                                                                                                                                                                                                                                                                                        |  |

| INTCON                                                             | GIE                                                       | PEIE                                                                                                | TMR0IE                                                                                                   | INTE                                                                                                                                                                                             | RBIE                                                                                                                                                                                         | TMR0IF                                                                                                                                                                                                                                                      | INTF                                                                                                                                                                                                                                                 | R0IF                                                                                                                                                                                                                                                                          | 0000 000x                                                                                                                                                                                                                                                                                                  | 0000 000u                                                                                                                                                                                                                                                                                                                                                                                              |  |

| PIR1                                                               | PSPIF <sup>(1)</sup>                                      | ADIF                                                                                                | RCIF                                                                                                     | TXIF                                                                                                                                                                                             | SSPIF                                                                                                                                                                                        | CCP1IF                                                                                                                                                                                                                                                      | TMR2IF                                                                                                                                                                                                                                               | TMR1IF                                                                                                                                                                                                                                                                        | 0000 0000                                                                                                                                                                                                                                                                                                  | 0000 0000                                                                                                                                                                                                                                                                                                                                                                                              |  |

| RCSTA                                                              | SPEN                                                      | RX9                                                                                                 | SREN                                                                                                     | CREN                                                                                                                                                                                             |                                                                                                                                                                                              | FERR                                                                                                                                                                                                                                                        | OERR                                                                                                                                                                                                                                                 | RX9D                                                                                                                                                                                                                                                                          | 0000 -00x                                                                                                                                                                                                                                                                                                  | 0000 -00x                                                                                                                                                                                                                                                                                                                                                                                              |  |

| RCREG                                                              | USART Re                                                  | eceive Re                                                                                           | gister                                                                                                   |                                                                                                                                                                                                  |                                                                                                                                                                                              |                                                                                                                                                                                                                                                             |                                                                                                                                                                                                                                                      |                                                                                                                                                                                                                                                                               | 0000 0000                                                                                                                                                                                                                                                                                                  | 0000 0000                                                                                                                                                                                                                                                                                                                                                                                              |  |

| PIE1                                                               | PSPIE <sup>(1)</sup>                                      | ADIE                                                                                                | RCIE                                                                                                     | TXIE                                                                                                                                                                                             | SSPIE                                                                                                                                                                                        | CCP1IE                                                                                                                                                                                                                                                      | TMR2IE                                                                                                                                                                                                                                               | TMR1IE                                                                                                                                                                                                                                                                        | 0000 0000                                                                                                                                                                                                                                                                                                  | 0000 0000                                                                                                                                                                                                                                                                                                                                                                                              |  |

| TXSTA                                                              | CSRC                                                      | TX9                                                                                                 | TXEN                                                                                                     | SYNC                                                                                                                                                                                             |                                                                                                                                                                                              | BRGH                                                                                                                                                                                                                                                        | TRMT                                                                                                                                                                                                                                                 | TX9D                                                                                                                                                                                                                                                                          | 0000 -010                                                                                                                                                                                                                                                                                                  | 0000 -010                                                                                                                                                                                                                                                                                                                                                                                              |  |

| SPBRG                                                              | Baud Rate                                                 | Baud Rate Generator Register                                                                        |                                                                                                          |                                                                                                                                                                                                  |                                                                                                                                                                                              |                                                                                                                                                                                                                                                             |                                                                                                                                                                                                                                                      |                                                                                                                                                                                                                                                                               |                                                                                                                                                                                                                                                                                                            | 0000 0000                                                                                                                                                                                                                                                                                                                                                                                              |  |

|                                                                    | Name<br>INTCON<br>PIR1<br>RCSTA<br>RCREG<br>PIE1<br>TXSTA | NameBit 7INTCONGIEPIR1PSPIF <sup>(1)</sup> RCSTASPENRCREGUSART RePIE1PSPIE <sup>(1)</sup> TXSTACSRC | NameBit 7Bit 6INTCONGIEPEIEPIR1PSPIF(1)ADIFRCSTASPENRX9RCREGUSART Receive RePIE1PSPIE(1)ADIETXSTACSRCTX9 | NameBit 7Bit 6Bit 5INTCONGIEPEIETMR0IEPIR1PSPIF <sup>(1)</sup> ADIFRCIFRCSTASPENRX9SRENRCREGUSART Receive RegisterPIE1PSPIE <sup>(1)</sup> ADIEPIE1PSPIE <sup>(1)</sup> ADIERCIETXSTACSRCTX9TXEN | NameBit 7Bit 6Bit 5Bit 4INTCONGIEPEIETMROIEINTEPIR1PSPIF <sup>(1)</sup> ADIFRCIFTXIFRCSTASPENRX9SRENCRENRCREGUSART Receive RegisterFIE1PSPIE <sup>(1)</sup> ADIERCIETXIETXSTACSRCTX9TXENSYNC | NameBit 7Bit 6Bit 5Bit 4Bit 3INTCONGIEPEIETMROIEINTERBIEPIR1PSPIF <sup>(1)</sup> ADIFRCIFTXIFSSPIFRCSTASPENRX9SRENCREN—RCREGUSART Receive RegisterFIE1PSPIE <sup>(1)</sup> ADIERCIETXIESSPIEPIE1PSPIE <sup>(1)</sup> ADIERCIETXIESSPIETXSTACSRCTX9TXENSYNC— | NameBit 7Bit 6Bit 5Bit 4Bit 3Bit 2INTCONGIEPEIETMR0IEINTERBIETMR0IFPIR1PSPIF <sup>(1)</sup> ADIFRCIFTXIFSSPIFCCP1IFRCSTASPENRX9SRENCREN—FERRRCREGUSART Receive RegisterFFFFPIE1PSPIE <sup>(1)</sup> ADIERCIETXIESSPIECCP1IETXSTACSRCTX9TXENSYNC—BRGH | NameBit 7Bit 6Bit 5Bit 4Bit 3Bit 2Bit 1INTCONGIEPEIETMROIEINTERBIETMROIFINTFPIR1PSPIF <sup>(1)</sup> ADIFRCIFTXIFSSPIFCCP1IFTMR2IFRCSTASPENRX9SRENCREN—FERROERRRCREGUSART Receive RegisterFIE1PSPIE <sup>(1)</sup> ADIERCIETXIESSPIECCP1IETMR2IETXSTACSRCTX9TXENSYNC—BRGHTRMT | NameBit 7Bit 6Bit 5Bit 4Bit 3Bit 2Bit 1Bit 0INTCONGIEPEIETMROIEINTERBIETMROIFINTFROIFPIR1PSPIF <sup>(1)</sup> ADIFRCIFTXIFSSPIFCCP1IFTMR2IFTMR1IFRCSTASPENRX9SRENCREN—FERROERRRX9DRCREGUSART Receive RegisterFIE1PSPIE <sup>(1)</sup> ADIERCIETXIESSPIECCP1IETMR2IETMR1IETXSTACSRCTX9TXENSYNC—BRGHTRMTTX9D | NameBit 7Bit 6Bit 5Bit 4Bit 3Bit 2Bit 1Bit 0Value on:<br>POR, BORINTCONGIEPEIETMROIEINTERBIETMROIFINTFROIF0000000xPIR1PSPIF <sup>(1)</sup> ADIFRCIFTXIFSSPIFCCP1IFTMR2IFTMR1IF00000000RCSTASPENRX9SRENCREN—FERROERRRX9D0000-00xRCREGUSART Receive RegisterSYPIECCP1IETMR2IETMR1IE00000000PIE1PSPIE <sup>(1)</sup> ADIERCIETXIESSPIECCP1IETMR2IETMR1IE00000000TXSTACSRCTX9TXENSYNC—BRGHTRMTTX9D0000-011 |  |

# TABLE 10-9: REGISTERS ASSOCIATED WITH SYNCHRONOUS MASTER RECEPTION

Legend: x = unknown, - = unimplemented, read as '0'. Shaded cells are not used for synchronous master reception.

Note 1: Bits PSPIE and PSPIF are reserved on 28-pin devices; always maintain these bits clear.

# REGISTER 11-2: ADCON1 REGISTER (ADDRESS 9Fh)

| R/W-0 | R/W-0 | U-0 | U-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 |

|-------|-------|-----|-----|-------|-------|-------|-------|

| ADFM  | ADCS2 | —   | —   | PCFG3 | PCFG2 | PCFG1 | PCFG0 |

| bit 7 |       |     |     |       |       |       | bit 0 |

bit 7 ADFM: A/D Result Format Select bit

1 = Right justified. Six (6) Most Significant bits of ADRESH are read as '0'.

0 = Left justified. Six (6) Least Significant bits of ADRESL are read as '0'.

bit 6 ADCS2: A/D Conversion Clock Select bit (ADCON1 bits in shaded area and in bold)

| ADCON1<br><adcs2></adcs2> | ADCON0<br><adcs1:adcs0></adcs1:adcs0> | Clock Conversion                                        |

|---------------------------|---------------------------------------|---------------------------------------------------------|

| 0                         | 00                                    | Fosc/2                                                  |

| 0                         | 01                                    | Fosc/8                                                  |

| 0                         | 10                                    | Fosc/32                                                 |

| 0                         | 11                                    | FRC (clock derived from the internal A/D RC oscillator) |

| 1                         | 00                                    | Fosc/4                                                  |

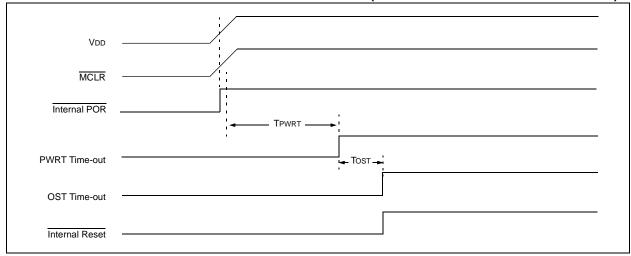

| 1                         | 01                                    | Fosc/16                                                 |