Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

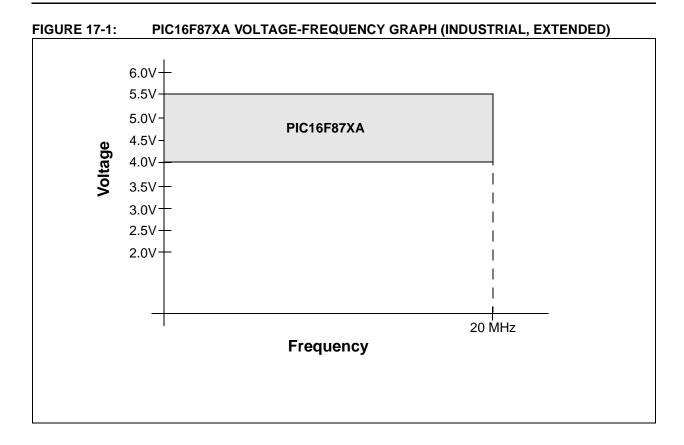

| Product Status             | Active                                                                     |

|----------------------------|----------------------------------------------------------------------------|

| Core Processor             | PIC                                                                        |

| Core Size                  | 8-Bit                                                                      |

| Speed                      | 20MHz                                                                      |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                          |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                      |

| Number of I/O              | 33                                                                         |

| Program Memory Size        | 7KB (4K x 14)                                                              |

| Program Memory Type        | FLASH                                                                      |

| EEPROM Size                | 128 x 8                                                                    |

| RAM Size                   | 192 x 8                                                                    |

| Voltage - Supply (Vcc/Vdd) | 4V ~ 5.5V                                                                  |

| Data Converters            | A/D 8x10b                                                                  |

| Oscillator Type            | External                                                                   |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                         |

| Mounting Type              | Surface Mount                                                              |

| Package / Case             | 44-TQFP                                                                    |

| Supplier Device Package    | 44-TQFP (10x10)                                                            |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16f874at-e-pt |

|                            |                                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

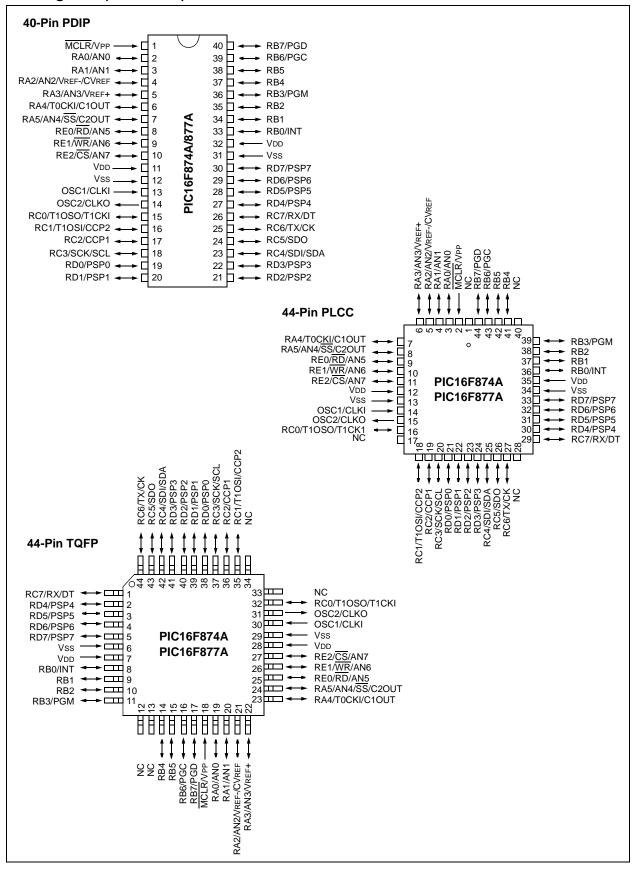

## **Pin Diagrams (Continued)**

| Pin Name        | PDIP, SOIC,<br>SSOP Pin# | QFN<br>Pin# | I/O/P<br>Type | Buffer<br>Type        | Description                                                                         |

|-----------------|--------------------------|-------------|---------------|-----------------------|-------------------------------------------------------------------------------------|

|                 |                          |             |               |                       | PORTB is a bidirectional I/O port. PORTB can be software                            |

|                 |                          |             |               |                       | programmed for internal weak pull-ups on all inputs.                                |

| RB0/INT         | 21                       | 18          |               | TTL/ST <sup>(1)</sup> |                                                                                     |

| RB0             |                          |             | I/O           |                       | Digital I/O.                                                                        |

| INT             |                          |             | I             |                       | External interrupt.                                                                 |

| RB1             | 22                       | 19          | I/O           | TTL                   | Digital I/O.                                                                        |

| RB2             | 23                       | 20          | I/O           | TTL                   | Digital I/O.                                                                        |

| RB3/PGM         | 24                       | 21          |               | TTL                   |                                                                                     |

| RB3             |                          |             | I/O           |                       | Digital I/O.                                                                        |

| PGM             |                          |             | I             |                       | Low-voltage (single-supply) ICSP programming enable pir                             |

| RB4             | 25                       | 22          | I/O           | TTL                   | Digital I/O.                                                                        |

| RB5             | 26                       | 23          | I/O           | TTL                   | Digital I/O.                                                                        |

| RB6/PGC         | 27                       | 24          |               | TTL/ST <sup>(2)</sup> |                                                                                     |

| RB6             |                          |             | I/O           |                       | Digital I/O.                                                                        |

| PGC             |                          |             | I             |                       | In-circuit debugger and ICSP programming clock.                                     |

| RB7/PGD         | 28                       | 25          |               | TTL/ST <sup>(2)</sup> |                                                                                     |

| RB7             | -                        | -           | I/O           |                       | Digital I/O.                                                                        |

| PGD             |                          |             | I/O           |                       | In-circuit debugger and ICSP programming data.                                      |

|                 |                          |             |               |                       | PORTC is a bidirectional I/O port.                                                  |

| RC0/T1OSO/T1CKI | 11                       | 8           |               | ST                    |                                                                                     |

| RC0             |                          | -           | I/O           |                       | Digital I/O.                                                                        |

| T1OSO           |                          |             | 0             |                       | Timer1 oscillator output.                                                           |

| T1CKI           |                          |             | I             |                       | Timer1 external clock input.                                                        |

| RC1/T1OSI/CCP2  | 12                       | 9           |               | ST                    |                                                                                     |

| RC1             |                          |             | I/O           |                       | Digital I/O.                                                                        |

| T1OSI           |                          |             | 1             |                       | Timer1 oscillator input.                                                            |

| CCP2            |                          |             | I/O           |                       | Capture2 input, Compare2 output, PWM2 output.                                       |

| RC2/CCP1        | 13                       | 10          |               | ST                    |                                                                                     |

| RC2             |                          |             | I/O           |                       | Digital I/O.                                                                        |

| CCP1            |                          |             | I/O           |                       | Capture1 input, Compare1 output, PWM1 output.                                       |

| RC3/SCK/SCL     | 14                       | 11          | 1/0           | ST                    | District VO                                                                         |

| RC3<br>SCK      |                          |             | I/O<br>I/O    |                       | Digital I/O.<br>Synchronous serial clock input/output for SPI mode.                 |

| SCL             |                          |             | 1/O           |                       | Synchronous serial clock input/output for J <sup>2</sup> C mode.                    |

| RC4/SDI/SDA     | 15                       | 12          | ., 0          | ST                    |                                                                                     |

| RC4             | 15                       | 12          | I/O           | 51                    | Digital I/O.                                                                        |

| SDI             |                          |             | ., c          |                       | SPI data in.                                                                        |

| SDA             |                          |             | I/O           |                       | I <sup>2</sup> C data I/O.                                                          |

| RC5/SDO         | 16                       | 13          |               | ST                    |                                                                                     |

| RC5             |                          |             | I/O           |                       | Digital I/O.                                                                        |

| SDO             |                          |             | 0             |                       | SPI data out.                                                                       |

| RC6/TX/CK       | 17                       | 14          |               | ST                    |                                                                                     |

| RC6             |                          |             | I/O           |                       | Digital I/O.                                                                        |

| TX              |                          |             | 0             |                       | USART asynchronous transmit.                                                        |

| CK              |                          |             | I/O           |                       | USART1 synchronous clock.                                                           |

| RC7/RX/DT       | 18                       | 15          |               | ST                    |                                                                                     |

| RC7             |                          |             | I/O           |                       | Digital I/O.                                                                        |

| RX<br>DT        |                          |             | I/O           |                       | USART asynchronous receive.                                                         |

|                 | 0.40                     | <b>F A</b>  |               |                       | USART synchronous data.                                                             |

| Vss             | 8, 19<br>20              | 5,6         | P             |                       | Ground reference for logic and I/O pins.<br>Positive supply for logic and I/O pins. |

| Vdd             |                          | 17          | Р             |                       |                                                                                     |

| TABLE 1-2: PIC16F873A/876A PINOUT DESCRIPTION (CONTINUE |

|---------------------------------------------------------|

|---------------------------------------------------------|

**Note 1:** This buffer is a Schmitt Trigger input when configured as the external interrupt.

2: This buffer is a Schmitt Trigger input when used in Serial Programming mode.

3: This buffer is a Schmitt Trigger input when configured in RC Oscillator mode and a CMOS input otherwise.

| Address              | Name       | Bit 7                | Bit 6         | Bit 5                     | Bit 4          | Bit 3        | Bit 2            | Bit 1         | Bit 0        | Value on:<br>POR, BOR | Details<br>on page |

|----------------------|------------|----------------------|---------------|---------------------------|----------------|--------------|------------------|---------------|--------------|-----------------------|--------------------|

| Bank 1               |            |                      |               |                           |                |              |                  |               |              |                       |                    |

| 80h <sup>(3)</sup>   | INDF       | Addressing           | this locatio  | n uses cont               | ents of FSR t  | o address d  | ata memory (     | not a physic  | al register) | 0000 0000             | 31, 150            |

| 81h                  | OPTION_REG | RBPU                 | INTEDG        | TOCS                      | T0SE           | PSA          | PS2              | PS1           | PS0          | 1111 1111             | 23, 150            |

| 82h <sup>(3)</sup>   | PCL        | Program C            | ounter (PC)   | Least Sign                | ificant Byte   |              |                  |               |              | 0000 0000             | 30, 150            |

| 83h <sup>(3)</sup>   | STATUS     | IRP                  | RP1           | RP0                       | TO             | PD           | Z                | DC            | С            | 0001 1xxx             | 22, 150            |

| 84h <sup>(3)</sup>   | FSR        | Indirect Da          | ta Memory     | Address Po                | inter          |              |                  |               |              | xxxx xxxx             | 31, 150            |

| 85h                  | TRISA      |                      |               | PORTA Da                  | ta Direction F | Register     |                  |               |              | 11 1111               | 43, 150            |

| 86h                  | TRISB      | PORTB Da             | ata Direction | Register                  |                |              |                  |               |              | 1111 1111             | 45, 150            |

| 87h                  | TRISC      | PORTC Da             | ata Directior | Register                  |                |              |                  |               |              | 1111 1111             | 47, 150            |

| 88h <sup>(4)</sup>   | TRISD      | PORTD Da             | ata Directior | n Register                |                |              |                  |               |              | 1111 1111             | 48, 151            |

| 89h <sup>(4)</sup>   | TRISE      | IBF                  | OBF           | IBOV                      | PSPMODE        |              | PORTE Dat        | a Direction I | bits         | 0000 -111             | 50, 151            |

| 8Ah <sup>(1,3)</sup> | PCLATH     | —                    |               |                           | Write Buffer   | for the uppe | er 5 bits of the | e Program C   | Counter      | 0 0000                | 30, 150            |

| 8Bh <sup>(3)</sup>   | INTCON     | GIE                  | PEIE          | TMR0IE                    | INTE           | RBIE         | TMR0IF           | INTF          | RBIF         | 0000 000x             | 24, 150            |

| 8Ch                  | PIE1       | PSPIE <sup>(2)</sup> | ADIE          | RCIE                      | TXIE           | SSPIE        | CCP1IE           | TMR2IE        | TMR1IE       | 0000 0000             | 25, 151            |

| 8Dh                  | PIE2       | —                    | CMIE          |                           | EEIE           | BCLIE        | —                | _             | CCP2IE       | -0-0 00               | 27, 151            |

| 8Eh                  | PCON       | _                    |               |                           | _              |              | _                | POR           | BOR          | dd                    | 29, 151            |

| 8Fh                  | _          | Unimpleme            | Unimplemented |                           |                |              |                  |               |              |                       |                    |

| 90h                  | —          | Unimpleme            | ented         |                           |                |              |                  |               |              | _                     | _                  |

| 91h                  | SSPCON2    | GCEN                 | ACKSTAT       | ACKDT                     | ACKEN          | RCEN         | PEN              | RSEN          | SEN          | 0000 0000             | 83, 151            |

| 92h                  | PR2        | Timer2 Per           | riod Registe  | r                         |                |              |                  |               |              | 1111 1111             | 62, 151            |

| 93h                  | SSPADD     | Synchrono            | us Serial Po  | ort (I <sup>2</sup> C mod | e) Address R   | egister      |                  |               |              | 0000 0000             | 79, 151            |

| 94h                  | SSPSTAT    | SMP                  | CKE           | D/A                       | Р              | S            | R/W              | UA            | BF           | 0000 0000             | 79, 151            |

| 95h                  | —          | Unimpleme            | ented         |                           | •              |              |                  |               |              | —                     |                    |

| 96h                  | _          | Unimpleme            | ented         |                           |                |              |                  |               |              | —                     |                    |

| 97h                  | —          | Unimpleme            | ented         |                           |                |              |                  |               |              | —                     |                    |

| 98h                  | TXSTA      | CSRC                 | TX9           | TXEN                      | SYNC           | _            | BRGH             | TRMT          | TX9D         | 0000 -010             | 111, 151           |

| 99h                  | SPBRG      | Baud Rate            | Generator     | Register                  | •              |              |                  |               |              | 0000 0000             | 113, 151           |

| 9Ah                  | —          | Unimpleme            | Unimplemented |                           |                |              |                  |               |              |                       | _                  |

| 9Bh                  | _          | Unimpleme            | ented         |                           |                |              |                  |               |              | _                     | —                  |

| 9Ch                  | CMCON      | C2OUT                | C1OUT         | C2INV                     | C1INV          | CIS          | CM2              | CM1           | CM0          | 0000 0111             | 135, 151           |

| 9Dh                  | CVRCON     | CVREN                | CVROE         | CVRR                      | _              | CVR3         | CVR2             | CVR1          | CVR0         | 000- 0000             | 141, 151           |

| 9Eh                  | ADRESL     | A/D Result           | Register Lo   | w Byte                    |                |              |                  |               |              | xxxx xxxx             | 133, 151           |

| 9Fh                  | ADCON1     | ADFM                 | ADCS2         | _                         | _              | PCFG3        | PCFG2            | PCFG1         | PCFG0        | 00 0000               | 128, 151           |

####

x = unknown, u = unchanged, q = value depends on condition, - = unimplemented, read as '0', r = reserved. Legend: Shaded locations are unimplemented, read as '0'.

Note 1: The upper byte of the program counter is not directly accessible. PCLATH is a holding register for the PC<12:8>, whose contents are transferred to the upper byte of the program counter.

2: Bits PSPIE and PSPIF are reserved on PIC16F873A/876A devices; always maintain these bits clear.

3: These registers can be addressed from any bank.

4: PORTD, PORTE, TRISD and TRISE are not implemented on PIC16F873A/876A devices, read as '0'.

5: Bit 4 of EEADRH implemented only on the PIC16F876A/877A devices.

## 3.0 DATA EEPROM AND FLASH PROGRAM MEMORY

The data EEPROM and Flash program memory is readable and writable during normal operation (over the full VDD range). This memory is not directly mapped in the register file space. Instead, it is indirectly addressed through the Special Function Registers. There are six SFRs used to read and write this memory:

- EECON1

- EECON2

- EEDATA

- EEDATH

- EEADR

- EEADRH

When interfacing to the data memory block, EEDATA holds the 8-bit data for read/write and EEADR holds the address of the EEPROM location being accessed. These devices have 128 or 256 bytes of data EEPROM (depending on the device), with an address range from 00h to FFh. On devices with 128 bytes, addresses from 80h to FFh are unimplemented and will wraparound to the beginning of data EEPROM memory. When writing to unimplemented locations, the on-chip charge pump will be turned off.

When interfacing the program memory block, the EEDATA and EEDATH registers form a two-byte word that holds the 14-bit data for read/write and the EEADR and EEADRH registers form a two-byte word that holds the 13-bit address of the program memory location being accessed. These devices have 4 or 8K words of program Flash, with an address range from 0000h to 0FFFh for the PIC16F873A/874A and 0000h to 1FFFh for the PIC16F876A/877A. Addresses above the range of the respective device will wraparound to the beginning of program memory.

The EEPROM data memory allows single-byte read and write. The Flash program memory allows single-word reads and four-word block writes. Program memory write operations automatically perform an erase-before-write on blocks of four words. A byte write in data EEPROM memory automatically erases the location and writes the new data (erase-before-write).

The write time is controlled by an on-chip timer. The write/erase voltages are generated by an on-chip charge pump, rated to operate over the voltage range of the device for byte or word operations.

When the device is code-protected, the CPU may continue to read and write the data EEPROM memory. Depending on the settings of the write-protect bits, the device may or may not be able to write certain blocks of the program memory; however, reads of the program memory are allowed. When code-protected, the device programmer can no longer access data or program memory; this does NOT inhibit internal reads or writes.

## 3.1 EEADR and EEADRH

The EEADRH:EEADR register pair can address up to a maximum of 256 bytes of data EEPROM or up to a maximum of 8K words of program EEPROM. When selecting a data address value, only the LSByte of the address is written to the EEADR register. When selecting a program address value, the MSByte of the address is written to the EEADRH register and the LSByte is written to the EEADR register.

If the device contains less memory than the full address reach of the address register pair, the Most Significant bits of the registers are not implemented. For example, if the device has 128 bytes of data EEPROM, the Most Significant bit of EEADR is not implemented on access to data EEPROM.

## 3.2 EECON1 and EECON2 Registers

EECON1 is the control register for memory accesses.

Control bit, EEPGD, determines if the access will be a program or data memory access. When clear, as it is when reset, any subsequent operations will operate on the data memory. When set, any subsequent operations will operate on the program memory.

Control bits, RD and WR, initiate read and write or erase, respectively. These bits cannot be cleared, only set, in software. They are cleared in hardware at completion of the read or write operation. The inability to clear the WR bit in software prevents the accidental, premature termination of a write operation.

The WREN bit, when set, will allow a write or erase operation. On power-up, the WREN bit is clear. The WRERR bit is set when a write (or erase) operation is interrupted by a  $\overline{\text{MCLR}}$  or a WDT Time-out Reset during normal operation. In these situations, following Reset, the user can check the WRERR bit and rewrite the location. The data and address will be unchanged in the EEDATA and EEADR registers.

Interrupt flag bit, EEIF in the PIR2 register, is set when the write is complete. It must be cleared in software.

EECON2 is not a physical register. Reading EECON2 will read all '0's. The EECON2 register is used exclusively in the EEPROM write sequence.

Note: The self-programming mechanism for Flash program memory has been changed. On previous PIC16F87X devices, Flash programming was done in single-word erase/ write cycles. The newer PIC18F87XA devices use a four-word erase/write cycle. See Section 3.6 "Writing to Flash Program Memory" for more information.

| Name            | Bit#  | Buffer Type | Function                                                                                            |

|-----------------|-------|-------------|-----------------------------------------------------------------------------------------------------|

| RC0/T1OSO/T1CKI | bit 0 | ST          | Input/output port pin or Timer1 oscillator output/Timer1 clock input.                               |

| RC1/T1OSI/CCP2  | bit 1 | ST          | Input/output port pin or Timer1 oscillator input or Capture2 input/<br>Compare2 output/PWM2 output. |

| RC2/CCP1        | bit 2 | ST          | Input/output port pin or Capture1 input/Compare1 output/<br>PWM1 output.                            |

| RC3/SCK/SCL     | bit 3 | ST          | RC3 can also be the synchronous serial clock for both SPI and I <sup>2</sup> C modes.               |

| RC4/SDI/SDA     | bit 4 | ST          | RC4 can also be the SPI data in (SPI mode) or data I/O (I <sup>2</sup> C mode).                     |

| RC5/SDO         | bit 5 | ST          | Input/output port pin or Synchronous Serial Port data output.                                       |

| RC6/TX/CK       | bit 6 | ST          | Input/output port pin or USART asynchronous transmit or<br>synchronous clock.                       |

| RC7/RX/DT       | bit 7 | ST          | Input/output port pin or USART asynchronous receive or synchronous data.                            |

## TABLE 4-5:PORTC FUNCTIONS

**Legend:** ST = Schmitt Trigger input

## TABLE 4-6: SUMMARY OF REGISTERS ASSOCIATED WITH PORTC

| Address | Name  | Bit 7 | Bit 6                         | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 | Value on:<br>POR, BOR | Value on<br>all other<br>Resets |

|---------|-------|-------|-------------------------------|-------|-------|-------|-------|-------|-------|-----------------------|---------------------------------|

| 07h     | PORTC | RC7   | RC6                           | RC5   | RC4   | RC3   | RC2   | RC1   | RC0   | xxxx xxxx             | uuuu uuuu                       |

| 87h     | TRISC | PORTC | PORTC Data Direction Register |       |       |       |       |       |       | 1111 1111             | 1111 1111                       |

**Legend:** x = unknown, u = unchanged

## 4.4 PORTD and TRISD Registers

| Note: | PORTD and TRISD are not implemented |

|-------|-------------------------------------|

|       | on the 28-pin devices.              |

PORTD is an 8-bit port with Schmitt Trigger input buffers. Each pin is individually configurable as an input or output.

PORTD can be configured as an 8-bit wide microprocessor port (Parallel Slave Port) by setting control bit, PSPMODE (TRISE<4>). In this mode, the input buffers are TTL.

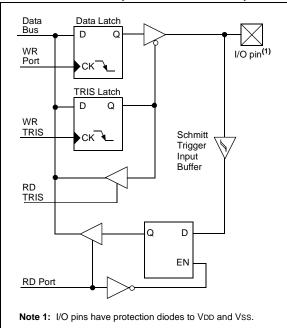

#### FIGURE 4-8: PORTD BLOCK DIAGRAM (IN I/O PORT MODE)

| Name     | Bit#  | Buffer Type           | Function                                            |

|----------|-------|-----------------------|-----------------------------------------------------|

| RD0/PSP0 | bit 0 | ST/TTL <sup>(1)</sup> | Input/output port pin or Parallel Slave Port bit 0. |

| RD1/PSP1 | bit 1 | ST/TTL <sup>(1)</sup> | Input/output port pin or Parallel Slave Port bit 1. |

| RD2/PSP2 | bit2  | ST/TTL <sup>(1)</sup> | Input/output port pin or Parallel Slave Port bit 2. |

| RD3/PSP3 | bit 3 | ST/TTL <sup>(1)</sup> | Input/output port pin or Parallel Slave Port bit 3. |

| RD4/PSP4 | bit 4 | ST/TTL <sup>(1)</sup> | Input/output port pin or Parallel Slave Port bit 4. |

| RD5/PSP5 | bit 5 | ST/TTL <sup>(1)</sup> | Input/output port pin or Parallel Slave Port bit 5. |

| RD6/PSP6 | bit 6 | ST/TTL <sup>(1)</sup> | Input/output port pin or Parallel Slave Port bit 6. |

| RD7/PSP7 | bit 7 | ST/TTL <sup>(1)</sup> | Input/output port pin or Parallel Slave Port bit 7. |

## TABLE 4-7:PORTD FUNCTIONS

Legend: ST = Schmitt Trigger input, TTL = TTL input

Note 1: Input buffers are Schmitt Triggers when in I/O mode and TTL buffers when in Parallel Slave Port mode.

| TABLE 4-8: SUMMARY OF REGISTERS ASSOCIATED WITH PORT |

|------------------------------------------------------|

|------------------------------------------------------|

| Address | Name  | Bit 7 | Bit 6                         | Bit 5 | Bit 4   | Bit 3 | Bit 2   | Bit 1     | Bit 0      |      | e on:<br>BOR | Valu<br>all o<br>Res |      |

|---------|-------|-------|-------------------------------|-------|---------|-------|---------|-----------|------------|------|--------------|----------------------|------|

| 08h     | PORTD | RD7   | RD6                           | RD5   | RD4     | RD3   | RD2     | RD1       | RD0        | xxxx | xxxx         | uuuu                 | uuuu |

| 88h     | TRISD | PORTI | PORTD Data Direction Register |       |         |       |         |           |            | 1111 | 1111         | 1111                 | 1111 |

| 89h     | TRISE | IBF   | OBF                           | IBOV  | PSPMODE |       | PORTE I | Data Dire | ction Bits | 0000 | -111         | 0000                 | -111 |

Legend: x = unknown, u = unchanged, - = unimplemented, read as '0'. Shaded cells are not used by PORTD.

### 9.3.1 REGISTERS

The MSSP module has four registers for SPI mode operation. These are:

- MSSP Control Register (SSPCON)

- MSSP Status Register (SSPSTAT)

- Serial Receive/Transmit Buffer Register (SSPBUF)

- MSSP Shift Register (SSPSR) Not directly accessible

SSPCON and SSPSTAT are the control and status registers in SPI mode operation. The SSPCON register is readable and writable. The lower six bits of the SSPSTAT are read-only. The upper two bits of the SSPSTAT are read/write. SSPSR is the shift register used for shifting data in or out. SSPBUF is the buffer register to which data bytes are written to or read from.

In receive operations, SSPSR and SSPBUF together create a double-buffered receiver. When SSPSR receives a complete byte, it is transferred to SSPBUF and the SSPIF interrupt is set.

During transmission, the SSPBUF is not doublebuffered. A write to SSPBUF will write to both SSPBUF and SSPSR.

## REGISTER 9-1: SSPSTAT: MSSP STATUS REGISTER (SPI MODE) (ADDRESS 94h)

|       | R/W-0                                                 | R/W-0           | R-0             | R-0          | R-0           | R-0           | R-0          | R-0           |  |  |

|-------|-------------------------------------------------------|-----------------|-----------------|--------------|---------------|---------------|--------------|---------------|--|--|

|       | SMP                                                   | CKE             | D/A             | Р            | S             | R/W           | UA           | BF            |  |  |

|       | bit 7                                                 |                 |                 |              |               |               |              | bit 0         |  |  |

| bit 7 | SMP: Sam                                              | ple bit         |                 |              |               |               |              |               |  |  |

|       | SPI Master                                            |                 |                 |              |               |               |              |               |  |  |

|       |                                                       | ata sampled     |                 |              |               |               |              |               |  |  |

|       |                                                       | ata sampled     | at middle o     | r data outpu | tume          |               |              |               |  |  |

|       | SMP must                                              | be cleared v    | when SPI is     | used in Slav | ve mode       |               |              |               |  |  |

| bit 6 |                                                       | Clock Select    |                 |              | o modo.       |               |              |               |  |  |

|       | 1 = Transm                                            | nit occurs on   | transition fr   | om active to | ldle clock s  | state         |              |               |  |  |

|       | 0 = Transm                                            | nit occurs on   | transition fr   | om Idle to a | ctive clock s | state         |              |               |  |  |

|       | Note:                                                 | Polarity of o   | clock state is  | s set by the | CKP bit (SS   | PCON1<4>      | ).           |               |  |  |

| bit 5 | D/A: Data/                                            | Address bit     |                 |              |               |               |              |               |  |  |

|       | Used in I <sup>2</sup> C                              | c mode only.    |                 |              |               |               |              |               |  |  |

| bit 4 | P: Stop bit                                           |                 |                 |              |               |               |              |               |  |  |

|       | Used in I <sup>2</sup> C                              | mode only.      | This bit is cle | ared when t  | he MSSP me    | odule is disa | bled, SSPEI  | N is cleared. |  |  |

| bit 3 | S: Start bit                                          |                 |                 |              |               |               |              |               |  |  |

|       | Used in I <sup>2</sup> C                              | c mode only.    |                 |              |               |               |              |               |  |  |

| bit 2 | R/W: Read                                             | I/Write bit inf | ormation        |              |               |               |              |               |  |  |

|       | Used in I <sup>2</sup> C                              | c mode only.    |                 |              |               |               |              |               |  |  |

| bit 1 | UA: Update                                            | e Address b     | it              |              |               |               |              |               |  |  |

|       | Used in I <sup>2</sup> C                              | c mode only.    |                 |              |               |               |              |               |  |  |

| bit 0 | <b>BF:</b> Buffer Full Status bit (Receive mode only) |                 |                 |              |               |               |              |               |  |  |

|       | 1 = Receive complete, SSPBUF is full                  |                 |                 |              |               |               |              |               |  |  |

|       | 0 = Receiv                                            | e not comple    | ete, SSPBU      | F is empty   |               |               |              |               |  |  |

|       | Legend:                                               |                 |                 |              |               |               |              |               |  |  |

|       | R = Reada                                             | ble bit         | W = W           | ritable bit  | U = Unim      | plemented     | bit, read as | '0'           |  |  |

|       | - n = Value                                           | at POR          | '1' = B         | it is set    | '0' = Bit i   | s cleared     | x = Bit is ι | Inknown       |  |  |

## 9.3.8 SLEEP OPERATION

In Master mode, all module clocks are halted and the transmission/reception will remain in that state until the device wakes from Sleep. After the device returns to normal mode, the module will continue to transmit/ receive data.

In Slave mode, the SPI Transmit/Receive Shift register operates asynchronously to the device. This allows the device to be placed in Sleep mode and data to be shifted into the SPI Transmit/Receive Shift register. When all 8 bits have been received, the MSSP interrupt flag bit will be set and if enabled, will wake the device from Sleep.

#### 9.3.9 EFFECTS OF A RESET

A Reset disables the MSSP module and terminates the current transfer.

#### 9.3.10 BUS MODE COMPATIBILITY

Table 9-1 shows the compatibility between the standard SPI modes and the states of the CKP and CKE control bits.

#### TABLE 9-1: SPI BUS MODES

| Standard SPI Mode | Control Bits State |     |  |  |  |

|-------------------|--------------------|-----|--|--|--|

| Terminology       | СКР                | CKE |  |  |  |

| 0, 0              | 0                  | 1   |  |  |  |

| 0, 1              | 0                  | 0   |  |  |  |

| 1, 0              | 1                  | 1   |  |  |  |

| 1, 1              | 1                  | 0   |  |  |  |

There is also a SMP bit which controls when the data is sampled.

| Name    | Bit 7                | Bit 6                                                    | Bit 5  | Bit 4  | Bit 3 | Bit 2  | Bit 1  | Bit 0  | Valu<br>POR, | e on<br>BOR | Valu<br>all o<br>Res | ther |

|---------|----------------------|----------------------------------------------------------|--------|--------|-------|--------|--------|--------|--------------|-------------|----------------------|------|

| INTCON  | GIE/<br>GIEH         | PEIE/<br>GIEL                                            | TMR0IE | INTOIE | RBIE  | TMR0IF | INTOIF | RBIF   | 0000         | 000x        | 0000                 | 000u |

| PIR1    | PSPIF <sup>(1)</sup> | ADIF                                                     | RCIF   | TXIF   | SSPIF | CCP1IF | TMR2IF | TMR1IF | 0000         | 0000        | 0000                 | 0000 |

| PIE1    | PSPIE <sup>(1)</sup> | ADIE                                                     | RCIE   | TXIE   | SSPIE | CCP1IE | TMR2IE | TMR1IE | 0000         | 0000        | 0000                 | 0000 |

| TRISC   | PORTC D              | PORTC Data Direction Register                            |        |        |       |        |        | 1111   | 1111         | 1111        | 1111                 |      |

| SSPBUF  | Synchron             | Synchronous Serial Port Receive Buffer/Transmit Register |        |        |       |        |        | xxxx   | xxxx         | uuuu        | uuuu                 |      |

| SSPCON  | WCOL                 | SSPOV                                                    | SSPEN  | CKP    | SSPM3 | SSPM2  | SSPM1  | SSPM0  | 0000         | 0000        | 0000                 | 0000 |

| TRISA   | —                    | PORTA Data Direction Register                            |        |        |       |        |        | 11     | 1111         | 11          | 1111                 |      |

| SSPSTAT | SMP                  | CKE                                                      | D/Ā    | Р      | S     | R/W    | UA     | BF     | 0000         | 0000        | 0000                 | 0000 |

#### TABLE 9-2: REGISTERS ASSOCIATED WITH SPI OPERATION

Legend: x = unknown, u = unchanged, - = unimplemented, read as '0'. Shaded cells are not used by the MSSP in SPI mode.

Note 1: The PSPIF, PSPIE and PSPIP bits are reserved on 28-pin devices; always maintain these bits clear.

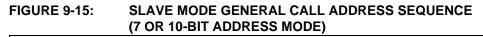

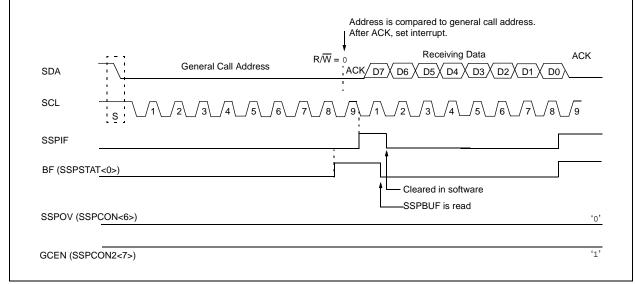

#### 9.4.5 GENERAL CALL ADDRESS SUPPORT

The addressing procedure for the  $I^2C$  bus is such that the first byte after the Start condition usually determines which device will be the slave addressed by the master. The exception is the general call address which can address all devices. When this address is used, all devices should, in theory, respond with an Acknowledge.

The general call address is one of eight addresses reserved for specific purposes by the I<sup>2</sup>C protocol. It consists of all '0's with R/W = 0.

The general call address is recognized when the General Call Enable bit (GCEN) is enabled (SSPCON2<7> set). Following a Start bit detect, 8 bits are shifted into the SSPSR and the address is compared against the SSPADD. It is also compared to the general call address and fixed in hardware.

If the general call address matches, the SSPSR is transferred to the SSPBUF, the BF flag bit is set (eighth bit) and on the falling edge of the ninth bit (ACK bit), the SSPIF interrupt flag bit is set.

When the interrupt is serviced, the source for the interrupt can be checked by reading the contents of the SSPBUF. The value can be used to determine if the address was device specific or a general call address.

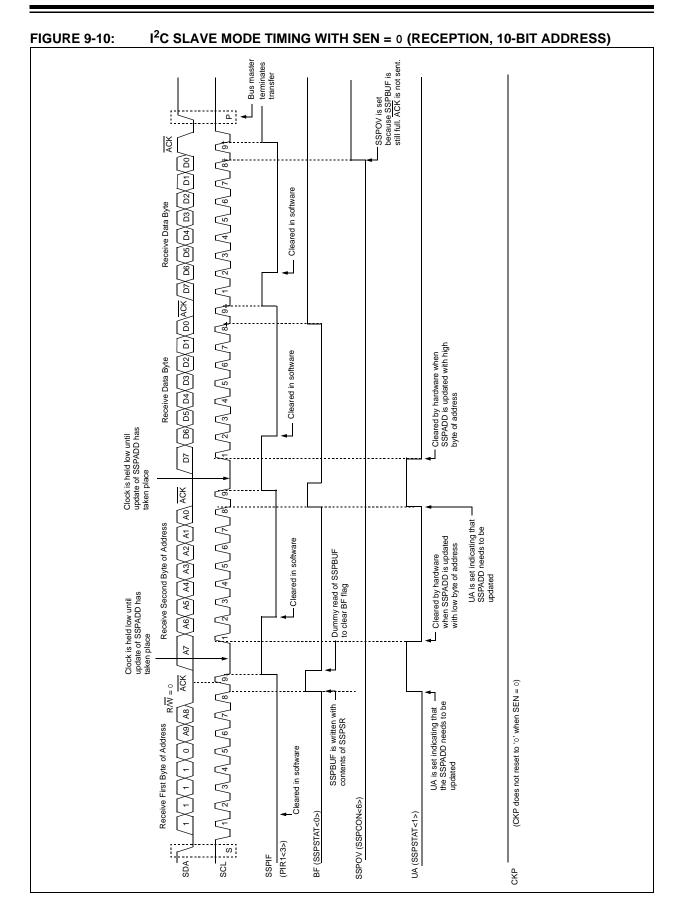

In 10-bit mode, the SSPADD is required to be updated for the second half of the address to match and the UA bit is set (SSPSTAT<1>). If the general call address is sampled when the GCEN bit is set, while the slave is configured in 10-bit Address mode, then the second half of the address is not necessary, the UA bit will not be set and the slave will begin receiving data after the Acknowledge (Figure 9-15).

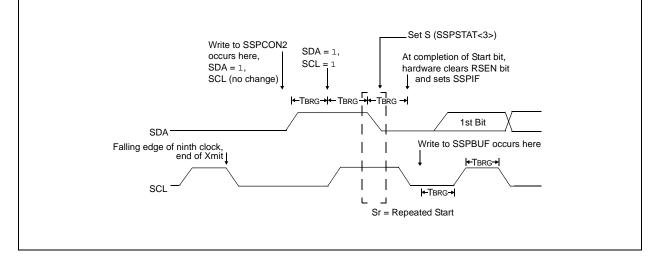

## 9.4.9 I<sup>2</sup>C MASTER MODE REPEATED START CONDITION TIMING

A Repeated Start condition occurs when the RSEN bit (SSPCON2<1>) is programmed high and the I<sup>2</sup>C logic module is in the Idle state. When the RSEN bit is set, the SCL pin is asserted low. When the SCL pin is sampled low, the Baud Rate Generator is loaded with the contents of SSPADD<5:0> and begins counting. The SDA pin is released (brought high) for one Baud Rate Generator count (TBRG). When the Baud Rate Generator times out, if SDA is sampled high, the SCL pin will be deasserted (brought high). When SCL is sampled high, the Baud Rate Generator is reloaded with the contents of SSPADD<6:0> and begins counting. SDA and SCL must be sampled high for one TBRG. This action is then followed by assertion of the SDA pin (SDA = 0) for one TBRG while SCL is high. Following this, the RSEN bit (SSPCON2<1>) will be automatically cleared and the Baud Rate Generator will not be reloaded, leaving the SDA pin held low. As soon as a Start condition is detected on the SDA and SCL pins, the S bit (SSPSTAT<3>) will be set. The SSPIF bit will not be set until the Baud Rate Generator has timed out.

- Note 1: If RSEN is programmed while any other event is in progress, it will not take effect.

- A bus collision during the Repeated Start condition occurs if:

- SDA is sampled low when SCL goes from low to high.

- SCL goes low before SDA is asserted low. This may indicate that another master is attempting to transmit a data '1'.

Immediately following the SSPIF bit getting set, the user may write the SSPBUF with the 7-bit address in 7-bit mode or the default first address in 10-bit mode. After the first eight bits are transmitted and an ACK is received, the user may then transmit an additional eight bits of address (10-bit mode) or eight bits of data (7-bit mode).

### 9.4.9.1 WCOL Status Flag

If the user writes the SSPBUF when a Repeated Start sequence is in progress, the WCOL is set and the contents of the buffer are unchanged (the write doesn't occur).

**Note:** Because queueing of events is not allowed, writing of the lower 5 bits of SSPCON2 is disabled until the Repeated Start condition is complete.

## FIGURE 9-20: REPEAT START CONDITION WAVEFORM

NOTES:

bit 0

## **13.0 COMPARATOR VOLTAGE REFERENCE MODULE**

The Comparator Voltage Reference Generator is a 16-tap resistor ladder network that provides a fixed voltage reference when the comparators are in mode '110'. A programmable register controls the function of the reference generator. Register 13-1 lists the bit functions of the CVRCON register.

As shown in Figure 13-1, the resistor ladder is segmented to provide two ranges of CVREF values and has a power-down function to conserve power when the reference is not being used. The comparator reference supply voltage (also referred to as CVRSRC) comes directly from VDD. It should be noted, however, that the voltage at the top of the ladder is CVRSRC - VSAT, where VSAT is the saturation voltage of the power switch transistor. This reference will only be as accurate as the values of CVRSRC and VSAT.

The output of the reference generator may be connected to the RA2/AN2/VREF-/CVREF pin. This can be used as a simple D/A function by the user if a very highimpedance load is used. The primary purpose of this function is to provide a test path for testing the reference generator function.

|   |      | R/W-0     | R/W-0        | R/W-0       | U-0         | R/W-0 | R/W-0 | R/W-0 | R/W-0 |

|---|------|-----------|--------------|-------------|-------------|-------|-------|-------|-------|

|   |      | CVREN     | CVROE        | CVRR        | —           | CVR3  | CVR2  | CVR1  | CVR0  |

|   |      | bit 7     |              |             |             |       |       |       | bit ( |

|   |      |           |              |             |             |       |       |       |       |

| b | it 7 | CVREN: Co | omparator V  | oltage Refe | rence Enabl | e bit |       |       |       |

|   |      | 1 = CVREF | circuit powe | ered on     |             |       |       |       |       |

## REGISTER 13-1: CVRCON CONTROL REGISTER (ADDRESS 9Dh)

|         | 1 = CVREF circuit powered on<br>0 = CVREF circuit powered down                                        |

|---------|-------------------------------------------------------------------------------------------------------|

|         |                                                                                                       |

| bit 6   | CVROE: Comparator VREF Output Enable bit                                                              |

|         | 1 = CVREF voltage level is output on RA2/AN2/VREF-/CVREF pin                                          |

|         | 0 = CVREF voltage level is disconnected from RA2/AN2/VREF-/CVREF pin                                  |

| bit 5   | CVRR: Comparator VREF Range Selection bit                                                             |

|         | 1 = 0 to 0.75 CVRSRC, with CVRSRC/24 step size                                                        |

|         | 0 = 0.25 CVRSRC to 0.75 CVRSRC, with CVRSRC/32 step size                                              |

| bit 4   | Unimplemented: Read as '0'                                                                            |

| bit 3-0 | <b>CVR3:CVR0:</b> Comparator VREF Value Selection bits $0 \le VR3:VR0 \le 15$                         |

|         | When CVRR = 1:                                                                                        |

|         | $\overline{\text{CVREF}} = (\text{VR} < 3:0 > / 24) \bullet (\text{CVRSRC})$                          |

|         | When CVRR = 0:                                                                                        |

|         | $\overline{\text{CVREF}} = 1/4 \bullet (\text{CVRSRC}) + (\text{VR3:VR0/32}) \bullet (\text{CVRSRC})$ |

|         |                                                                                                       |

|         |                                                                                                       |

| Legend:           |                  |                      |                    |

|-------------------|------------------|----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented    | bit, read as '0'   |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared | x = Bit is unknown |

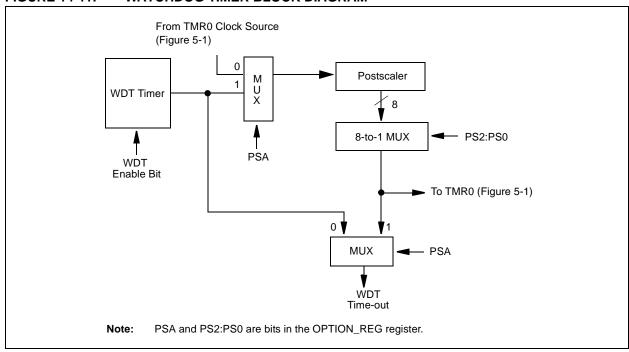

## 14.13 Watchdog Timer (WDT)

The Watchdog Timer is a free running, on-chip RC oscillator which does not require any external components. This RC oscillator is separate from the RC oscillator of the OSC1/CLKI pin. That means that the WDT will run even if the clock on the OSC1/CLKI and OSC2/CLKO pins of the device has been stopped, for example, by execution of a SLEEP instruction.

During normal operation, a WDT time-out generates a device Reset (Watchdog Timer Reset). If the device is in Sleep mode, a WDT time-out causes the device to wake-up and continue with normal operation (Watchdog Timer Wake-up). The TO bit in the Status register will be cleared upon a Watchdog Timer time-out.

The WDT can be permanently disabled by clearing configuration bit, WDTE (Section 14.1 "Configuration Bits").

WDT time-out period values may be found in **Section 17.0** "**Electrical Characteristics**" under parameter #31. Values for the WDT prescaler (actually a postscaler but shared with the Timer0 prescaler) may be assigned using the OPTION\_REG register.

- **Note 1:** The CLRWDT and SLEEP instructions clear the WDT and the postscaler, if assigned to the WDT and prevent it from timing out and generating a device Reset condition.

- 2: When a CLRWDT instruction is executed and the prescaler is assigned to the WDT, the prescaler count will be cleared but the prescaler assignment is not changed.

## FIGURE 14-11: WATCHDOG TIMER BLOCK DIAGRAM

#### TABLE 14-7: SUMMARY OF WATCHDOG TIMER REGISTERS

| Address   | Name         | Bit 7 | Bit 6                | Bit 5 | Bit 4 | Bit 3                | Bit 2 | Bit 1 | Bit 0 |

|-----------|--------------|-------|----------------------|-------|-------|----------------------|-------|-------|-------|

| 2007h     | Config. bits | (1)   | BODEN <sup>(1)</sup> | CP1   | CP0   | PWRTE <sup>(1)</sup> | WDTE  | Fosc1 | Fosc0 |

| 81h, 181h | OPTION_REG   | RBPU  | INTEDG               | TOCS  | TOSE  | PSA                  | PS2   | PS1   | PS0   |

Legend: Shaded cells are not used by the Watchdog Timer.

Note 1: See Register 14-1 for operation of these bits.

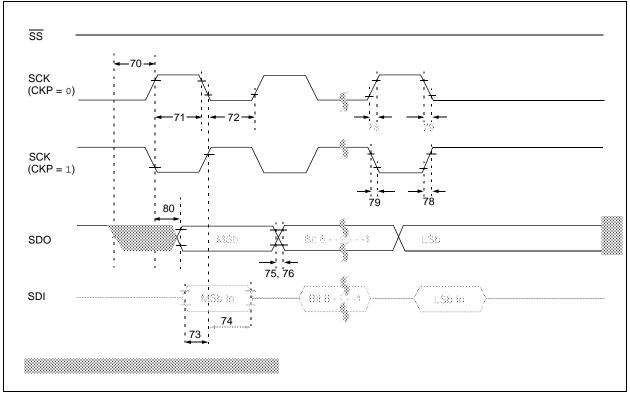

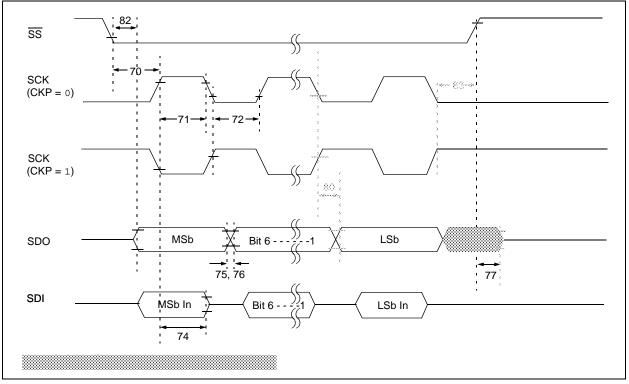

## FIGURE 17-11: SPI MASTER MODE TIMING (CKE = 0, SMP = 0)

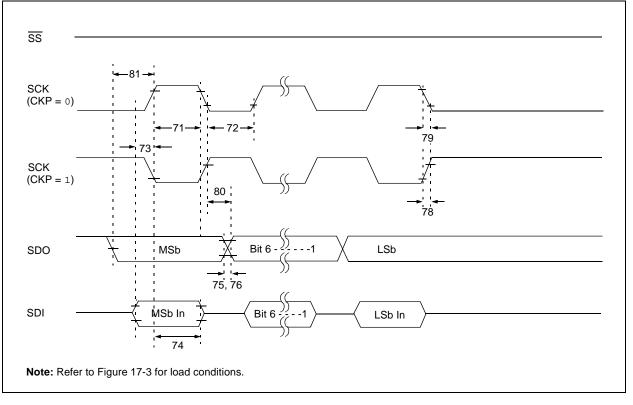

## FIGURE 17-12: SPI MASTER MODE TIMING (CKE = 1, SMP = 1)

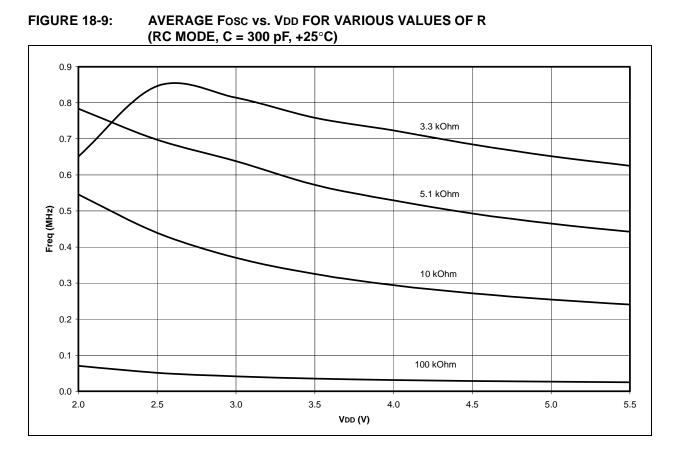

100 Max (125°C) 10 Max (85°C) 1 IPD (NA) 0.1 0.01 Тур (25°С) Typical: statistical mean @ 25°C **Maximum:** mean +  $3\sigma$  (-40°C to +125°C) **Minimum:** mean -  $3\sigma$  (-40°C to +125°C) 0.001 2.0 2.5 3.0 3.5 4.0 4.5 5.0 5.5 VDD (V)

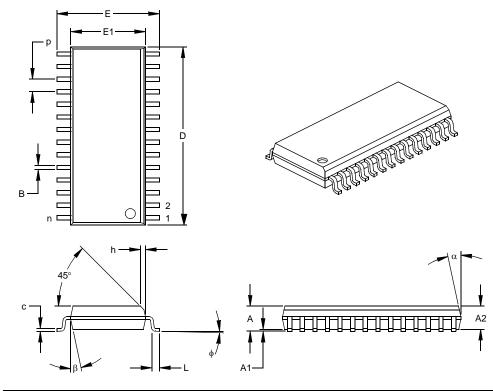

## 28-Lead Plastic Small Outline (SO) – Wide, 300 mil (SOIC)

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

|                          | Units       |      | INCHES* |      | MILLIMETERS |       |       |  |

|--------------------------|-------------|------|---------|------|-------------|-------|-------|--|

| Dimens                   | sion Limits | MIN  | NOM     | MAX  | MIN         | NOM   | MAX   |  |

| Number of Pins           | n           |      | 28      |      |             | 28    |       |  |

| Pitch                    | р           |      | .050    |      |             | 1.27  |       |  |

| Overall Height           | А           | .093 | .099    | .104 | 2.36        | 2.50  | 2.64  |  |

| Molded Package Thickness | A2          | .088 | .091    | .094 | 2.24        | 2.31  | 2.39  |  |

| Standoff §               | A1          | .004 | .008    | .012 | 0.10        | 0.20  | 0.30  |  |

| Overall Width            | E           | .394 | .407    | .420 | 10.01       | 10.34 | 10.67 |  |

| Molded Package Width     | E1          | .288 | .295    | .299 | 7.32        | 7.49  | 7.59  |  |

| Overall Length           | D           | .695 | .704    | .712 | 17.65       | 17.87 | 18.08 |  |

| Chamfer Distance         | h           | .010 | .020    | .029 | 0.25        | 0.50  | 0.74  |  |

| Foot Length              | L           | .016 | .033    | .050 | 0.41        | 0.84  | 1.27  |  |

| Foot Angle Top           | φ           | 0    | 4       | 8    | 0           | 4     | 8     |  |

| Lead Thickness           | С           | .009 | .011    | .013 | 0.23        | 0.28  | 0.33  |  |

| Lead Width               | В           | .014 | .017    | .020 | 0.36        | 0.42  | 0.51  |  |

| Mold Draft Angle Top     | α           | 0    | 12      | 15   | 0           | 12    | 15    |  |

| Mold Draft Angle Bottom  | β           | 0    | 12      | 15   | 0           | 12    | 15    |  |

\* Controlling Parameter § Significant Characteristic

Notes:

Dimensions D and E1 do not include mold flash or protrusions. Mold flash or protrusions shall not exceed .010" (0.254mm) per side. JEDEC Equivalent: MS-013

Drawing No. C04-052

#### I

| I/O Ports                                                                                                                                                                                                                                                                                                                                       |                                                                                                                                                                                              |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| I2C Bus Data Requirements                                                                                                                                                                                                                                                                                                                       |                                                                                                                                                                                              |

| I <sup>2</sup> C Bus Start/Stop Bits Requirements                                                                                                                                                                                                                                                                                               |                                                                                                                                                                                              |

|                                                                                                                                                                                                                                                                                                                                                 |                                                                                                                                                                                              |

| I <sup>2</sup> C Mode                                                                                                                                                                                                                                                                                                                           |                                                                                                                                                                                              |

| Registers                                                                                                                                                                                                                                                                                                                                       | 80                                                                                                                                                                                           |

| I <sup>2</sup> C Mode                                                                                                                                                                                                                                                                                                                           | 80                                                                                                                                                                                           |

| ACK Pulse                                                                                                                                                                                                                                                                                                                                       |                                                                                                                                                                                              |

|                                                                                                                                                                                                                                                                                                                                                 |                                                                                                                                                                                              |

| Acknowledge Sequence Timing                                                                                                                                                                                                                                                                                                                     |                                                                                                                                                                                              |

| Baud Rate Generator                                                                                                                                                                                                                                                                                                                             |                                                                                                                                                                                              |

| Bus Collision                                                                                                                                                                                                                                                                                                                                   |                                                                                                                                                                                              |

| Repeated Start Condition                                                                                                                                                                                                                                                                                                                        |                                                                                                                                                                                              |

| Start Condition                                                                                                                                                                                                                                                                                                                                 |                                                                                                                                                                                              |

|                                                                                                                                                                                                                                                                                                                                                 |                                                                                                                                                                                              |

| Stop Condition                                                                                                                                                                                                                                                                                                                                  |                                                                                                                                                                                              |

| Clock Arbitration                                                                                                                                                                                                                                                                                                                               |                                                                                                                                                                                              |

| Effect of a Reset                                                                                                                                                                                                                                                                                                                               | 105                                                                                                                                                                                          |

| General Call Address Support                                                                                                                                                                                                                                                                                                                    | 94                                                                                                                                                                                           |

| Master Mode                                                                                                                                                                                                                                                                                                                                     |                                                                                                                                                                                              |

|                                                                                                                                                                                                                                                                                                                                                 |                                                                                                                                                                                              |

| Operation                                                                                                                                                                                                                                                                                                                                       |                                                                                                                                                                                              |

| Repeated Start Timing                                                                                                                                                                                                                                                                                                                           | 100                                                                                                                                                                                          |

| Master Mode Reception                                                                                                                                                                                                                                                                                                                           |                                                                                                                                                                                              |

| Master Mode Start Condition                                                                                                                                                                                                                                                                                                                     |                                                                                                                                                                                              |

|                                                                                                                                                                                                                                                                                                                                                 |                                                                                                                                                                                              |

| Master Mode Transmission                                                                                                                                                                                                                                                                                                                        |                                                                                                                                                                                              |

| Multi-Master Communication, Bus Collision                                                                                                                                                                                                                                                                                                       |                                                                                                                                                                                              |

| and Arbitration                                                                                                                                                                                                                                                                                                                                 | 105                                                                                                                                                                                          |

| Multi-Master Mode                                                                                                                                                                                                                                                                                                                               | 105                                                                                                                                                                                          |

| Read/Write Bit Information (R/W Bit)                                                                                                                                                                                                                                                                                                            |                                                                                                                                                                                              |

|                                                                                                                                                                                                                                                                                                                                                 |                                                                                                                                                                                              |

| Serial Clock (RC3/SCK/SCL)                                                                                                                                                                                                                                                                                                                      |                                                                                                                                                                                              |

| Slave Mode                                                                                                                                                                                                                                                                                                                                      |                                                                                                                                                                                              |

| Addressing                                                                                                                                                                                                                                                                                                                                      | 84                                                                                                                                                                                           |

| Reception                                                                                                                                                                                                                                                                                                                                       |                                                                                                                                                                                              |

| Transmission                                                                                                                                                                                                                                                                                                                                    |                                                                                                                                                                                              |

| Sleep Operation                                                                                                                                                                                                                                                                                                                                 |                                                                                                                                                                                              |

|                                                                                                                                                                                                                                                                                                                                                 |                                                                                                                                                                                              |

|                                                                                                                                                                                                                                                                                                                                                 |                                                                                                                                                                                              |

| Stop Condition Timing                                                                                                                                                                                                                                                                                                                           | 104                                                                                                                                                                                          |

| Stop Condition Timing<br>ID Locations                                                                                                                                                                                                                                                                                                           | 104<br>143, 157                                                                                                                                                                              |