Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                           |

|----------------------------|---------------------------------------------------------------------------|

| Product Status             | Active                                                                    |

| Core Processor             | PIC                                                                       |

| Core Size                  | 8-Bit                                                                     |

| Speed                      | 20MHz                                                                     |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                         |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                     |

| Number of I/O              | 33                                                                        |

| Program Memory Size        | 7KB (4K x 14)                                                             |

| Program Memory Type        | FLASH                                                                     |

| EEPROM Size                | 128 x 8                                                                   |

| RAM Size                   | 192 x 8                                                                   |

| Voltage - Supply (Vcc/Vdd) | 4V ~ 5.5V                                                                 |

| Data Converters            | A/D 8x10b                                                                 |

| Oscillator Type            | External                                                                  |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                         |

| Mounting Type              | Surface Mount                                                             |

| Package / Case             | 44-LCC (J-Lead)                                                           |

| Supplier Device Package    | 44-PLCC (16.59x16.59)                                                     |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16f874at-i-l |

|                            |                                                                           |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

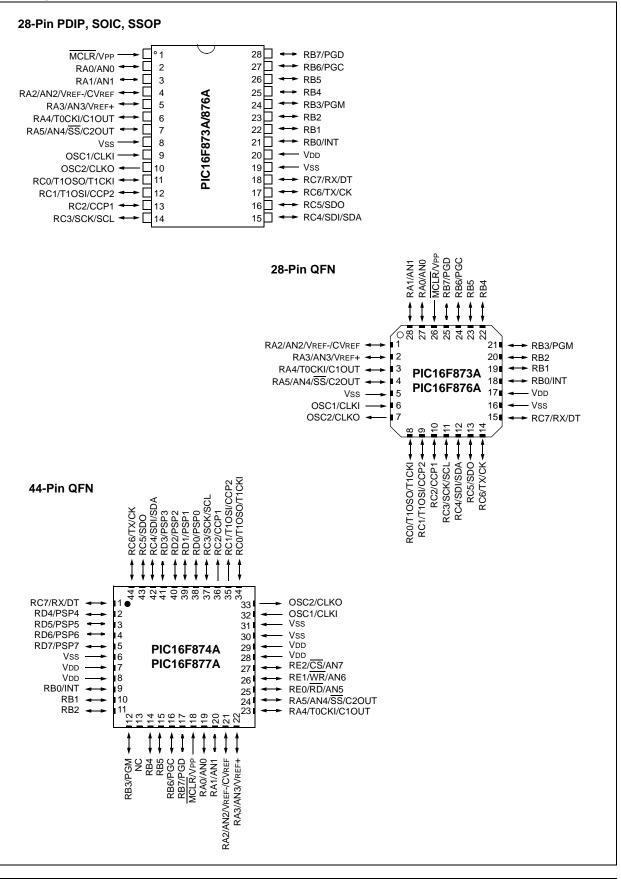

#### **Pin Diagrams**

| Pin Name                                                | PDIP, SOIC,<br>SSOP Pin# | QFN<br>Pin# | I/O/P<br>Type      | Buffer<br>Type         | Description                                                                                                                                                                                                                 |

|---------------------------------------------------------|--------------------------|-------------|--------------------|------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| OSC1/CLKI<br>OSC1<br>CLKI                               | 9                        | 6           |                    | ST/CMOS <sup>(3)</sup> | Oscillator crystal or external clock input.<br>Oscillator crystal input or external clock source input. ST<br>buffer when configured in RC mode; otherwise CMOS.<br>External clock source input. Always associated with pin |

| 0EI II                                                  |                          |             |                    |                        | function OSC1 (see OSC1/CLKI, OSC2/CLKO pins).                                                                                                                                                                              |

| OSC2/CLKO<br>OSC2                                       | 10                       | 7           | Ο                  | _                      | Oscillator crystal or clock output.<br>Oscillator crystal output. Connects to crystal or resonator<br>in Crystal Oscillator mode.                                                                                           |

| CLKO                                                    |                          |             | 0                  |                        | In RC mode, OSC2 pin outputs CLKO, which has 1/4 the<br>frequency of OSC1 and denotes the instruction cycle rate                                                                                                            |

| MCLR/VPP<br>MCLR                                        | 1                        | 26          | I                  | ST                     | Master Clear (input) or programming voltage (output).<br>Master Clear (Reset) input. This pin is an active low Reset<br>to the device.                                                                                      |

| VPP                                                     |                          |             | Р                  |                        | Programming voltage input.                                                                                                                                                                                                  |

|                                                         |                          |             |                    |                        | PORTA is a bidirectional I/O port.                                                                                                                                                                                          |

| RA0/AN0<br>RA0<br>AN0                                   | 2                        | 27          | I/O<br>I           | TTL                    | Digital I/O.<br>Analog input 0.                                                                                                                                                                                             |

| RA1/AN1<br>RA1<br>AN1                                   | 3                        | 28          | I/O<br>I           | TTL                    | Digital I/O.<br>Analog input 1.                                                                                                                                                                                             |

| RA2/AN2/VREF-/<br>CVREF<br>RA2<br>AN2<br>VREF-<br>CVREF | 4                        | 1           | I/O<br>I<br>I<br>O | TTL                    | Digital I/O.<br>Analog input 2.<br>A/D reference voltage (Low) input.<br>Comparator VREF output.                                                                                                                            |

| RA3/AN3/VREF+<br>RA3<br>AN3<br>VREF+                    | 5                        | 2           | I/O<br>I<br>I      | TTL                    | Digital I/O.<br>Analog input 3.<br>A/D reference voltage (High) input.                                                                                                                                                      |

| RA4/T0CKI/C1OUT<br>RA4<br>T0CKI<br>C1OUT                | 6                        | 3           | I/O<br>I<br>O      | ST                     | Digital I/O – Open-drain when configured as output.<br>Timer0 external clock input.<br>Comparator 1 output.                                                                                                                 |

| RA5/AN4/SS/C2OUT<br>RA5<br>AN4<br>SS<br>C2OUT           | 7<br>O = ou              | 4           | I/O<br>I<br>I<br>O | TTL                    | Digital I/O.<br>Analog input 4.<br>SPI slave select input.<br>Comparator 2 output.                                                                                                                                          |

#### TABLE 1-2:PIC16F873A/876A PINOUT DESCRIPTION

— = Not used TTL = TTL input ST = Schmitt Trigger input

**Note 1:** This buffer is a Schmitt Trigger input when configured as the external interrupt.

2: This buffer is a Schmitt Trigger input when used in Serial Programming mode.

3: This buffer is a Schmitt Trigger input when configured in RC Oscillator mode and a CMOS input otherwise.

| 1 1 4 1 | սու | 2-3: |  |

|---------|-----|------|--|

#### PIC16F876A/877A REGISTER FILE MAP

| Indirect addr.(*)    | 00h         | Indirect addr.(*)             |           | Indirect addr.(*)   | 100h          | Indirect addr.(*)       | 10 |

|----------------------|-------------|-------------------------------|-----------|---------------------|---------------|-------------------------|----|

| TMR0                 | 00n<br>01h  | OPTION REG                    | 80h       | TMR0                | 100h          | OPTION_REG              | 18 |

| PCL                  | 01h<br>02h  |                               | 81h       | PCL                 | 10111<br>102h |                         | 18 |

|                      | 02n<br>03h  | PCL<br>STATUS                 | 82h       | STATUS              | 10211<br>103h | PCL<br>STATUS           | 18 |

| STATUS               | 03n<br>04h  |                               | 83h       | FSR                 | 103n<br>104h  |                         | 18 |

| FSR                  |             | FSR                           | 84h       | FSR                 | 1041<br>105h  | FSR                     | 18 |

| PORTA                | 05h<br>06h  | TRISA                         | 85h       | DODTD               | 105h          | TRISB                   | 18 |

| PORTB                |             | TRISB                         | 86h       | PORTB               | 106n<br>107h  | TRISB                   | 18 |

|                      | 07h         | TRISC<br>TRISD <sup>(1)</sup> | 87h       |                     | 1071<br>108h  |                         | 18 |

| PORTD <sup>(1)</sup> | 08h         | TRISD <sup>(1)</sup>          | 88h       |                     | 109h          |                         | 18 |

| PORTE <sup>(1)</sup> | 09h         |                               | 89h       | PCLATH              | 1091<br>10Ah  | PCLATH                  | 18 |

| PCLATH               | 0Ah         | PCLATH                        | 8Ah       |                     | 10An<br>10Bh  | INTCON                  | 18 |

| INTCON               | 0Bh         | INTCON                        | 8Bh       | INTCON              | 10Bn<br>10Ch  | EECON1                  | 18 |

| PIR1                 | 0Ch         | PIE1                          | 8Ch       | EEDATA              |               |                         | 18 |

| PIR2                 | 0Dh         | PIE2                          | 8Dh       | EEADR               | 10Dh          | EECON2                  | 18 |

| TMR1L                | 0Eh         | PCON                          | 8Eh       | EEDATH              | 10Eh          | Reserved <sup>(2)</sup> | 18 |

| TMR1H                | 0Fh         |                               | 8Fh       | EEADRH              | 10Fh          | Reserved <sup>(2)</sup> | 18 |

| T1CON                | 10h         |                               | 90h       |                     | 110h          |                         | 19 |

| TMR2                 | 11h         | SSPCON2                       | 91h       |                     | 111h          |                         | 19 |

| T2CON                | 12h         | PR2                           | 92h       |                     | 112h          |                         | 19 |

| SSPBUF               | 13h         | SSPADD                        | 93h       |                     | 113h          |                         | 19 |

| SSPCON               | 14h         | SSPSTAT                       | 94h       |                     | 114h          |                         | 19 |

| CCPR1L               | 15h         |                               | 95h       |                     | 115h          |                         | 19 |

| CCPR1H               | 16h         |                               | 96h       | Conorol             | 116h          | Conorol                 | 19 |

| CCP1CON              | 17h         |                               | 97h       | General<br>Purpose  | 117h          | General<br>Purpose      | 19 |

| RCSTA                | 18h         | TXSTA                         | 98h       | Register            | 118h          | Register                | 19 |

| TXREG                | 19h         | SPBRG                         | 99h       | 16 Bytes            | 119h          | 16 Bytes                | 19 |

| RCREG                | 1Ah         |                               | 9Ah       |                     | 11Ah          |                         | 19 |

| CCPR2L               | 1Bh         |                               | 9Bh       |                     | 11Bh          |                         | 19 |

| CCPR2H               | 1Ch         | CMCON                         | 9Ch       |                     | 11Ch          |                         | 19 |

| CCP2CON              | 1Dh         | CVRCON                        | 9Dh       |                     | 11Dh          |                         | 19 |

| ADRESH               | 1Eh         | ADRESL                        | 9Eh       |                     | 11Eh          |                         | 19 |

| ADCON0               | 1Fh         | ADCON1                        | 9Fh       |                     | 11Fh          |                         | 19 |

|                      | 20h         |                               | A0h       |                     | 120h          |                         | 1A |

|                      |             | General                       |           | General             |               | General                 |    |

| General              |             | Purpose                       |           | Purpose             |               | Purpose                 |    |

| Purpose              |             | Register                      |           | Register            |               | Register                |    |

| Register             |             | 80 Bytes                      |           | 80 Bytes            |               | 80 Bytes                |    |

| 96 Bytes             |             |                               | EFh       |                     | 16Fh          |                         | 1E |

|                      |             | accesses                      | F0h       | 200005005           | 170h          | accesses                | 1F |

|                      |             | 70h-7Fh                       |           | accesses<br>70h-7Fh |               | 70h - 7Fh               |    |

| <b>_</b>             | 7Fh         |                               | FFh       |                     | 17Fh          |                         | 1F |

| Bank 0               |             | Bank 1                        |           | Bank 2              |               | Bank 3                  |    |

| Unimple              | mented d    | ata memory locati             | ons. read | <b>as</b> '0'.      |               |                         |    |

|                      | iysical reg | -                             |           |                     |               |                         |    |

#### 2.2.2.3 INTCON Register

The INTCON register is a readable and writable register, which contains various enable and flag bits for the TMR0 register overflow, RB port change and external RB0/INT pin interrupts. Note: Interrupt flag bits are set when an interrupt condition occurs regardless of the state of its corresponding enable bit or the global enable bit, GIE (INTCON<7>). User software should ensure the appropriate interrupt flag bits are clear prior to enabling an interrupt.

#### REGISTER 2-3: INTCON REGISTER (ADDRESS 0Bh, 8Bh, 10Bh, 18Bh)

| R/W-0                                                                                                             | R/W-0                         | R/W-0                                    | R/W-0        | R/W-0        | R/W-0         | R/W-0        | R/W-x |  |  |

|-------------------------------------------------------------------------------------------------------------------|-------------------------------|------------------------------------------|--------------|--------------|---------------|--------------|-------|--|--|

| GIE                                                                                                               | PEIE                          | TMR0IE                                   | INTE         | RBIE         | TMR0IF        | INTF         | RBIF  |  |  |

| bit 7                                                                                                             |                               |                                          |              |              |               |              | bit 0 |  |  |

|                                                                                                                   | al Interrupt E                |                                          |              |              |               |              |       |  |  |

|                                                                                                                   | s all unmas<br>es all interru | ked interrupt<br>pts                     | ts           |              |               |              |       |  |  |

| PEIE: Peri                                                                                                        | oheral Interr                 | upt Enable b                             | oit          |              |               |              |       |  |  |

|                                                                                                                   |                               | ked peripher<br>eral interrup            | •            |              |               |              |       |  |  |

| TMR0IE: T                                                                                                         | MR0 Overfl                    | ow Interrupt                             | Enable bit   |              |               |              |       |  |  |

|                                                                                                                   | s the TMR0                    |                                          |              |              |               |              |       |  |  |

|                                                                                                                   | es the TMR                    | •                                        |              |              |               |              |       |  |  |

|                                                                                                                   |                               | al Interrupt E                           |              |              |               |              |       |  |  |

| <ol> <li>= Enables the RB0/INT external interrupt</li> <li>0 = Disables the RB0/INT external interrupt</li> </ol> |                               |                                          |              |              |               |              |       |  |  |

|                                                                                                                   |                               |                                          |              |              |               |              |       |  |  |

|                                                                                                                   | •                             | e Interrupt Ei<br>rt change in           |              |              |               |              |       |  |  |

|                                                                                                                   | •                             | ort change in                            | •            |              |               |              |       |  |  |

|                                                                                                                   | •                             | ow Interrupt                             | •            |              |               |              |       |  |  |

| 1 = TMR0                                                                                                          | register has                  | overflowed                               | (must be cle | ared in soft | ware)         |              |       |  |  |

|                                                                                                                   |                               | al Interrupt F                           |              |              |               |              |       |  |  |

| 1 = The RE                                                                                                        | B0/INT exter                  | nal interrupt                            | occurred (n  |              | red in softwa | are)         |       |  |  |

| RBIF: RB I                                                                                                        | Port Change                   | Interrupt Fl                             | ag bit       |              |               |              |       |  |  |

| the bit                                                                                                           | . Reading F                   | RB7:RB4 p<br>ORTB will e<br>n software). |              |              |               |              |       |  |  |

| 0 = None                                                                                                          | of the RB7:F                  | RB4 pins hav                             | ve changed   | state        |               |              |       |  |  |

| Legend:                                                                                                           |                               |                                          |              |              |               |              |       |  |  |

| R = Reada                                                                                                         | ble bit                       | W = W                                    | /ritable bit | U = Unin     | nplemented    | bit. read as | '0'   |  |  |

| R = Readable bit   | W = Writable bit | U = Unimplemented bit, read as '0'     |  |

|--------------------|------------------|----------------------------------------|--|

| - n = Value at POR | '1' = Bit is set | 0' = Bit is cleared x = Bit is unknown |  |

## 3.0 DATA EEPROM AND FLASH PROGRAM MEMORY

The data EEPROM and Flash program memory is readable and writable during normal operation (over the full VDD range). This memory is not directly mapped in the register file space. Instead, it is indirectly addressed through the Special Function Registers. There are six SFRs used to read and write this memory:

- EECON1

- EECON2

- EEDATA

- EEDATH

- EEADR

- EEADRH

When interfacing to the data memory block, EEDATA holds the 8-bit data for read/write and EEADR holds the address of the EEPROM location being accessed. These devices have 128 or 256 bytes of data EEPROM (depending on the device), with an address range from 00h to FFh. On devices with 128 bytes, addresses from 80h to FFh are unimplemented and will wraparound to the beginning of data EEPROM memory. When writing to unimplemented locations, the on-chip charge pump will be turned off.

When interfacing the program memory block, the EEDATA and EEDATH registers form a two-byte word that holds the 14-bit data for read/write and the EEADR and EEADRH registers form a two-byte word that holds the 13-bit address of the program memory location being accessed. These devices have 4 or 8K words of program Flash, with an address range from 0000h to 0FFFh for the PIC16F873A/874A and 0000h to 1FFFh for the PIC16F876A/877A. Addresses above the range of the respective device will wraparound to the beginning of program memory.

The EEPROM data memory allows single-byte read and write. The Flash program memory allows single-word reads and four-word block writes. Program memory write operations automatically perform an erase-before-write on blocks of four words. A byte write in data EEPROM memory automatically erases the location and writes the new data (erase-before-write).

The write time is controlled by an on-chip timer. The write/erase voltages are generated by an on-chip charge pump, rated to operate over the voltage range of the device for byte or word operations.

When the device is code-protected, the CPU may continue to read and write the data EEPROM memory. Depending on the settings of the write-protect bits, the device may or may not be able to write certain blocks of the program memory; however, reads of the program memory are allowed. When code-protected, the device programmer can no longer access data or program memory; this does NOT inhibit internal reads or writes.

## 3.1 EEADR and EEADRH

The EEADRH:EEADR register pair can address up to a maximum of 256 bytes of data EEPROM or up to a maximum of 8K words of program EEPROM. When selecting a data address value, only the LSByte of the address is written to the EEADR register. When selecting a program address value, the MSByte of the address is written to the EEADRH register and the LSByte is written to the EEADR register.

If the device contains less memory than the full address reach of the address register pair, the Most Significant bits of the registers are not implemented. For example, if the device has 128 bytes of data EEPROM, the Most Significant bit of EEADR is not implemented on access to data EEPROM.

## 3.2 EECON1 and EECON2 Registers

EECON1 is the control register for memory accesses.

Control bit, EEPGD, determines if the access will be a program or data memory access. When clear, as it is when reset, any subsequent operations will operate on the data memory. When set, any subsequent operations will operate on the program memory.

Control bits, RD and WR, initiate read and write or erase, respectively. These bits cannot be cleared, only set, in software. They are cleared in hardware at completion of the read or write operation. The inability to clear the WR bit in software prevents the accidental, premature termination of a write operation.

The WREN bit, when set, will allow a write or erase operation. On power-up, the WREN bit is clear. The WRERR bit is set when a write (or erase) operation is interrupted by a  $\overline{\text{MCLR}}$  or a WDT Time-out Reset during normal operation. In these situations, following Reset, the user can check the WRERR bit and rewrite the location. The data and address will be unchanged in the EEDATA and EEADR registers.

Interrupt flag bit, EEIF in the PIR2 register, is set when the write is complete. It must be cleared in software.

EECON2 is not a physical register. Reading EECON2 will read all '0's. The EECON2 register is used exclusively in the EEPROM write sequence.

Note: The self-programming mechanism for Flash program memory has been changed. On previous PIC16F87X devices, Flash programming was done in single-word erase/ write cycles. The newer PIC18F87XA devices use a four-word erase/write cycle. See Section 3.6 "Writing to Flash Program Memory" for more information.

#### 3.5 Reading Flash Program Memory

To read a program memory location, the user must write two bytes of the address to the EEADR and EEADRH registers, set the EEPGD control bit (EECON1<7>) and then set control bit RD (EECON1<0>). Once the read control bit is set, the program memory Flash controller will use the next two instruction cycles to read the data. This causes these two instructions immediately following the "BSF EECON1, RD" instruction to be ignored. The data is available in the very next cycle in the EEDATA and EEDATH registers; therefore, it can be read as two bytes in the following instructions. EEDATA and EEDATH registers will hold this value until another read or until it is written to by the user (during a write operation).

| EXAMPLE 3-3: | FLASH PROGRAM READ |

|--------------|--------------------|

|              |                    |

|                           | BSF   | STATUS, RP1     | i                                                    |  |

|---------------------------|-------|-----------------|------------------------------------------------------|--|

|                           | BCF   | STATUS, RPO     | ; Bank 2                                             |  |

|                           | MOVLW | MS PROG EE ADDR | i                                                    |  |

|                           | MOVWF | EEADRH          | ; MS Byte of Program Address to read                 |  |

|                           | MOVLW | LS_PROG_EE_ADDR | i                                                    |  |

|                           | MOVWF | EEADR           | ; LS Byte of Program Address to read                 |  |

|                           | BSF   | STATUS, RPO     | ; Bank 3                                             |  |

|                           | BSF   | EECON1, EEPGD   | ; Point to PROGRAM memory                            |  |

|                           | BSF   | EECON1, RD      | ; EE Read                                            |  |

| Required<br>Sequence<br>; |       |                 |                                                      |  |

| luer                      | NOP   |                 |                                                      |  |

| Seq                       | NOP   |                 | ; Any instructions here are ignored as program       |  |

|                           |       |                 | ; memory is read in second cycle after BSF EECON1,RD |  |

| ;                         |       |                 |                                                      |  |

|                           | BCF   | STATUS, RPO     | ; Bank 2                                             |  |

|                           | MOVF  | EEDATA, W       | ; W = LS Byte of Program EEDATA                      |  |

|                           | MOVWF | DATAL           | ;                                                    |  |

|                           | MOVF  | EEDATH, W       | ; W = MS Byte of Program EEDATA                      |  |

|                           | MOVWF | DATAH           | ;                                                    |  |

|                           |       |                 |                                                      |  |

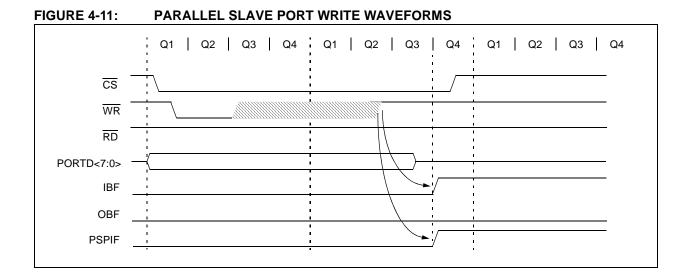

#### FIGURE 4-12: PARALLEL SLAVE PORT READ WAVEFORMS

#### TABLE 4-11: REGISTERS ASSOCIATED WITH PARALLEL SLAVE PORT

| Address | Name   | Bit 7                | Bit 6    | Bit 5     | Bit 4           | Bit 3     | Bit 2   | Bit 1       | Bit 0   | Value on:<br>POR, BOR | Value on<br>all other<br>Resets |

|---------|--------|----------------------|----------|-----------|-----------------|-----------|---------|-------------|---------|-----------------------|---------------------------------|

| 08h     | PORTD  | Port Data            | Latch wh | en writte | en; Port pins w | /hen read |         |             |         | xxxx xxxx             | uuuu uuuu                       |

| 09h     | PORTE  | _                    | _        | _         | _               | —         | RE2     | RE1         | RE0     | xxx                   | uuu                             |

| 89h     | TRISE  | IBF                  | OBF      | IBOV      | PSPMODE         | _         | PORTE D | ata Directi | on bits | 0000 -111             | 0000 -111                       |

| 0Ch     | PIR1   | PSPIF <sup>(1)</sup> | ADIF     | RCIF      | TXIF            | SSPIF     | CCP1IF  | TMR2IF      | TMR1IF  | 0000 0000             | 0000 0000                       |

| 8Ch     | PIE1   | PSPIE <sup>(1)</sup> | ADIE     | RCIE      | TXIE            | SSPIE     | CCP1IE  | TMR2IE      | TMR1IE  | 0000 0000             | 0000 0000                       |

| 9Fh     | ADCON1 | ADFM                 | ADCS2    | _         | —               | PCFG3     | PCFG2   | PCFG1       | PCFG0   | 00 0000               | 00 0000                         |

**Legend:** x = unknown, u = unchanged, - = unimplemented, read as '0'. Shaded cells are not used by the Parallel Slave Port. **Note 1:** Bits PSPIE and PSPIF are reserved on the PIC16F873A/876A; always maintain these bits clear.

| REGISTER 8-1: | CCP1CON                                                                                                                                | I REGISTE                                                                                                                          | ER/CCP2C                                                                                                                          | ON REGIS                                                                                           | STER (ADDF                                                                                              | RESS 17h                                     | /1Dh)         |            |  |  |

|---------------|----------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------|----------------------------------------------|---------------|------------|--|--|

|               | U-0                                                                                                                                    | U-0                                                                                                                                | R/W-0                                                                                                                             | R/W-0                                                                                              | R/W-0                                                                                                   | R/W-0                                        | R/W-0         | R/W-0      |  |  |

|               | —                                                                                                                                      | _                                                                                                                                  | CCPxX                                                                                                                             | CCPxY                                                                                              | CCPxM3                                                                                                  | CCPxM2                                       | CCPxM1        | CCPxM0     |  |  |

|               | bit 7                                                                                                                                  |                                                                                                                                    |                                                                                                                                   |                                                                                                    |                                                                                                         |                                              |               | bit 0      |  |  |

| bit 7-6       | Unimplem                                                                                                                               | ented: Rea                                                                                                                         | <b>d as</b> '0'                                                                                                                   |                                                                                                    |                                                                                                         |                                              |               |            |  |  |

| bit 5-4       | CCPxX:CC                                                                                                                               | PxY: PWM                                                                                                                           | Least Sign                                                                                                                        | ificant bits                                                                                       |                                                                                                         |                                              |               |            |  |  |

|               | <u>Capture mo</u><br>Unused.                                                                                                           | ode:                                                                                                                               |                                                                                                                                   |                                                                                                    |                                                                                                         |                                              |               |            |  |  |

|               | <u>Compare n</u><br>Unused.                                                                                                            | <u>node:</u>                                                                                                                       |                                                                                                                                   |                                                                                                    |                                                                                                         |                                              |               |            |  |  |

|               | <u>PWM mode</u><br>These bits                                                                                                          |                                                                                                                                    | LSbs of the                                                                                                                       | e PWM duty                                                                                         | cycle. The eig                                                                                          | jht MSbs ar                                  | e found in C  | CPRxL.     |  |  |

| bit 3-0       | CCPxM3:CCPxM0: CCPx Mode Select bits                                                                                                   |                                                                                                                                    |                                                                                                                                   |                                                                                                    |                                                                                                         |                                              |               |            |  |  |

|               | 0100 = Ca<br>0101 = Ca<br>0110 = Ca<br>0111 = Ca<br>1000 = Co<br>1001 = Co<br>1010 = Co<br>una<br>1011 = Co<br>res<br>ena<br>11xx = PW | pture mode<br>pture mode<br>pture mode<br>mpare mode<br>mpare mode<br>mpare mode<br>affected)<br>mpare mode<br>ets TMR1;<br>abled) | , every fallir<br>, every risin<br>, every 4th r<br>, every 16th<br>e, set outpu<br>e, clear outp<br>e, generate<br>e, trigger sp | ng edge<br>g edge<br>rising edge<br>t on match (<br>out on match<br>software int<br>ecial event (f | ets CCPx mod<br>CCPxIF bit is<br>a (CCPxIF bit i<br>errupt on mat<br>CCPxIF bit is s<br>and starts an A | set)<br>is set)<br>ch (CCPxIF<br>set, CCPx p | in is unaffec | ted); CCP1 |  |  |

|               | Legend:                                                                                                                                |                                                                                                                                    |                                                                                                                                   |                                                                                                    |                                                                                                         |                                              |               |            |  |  |

|               | R = Reada                                                                                                                              | ble bit                                                                                                                            |                                                                                                                                   | Vritable bit                                                                                       | •                                                                                                       |                                              | oit, read as  | ʻ0'        |  |  |

|               | - n = Value                                                                                                                            | at POR                                                                                                                             | '1' = E                                                                                                                           | Bit is set                                                                                         | '0' = Bit is                                                                                            | cleared                                      | x = Bit is u  | nknown     |  |  |

#### 9.4.2 OPERATION

The MSSP module functions are enabled by setting MSSP Enable bit, SSPEN (SSPCON<5>).

The SSPCON register allows control of the I $^2$ C operation. Four mode selection bits (SSPCON<3:0>) allow one of the following I $^2$ C modes to be selected:

- I<sup>2</sup>C Master mode, clock = OSC/4 (SSPADD + 1)

- I<sup>2</sup>C Slave mode (7-bit address)

- I<sup>2</sup>C Slave mode (10-bit address)

- I<sup>2</sup>C Slave mode (7-bit address) with Start and Stop bit interrupts enabled

- I<sup>2</sup>C Slave mode (10-bit address) with Start and Stop bit interrupts enabled

- I<sup>2</sup>C Firmware Controlled Master mode, slave is Idle

Selection of any I<sup>2</sup>C mode, with the SSPEN bit set, forces the SCL and SDA pins to be open-drain, provided these pins are programmed to inputs by setting the appropriate TRISC bits. To ensure proper operation of the module, pull-up resistors must be provided externally to the SCL and SDA pins.

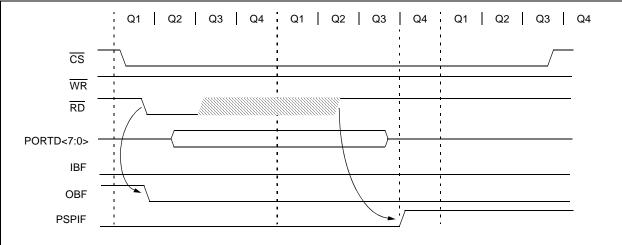

#### 9.4.3 SLAVE MODE

In Slave mode, the SCL and SDA pins must be configured as inputs (TRISC<4:3> set). The MSSP module will override the input state with the output data when required (slave-transmitter).

The I<sup>2</sup>C Slave mode hardware will always generate an interrupt on an address match. Through the mode select bits, the user can also choose to interrupt on Start and Stop bits

When an address is matched, or the data transfer after an address match is received, the hardware automatically will generate the Acknowledge ( $\overline{ACK}$ ) pulse and load the SSPBUF register with the received value currently in the SSPSR register.

Any combination of the following conditions will cause the MSSP module not to give this ACK pulse:

- The buffer full bit, BF (SSPSTAT<0>), was set before the transfer was received.

- The overflow bit, SSPOV (SSPCON<6>), was set before the transfer was received.

In this case, the SSPSR register value is not loaded into the SSPBUF, but bit SSPIF (PIR1<3>) is set. The BF bit is cleared by reading the SSPBUF register, while bit SSPOV is cleared through software.

The SCL clock input must have a minimum high and low for proper operation. The high and low times of the  $I^2C$  specification, as well as the requirement of the MSSP module, are shown in timing parameter #100 and parameter #101.

#### 9.4.3.1 Addressing

Once the MSSP module has been enabled, it waits for a Start condition to occur. Following the Start condition, the 8 bits are shifted into the SSPSR register. All incoming bits are sampled with the rising edge of the clock (SCL) line. The value of register SSPSR<7:1> is compared to the value of the SSPADD register. The address is compared on the falling edge of the eighth clock (SCL) pulse. If the addresses match, and the BF and SSPOV bits are clear, the following events occur:

- 1. The SSPSR register value is loaded into the SSPBUF register.

- 2. The Buffer Full bit, BF, is set.

- 3. An ACK pulse is generated.

- 4. MSSP Interrupt Flag bit, SSPIF (PIR1<3>), is set (interrupt is generated if enabled) on the falling edge of the ninth SCL pulse.

In 10-bit Address mode, two address bytes need to be received by the slave. The five Most Significant bits (MSbs) of the first address byte specify if this is a 10-bit address. Bit R/W (SSPSTAT<2>) must specify a write so the slave device will receive the second address byte. For a 10-bit address, the first byte would equal '11110 A9 A8 0', where 'A9' and 'A8' are the two MSbs of the address. The sequence of events for 10-bit address is as follows, with steps 7 through 9 for the slave-transmitter:

- 1. Receive first (high) byte of address (bits SSPIF, BF and bit UA (SSPSTAT<1>) are set).

- Update the SSPADD register with second (low) byte of address (clears bit UA and releases the SCL line).

- 3. Read the SSPBUF register (clears bit BF) and clear flag bit SSPIF.

- 4. Receive second (low) byte of address (bits SSPIF, BF and UA are set).

- 5. Update the SSPADD register with the first (high) byte of address. If match releases SCL line, this will clear bit UA.

- 6. Read the SSPBUF register (clears bit BF) and clear flag bit SSPIF.

- 7. Receive Repeated Start condition.

- 8. Receive first (high) byte of address (bits SSPIF and BF are set).

- 9. Read the SSPBUF register (clears bit BF) and clear flag bit SSPIF.

I<sup>2</sup>C SLAVE MODE TIMING (TRANSMISSION, 7-BIT ADDRESS)

#### 9.4.7.1 Clock Arbitration

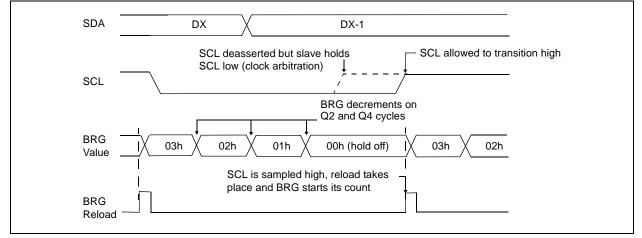

Clock arbitration occurs when the master, during any receive, transmit or Repeated Start/Stop condition, deasserts the SCL pin (SCL allowed to float high). When the SCL pin is allowed to float high, the Baud Rate Generator (BRG) is suspended from counting until the SCL pin is actually sampled high. When the

SCL pin is sampled high, the Baud Rate Generator is reloaded with the contents of SSPADD<6:0> and begins counting. This ensures that the SCL high time will always be at least one BRG rollover count, in the event that the clock is held low by an external device (Figure 9-17).

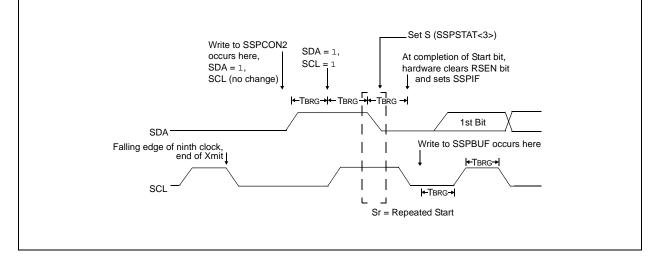

### 9.4.9 I<sup>2</sup>C MASTER MODE REPEATED START CONDITION TIMING

A Repeated Start condition occurs when the RSEN bit (SSPCON2<1>) is programmed high and the I<sup>2</sup>C logic module is in the Idle state. When the RSEN bit is set, the SCL pin is asserted low. When the SCL pin is sampled low, the Baud Rate Generator is loaded with the contents of SSPADD<5:0> and begins counting. The SDA pin is released (brought high) for one Baud Rate Generator count (TBRG). When the Baud Rate Generator times out, if SDA is sampled high, the SCL pin will be deasserted (brought high). When SCL is sampled high, the Baud Rate Generator is reloaded with the contents of SSPADD<6:0> and begins counting. SDA and SCL must be sampled high for one TBRG. This action is then followed by assertion of the SDA pin (SDA = 0) for one TBRG while SCL is high. Following this, the RSEN bit (SSPCON2<1>) will be automatically cleared and the Baud Rate Generator will not be reloaded, leaving the SDA pin held low. As soon as a Start condition is detected on the SDA and SCL pins, the S bit (SSPSTAT<3>) will be set. The SSPIF bit will not be set until the Baud Rate Generator has timed out.

- Note 1: If RSEN is programmed while any other event is in progress, it will not take effect.

- A bus collision during the Repeated Start condition occurs if:

- SDA is sampled low when SCL goes from low to high.

- SCL goes low before SDA is asserted low. This may indicate that another master is attempting to transmit a data '1'.

Immediately following the SSPIF bit getting set, the user may write the SSPBUF with the 7-bit address in 7-bit mode or the default first address in 10-bit mode. After the first eight bits are transmitted and an ACK is received, the user may then transmit an additional eight bits of address (10-bit mode) or eight bits of data (7-bit mode).

#### 9.4.9.1 WCOL Status Flag

If the user writes the SSPBUF when a Repeated Start sequence is in progress, the WCOL is set and the contents of the buffer are unchanged (the write doesn't occur).

Note: Because queueing of events is not allowed, writing of the lower 5 bits of SSPCON2 is disabled until the Repeated Start condition is complete.

## FIGURE 9-20: REPEAT START CONDITION WAVEFORM

NOTES:

bit 0

## **13.0 COMPARATOR VOLTAGE REFERENCE MODULE**

The Comparator Voltage Reference Generator is a 16-tap resistor ladder network that provides a fixed voltage reference when the comparators are in mode '110'. A programmable register controls the function of the reference generator. Register 13-1 lists the bit functions of the CVRCON register.

As shown in Figure 13-1, the resistor ladder is segmented to provide two ranges of CVREF values and has a power-down function to conserve power when the reference is not being used. The comparator reference supply voltage (also referred to as CVRSRC) comes directly from VDD. It should be noted, however, that the voltage at the top of the ladder is CVRSRC - VSAT, where VSAT is the saturation voltage of the power switch transistor. This reference will only be as accurate as the values of CVRSRC and VSAT.

The output of the reference generator may be connected to the RA2/AN2/VREF-/CVREF pin. This can be used as a simple D/A function by the user if a very highimpedance load is used. The primary purpose of this function is to provide a test path for testing the reference generator function.

|   |      | R/W-0     | R/W-0        | R/W-0       | U-0         | R/W-0 | R/W-0 | R/W-0 | R/W-0 |

|---|------|-----------|--------------|-------------|-------------|-------|-------|-------|-------|

|   |      | CVREN     | CVROE        | CVRR        | —           | CVR3  | CVR2  | CVR1  | CVR0  |

|   |      | bit 7     |              |             |             |       |       |       | bit ( |

|   |      |           |              |             |             |       |       |       |       |

| b | it 7 | CVREN: Co | omparator V  | oltage Refe | rence Enabl | e bit |       |       |       |

|   |      | 1 = CVREF | circuit powe | ered on     |             |       |       |       |       |

### REGISTER 13-1: CVRCON CONTROL REGISTER (ADDRESS 9Dh)

|         | <ul> <li>1 = CVREF circuit powered on</li> <li>0 = CVREF circuit powered down</li> </ul>                                               |

|---------|----------------------------------------------------------------------------------------------------------------------------------------|

|         |                                                                                                                                        |

| bit 6   | CVROE: Comparator VREF Output Enable bit                                                                                               |

|         | 1 = CVREF voltage level is output on RA2/AN2/VREF-/CVREF pin                                                                           |

|         | 0 = CVREF voltage level is disconnected from RA2/AN2/VREF-/CVREF pin                                                                   |

| bit 5   | CVRR: Comparator VREF Range Selection bit                                                                                              |

|         | 1 = 0 to 0.75 CVRSRC, with CVRSRC/24 step size                                                                                         |

|         | 0 = 0.25 CVRSRC to 0.75 CVRSRC, with CVRSRC/32 step size                                                                               |

| bit 4   | Unimplemented: Read as '0'                                                                                                             |

| bit 3-0 | <b>CVR3:CVR0:</b> Comparator VREF Value Selection bits $0 \le VR3:VR0 \le 15$                                                          |

|         | When CVRR = 1:                                                                                                                         |

|         | $\overline{\text{CVREF}} = (\text{VR} < 3:0 > / 24) \bullet (\text{CVRSRC})$                                                           |

|         | When CVRR = 0:                                                                                                                         |

|         | $\overline{\text{CVREF}} = 1/4 \bullet (\overline{\text{CVRSRC}}) + (\overline{\text{VR3:VR0}}/32) \bullet (\overline{\text{CVRSRC}})$ |

|         |                                                                                                                                        |

|         |                                                                                                                                        |

| Legend:           |                  |                      |                    |

|-------------------|------------------|----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented    | bit, read as '0'   |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared | x = Bit is unknown |

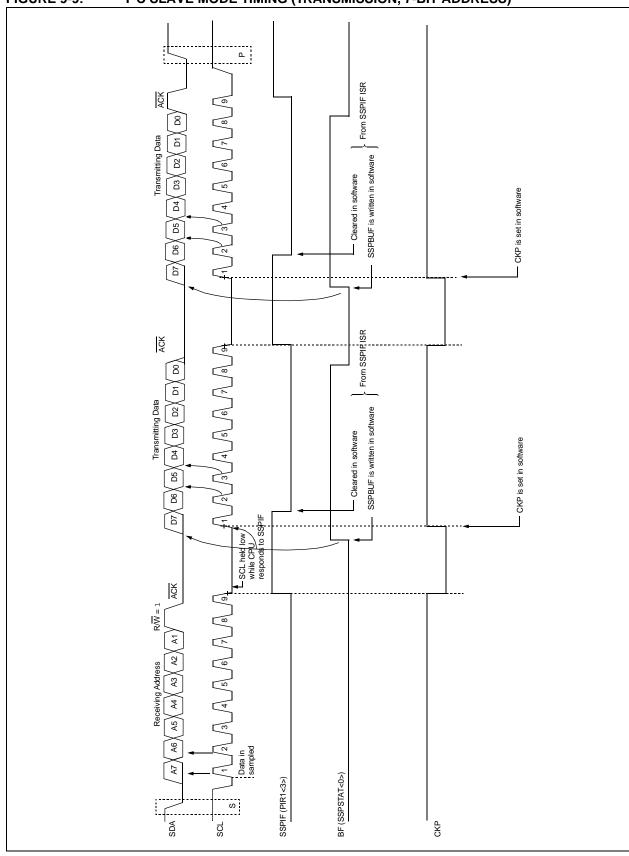

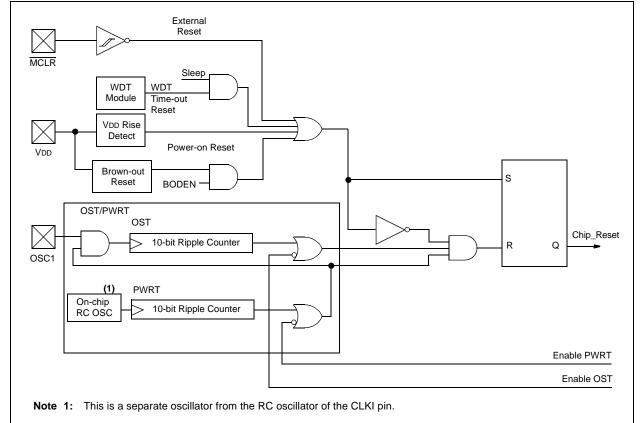

### 14.3 Reset

The PIC16F87XA differentiates between various kinds of Reset:

- Power-on Reset (POR)

- MCLR Reset during normal operation

- MCLR Reset during Sleep

- WDT Reset (during normal operation)

- WDT Wake-up (during Sleep)

- Brown-out Reset (BOR)

Some registers are not affected in any Reset condition. Their status is unknown on POR and unchanged in any other Reset. Most other registers are reset to a "Reset state" on Power-on Reset (POR), on the MCLR and WDT Reset, on MCLR Reset during Sleep and Brownout Reset (BOR). They are not affected by a WDT wake-up which is viewed as the resumption of normal operation. The TO and PD bits are set or cleared differently in different Reset situations as indicated in Table 14-4. These bits are used in software to determine the nature of the Reset. See Table 14-6 for a full description of Reset states of all registers.

A simplified block diagram of the on-chip Reset circuit is shown in Figure 14-4.

#### FIGURE 14-4: SIMPLIFIED BLOCK DIAGRAM OF ON-CHIP RESET CIRCUIT

#### 14.10 Power Control/Status Register (PCON)

The Power Control/Status Register, PCON, has up to two bits depending upon the device.

Bit 0 is the Brown-out Reset Status bit, BOR. The BOR bit is unknown on a Power-on Reset. It must then be set by the user and checked on subsequent Resets to see if it has been cleared, indicating that a BOR has occurred.

When the Brown-out Reset is disabled, the state of the BOR bit is unpredictable and is, therefore, not valid at any time.

Bit 1 is the Power-on Reset Status bit,  $\overline{\text{POR}}$ . It is cleared on a Power-on Reset and unaffected otherwise. The user must set this bit following a Power-on Reset.

#### TABLE 14-3: TIME-OUT IN VARIOUS SITUATIONS

| Oscillator Configuration | Power             | Power-up         |                   | Wake-up from |

|--------------------------|-------------------|------------------|-------------------|--------------|

|                          | <b>PWRTE =</b> 0  | <b>PWRTE</b> = 1 | Brown-out         | Sleep        |

| XT, HS, LP               | 72 ms + 1024 Tosc | 1024 Tosc        | 72 ms + 1024 Tosc | 1024 Tosc    |

| RC                       | 72 ms             | —                | 72 ms             | —            |

#### TABLE 14-4: STATUS BITS AND THEIR SIGNIFICANCE

| POR | BOR | то | PD | Condition                                               |

|-----|-----|----|----|---------------------------------------------------------|

| 0   | x   | 1  | 1  | Power-on Reset                                          |

| 0   | x   | 0  | x  | Illegal, TO is set on POR                               |

| 0   | x   | x  | 0  | Illegal, PD is set on POR                               |

| 1   | 0   | 1  | 1  | Brown-out Reset                                         |

| 1   | 1   | 0  | 1  | WDT Reset                                               |

| 1   | 1   | 0  | 0  | WDT Wake-up                                             |

| 1   | 1   | u  | u  | MCLR Reset during normal operation                      |

| 1   | 1   | 1  | 0  | MCLR Reset during Sleep or Interrupt Wake-up from Sleep |

**Legend:** x = don't care, u = unchanged

#### TABLE 14-5: RESET CONDITIONS FOR SPECIAL REGISTERS

| Condition                          | Program<br>Counter    | Status<br>Register | PCON<br>Register |

|------------------------------------|-----------------------|--------------------|------------------|

| Power-on Reset                     | 000h                  | 0001 1xxx          | 0x               |

| MCLR Reset during normal operation | 000h                  | 000u uuuu          | uu               |

| MCLR Reset during Sleep            | 000h                  | 0001 Ouuu          | uu               |

| WDT Reset                          | 000h                  | 0000 luuu          | uu               |

| WDT Wake-up                        | PC + 1                | uuu0 0uuu          | uu               |

| Brown-out Reset                    | 000h                  | 0001 luuu          | u0               |

| Interrupt Wake-up from Sleep       | PC + 1 <sup>(1)</sup> | uuul Ouuu          | uu               |

Legend: u = unchanged, x = unknown, - = unimplemented bit, read as '0'

**Note 1:** When the wake-up is due to an interrupt and the GIE bit is set, the PC is loaded with the interrupt vector (0004h).

| 15.2 | Instruction | Descriptions |

|------|-------------|--------------|

|------|-------------|--------------|

| ADDLW            | Add Literal and W                                                                                                          |

|------------------|----------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [ <i>label</i> ] ADDLW k                                                                                                   |

| Operands:        | $0 \leq k \leq 255$                                                                                                        |

| Operation:       | $(W) + k \to (W)$                                                                                                          |

| Status Affected: | C, DC, Z                                                                                                                   |

| Description:     | The contents of the W register<br>are added to the eight-bit literal 'k'<br>and the result is placed in the W<br>register. |

|                  | register.                                                                                                                                                      |  |

|------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| ADDWF            | Add W and f                                                                                                                                                    |  |

| Syntax:          | [label] ADDWF f,d                                                                                                                                              |  |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ d \in [0,1] \end{array}$                                                                                                |  |

| Operation:       | (W) + (f) $\rightarrow$ (destination)                                                                                                                          |  |

| Status Affected: | C, DC, Z                                                                                                                                                       |  |

| Description:     | Add the contents of the W register<br>with register 'f'. If 'd' is '0', the<br>result is stored in the W register. If<br>'d' is '1', the result is stored back |  |

| BCF              | Bit Clear f                                                         |

|------------------|---------------------------------------------------------------------|

| Syntax:          | [label]BCF f,b                                                      |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ 0 \leq b \leq 7 \end{array}$ |

| Operation:       | $0 \rightarrow (f < b >)$                                           |

| Status Affected: | None                                                                |

| Description:     | Bit 'b' in register 'f' is cleared.                                 |

| BSF              | Bit Set f                                                           |

|------------------|---------------------------------------------------------------------|

| Syntax:          | [ <i>label</i> ] BSF f,b                                            |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ 0 \leq b \leq 7 \end{array}$ |

| Operation:       | $1 \rightarrow (f < b >)$                                           |

| Status Affected: | None                                                                |

| Description:     | Bit 'b' in register 'f' is set.                                     |

| ANDLW            | AND Literal with W                                                                                                     |

|------------------|------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [ <i>label</i> ] ANDLW k                                                                                               |

| Operands:        | $0 \leq k \leq 255$                                                                                                    |

| Operation:       | (W) .AND. (k) $\rightarrow$ (W)                                                                                        |

| Status Affected: | Z                                                                                                                      |

| Description:     | The contents of W register are<br>AND'ed with the eight-bit literal<br>'k'. The result is placed in the W<br>register. |

in register 'f'.

| BTFSS            | Bit Test f, Skip if Set                                                                                                                                                                                         |

|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [ label ] BTFSS f,b                                                                                                                                                                                             |

| Operands:        | $0 \le f \le 127$<br>$0 \le b < 7$                                                                                                                                                                              |

| Operation:       | skip if (f <b>) = 1</b>                                                                                                                                                                                         |

| Status Affected: | None                                                                                                                                                                                                            |

| Description:     | If bit 'b' in register 'f' is '0', the next<br>instruction is executed.<br>If bit 'b' is '1', then the next instruc-<br>tion is discarded and a NOP is<br>executed instead, making this a<br>2 TCY instruction. |

| ANDWF            | AND W with f                                                                                                                                                    |

|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [label] ANDWF f,d                                                                                                                                               |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ d \in [0,1] \end{array}$                                                                                                 |

| Operation:       | (W) .AND. (f) $\rightarrow$ (destination)                                                                                                                       |

| Status Affected: | Z                                                                                                                                                               |

| Description:     | AND the W register with register<br>'f'. If 'd' is '0', the result is stored in<br>the W register. If 'd' is '1', the<br>result is stored back in register 'f'. |

| BTFSC            | Bit Test, Skip if Clear                                                                                                                                                                                      |

|------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [ label ] BTFSC f,b                                                                                                                                                                                          |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ 0 \leq b \leq 7 \end{array}$                                                                                                                                          |

| Operation:       | skip if (f <b>) = <math>0</math></b>                                                                                                                                                                         |

| Status Affected: | None                                                                                                                                                                                                         |

| Description:     | If bit 'b' in register 'f' is '1', the next instruction is executed.<br>If bit 'b' in register 'f' is '0', the next instruction is discarded and a NOP is executed instead, making this a 2 TCY instruction. |

#### 16.3 MPLAB C17 and MPLAB C18 C Compilers

The MPLAB C17 and MPLAB C18 Code Development Systems are complete ANSI C compilers for Microchip's PIC17CXXX and PIC18CXXX family of microcontrollers. These compilers provide powerful integration capabilities, superior code optimization and ease of use not found with other compilers.

For easy source level debugging, the compilers provide symbol information that is optimized to the MPLAB IDE debugger.

### 16.4 MPLINK Object Linker/ MPLIB Object Librarian

The MPLINK object linker combines relocatable objects created by the MPASM assembler and the MPLAB C17 and MPLAB C18 C compilers. It can link relocatable objects from precompiled libraries, using directives from a linker script.

The MPLIB object librarian manages the creation and modification of library files of pre-compiled code. When a routine from a library is called from a source file, only the modules that contain that routine will be linked in with the application. This allows large libraries to be used efficiently in many different applications.

The object linker/library features include:

- Efficient linking of single libraries instead of many smaller files

- Enhanced code maintainability by grouping related modules together

- Flexible creation of libraries with easy module listing, replacement, deletion and extraction

## 16.5 MPLAB C30 C Compiler

The MPLAB C30 C compiler is a full-featured, ANSI compliant, optimizing compiler that translates standard ANSI C programs into dsPIC30F assembly language source. The compiler also supports many command-line options and language extensions to take full advantage of the dsPIC30F device hardware capabilities, and afford fine control of the compiler code generator.

MPLAB C30 is distributed with a complete ANSI C standard library. All library functions have been validated and conform to the ANSI C library standard. The library includes functions for string manipulation, dynamic memory allocation, data conversion, time-keeping, and math functions (trigonometric, exponential and hyperbolic). The compiler provides symbolic information for high level source debugging with the MPLAB IDE.

## 16.6 MPLAB ASM30 Assembler, Linker, and Librarian

MPLAB ASM30 assembler produces relocatable machine code from symbolic assembly language for dsPIC30F devices. MPLAB C30 compiler uses the assembler to produce it's object file. The assembler generates relocatable object files that can then be archived or linked with other relocatable object files and archives to create an executable file. Notable features of the assembler include:

- Support for the entire dsPIC30F instruction set

- · Support for fixed-point and floating-point data

- Command line interface

- Rich directive set

- Flexible macro language

- MPLAB IDE compatibility

### 16.7 MPLAB SIM Software Simulator

The MPLAB SIM software simulator allows code development in a PC hosted environment by simulating the PIC series microcontrollers on an instruction level. On any given instruction, the data areas can be examined or modified and stimuli can be applied from a file, or user defined key press, to any pin. The execution can be performed in Single-Step, Execute Until Break, or Trace mode.

The MPLAB SIM simulator fully supports symbolic debugging using the MPLAB C17 and MPLAB C18 C Compilers, as well as the MPASM assembler. The software simulator offers the flexibility to develop and debug code outside of the laboratory environment, making it an excellent, economical software development tool.

## 16.8 MPLAB SIM30 Software Simulator

The MPLAB SIM30 software simulator allows code development in a PC hosted environment by simulating the dsPIC30F series microcontrollers on an instruction level. On any given instruction, the data areas can be examined or modified and stimuli can be applied from a file, or user defined key press, to any of the pins.

The MPLAB SIM30 simulator fully supports symbolic debugging using the MPLAB C30 C Compiler and MPLAB ASM30 assembler. The simulator runs in either a Command Line mode for automated tasks, or from MPLAB IDE. This high speed simulator is designed to debug, analyze and optimize time intensive DSP routines.

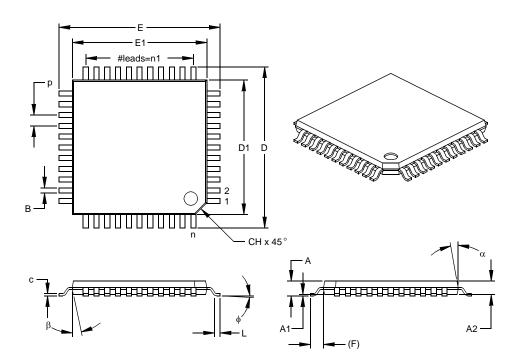

## 44-Lead Plastic Thin Quad Flatpack (PT) 10x10x1 mm Body, 1.0/0.10 mm Lead Form (TQFP)

Note: For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

|                          | Units  | INCHES |      |      | MILLIMETERS* |       |       |

|--------------------------|--------|--------|------|------|--------------|-------|-------|

| Dimension                | Limits | MIN    | NOM  | MAX  | MIN          | NOM   | MAX   |

| Number of Pins           | n      |        | 44   |      |              | 44    |       |

| Pitch                    | р      |        | .031 |      |              | 0.80  |       |

| Pins per Side            | n1     |        | 11   |      |              | 11    |       |

| Overall Height           | А      | .039   | .043 | .047 | 1.00         | 1.10  | 1.20  |

| Molded Package Thickness | A2     | .037   | .039 | .041 | 0.95         | 1.00  | 1.05  |

| Standoff §               | A1     | .002   | .004 | .006 | 0.05         | 0.10  | 0.15  |

| Foot Length              | L      | .018   | .024 | .030 | 0.45         | 0.60  | 0.75  |

| Footprint (Reference)    | (F)    |        | .039 |      | 1.00         |       |       |

| Foot Angle               | φ      | 0      | 3.5  | 7    | 0            | 3.5   | 7     |

| Overall Width            | Е      | .463   | .472 | .482 | 11.75        | 12.00 | 12.25 |

| Overall Length           | D      | .463   | .472 | .482 | 11.75        | 12.00 | 12.25 |

| Molded Package Width     | E1     | .390   | .394 | .398 | 9.90         | 10.00 | 10.10 |

| Molded Package Length    | D1     | .390   | .394 | .398 | 9.90         | 10.00 | 10.10 |

| Lead Thickness           | С      | .004   | .006 | .008 | 0.09         | 0.15  | 0.20  |

| Lead Width               | В      | .012   | .015 | .017 | 0.30         | 0.38  | 0.44  |

| Pin 1 Corner Chamfer     | CH     | .025   | .035 | .045 | 0.64         | 0.89  | 1.14  |

| Mold Draft Angle Top     | α      | 5      | 10   | 15   | 5            | 10    | 15    |

| Mold Draft Angle Bottom  | β      | 5      | 10   | 15   | 5            | 10    | 15    |

\* Controlling Parameter § Significant Characteristic

Notes:

Dimensions D1 and E1 do not include mold flash or protrusions. Mold flash or protrusions shall not exceed .010" (0.254mm) per side. JEDEC Equivalent: MS-026 Drawing No. C04-076