Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                     |

|----------------------------|----------------------------------------------------------------------------|

| Core Processor             | PIC                                                                        |

| Core Size                  | 8-Bit                                                                      |

| Speed                      | 20MHz                                                                      |

| Connectivity               | I²C, SPI, UART/USART                                                       |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                      |

| Number of I/O              | 33                                                                         |

| Program Memory Size        | 7KB (4K x 14)                                                              |

| Program Memory Type        | FLASH                                                                      |

| EEPROM Size                | 128 x 8                                                                    |

| RAM Size                   | 192 x 8                                                                    |

| Voltage - Supply (Vcc/Vdd) | 4V ~ 5.5V                                                                  |

| Data Converters            | A/D 8x10b                                                                  |

| Oscillator Type            | External                                                                   |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                          |

| Mounting Type              | Surface Mount                                                              |

| Package / Case             | 44-TQFP                                                                    |

| Supplier Device Package    | 44-TQFP (10x10)                                                            |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16f874at-i-pt |

|                            |                                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| Pin Name        | PDIP, SOIC,<br>SSOP Pin# | QFN<br>Pin# | I/O/P<br>Type | Buffer<br>Type        | Description                                                                         |  |  |  |  |

|-----------------|--------------------------|-------------|---------------|-----------------------|-------------------------------------------------------------------------------------|--|--|--|--|

|                 |                          |             |               |                       | PORTB is a bidirectional I/O port. PORTB can be software                            |  |  |  |  |

|                 |                          |             |               |                       | programmed for internal weak pull-ups on all inputs.                                |  |  |  |  |

| RB0/INT         | 21                       | 18          |               | TTL/ST <sup>(1)</sup> |                                                                                     |  |  |  |  |

| RB0             |                          |             | I/O           |                       | Digital I/O.                                                                        |  |  |  |  |

| INT             |                          |             | I             |                       | External interrupt.                                                                 |  |  |  |  |

| RB1             | 22                       | 19          | I/O           | TTL                   | Digital I/O.                                                                        |  |  |  |  |

| RB2             | 23                       | 20          | I/O           | TTL                   | Digital I/O.                                                                        |  |  |  |  |

| RB3/PGM         | 24                       | 21          |               | TTL                   |                                                                                     |  |  |  |  |

| RB3             |                          |             | I/O           |                       | Digital I/O.                                                                        |  |  |  |  |

| PGM             |                          |             | I             |                       | Low-voltage (single-supply) ICSP programming enable pir                             |  |  |  |  |

| RB4             | 25                       | 22          | I/O           | TTL                   | Digital I/O.                                                                        |  |  |  |  |

| RB5             | 26                       | 23          | I/O           | TTL                   | Digital I/O.                                                                        |  |  |  |  |

| RB6/PGC         | 27                       | 24          |               | TTL/ST <sup>(2)</sup> |                                                                                     |  |  |  |  |

| RB6             |                          |             | I/O           |                       | Digital I/O.                                                                        |  |  |  |  |

| PGC             |                          |             | I             |                       | In-circuit debugger and ICSP programming clock.                                     |  |  |  |  |

| RB7/PGD         | 28                       | 25          |               | TTL/ST <sup>(2)</sup> |                                                                                     |  |  |  |  |

| RB7             | -                        | -           | I/O           |                       | Digital I/O.                                                                        |  |  |  |  |

| PGD             |                          |             | I/O           |                       | In-circuit debugger and ICSP programming data.                                      |  |  |  |  |

|                 |                          |             |               |                       | PORTC is a bidirectional I/O port.                                                  |  |  |  |  |

| RC0/T1OSO/T1CKI | 11                       | 8           |               | ST                    |                                                                                     |  |  |  |  |

| RC0             |                          | -           | I/O           |                       | Digital I/O.                                                                        |  |  |  |  |

| T1OSO           |                          |             | 0             |                       | Timer1 oscillator output.                                                           |  |  |  |  |

| T1CKI           |                          |             | I             |                       | Timer1 external clock input.                                                        |  |  |  |  |

| RC1/T1OSI/CCP2  | 12                       | 9           |               | ST                    |                                                                                     |  |  |  |  |

| RC1             |                          |             | I/O           |                       | Digital I/O.                                                                        |  |  |  |  |

| T1OSI           |                          |             | 1             |                       | Timer1 oscillator input.                                                            |  |  |  |  |

| CCP2            |                          |             | I/O           |                       | Capture2 input, Compare2 output, PWM2 output.                                       |  |  |  |  |

| RC2/CCP1        | 13                       | 10          |               | ST                    |                                                                                     |  |  |  |  |

| RC2             |                          |             | I/O           |                       | Digital I/O.                                                                        |  |  |  |  |

| CCP1            |                          |             | I/O           |                       | Capture1 input, Compare1 output, PWM1 output.                                       |  |  |  |  |

| RC3/SCK/SCL     | 14                       | 11          | 1/0           | ST                    |                                                                                     |  |  |  |  |

| RC3<br>SCK      |                          |             | I/O<br>I/O    |                       | Digital I/O.<br>Synchronous serial clock input/output for SPI mode.                 |  |  |  |  |

| SCL             |                          |             | 1/O           |                       | Synchronous serial clock input/output for Sr I mode.                                |  |  |  |  |

| RC4/SDI/SDA     | 15                       | 12          | ., 0          | ST                    |                                                                                     |  |  |  |  |

| RC4             | 15                       | 12          | I/O           | 51                    | Digital I/O.                                                                        |  |  |  |  |

| SDI             |                          |             | ., c          |                       | SPI data in.                                                                        |  |  |  |  |

| SDA             |                          |             | I/O           |                       | I <sup>2</sup> C data I/O.                                                          |  |  |  |  |

| RC5/SDO         | 16                       | 13          |               | ST                    |                                                                                     |  |  |  |  |

| RC5             |                          |             | I/O           |                       | Digital I/O.                                                                        |  |  |  |  |

| SDO             |                          |             | 0             |                       | SPI data out.                                                                       |  |  |  |  |

| RC6/TX/CK       | 17                       | 14          |               | ST                    |                                                                                     |  |  |  |  |

| RC6             |                          |             | I/O           |                       | Digital I/O.                                                                        |  |  |  |  |

| TX              |                          |             | 0             |                       | USART asynchronous transmit.                                                        |  |  |  |  |

| CK              |                          |             | I/O           |                       | USART1 synchronous clock.                                                           |  |  |  |  |

| RC7/RX/DT       | 18                       | 15          |               | ST                    |                                                                                     |  |  |  |  |

| RC7             |                          |             | I/O           |                       | Digital I/O.                                                                        |  |  |  |  |

| RX<br>DT        |                          |             | I/O           |                       | USART asynchronous receive.                                                         |  |  |  |  |

|                 | 0.40                     | <b>F A</b>  |               |                       | USART synchronous data.                                                             |  |  |  |  |

| Vss             | 8, 19<br>20              | 5,6         | P             |                       | Ground reference for logic and I/O pins.<br>Positive supply for logic and I/O pins. |  |  |  |  |

| Vdd             |                          | 17          | Р             |                       |                                                                                     |  |  |  |  |

| TABLE 1-2: PIC16F873A/876A PINOUT DESCRIPTION (CONTINUE |

|---------------------------------------------------------|

|---------------------------------------------------------|

**Note 1:** This buffer is a Schmitt Trigger input when configured as the external interrupt.

2: This buffer is a Schmitt Trigger input when used in Serial Programming mode.

3: This buffer is a Schmitt Trigger input when configured in RC Oscillator mode and a CMOS input otherwise.

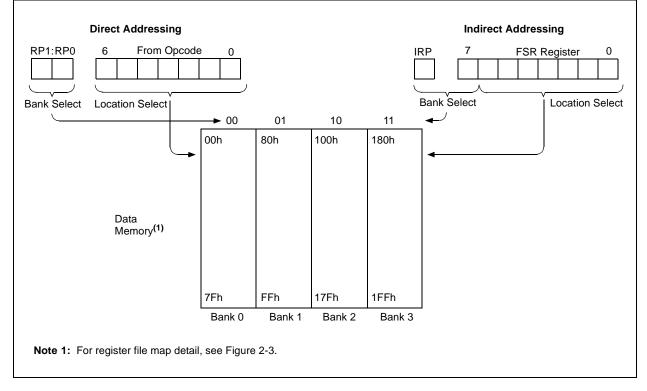

### 2.5 Indirect Addressing, INDF and FSR Registers

The INDF register is not a physical register. Addressing the INDF register will cause indirect addressing.

Indirect addressing is possible by using the INDF register. Any instruction using the INDF register actually accesses the register pointed to by the File Select Register, FSR. Reading the INDF register itself, indirectly (FSR = 0) will read 00h. Writing to the INDF register indirectly results in a no operation (although status bits may be affected). An effective 9-bit address is obtained by concatenating the 8-bit FSR register and the IRP bit (Status<7>) as shown in Figure 2-6. A simple program to clear RAM locations 20h-2Fh using indirect addressing is shown in Example 2-2.

#### EXAMPLE 2-2: INDIRECT ADDRESSING

|          | MOVLW | 0x20  | ;initialize pointer  |

|----------|-------|-------|----------------------|

|          | MOVWF | FSR   | ;to RAM              |

| NEXT     | CLRF  | INDF  | clear INDF register; |

|          | INCF  | FSR,F | ;inc pointer         |

|          | BTFSS | FSR,4 | ;all done?           |

|          | GOTO  | NEXT  | ;no clear next       |

| CONTINUE |       |       |                      |

|          | :     |       | ;yes continue        |

| 1        |       |       |                      |

NOTES:

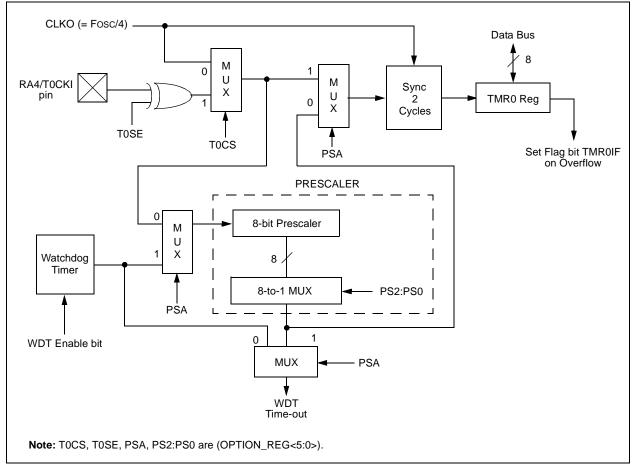

## 5.0 TIMER0 MODULE

The Timer0 module timer/counter has the following features:

- 8-bit timer/counter

- Readable and writable

- 8-bit software programmable prescaler

- · Internal or external clock select

- Interrupt on overflow from FFh to 00h

- Edge select for external clock

Figure 5-1 is a block diagram of the Timer0 module and the prescaler shared with the WDT.

Additional information on the Timer0 module is available in the PIC<sup>®</sup> Mid-Range MCU Family Reference Manual (DS33023).

Timer mode is selected by clearing bit TOCS (OPTION\_REG<5>). In Timer mode, the Timer0 module will increment every instruction cycle (without prescaler). If the TMR0 register is written, the increment is inhibited for the following two instruction cycles. The user can work around this by writing an adjusted value to the TMR0 register.

Counter mode is selected by setting bit T0CS (OPTION\_REG<5>). In Counter mode, Timer0 will increment either on every rising or falling edge of pin RA4/T0CKI. The incrementing edge is determined by the Timer0 Source Edge Select bit, T0SE (OPTION\_REG<4>). Clearing bit T0SE selects the rising edge. Restrictions on the external clock input are discussed in detail in Section 5.2 "Using Timer0 with an External Clock".

The prescaler is mutually exclusively shared between the Timer0 module and the Watchdog Timer. The prescaler is not readable or writable. **Section 5.3** "**Prescaler**" details the operation of the prescaler.

### 5.1 Timer0 Interrupt

The TMR0 interrupt is generated when the TMR0 register overflows from FFh to 00h. This overflow sets bit TMR0IF (INTCON<2>). The interrupt can be masked by clearing bit TMR0IE (INTCON<5>). Bit TMR0IF must be cleared in software by the Timer0 module Interrupt Service Routine before re-enabling this interrupt. The TMR0 interrupt cannot awaken the processor from Sleep since the timer is shut-off during Sleep.

FIGURE 5-1: BLOCK DIAGRAM OF THE TIMER0/WDT PRESCALER

| TABLE 5-1: | <b>REGISTERS ASSOCIATED WITH TIMER0</b> |

|------------|-----------------------------------------|

|------------|-----------------------------------------|

| Address               | Name       | Bit 7                  | Bit 6  | Bit 5  | Bit 4 | Bit 3 | Bit 2  | Bit 1 | Bit 0     | Value on:<br>POR, BOR | Value on<br>all other<br>Resets |

|-----------------------|------------|------------------------|--------|--------|-------|-------|--------|-------|-----------|-----------------------|---------------------------------|

| 01h,101h              | TMR0       | Timer0 Module Register |        |        |       |       |        |       | xxxx xxxx | uuuu uuuu             |                                 |

| 0Bh,8Bh,<br>10Bh,18Bh | INTCON     | GIE                    | PEIE   | TMR0IE | INTE  | RBIE  | TMR0IF | INTF  | RBIF      | 0000 000x             | 0000 000u                       |

| 81h,181h              | OPTION_REG | RBPU                   | INTEDG | TOCS   | T0SE  | PSA   | PS2    | PS1   | PS0       | 1111 1111             | 1111 1111                       |

**Legend:** x = unknown, u = unchanged, - = unimplemented locations read as '0'. Shaded cells are not used by Timer0.

### 9.3.2 OPERATION

When initializing the SPI, several options need to be specified. This is done by programming the appropriate control bits (SSPCON<5:0> and SSPSTAT<7:6>). These control bits allow the following to be specified:

- Master mode (SCK is the clock output)

- Slave mode (SCK is the clock input)

- Clock Polarity (Idle state of SCK)

- Data Input Sample Phase (middle or end of data output time)

- Clock Edge (output data on rising/falling edge of SCK)

- Clock Rate (Master mode only)

- Slave Select mode (Slave mode only)

The MSSP consists of a transmit/receive shift register (SSPSR) and a buffer register (SSPBUF). The SSPSR shifts the data in and out of the device, MSb first. The SSPBUF holds the data that was written to the SSPSR until the received data is ready. Once the eight bits of data have been received, that byte is moved to the SSPBUF register. Then, the Buffer Full detect bit, BF (SSPSTAT<0>), and the interrupt flag bit, SSPIF, are set. This double-buffering of the received data (SSPBUF) allows the next byte to start reception before reading the data that was just received. Any write to the

SSPBUF register during transmission/reception of data will be ignored and the write collision detect bit, WCOL (SSPCON<7>), will be set. User software must clear the WCOL bit so that it can be determined if the following write(s) to the SSPBUF register completed successfully.

When the application software is expecting to receive valid data, the SSPBUF should be read before the next byte of data to transfer is written to the SSPBUF. Buffer Full bit, BF (SSPSTAT<0>), indicates when SSPBUF has been loaded with the received data (transmission is complete). When the SSPBUF is read, the BF bit is cleared. This data may be irrelevant if the SPI is only a transmitter. Generally, the MSSP interrupt is used to determine when the transmission/reception has completed. The SSPBUF must be read and/or written. If the interrupt method is not going to be used, then software polling can be done to ensure that a write collision does not occur. Example 9-1 shows the loading of the SSPBUF (SSPSR) for data transmission.

The SSPSR is not directly readable or writable and can only be accessed by addressing the SSPBUF register. Additionally, the MSSP Status register (SSPSTAT) indicates the various status conditions.

#### EXAMPLE 9-1: LOADING THE SSPBUF (SSPSR) REGISTER

| LOOP | BRA           | SSPSTAT, BF<br>LOOP<br>SSPBUF, W | ;Has data been received(transmit complete)?<br>;No<br>;WREG reg = contents of SSPBUF |

|------|---------------|----------------------------------|--------------------------------------------------------------------------------------|

|      | MOVWF         | RXDATA                           | ;Save in user RAM, if data is meaningful                                             |

|      | MOVF<br>MOVWF | TXDATA, W<br>SSPBUF              | ;W reg = contents of TXDATA<br>;New data to xmit                                     |

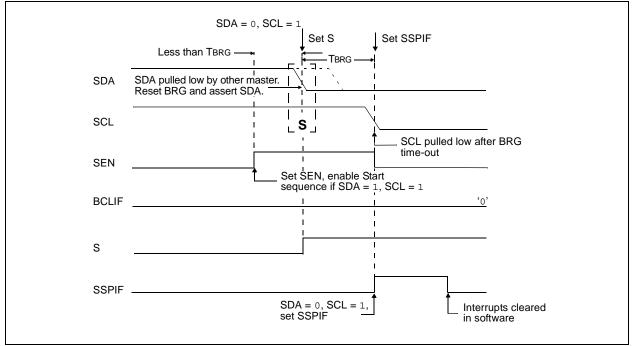

#### 9.4.10 I<sup>2</sup>C MASTER MODE TRANSMISSION

Transmission of a data byte, a 7-bit address or the other half of a 10-bit address is accomplished by simply writing a value to the SSPBUF register. This action will set the Buffer Full flag bit, BF, and allow the Baud Rate Generator to begin counting and start the next transmission. Each bit of address/data will be shifted out onto the SDA pin after the falling edge of SCL is asserted (see data hold time specification, parameter #106). SCL is held low for one Baud Rate Generator rollover count (TBRG). Data should be valid before SCL is released high (see data setup time specification, parameter #107). When the SCL pin is released high, it is held that way for TBRG. The data on the SDA pin must remain stable for that duration and some hold time after the next falling edge of SCL. After the eighth bit is shifted out (the falling edge of the eighth clock), the BF flag is cleared and the master releases SDA. This allows the slave device being addressed to respond with an ACK bit during the ninth bit time, if an address match occurred or if data was received properly. The status of ACK is written into the ACKDT bit on the falling edge of the ninth clock. If the master receives an Acknowledge, the Acknowledge Status bit, ACKSTAT, is cleared. If not, the bit is set. After the ninth clock, the SSPIF bit is set and the master clock (Baud Rate Generator) is suspended until the next data byte is loaded into the SSPBUF, leaving SCL low and SDA unchanged (Figure 9-21).

After the write to the SSPBUF, each bit of address will be shifted out on the falling edge of SCL, until all seven address bits and the R/W bit are completed. On the falling edge of the eighth clock, the master will deassert the SDA pin, allowing the slave to respond with an Acknowledge. On the falling edge of the ninth clock, the master will sample the SDA pin to see if the address was recognized by a slave. The status of the ACK bit is loaded into the ACKSTAT status bit (SSPCON2<6>). Following the falling edge of the ninth clock transmission of the address, the SSPIF is set, the BF flag is cleared and the Baud Rate Generator is turned off until another write to the SSPBUF takes place, holding SCL low and allowing SDA to float.

#### 9.4.10.1 BF Status Flag

In Transmit mode, the BF bit (SSPSTAT<0>) is set when the CPU writes to SSPBUF and is cleared when all eight bits are shifted out.

#### 9.4.10.2 WCOL Status Flag

If the user writes the SSPBUF when a transmit is already in progress (i.e., SSPSR is still shifting out a data byte), the WCOL is set and the contents of the buffer are unchanged (the write doesn't occur).

WCOL must be cleared in software.

#### 9.4.10.3 ACKSTAT Status Flag

In Transmit mode, the ACKSTAT bit (SSPCON2<6>) is cleared when the slave has sent an Acknowledge  $(\overline{ACK} = 0)$  and is set when the slave does Not Acknowledge  $(\overline{ACK} = 1)$ . A slave sends an Acknowledge when it has recognized its address (including a general call) or when the slave has properly received its data.

#### 9.4.11 I<sup>2</sup>C MASTER MODE RECEPTION

Master mode reception is enabled by programming the Receive Enable bit, RCEN (SSPCON2<3>).

Note: The MSSP module must be in an Idle state before the RCEN bit is set or the RCEN bit will be disregarded.

The Baud Rate Generator begins counting and on each rollover, the state of the SCL pin changes (high to low/ low to high) and data is shifted into the SSPSR. After the falling edge of the eighth clock, the receive enable flag is automatically cleared, the contents of the SSPSR are loaded into the SSPBUF, the BF flag bit is set, the SSPIF flag bit is set and the Baud Rate Generator is suspended from counting, holding SCL low. The MSSP is now in Idle state, awaiting the next command. When the buffer is read by the CPU, the BF flag bit is automatically cleared. The user can then send an Acknowledge bit at the end of reception by setting the Acknowledge Sequence Enable bit, ACKEN (SSPCON2<4>).

#### 9.4.11.1 BF Status Flag

In receive operation, the BF bit is set when an address or data byte is loaded into SSPBUF from SSPSR. It is cleared when the SSPBUF register is read.

#### 9.4.11.2 SSPOV Status Flag

In receive operation, the SSPOV bit is set when 8 bits are received into the SSPSR and the BF flag bit is already set from a previous reception.

#### 9.4.11.3 WCOL Status Flag

If the user writes the SSPBUF when a receive is already in progress (i.e., SSPSR is still shifting in a data byte), the WCOL bit is set and the contents of the buffer are unchanged (the write doesn't occur).

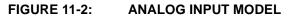

### 11.1 A/D Acquisition Requirements

For the A/D converter to meet its specified accuracy, the charge holding capacitor (CHOLD) must be allowed to fully charge to the input channel voltage level. The analog input model is shown in Figure 11-2. The source impedance (Rs) and the internal sampling switch impedance (Rss) directly affect the time required to charge the capacitor CHOLD. The sampling switch (Rss) impedance varies over the device voltage (VDD); see Figure 11-2. The maximum recommended impedance for analog sources is 2.5 k $\Omega$ . As the impedance is decreased, the acquisition time may be

#### EQUATION 11-1: ACQUISITION TIME

decreased. After the analog input channel is selected (changed), this acquisition must be done before the conversion can be started.

To calculate the minimum acquisition time, Equation 11-1 may be used. This equation assumes that 1/2 LSb error is used (1024 steps for the A/D). The 1/2 LSb error is the maximum error allowed for the A/D to meet its specified resolution.

To calculate the minimum acquisition time, TACQ, see the PIC<sup>®</sup> Mid-Range MCU Family Reference Manual (DS33023).

| TACQ | = Amplifier Settling Time + Hold Capacitor Charging Time + Temperature Coefficient                                                                                                                                                                                |

|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Тс   | = TAMP + TC + TCOFF<br>= $2 \mu s + TC + [(Temperature - 25^{\circ}C)(0.05 \mu s/^{\circ}C)]$<br>= CHOLD (RIC + RSs + RS) In(1/2047)<br>= $-120 \text{ pF} (1 \text{ k}\Omega + 7 \text{ k}\Omega + 10 \text{ k}\Omega) \text{ In}(0.0004885)$<br>= $16.47 \mu s$ |

| TACQ | = $2 \ \mu s + 16.47 \ \mu s + [(50^{\circ}C - 25^{\circ}C)(0.05 \ \mu s/^{\circ}C)]$<br>= $19.72 \ \mu s$                                                                                                                                                        |

Note 1: The reference voltage (VREF) has no effect on the equation since it cancels itself out.

- 2: The charge holding capacitor (CHOLD) is not discharged after each conversion.

- **3:** The maximum recommended impedance for analog sources is 2.5 k $\Omega$ . This is required to meet the pin leakage specification.

## 12.0 COMPARATOR MODULE

REGISTER 12-1: CMCON REGISTER

The comparator module contains two analog comparators. The inputs to the comparators are multiplexed with I/O port pins RA0 through RA3, while the outputs are multiplexed to pins RA4 and RA5. The on-chip voltage reference (Section 13.0 "Comparator Voltage Reference Module") can also be an input to the comparators. The CMCON register (Register 12-1) controls the comparator input and output multiplexers. A block diagram of the various comparator configurations is shown in Figure 12-1.

|       | R-0                            | R-0                                     | R/W-0        | R/W-0       | R/W-0       | R/W-1         | R/W-1        | R/W-1  |

|-------|--------------------------------|-----------------------------------------|--------------|-------------|-------------|---------------|--------------|--------|

|       | C2OUT                          | C1OUT                                   | C2INV        | C1INV       | CIS         | CM2           | CM1          | CM0    |

|       | bit 7                          |                                         |              |             |             |               |              | bit 0  |

|       |                                |                                         |              |             |             |               |              |        |

| bit 7 | <b>C2OUT</b> : Co              | omparator 2                             | Output bit   |             |             |               |              |        |

|       | When C2IN                      |                                         |              |             |             |               |              |        |

|       |                                | + > C2 VIN-                             |              |             |             |               |              |        |

|       | 0 = C2 VIN<br>When C2IN        | + < C2 VIN-                             |              |             |             |               |              |        |

|       |                                | $\overline{NV} = \bot$ .<br>+ < C2 VIN- |              |             |             |               |              |        |

|       | -                              | + > C2 VIN-                             |              |             |             |               |              |        |

| bit 6 | <b>C10UT</b> : Co              | omparator 1                             | Output bit   |             |             |               |              |        |

|       | When C1IN                      |                                         |              |             |             |               |              |        |

|       |                                | + > C1 VIN-                             |              |             |             |               |              |        |

|       |                                | + < C1 VIN-                             |              |             |             |               |              |        |

|       | <u>When C1IN</u><br>1 = C1 VIN | <u>NV = 1:</u><br>+ < C1 VIN-           |              |             |             |               |              |        |

|       |                                | + > C1 VIN-                             |              |             |             |               |              |        |

| bit 5 | C2INV: Co                      | mparator 2 (                            | Dutput Inver | sion bit    |             |               |              |        |

|       |                                | put inverted                            | ·            |             |             |               |              |        |

|       |                                | put not inver                           | ted          |             |             |               |              |        |

| bit 4 | C1INV: Co                      | mparator 1 (                            | Dutput Inver | sion bit    |             |               |              |        |

|       |                                | put inverted                            |              |             |             |               |              |        |

|       | -                              | put not inver                           |              |             |             |               |              |        |

| bit 3 | -                              | arator Input                            |              |             |             |               |              |        |

|       |                                | 2:CM0 = 110                             |              |             |             |               |              |        |

|       |                                | I- connects t                           |              |             |             |               |              |        |

|       | -                              | - connects t                            |              |             |             |               |              |        |

|       |                                | I- connects t                           |              |             |             |               |              |        |

| bit 2 | CM2:CM0:                       | Comparato                               | r Mode bits  |             |             |               |              |        |

|       | Figure 12-7                    | 1 shows the                             | Comparator   | modes and   | CM2:CM0     | bit settings. |              |        |

|       |                                |                                         |              |             |             |               |              |        |

|       | Legend:                        |                                         |              |             |             |               |              |        |

|       | R = Reada                      | ble bit                                 | W = W        | ritable bit | U = Unin    | nplemented    | bit, read as | 0'     |

|       | - n = Value                    | at POR                                  | '1' = B      | it is set   | '0' = Bit i | s cleared     | x = Bit is u | nknown |

|       |                                |                                         |              |             |             |               |              |        |

NOTES:

#### 17.2 DC Characteristics: PIC16F873A/874A/876A/877A (Industrial, Extended) PIC16LF873A/874A/876A/877A (Industrial)

| DC CHA       | DC CHARACTERISTICS |                                         |                    | $\begin{array}{l} \mbox{Standard Operating Conditions (unless otherwise stated)}\\ \mbox{Operating temperature} & -40^{\circ}C \leq TA \leq +85^{\circ}C \ \ for industrial \\ -40^{\circ}C \leq TA \leq +125^{\circ}C \ \ for extended \\ \mbox{Operating voltage VDD range as described in DC specification} \\ \mbox{(Section 17.1)} \end{array}$ |          |       |                                                             |  |  |  |

|--------------|--------------------|-----------------------------------------|--------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|-------|-------------------------------------------------------------|--|--|--|

| Param<br>No. | Sym                | Characteristic                          | Min                | Тур†                                                                                                                                                                                                                                                                                                                                                 | Max      | Units | Conditions                                                  |  |  |  |

|              | VIL                | Input Low Voltage                       |                    |                                                                                                                                                                                                                                                                                                                                                      |          |       |                                                             |  |  |  |

|              |                    | I/O ports:                              |                    |                                                                                                                                                                                                                                                                                                                                                      |          |       |                                                             |  |  |  |

| D030         |                    | with TTL buffer                         | Vss                | —                                                                                                                                                                                                                                                                                                                                                    | 0.15 Vdd | V     | For entire VDD range                                        |  |  |  |

| D030A        |                    |                                         | Vss                | —                                                                                                                                                                                                                                                                                                                                                    | 0.8V     | V     | $4.5V \le V\text{DD} \le 5.5V$                              |  |  |  |

| D031         |                    | with Schmitt Trigger buffer             | Vss                | —                                                                                                                                                                                                                                                                                                                                                    | 0.2 Vdd  | V     |                                                             |  |  |  |

| D032         |                    | MCLR, OSC1 (in RC mode)                 | Vss                | —                                                                                                                                                                                                                                                                                                                                                    | 0.2 Vdd  | V     |                                                             |  |  |  |

| D033         |                    | OSC1 (in XT and LP modes)               | Vss                | —                                                                                                                                                                                                                                                                                                                                                    | 0.3V     | V     | (Note 1)                                                    |  |  |  |

|              |                    | OSC1 (in HS mode)                       | Vss                | —                                                                                                                                                                                                                                                                                                                                                    | 0.3 Vdd  | V     |                                                             |  |  |  |

|              |                    | Ports RC3 and RC4:                      |                    | —                                                                                                                                                                                                                                                                                                                                                    |          |       |                                                             |  |  |  |

| D034         |                    | with Schmitt Trigger buffer             | Vss                | —                                                                                                                                                                                                                                                                                                                                                    | 0.3 Vdd  | V     | For entire VDD range                                        |  |  |  |

| D034A        |                    | with SMBus                              | -0.5               | —                                                                                                                                                                                                                                                                                                                                                    | 0.6      | V     | For VDD = 4.5 to 5.5V                                       |  |  |  |

|              | VIH                | Input High Voltage                      |                    |                                                                                                                                                                                                                                                                                                                                                      | -        |       |                                                             |  |  |  |

|              |                    | I/O ports:                              |                    | —                                                                                                                                                                                                                                                                                                                                                    |          |       |                                                             |  |  |  |

| D040         |                    | with TTL buffer                         | 2.0                | —                                                                                                                                                                                                                                                                                                                                                    | Vdd      | V     | $4.5V \leq V\text{DD} \leq 5.5V$                            |  |  |  |

| D040A        |                    |                                         | 0.25 VDD<br>+ 0.8V |                                                                                                                                                                                                                                                                                                                                                      | Vdd      | V     | For entire VDD range                                        |  |  |  |

| D041         |                    | with Schmitt Trigger buffer             | 0.8 Vdd            | —                                                                                                                                                                                                                                                                                                                                                    | Vdd      | V     | For entire VDD range                                        |  |  |  |

| D042         |                    | MCLR                                    | 0.8 Vdd            | —                                                                                                                                                                                                                                                                                                                                                    | Vdd      | V     |                                                             |  |  |  |

| D042A        |                    | OSC1 (in XT and LP modes)               | 1.6V               | —                                                                                                                                                                                                                                                                                                                                                    | Vdd      | V     | (Note 1)                                                    |  |  |  |

|              |                    | OSC1 (in HS mode)                       | 0.7 Vdd            | —                                                                                                                                                                                                                                                                                                                                                    | Vdd      | V     |                                                             |  |  |  |

| D043         |                    | OSC1 (in RC mode)                       | 0.9 Vdd            | —                                                                                                                                                                                                                                                                                                                                                    | Vdd      | V     |                                                             |  |  |  |

|              |                    | Ports RC3 and RC4:                      |                    |                                                                                                                                                                                                                                                                                                                                                      |          |       |                                                             |  |  |  |

| D044         |                    | with Schmitt Trigger buffer             | 0.7 Vdd            | —                                                                                                                                                                                                                                                                                                                                                    | Vdd      | V     | For entire VDD range                                        |  |  |  |

| D044A        |                    | with SMBus                              | 1.4                | —                                                                                                                                                                                                                                                                                                                                                    | 5.5      | V     | For VDD = 4.5 to 5.5V                                       |  |  |  |

| D070         | Ipurb              | PORTB Weak Pull-up Current              | 50                 | 250                                                                                                                                                                                                                                                                                                                                                  | 400      | μA    | Vdd = 5V, Vpin = Vss,<br>-40°С то +85°С                     |  |  |  |

|              | lı∟                | Input Leakage Current <sup>(2, 3)</sup> |                    |                                                                                                                                                                                                                                                                                                                                                      |          |       |                                                             |  |  |  |

| D060         |                    | I/O ports                               | _                  | _                                                                                                                                                                                                                                                                                                                                                    | ±1       | μA    | $Vss \le VPIN \le VDD,$ pin at high-impedance               |  |  |  |

| D061         |                    | MCLR, RA4/T0CKI                         | _                  | —                                                                                                                                                                                                                                                                                                                                                    | ±5       | μA    | $Vss \leq V \text{PIN} \leq V \text{DD}$                    |  |  |  |

| D063         |                    | OSC1                                    | _                  | —                                                                                                                                                                                                                                                                                                                                                    | ±5       | μA    | Vss $\leq$ VPIN $\leq$ VDD, XT, HS and LP osc configuration |  |  |  |

† Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

Note 1: In RC oscillator configuration, the OSC1/CLKI pin is a Schmitt Trigger input. It is not recommended that the PIC16F87XA be driven with external clock in RC mode.

2: The leakage current on the MCLR pin is strongly dependent on the applied voltage level. The specified levels represent normal operating conditions. Higher leakage current may be measured at different input voltages.

3: Negative current is defined as current sourced by the pin.

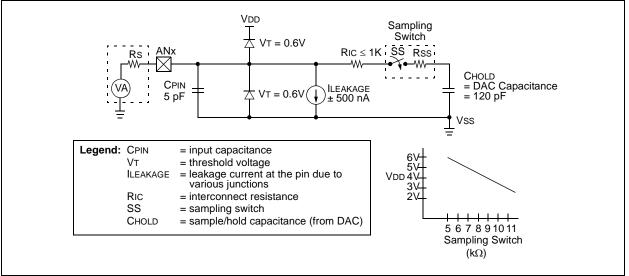

| TABLE 17-3: | EXTERNAL | CLOCK TIMING REQUIREMENTS |

|-------------|----------|---------------------------|

|-------------|----------|---------------------------|

| Param<br>No. | Symbol            | Characteristic                   | Min    | Тур† | Max       | Units       | Conditions                 |

|--------------|-------------------|----------------------------------|--------|------|-----------|-------------|----------------------------|

|              | Fosc              | External CLKI Frequency          | DC     | _    | 1         | MHz         | XT and RC Osc mode         |

|              |                   | (Note 1)                         | DC     | _    | 20        | MHz         | HS Osc mode                |

|              |                   |                                  | DC     | _    | 32        | kHz         | LP Osc mode                |

|              |                   | Oscillator Frequency             | DC     | _    | 4         | MHz         | RC Osc mode                |

|              |                   | (Note 1)                         | 0.1    | —    | 4         | MHz         | XT Osc mode                |

|              |                   |                                  | 4<br>5 | _    | 20<br>200 | MHz<br>kHz  | HS Osc mode<br>LP Osc mode |

| 1            | Tosc              | External CLKI Period             | 1000   | _    |           | ns          | XT and RC Osc mode         |

|              | (Note 1)          | 50                               | _      | _    | ns        | HS Osc mode |                            |

|              |                   | 5                                | —      | —    | μS        | LP Osc mode |                            |

|              | Oscillator Period | 250                              | —      | —    | ns        | RC Osc mode |                            |

|              |                   | (Note 1)                         | 250    | —    | 1         | μS          | XT Osc mode                |

|              |                   |                                  | 100    | —    | 250       | ns          | HS Osc mode                |

|              |                   |                                  | 50     | —    | 250       | ns          | HS Osc mode                |

|              |                   |                                  | 31.25  |      | —         | μS          | LP Osc mode                |

| 2            | Тсү               | Instruction Cycle Time (Note 1)  | 200    | Тсү  | DC        | ns          | Tcy = 4/Fosc               |

| 3            | TosL,             | External Clock in (OSC1) High or | 100    | —    | —         | ns          | XT oscillator              |

|              | TosH              | Low Time                         | 2.5    | —    | —         | μS          | LP oscillator              |

|              |                   |                                  | 15     |      | —         | ns          | HS oscillator              |

| 4            | TosR,             | External Clock in (OSC1) Rise or | _      |      | 25        | ns          | XT oscillator              |

|              | TosF              | Fall Time                        | —      | —    | 50        | ns          | LP oscillator              |

|              |                   |                                  | —      | _    | 15        | ns          | HS oscillator              |

† Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

**Note 1:** Instruction cycle period (TCY) equals four times the input oscillator time base period. All specified values are based on characterization data for that particular oscillator type, under standard operating conditions, with the device executing code. Exceeding these specified limits may result in an unstable oscillator operation and/or higher than expected current consumption. All devices are tested to operate at "min." values with an external clock applied to the OSC1/CLKI pin. When an external clock input is used, the "max." cycle time limit is "DC" (no clock) for all devices.

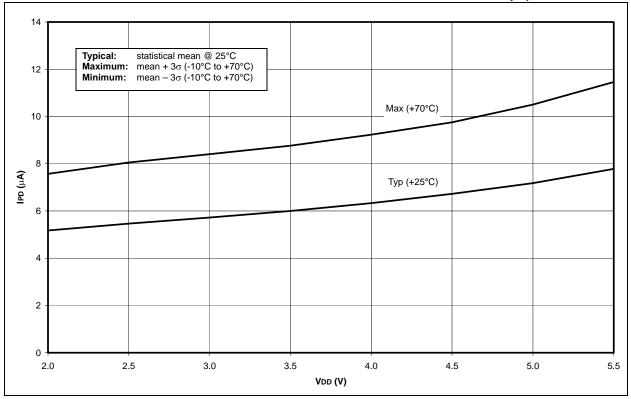

# FIGURE 18-11: TYPICAL AND MAXIMUM $\triangle$ ITMR1 vs. VDD OVER TEMPERATURE (-10°C TO +70°C, TIMER1 WITH OSCILLATOR, XTAL = 32 kHz, C1 AND C2 = 47 pF)

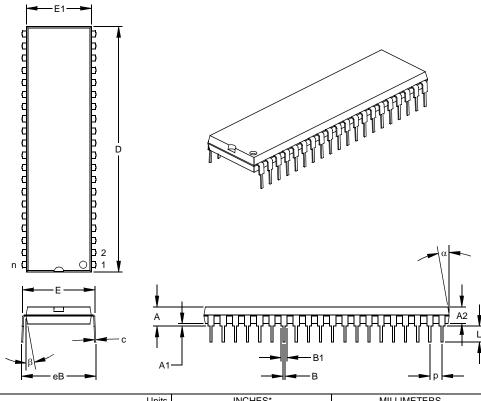

### 40-Lead Plastic Dual In-line (P) - 600 mil (PDIP)

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

|                            | Units    | INCHES* |       | MILLIMETERS |       |       |       |

|----------------------------|----------|---------|-------|-------------|-------|-------|-------|

| Dimensio                   | n Limits | MIN     | NOM   | MAX         | MIN   | NOM   | MAX   |

| Number of Pins             | n        |         | 40    |             |       | 40    |       |

| Pitch                      | р        |         | .100  |             |       | 2.54  |       |

| Top to Seating Plane       | А        | .160    | .175  | .190        | 4.06  | 4.45  | 4.83  |

| Molded Package Thickness   | A2       | .140    | .150  | .160        | 3.56  | 3.81  | 4.06  |

| Base to Seating Plane      | A1       | .015    |       |             | 0.38  |       |       |

| Shoulder to Shoulder Width | E        | .595    | .600  | .625        | 15.11 | 15.24 | 15.88 |

| Molded Package Width       | E1       | .530    | .545  | .560        | 13.46 | 13.84 | 14.22 |

| Overall Length             | D        | 2.045   | 2.058 | 2.065       | 51.94 | 52.26 | 52.45 |

| Tip to Seating Plane       | L        | .120    | .130  | .135        | 3.05  | 3.30  | 3.43  |

| Lead Thickness             | С        | .008    | .012  | .015        | 0.20  | 0.29  | 0.38  |

| Upper Lead Width           | B1       | .030    | .050  | .070        | 0.76  | 1.27  | 1.78  |

| Lower Lead Width           | В        | .014    | .018  | .022        | 0.36  | 0.46  | 0.56  |

| Overall Row Spacing §      | eB       | .620    | .650  | .680        | 15.75 | 16.51 | 17.27 |

| Mold Draft Angle Top       | α        | 5       | 10    | 15          | 5     | 10    | 15    |

| Mold Draft Angle Bottom    | β        | 5       | 10    | 15          | 5     | 10    | 15    |

\* Controlling Parameter § Significant Characteristic

Notes:

Dimensions D and E1 do not include mold flash or protrusions. Mold flash or protrusions shall not exceed

.010" (0.254mm) per side. JEDEC Equivalent: MO-011

Drawing No. C04-016

## APPENDIX C: CONVERSION CONSIDERATIONS

Considerations for converting from previous versions of devices to the ones listed in this data sheet are listed in Table C-1.

| TABLE C-1: CONVERSION CONSIDERATION |

|-------------------------------------|

|-------------------------------------|

| Characteristic                     | PIC16C7X                                         | PIC16F87X                                               | PIC16F87XA                                               |

|------------------------------------|--------------------------------------------------|---------------------------------------------------------|----------------------------------------------------------|

| Pins                               | 28/40                                            | 28/40                                                   | 28/40                                                    |

| Timers                             | 3                                                | 3                                                       | 3                                                        |

| Interrupts                         | 11 or 12                                         | 13 or 14                                                | 14 or 15                                                 |

| Communication                      | PSP, USART, SSP<br>(SPI, I <sup>2</sup> C Slave) | PSP, USART, SSP<br>(SPI, I <sup>2</sup> C Master/Slave) | PSP, USART, SSP<br>(SPI, I <sup>2</sup> C Master/Slave)  |

| Frequency                          | 20 MHz                                           | 20 MHz                                                  | 20 MHz                                                   |

| Voltage                            | 2.5V-5.5V                                        | 2.2V-5.5V                                               | 2.0V-5.5V                                                |

| A/D                                | 8-bit,<br>4 conversion clock selects             | 10-bit,<br>4 conversion clock selects                   | 10-bit,<br>7 conversion clock selects                    |

| CCP                                | 2                                                | 2                                                       | 2                                                        |

| Comparator                         | _                                                | _                                                       | 2                                                        |

| Comparator Voltage<br>Reference    | _                                                | _                                                       | Yes                                                      |

| Program Memory                     | 4K, 8K EPROM                                     | 4K, 8K Flash<br>(Erase/Write on<br>single-word)         | 4K, 8K Flash<br>(Erase/Write on<br>four-word blocks)     |

| RAM                                | 192, 368 bytes                                   | 192, 368 bytes                                          | 192, 368 bytes                                           |

| EEPROM Data                        | None                                             | 128, 256 bytes                                          | 128, 256 bytes                                           |

| Code Protection                    | On/Off                                           | Segmented, starting at end<br>of program memory         | On/Off                                                   |

| Program Memory<br>Write Protection | _                                                | On/Off                                                  | Segmented, starting at<br>beginning of<br>program memory |

| Other                              |                                                  | In-Circuit Debugger,<br>Low-Voltage Programming         | In-Circuit Debugger,<br>Low-Voltage Programming          |

| I <sup>2</sup> C Bus Data191                                  | 1 |

|---------------------------------------------------------------|---|

|                                                               |   |

| I <sup>2</sup> C Bus Start/Stop Bits                          |   |

| I <sup>2</sup> C Master Mode (Reception, 7-bit Address)       | 3 |

| I <sup>2</sup> C Master Mode (Transmission,                   |   |

| 7 or 10-bit Address)102                                       |   |

| I <sup>2</sup> C Slave Mode (Transmission, 10-bit Address) 89 | 9 |

| I <sup>2</sup> C Slave Mode (Transmission, 7-bit Address)87   | 7 |

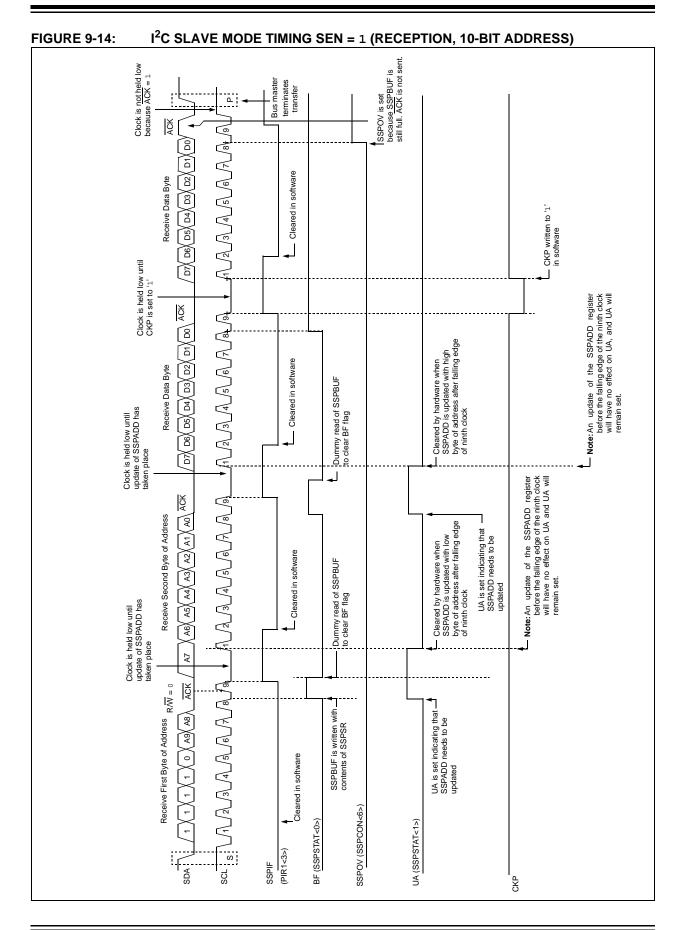

| $I^2C$ Slave Mode with SEN = 1 (Reception,                    |   |

| 10-bit Address)93                                             | 3 |

| $I^2C$ Slave Mode with SEN = 0 (Reception,                    | - |

| 10-bit Address)                                               | ρ |

| $I^{2}C$ Slave Mode with SEN = 0 (Reception,                  | 5 |

|                                                               | ~ |

| 7-bit Address)                                                | D |

| $I^2C$ Slave Mode with SEN = 1 (Reception,                    | _ |

| 7-bit Address)92                                              |   |

| Parallel Slave Port (PIC16F874A/877A Only)                    |   |

| Parallel Slave Port (PSP) Read52                              | 2 |

| Parallel Slave Port (PSP) Write                               | 2 |

| Repeat Start Condition                                        |   |

| Reset, Watchdog Timer, Start-up Timer                         |   |

| and Power-up Timer                                            | 4 |

| Slave Mode General Call Address Sequence                      |   |

| (7 or 10-bit Address Mode)                                    | 4 |

|                                                               |   |

| Slave Synchronization                                         | ( |

| Slow Rise Time (MCLR Tied to VDD via                          | _ |

| RC Network)152                                                |   |

| SPI Master Mode (CKE = 0, SMP = 0)                            | 8 |

| SPI Master Mode (CKE = 1, SMP = 1)                            | В |

| SPI Mode (Master Mode)76                                      | ô |

| SPI Mode (Slave Mode with CKE = 0)78                          | 8 |

| SPI Mode (Slave Mode with CKE = 1)78                          |   |

| SPI Slave Mode (CKE = 0)                                      |   |

| SPI Slave Mode (CKE = 1)                                      | 9 |

| Stop Condition Receive or Transmit Mode                       |   |

| Synchronous Reception                                         | Ŧ |

|                                                               |   |

| (Master Mode, SREN) 124                                       |   |

| Synchronous Transmission                                      |   |

| Synchronous Transmission (Through TXEN)                       | 2 |

| Time-out Sequence on Power-up                                 |   |

| (MCLR Not Tied to VDD)                                        |   |

| Case 1 152                                                    | 2 |

| Case 2 152                                                    | 2 |

| Time-out Sequence on Power-up (MCLR Tied                      |   |

| to VDD via RC Network)151                                     | 1 |

| Timer0 and Timer1 External Clock                              |   |

| USART Synchronous Receive                                     |   |

| (Master/Slave)                                                | R |

| USART Synchronous Transmission                                | 0 |

|                                                               | 0 |

| (Master/Slave)                                                |   |

| Wake-up from Sleep via Interrupt                              |   |

| Timing Parameter Symbology                                    |   |

| TMR0 Register                                                 |   |

| TMR1CS Bit                                                    |   |

| TMR1H Register19                                              |   |

| TMR1L Register                                                | 9 |

| TMR1ON Bit                                                    |   |

| TMR2 Register                                                 | 9 |

| TMR2ON Bit61                                                  |   |

| TMRO Register                                                 |   |

| TOUTPS0 Bit                                                   |   |

| TOUTPS1 Bit                                                   |   |

| TOUTPS2 Bit                                                   |   |

| TOUTPS2 Bit                                                   |   |

|                                                               |   |

| TRISA Register                                                | J |

| TRISB Register | 20  |

|----------------|-----|

| TRISC Register |     |

| TRISD Register |     |

| TRISE Register | 20  |

| IBF Bit        | 50  |

| IBOV Bit       | 50  |

| OBF Bit        | 50  |

| PSPMODE Bit    |     |

| TXREG Register | 19  |

| TXSTA Register |     |

| BRGH Bit       | 111 |

| CSRC Bit       | 111 |

| SYNC Bit       | 111 |

| TRMT Bit       | 111 |

| TX9 Bit        |     |

| TX9D Bit       | 111 |

| TXEN Bit       | 111 |

# U

| USART 1                                   | 11 |

|-------------------------------------------|----|

| Address Detect Enable (ADDEN Bit) 1       |    |

| Asynchronous Mode 1                       |    |

| Asynchronous Receive (9-bit Mode) 1       |    |

| Asynchronous Receive with Address Detect. |    |

| See Asynchronous Receive (9-bit Mode).    |    |

| Asynchronous Receiver                     | 17 |

| Asynchronous Reception1                   |    |

| Asynchronous Transmitter1                 |    |

| Baud Rate Generator (BRG) 1               |    |

| Baud Rate Formula 1                       |    |

| Baud Rates, Asynchronous Mode             | -  |

| (BRGH = 0)                                | 14 |

| Baud Rates, Asynchronous Mode             |    |

| (BRGH = 1) 1                              | 14 |

| High Baud Rate Select (BRGH Bit) 1        |    |

| Sampling 1                                |    |

| Clock Source Select (CSRC Bit) 1          |    |

| Continuous Receive Enable (CREN Bit) 1    |    |

| Framing Error (FERR Bit) 1                |    |

| Mode Select (SYNC Bit) 1                  |    |

| Overrun Error (OERR Bit) 1                |    |

| Receive Data, 9th Bit (RX9D Bit) 1        |    |

| Receive Enable, 9-bit (RX9 Bit) 1         |    |

| Serial Port Enable (SPEN Bit)111, 1       |    |

| Single Receive Enable (SREN Bit) 1        |    |

| Synchronous Master Mode 1                 |    |

| Synchronous Master Reception 1            |    |

| Synchronous Master Transmission1          |    |

| Synchronous Slave Mode 1                  | 24 |

| Synchronous Slave Reception1              |    |

| Synchronous Slave Transmit 1              |    |

| Transmit Data, 9th Bit (TX9D) 1           |    |

| Transmit Enable (TXEN Bit) 1              |    |

| Transmit Enable, 9-bit (TX9 Bit) 1        |    |

| Transmit Shift Register Status (TRMT Bit) |    |

| USART Synchronous Receive Requirements    |    |

| V                                         |    |

| V                                         |    |

|                                           |    |

| VDD Pin                          |     |

|----------------------------------|-----|

| Voltage Reference Specifications | 180 |

| Vss Pin                          |     |

### READER RESPONSE

It is our intention to provide you with the best documentation possible to ensure successful use of your Microchip product. If you wish to provide your comments on organization, clarity, subject matter, and ways in which our documentation can better serve you, please FAX your comments to the Technical Publications Manager at (480) 792-4150.

Please list the following information, and use this outline to provide us with your comments about this document.

| TO:<br>RE: | Technical Publications Manager<br>Reader Response                            | Total Pages Sent                  |  |  |

|------------|------------------------------------------------------------------------------|-----------------------------------|--|--|

| From       | 1: Name                                                                      |                                   |  |  |

|            | Company                                                                      |                                   |  |  |

|            | Address                                                                      |                                   |  |  |

|            | City / State / ZIP / Country                                                 |                                   |  |  |

|            | Telephone: ()                                                                | FAX: ()                           |  |  |

| Appli      | ication (optional):                                                          |                                   |  |  |

| Wou        | ld you like a reply?YN                                                       |                                   |  |  |

| Devi       | ce: PIC16F87XA                                                               | Literature Number: DS39582C       |  |  |

| Ques       | stions:                                                                      |                                   |  |  |

| 1. V       | What are the best features of this document?                                 |                                   |  |  |

| -          |                                                                              |                                   |  |  |

| 2. H       | How does this document meet your hardware and software                       | re development needs?             |  |  |

| _          |                                                                              |                                   |  |  |

| -<br>3. E  | . Do you find the organization of this document easy to follow? If not, why? |                                   |  |  |

| _          |                                                                              |                                   |  |  |

| -          |                                                                              |                                   |  |  |

| 4. V       | What additions to the document do you think would enhar                      | nce the structure and subject?    |  |  |

| -          |                                                                              |                                   |  |  |

| 5. V       | What deletions from the document could be made without                       | affecting the overall usefulness? |  |  |

|            |                                                                              |                                   |  |  |

| 6. l       | s there any incorrect or misleading information (what and                    | where)?                           |  |  |

| -          |                                                                              |                                   |  |  |

| 7. H       | How would you improve this document?                                         |                                   |  |  |

| -          |                                                                              |                                   |  |  |

DS39582C-page 230