Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                           |

|----------------------------|---------------------------------------------------------------------------|

| Product Status             | Active                                                                    |

| Core Processor             | PIC                                                                       |

| Core Size                  | 8-Bit                                                                     |

| Speed                      | 20MHz                                                                     |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                         |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                     |

| Number of I/O              | 22                                                                        |

| Program Memory Size        | 14KB (8K x 14)                                                            |

| Program Memory Type        | FLASH                                                                     |

| EEPROM Size                | 256 x 8                                                                   |

| RAM Size                   | 368 x 8                                                                   |

| Voltage - Supply (Vcc/Vdd) | 4V ~ 5.5V                                                                 |

| Data Converters            | A/D 5x10b                                                                 |

| Oscillator Type            | External                                                                  |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                        |

| Mounting Type              | Surface Mount                                                             |

| Package / Case             | 28-SOIC (0.295", 7.50mm Width)                                            |

| Supplier Device Package    | 28-SOIC                                                                   |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16f876a-e-so |

|                            |                                                                           |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| Address | Name   | Bit 7 | Bit 6 | Bit 5 | Bit 4   | Bit 3 | Bit 2   | Bit 1       | Bit 0     | Value on:<br>POR, BOR | Value on<br>all other<br>Resets |

|---------|--------|-------|-------|-------|---------|-------|---------|-------------|-----------|-----------------------|---------------------------------|

| 09h     | PORTE  | —     | —     | _     | —       |       | RE2     | RE1         | RE0       | xxx                   | uuu                             |

| 89h     | TRISE  | IBF   | OBF   | IBOV  | PSPMODE | —     | PORTE D | Data Direct | tion bits | 0000 -111             | 0000 -111                       |

| 9Fh     | ADCON1 | ADFM  | ADCS2 | _     | —       | PCFG3 | PCFG2   | PCFG1       | PCFG0     | 00 0000               | 00 0000                         |

#### **TABLE 4-10:** SUMMARY OF REGISTERS ASSOCIATED WITH PORTE

Legend: x = unknown, u = unchanged, - = unimplemented, read as '0'. Shaded cells are not used by PORTE.

#### **REGISTER 4-1: TRISE REGISTER (ADDRESS 89h)**

| R-0   | R-0 | R/W-0 | R/W-0   | U-0 | R/W-1 | R/W-1 | R/W-1 |

|-------|-----|-------|---------|-----|-------|-------|-------|

| IBF   | OBF | IBOV  | PSPMODE | —   | Bit 2 | Bit 1 | Bit 0 |

| bit 7 |     |       |         |     |       |       | bit 0 |

#### Parallel Slave Port Status/Control Bits:

| bit 7 | IBF: Input Buffer Full Stat                           | tus bit                              |                      |                        |

|-------|-------------------------------------------------------|--------------------------------------|----------------------|------------------------|

|       | 1 = A word has been rece                              | eived and is waiting to              | be read by the CPU   |                        |

|       | 0 = No word has been re-                              | ceived                               |                      |                        |

| bit 6 | <b>OBF</b> : Output Buffer Full                       | Status bit                           |                      |                        |

|       | 1 = The output buffer still                           | holds a previously wri               | tten word            |                        |

|       | 0 = The output buffer has                             | been read                            |                      |                        |

| bit 5 | IBOV: Input Buffer Overf                              | low Detect bit (in Micro             | processor mode)      |                        |

|       | <ol> <li>A write occurred wh<br/>software)</li> </ol> | en a previously input                | word has not been re | ad (must be cleared in |

|       | 0 = No overflow occurred                              | b                                    |                      |                        |

| bit 4 | PSPMODE: Parallel Slav                                | e Port Mode Select bit               |                      |                        |

|       | 1 = PORTD functions in F                              | Parallel Slave Port mo               | de                   |                        |

|       | 0 = PORTD functions in g                              | general purpose I/O m                | ode                  |                        |

| bit 3 | Unimplemented: Read a                                 | <b>as</b> '0'                        |                      |                        |

|       | PORTE Data Direction E                                | <u>Bits:</u>                         |                      |                        |

| bit 2 | Bit 2: Direction Control bi                           | it for pin RE2/ $\overline{CS}$ /AN7 |                      |                        |

|       | 1 = Input                                             |                                      |                      |                        |

|       | 0 = Output                                            |                                      |                      |                        |

| bit 1 | Bit 1: Direction Control bi                           | it for pin RE1/WR/AN6                |                      |                        |

|       | 1 = Input                                             |                                      |                      |                        |

|       | 0 = Output                                            |                                      |                      |                        |

| bit 0 | Bit 0: Direction Control bi                           | it for pin RE0/RD/AN5                |                      |                        |

|       | 1 = Input                                             |                                      |                      |                        |

|       | 0 = Output                                            |                                      |                      |                        |

|       |                                                       |                                      |                      |                        |

|       | Legend:                                               |                                      |                      |                        |

|       | R = Readable bit                                      | W = Writable bit                     | U = Unimplemented    | bit, read as '0'       |

|       | - n = Value at POR                                    | '1' = Bit is set                     | '0' = Bit is cleared | x = Bit is unknown     |

|       | L                                                     |                                      |                      |                        |

#### 5.2 Using Timer0 with an External Clock

When no prescaler is used, the external clock input is the same as the prescaler output. The synchronization of T0CKI with the internal phase clocks is accomplished by sampling the prescaler output on the Q2 and Q4 cycles of the internal phase clocks. Therefore, it is necessary for T0CKI to be high for at least 2 Tosc (and a small RC delay of 20 ns) and low for at least 2 Tosc (and a small RC delay of 20 ns). Refer to the electrical specification of the desired device.

#### 5.3 Prescaler

REGISTER 5-1:

There is only one prescaler available which is mutually exclusively shared between the Timer0 module and the Watchdog Timer. A prescaler assignment for the

**OPTION REG REGISTER**

Timer0 module means that there is no prescaler for the Watchdog Timer and vice versa. This prescaler is not readable or writable (see Figure 5-1).

The PSA and PS2:PS0 bits (OPTION\_REG<3:0>) determine the prescaler assignment and prescale ratio.

When assigned to the Timer0 module, all instructions writing to the TMR0 register (e.g., CLRF1, MOVWF1, BSF1, x....etc.) will clear the prescaler. When assigned to WDT, a CLRWDT instruction will clear the prescaler along with the Watchdog Timer. The prescaler is not readable or writable.

Note: Writing to TMR0 when the prescaler is assigned to Timer0 will clear the prescaler count, but will not change the prescaler assignment.

| . (                                         |                                                                                     | REG REGI                                                                   | SIER         |               |                   |            |               |            |  |  |

|---------------------------------------------|-------------------------------------------------------------------------------------|----------------------------------------------------------------------------|--------------|---------------|-------------------|------------|---------------|------------|--|--|

| _                                           | R/W-1                                                                               | R/W-1                                                                      | R/W-1        | R/W-1         | R/W-1             | R/W-1      | R/W-1         | R/W-1      |  |  |

|                                             | RBPU                                                                                | INTEDG                                                                     | TOCS         | TOSE          | PSA               | PS2        | PS1           | PS0        |  |  |

| _                                           | bit 7                                                                               |                                                                            |              |               |                   |            |               | bit 0      |  |  |

|                                             | RBPU                                                                                |                                                                            |              |               |                   |            |               |            |  |  |

|                                             | INTEDG                                                                              |                                                                            |              |               |                   |            |               |            |  |  |

|                                             | TOCS: TM                                                                            | R0 Clock So                                                                | urce Selec   | t bit         |                   |            |               |            |  |  |

|                                             |                                                                                     | tion on T0CK                                                               | •            |               |                   |            |               |            |  |  |

| 0 = Internal instruction cycle clock (CLKO) |                                                                                     |                                                                            |              |               |                   |            |               |            |  |  |

|                                             |                                                                                     | R0 Source E                                                                | •            |               |                   |            |               |            |  |  |

|                                             |                                                                                     | nent on high-f<br>nent on low-to                                           |              |               |                   |            |               |            |  |  |

|                                             | PSA: Pres                                                                           | PSA: Prescaler Assignment bit                                              |              |               |                   |            |               |            |  |  |

|                                             |                                                                                     | escaler is assigned to the WDT<br>escaler is assigned to the Timer0 module |              |               |                   |            |               |            |  |  |

|                                             | PS2:PS0:                                                                            | Prescaler Ra                                                               | ate Select b | oits          |                   |            |               |            |  |  |

|                                             | Bit Value                                                                           | TMR0 Rate                                                                  | WDT Rate     | 1             |                   |            |               |            |  |  |

|                                             | 000                                                                                 | 1:2                                                                        | 1:1          | -             |                   |            |               |            |  |  |

|                                             | 001                                                                                 | 1:4<br>1:8                                                                 | 1:2          |               |                   |            |               |            |  |  |

|                                             | 010<br>011                                                                          | 1:0                                                                        | 1:4          |               |                   |            |               |            |  |  |

|                                             | 100                                                                                 | 1:32                                                                       | 1:16         |               |                   |            |               |            |  |  |

|                                             | 101                                                                                 | 1:64                                                                       | 1:32         |               |                   |            |               |            |  |  |

|                                             | 110                                                                                 | 1:128                                                                      | 1:64         |               |                   |            |               |            |  |  |

|                                             | 111                                                                                 | 1 : 256                                                                    | 1 : 128      |               |                   |            |               |            |  |  |

| Γ                                           | Legend:                                                                             |                                                                            |              |               |                   |            |               |            |  |  |

|                                             | R = Readable bit W =                                                                |                                                                            |              | Vritable bit  | U = Unimpl        | emented b  | it, read as ' | C'         |  |  |

|                                             | - n = Value at POR $(1)^2$ = Bit is set $(0)^2$ = Bit is cleared x = Bit is unknown |                                                                            |              |               |                   |            |               |            |  |  |

| Γ                                           | Note:                                                                               | To avoid an                                                                | unintende    | device Re     | set, the instruct | ion sequer | nce shown i   | n the PIC® |  |  |

|                                             | 1016.                                                                               | Mid-Range                                                                  | MCU Fam      | ily Reference | t from Timer0 t   | 33023) mu  | ist be exec   | uted when  |  |  |

be followed even if the WDT is disabled.

NOTES:

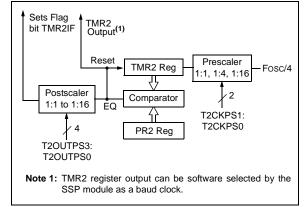

### 7.0 TIMER2 MODULE

Timer2 is an 8-bit timer with a prescaler and a postscaler. It can be used as the PWM time base for the PWM mode of the CCP module(s). The TMR2 register is readable and writable and is cleared on any device Reset.

The input clock (Fosc/4) has a prescale option of 1:1, 1:4 or 1:16, selected by control bits T2CKPS1:T2CKPS0 (T2CON<1:0>).

The Timer2 module has an 8-bit period register, PR2. Timer2 increments from 00h until it matches PR2 and then resets to 00h on the next increment cycle. PR2 is a readable and writable register. The PR2 register is initialized to FFh upon Reset.

The match output of TMR2 goes through a 4-bit postscaler (which gives a 1:1 to 1:16 scaling inclusive) to generate a TMR2 interrupt (latched in flag bit, TMR2IF (PIR1<1>)).

Timer2 can be shut-off by clearing control bit, TMR2ON (T2CON<2>), to minimize power consumption.

Register 7-1 shows the Timer2 Control register.

Additional information on timer modules is available in the PIC<sup>®</sup> Mid-Range MCU Family Reference Manual (DS33023).

#### FIGURE 7-1: TIMER2 BLOCK DIAGRAM

#### REGISTER 7-1: T2CON: TIMER2 CONTROL REGISTER (ADDRESS 12h)

| ER 7-1: | T2CON: T                                                                                           | IMER2 CC     | NTROL R         | EGISTER      | (ADDRESS      | 5 12h)    |              |         |  |

|---------|----------------------------------------------------------------------------------------------------|--------------|-----------------|--------------|---------------|-----------|--------------|---------|--|

|         | U-0                                                                                                | R/W-0        | R/W-0           | R/W-0        | R/W-0         | R/W-0     | R/W-0        | R/W-0   |  |

|         |                                                                                                    | TOUTPS3      | TOUTPS2         | TOUTPS1      | TOUTPS0       | TMR2ON    | T2CKPS1      | T2CKPS0 |  |

|         | bit 7                                                                                              |              |                 |              |               |           |              | bit 0   |  |

| bit 7   | Unimplem                                                                                           | nented: Rea  | <b>d as</b> '0' |              |               |           |              |         |  |

| bit 6-3 | TOUTPS3                                                                                            | :TOUTPS0:    | Timer2 Out      | put Postsca  | e Select bits |           |              |         |  |

|         | 0000 = 1:1 postscale<br>0001 = 1:2 postscale<br>0010 = 1:3 postscale<br>•<br>•<br>•<br>•<br>•<br>• |              |                 |              |               |           |              |         |  |

|         | 1111 <b>= 1</b> :1                                                                                 | 16 postscale |                 |              |               |           |              |         |  |

| bit 2   | TMR2ON:                                                                                            | Timer2 On I  | oit             |              |               |           |              |         |  |

|         | 1 = Timer2<br>0 = Timer2                                                                           |              |                 |              |               |           |              |         |  |

| bit 1-0 | T2CKPS1                                                                                            | :T2CKPS0:    | Timer2 Cloc     | k Prescale   | Select bits   |           |              |         |  |

|         | 00 = Preso<br>01 = Preso<br>1x = Preso                                                             | caler is 4   |                 |              |               |           |              |         |  |

|         | Logondi                                                                                            |              |                 |              |               |           |              |         |  |

|         | Legend:                                                                                            |              | 147 14          |              |               |           |              | (O)     |  |

|         | R = Reada                                                                                          |              |                 | Vritable bit |               | -         | bit, read as |         |  |

|         | - n = Value                                                                                        | e at POR     | `1 <i>`</i> = E | Bit is set   | 0' = Bit is   | s cleared | x = Bit is u | nknown  |  |

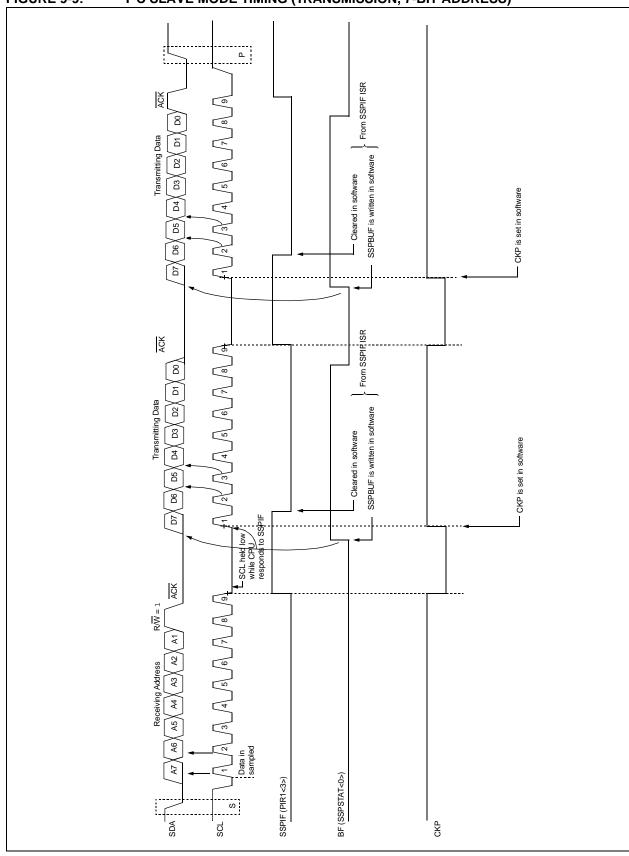

I<sup>2</sup>C SLAVE MODE TIMING (TRANSMISSION, 7-BIT ADDRESS)

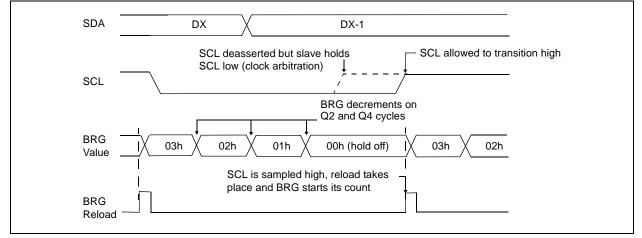

#### 9.4.7.1 Clock Arbitration

Clock arbitration occurs when the master, during any receive, transmit or Repeated Start/Stop condition, deasserts the SCL pin (SCL allowed to float high). When the SCL pin is allowed to float high, the Baud Rate Generator (BRG) is suspended from counting until the SCL pin is actually sampled high. When the

SCL pin is sampled high, the Baud Rate Generator is reloaded with the contents of SSPADD<6:0> and begins counting. This ensures that the SCL high time will always be at least one BRG rollover count, in the event that the clock is held low by an external device (Figure 9-17).

#### 9.4.10 I<sup>2</sup>C MASTER MODE TRANSMISSION

Transmission of a data byte, a 7-bit address or the other half of a 10-bit address is accomplished by simply writing a value to the SSPBUF register. This action will set the Buffer Full flag bit, BF, and allow the Baud Rate Generator to begin counting and start the next transmission. Each bit of address/data will be shifted out onto the SDA pin after the falling edge of SCL is asserted (see data hold time specification, parameter #106). SCL is held low for one Baud Rate Generator rollover count (TBRG). Data should be valid before SCL is released high (see data setup time specification, parameter #107). When the SCL pin is released high, it is held that way for TBRG. The data on the SDA pin must remain stable for that duration and some hold time after the next falling edge of SCL. After the eighth bit is shifted out (the falling edge of the eighth clock), the BF flag is cleared and the master releases SDA. This allows the slave device being addressed to respond with an ACK bit during the ninth bit time, if an address match occurred or if data was received properly. The status of ACK is written into the ACKDT bit on the falling edge of the ninth clock. If the master receives an Acknowledge, the Acknowledge Status bit, ACKSTAT, is cleared. If not, the bit is set. After the ninth clock, the SSPIF bit is set and the master clock (Baud Rate Generator) is suspended until the next data byte is loaded into the SSPBUF, leaving SCL low and SDA unchanged (Figure 9-21).

After the write to the SSPBUF, each bit of address will be shifted out on the falling edge of SCL, until all seven address bits and the R/W bit are completed. On the falling edge of the eighth clock, the master will deassert the SDA pin, allowing the slave to respond with an Acknowledge. On the falling edge of the ninth clock, the master will sample the SDA pin to see if the address was recognized by a slave. The status of the ACK bit is loaded into the ACKSTAT status bit (SSPCON2<6>). Following the falling edge of the ninth clock transmission of the address, the SSPIF is set, the BF flag is cleared and the Baud Rate Generator is turned off until another write to the SSPBUF takes place, holding SCL low and allowing SDA to float.

#### 9.4.10.1 BF Status Flag

In Transmit mode, the BF bit (SSPSTAT<0>) is set when the CPU writes to SSPBUF and is cleared when all eight bits are shifted out.

#### 9.4.10.2 WCOL Status Flag

If the user writes the SSPBUF when a transmit is already in progress (i.e., SSPSR is still shifting out a data byte), the WCOL is set and the contents of the buffer are unchanged (the write doesn't occur).

WCOL must be cleared in software.

#### 9.4.10.3 ACKSTAT Status Flag

In Transmit mode, the ACKSTAT bit (SSPCON2<6>) is cleared when the slave has sent an Acknowledge  $(\overline{ACK} = 0)$  and is set when the slave does Not Acknowledge  $(\overline{ACK} = 1)$ . A slave sends an Acknowledge when it has recognized its address (including a general call) or when the slave has properly received its data.

#### 9.4.11 I<sup>2</sup>C MASTER MODE RECEPTION

Master mode reception is enabled by programming the Receive Enable bit, RCEN (SSPCON2<3>).

Note: The MSSP module must be in an Idle state before the RCEN bit is set or the RCEN bit will be disregarded.

The Baud Rate Generator begins counting and on each rollover, the state of the SCL pin changes (high to low/ low to high) and data is shifted into the SSPSR. After the falling edge of the eighth clock, the receive enable flag is automatically cleared, the contents of the SSPSR are loaded into the SSPBUF, the BF flag bit is set, the SSPIF flag bit is set and the Baud Rate Generator is suspended from counting, holding SCL low. The MSSP is now in Idle state, awaiting the next command. When the buffer is read by the CPU, the BF flag bit is automatically cleared. The user can then send an Acknowledge bit at the end of reception by setting the Acknowledge Sequence Enable bit, ACKEN (SSPCON2<4>).

#### 9.4.11.1 BF Status Flag

In receive operation, the BF bit is set when an address or data byte is loaded into SSPBUF from SSPSR. It is cleared when the SSPBUF register is read.

#### 9.4.11.2 SSPOV Status Flag

In receive operation, the SSPOV bit is set when 8 bits are received into the SSPSR and the BF flag bit is already set from a previous reception.

#### 9.4.11.3 WCOL Status Flag

If the user writes the SSPBUF when a receive is already in progress (i.e., SSPSR is still shifting in a data byte), the WCOL bit is set and the contents of the buffer are unchanged (the write doesn't occur).

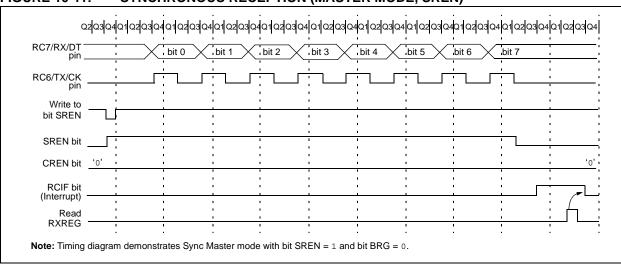

#### 10.1 USART Baud Rate Generator (BRG)

The BRG supports both the Asynchronous and Synchronous modes of the USART. It is a dedicated 8-bit baud rate generator. The SPBRG register controls the period of a free running 8-bit timer. In Asynchronous mode, bit BRGH (TXSTA<2>) also controls the baud rate. In Synchronous mode, bit BRGH is ignored. Table 10-1 shows the formula for computation of the baud rate for different USART modes which only apply in Master mode (internal clock).

Given the desired baud rate and FOSC, the nearest integer value for the SPBRG register can be calculated using the formula in Table 10-1. From this, the error in baud rate can be determined. It may be advantageous to use the high baud rate (BRGH = 1) even for slower baud clocks. This is because the FOSC/(16 (X + 1)) equation can reduce the baud rate error in some cases.

Writing a new value to the SPBRG register causes the BRG timer to be reset (or cleared). This ensures the BRG does not wait for a timer overflow before outputting the new baud rate.

#### 10.1.1 SAMPLING

The data on the RC7/RX/DT pin is sampled three times by a majority detect circuit to determine if a high or a low level is present at the RX pin.

#### TABLE 10-1: BAUD RATE FORMULA

| SYNC | BRGH = 0 (Low Speed)                         | BRGH = 1 (High Speed)           |  |  |  |  |

|------|----------------------------------------------|---------------------------------|--|--|--|--|

| 0    | (Asynchronous) Baud Rate = Fosc/(64 (X + 1)) | Baud Rate = $FOSC/(16 (X + 1))$ |  |  |  |  |

| 1    | (Synchronous) Baud Rate = FOSC/(4 (X + 1))   | N/A                             |  |  |  |  |

**Legend:** X = value in SPBRG (0 to 255)

#### TABLE 10-2: REGISTERS ASSOCIATED WITH BAUD RATE GENERATOR

| Address | Name  | Bit 7   | Bit 6                        | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 | Value on<br>POR, BO | all     | ue on<br>other<br>sets |

|---------|-------|---------|------------------------------|-------|-------|-------|-------|-------|-------|---------------------|---------|------------------------|

| 98h     | TXSTA | CSRC    | TX9                          | TXEN  | SYNC  | _     | BRGH  | TRMT  | TX9D  | 0000 -01            | .0 0000 | -010                   |

| 18h     | RCSTA | SPEN    | RX9                          | SREN  | CREN  | ADDEN | FERR  | OERR  | RX9D  | 0000 000            | x 0000  | 000x                   |

| 99h     | SPBRG | Baud Ra | Baud Rate Generator Register |       |       |       |       |       |       | 0000 000            | 0 0000  | 0000                   |

Legend: x = unknown, - = unimplemented, read as '0'. Shaded cells are not used by the BRG.

#### FIGURE 10-11: SYNCHRONOUS RECEPTION (MASTER MODE, SREN)

#### 10.4 USART Synchronous Slave Mode

Synchronous Slave mode differs from the Master mode in the fact that the shift clock is supplied externally at the RC6/TX/CK pin (instead of being supplied internally in Master mode). This allows the device to transfer or receive data while in Sleep mode. Slave mode is entered by clearing bit, CSRC (TXSTA<7>).

#### 10.4.1 USART SYNCHRONOUS SLAVE TRANSMIT

The operation of the Synchronous Master and Slave modes is identical, except in the case of the Sleep mode.

If two words are written to the TXREG and then the SLEEP instruction is executed, the following will occur:

- a) The first word will immediately transfer to the TSR register and transmit.

- b) The second word will remain in TXREG register.

- c) Flag bit TXIF will not be set.

- d) When the first word has been shifted out of TSR, the TXREG register will transfer the second word to the TSR and flag bit TXIF will now be set.

- e) If enable bit TXIE is set, the interrupt will wake the chip from Sleep and if the global interrupt is enabled, the program will branch to the interrupt vector (0004h).

When setting up a Synchronous Slave Transmission, follow these steps:

- 1. Enable the synchronous slave serial port by setting bits SYNC and SPEN and clearing bit CSRC.

- 2. Clear bits CREN and SREN.

- 3. If interrupts are desired, then set enable bit TXIE.

- 4. If 9-bit transmission is desired, then set bit TX9.

- 5. Enable the transmission by setting enable bit TXEN.

- 6. If 9-bit transmission is selected, the ninth bit should be loaded in bit TX9D.

- 7. Start transmission by loading data to the TXREG register.

- 8. If using interrupts, ensure that GIE and PEIE (bits 7 and 6) of the INTCON register are set.

| Address                | Name   | Bit 7                | Bit 6                        | Bit 5   | Bit 4 | Bit 3 | Bit 2  | Bit 1  | Bit 0  |      | e on:<br>BOR | all c | ie on<br>other<br>sets |

|------------------------|--------|----------------------|------------------------------|---------|-------|-------|--------|--------|--------|------|--------------|-------|------------------------|

| 0Bh, 8Bh,<br>10Bh,18Bh | INTCON | GIE                  | PEIE                         | TMR0IE  | INTE  | RBIE  | TMR0IF | INTF   | R0IF   | 0000 | 000x         | 0000  | 000u                   |

| 0Ch                    | PIR1   | PSPIF <sup>(1)</sup> | ADIF                         | RCIF    | TXIF  | SSPIF | CCP1IF | TMR2IF | TMR1IF | 0000 | 0000         | 0000  | 0000                   |

| 18h                    | RCSTA  | SPEN                 | RX9                          | SREN    | CREN  | ADDEN | FERR   | OERR   | RX9D   | 0000 | 000x         | 0000  | 000x                   |

| 19h                    | TXREG  | USART Tr             | ansmit Re                    | egister |       |       |        |        |        | 0000 | 0000         | 0000  | 0000                   |

| 8Ch                    | PIE1   | PSPIE <sup>(1)</sup> | ADIE                         | RCIE    | TXIE  | SSPIE | CCP1IE | TMR2IE | TMR1IE | 0000 | 0000         | 0000  | 0000                   |

| 98h                    | TXSTA  | CSRC                 | TX9                          | TXEN    | SYNC  | -     | BRGH   | TRMT   | TX9D   | 0000 | -010         | 0000  | -010                   |

| 99h                    | SPBRG  | Baud Rate            | Baud Rate Generator Register |         |       |       |        |        |        |      | 0000         | 0000  | 0000                   |

Legend: x = unknown, - = unimplemented, read as '0'. Shaded cells are not used for synchronous slave transmission.

Note 1: Bits PSPIE and PSPIF are reserved on 28-pin devices; always maintain these bits clear.

#### 10.4.2 USART SYNCHRONOUS SLAVE RECEPTION

The operation of the Synchronous Master and Slave modes is identical, except in the case of the Sleep mode. Bit SREN is a "don't care" in Slave mode.

If receive is enabled by setting bit CREN prior to the SLEEP instruction, then a word may be received during Sleep. On completely receiving the word, the RSR register will transfer the data to the RCREG register and if enable bit RCIE bit is set, the interrupt generated will wake the chip from Sleep. If the global interrupt is enabled, the program will branch to the interrupt vector (0004h).

When setting up a Synchronous Slave Reception, follow these steps:

- Enable the synchronous master serial port by setting bits SYNC and SPEN and clearing bit CSRC.

- 2. If interrupts are desired, set enable bit RCIE.

- 3. If 9-bit reception is desired, set bit RX9.

- 4. To enable reception, set enable bit CREN.

- Flag bit RCIF will be set when reception is complete and an interrupt will be generated if enable bit RCIE was set.

- Read the RCSTA register to get the ninth bit (if enabled) and determine if any error occurred during reception.

- 7. Read the 8-bit received data by reading the RCREG register.

- 8. If any error occurred, clear the error by clearing bit CREN.

- 9. If using interrupts, ensure that GIE and PEIE (bits 7 and 6) of the INTCON register are set.

| Address                | Name   | Bit 7                | Bit 6    | Bit 5     | Bit 4     | Bit 3 | Bit 2  | Bit 1  | Bit 0  | Value on:<br>POR, BOR | Value on<br>all other<br>Resets |

|------------------------|--------|----------------------|----------|-----------|-----------|-------|--------|--------|--------|-----------------------|---------------------------------|

| 0Bh, 8Bh,<br>10Bh,18Bh | INTCON | GIE                  | PEIE     | TMR0IE    | INTE      | RBIE  | TMR0IF | INTF   | R0IF   | 0000 000x             | 0000 000u                       |

| 0Ch                    | PIR1   | PSPIF <sup>(1)</sup> | ADIF     | RCIF      | TXIF      | SSPIF | CCP1IF | TMR2IF | TMR1IF | 0000 0000             | 0000 0000                       |

| 18h                    | RCSTA  | SPEN                 | RX9      | SREN      | CREN      | ADDEN | FERR   | OERR   | RX9D   | 0000 000x             | x000 000x                       |

| 1Ah                    | RCREG  | USART R              | eceive R | egister   |           |       |        |        |        | 0000 0000             | 0000 0000                       |

| 8Ch                    | PIE1   | PSPIE <sup>(1)</sup> | ADIE     | RCIE      | TXIE      | SSPIE | CCP1IE | TMR2IE | TMR1IE | 0000 0000             | 0000 0000                       |

| 98h                    | TXSTA  | CSRC                 | TX9      | TXEN      | SYNC      | —     | BRGH   | TRMT   | TX9D   | 0000 -010             | 0000 -010                       |

| 99h                    | SPBRG  | Baud Rate            | e Genera | 0000 0000 | 0000 0000 |       |        |        |        |                       |                                 |

#### TABLE 10-11: REGISTERS ASSOCIATED WITH SYNCHRONOUS SLAVE RECEPTION

Legend: x = unknown, - = unimplemented, read as '0'. Shaded cells are not used for synchronous slave reception.

Note 1: Bits PSPIE and PSPIF are reserved on 28-pin devices, always maintain these bits clear.

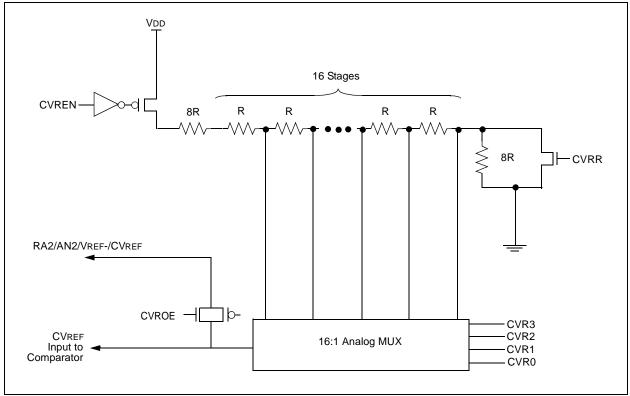

| <b>TABLE 13-1</b> : | REGISTERS ASSOCIATED WITH COMPARATOR VOLTAGE REFERENCE |

|---------------------|--------------------------------------------------------|

|---------------------|--------------------------------------------------------|

| Address | Name   | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 | Value on<br>POR | Value on<br>all other<br>Resets |

|---------|--------|-------|-------|-------|-------|-------|-------|-------|-------|-----------------|---------------------------------|

| 9Dh     | CVRCON | CVREN | CVROE | CVRR  |       | CVR3  | CVR2  | CVR1  | CVR0  | 000- 0000       | 000- 0000                       |

| 9Ch     | CMCON  | C2OUT | C10UT | C2INV | C1INV | CIS   | CM2   | CM1   | CM0   | 0000 0111       | 0000 0111                       |

**Legend:** x = unknown, u = unchanged, - = unimplemented, read as '0'. Shaded cells are not used with the comparator voltage reference.

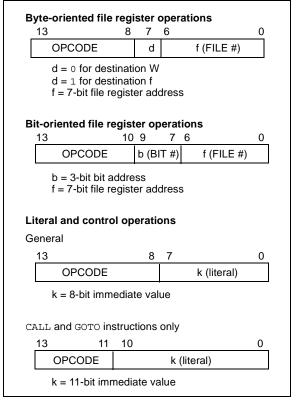

### 15.0 INSTRUCTION SET SUMMARY

The PIC16 instruction set is highly orthogonal and is comprised of three basic categories:

- Byte-oriented operations

- Bit-oriented operations

- Literal and control operations

Each PIC16 instruction is a 14-bit word divided into an **opcode** which specifies the instruction type and one or more **operands** which further specify the operation of the instruction. The formats for each of the categories is presented in Figure 15-1, while the various opcode fields are summarized in Table 15-1.

Table 15-2 lists the instructions recognized by the MPASM<sup>™</sup> Assembler. A complete description of each instruction is also available in the PIC<sup>®</sup> Mid-Range MCU Family Reference Manual (DS33023).

For **byte-oriented** instructions, 'f' represents a file register designator and 'd' represents a destination designator. The file register designator specifies which file register is to be used by the instruction.

The destination designator specifies where the result of the operation is to be placed. If 'd' is zero, the result is placed in the W register. If 'd' is one, the result is placed in the file register specified in the instruction.

For **bit-oriented** instructions, 'b' represents a bit field designator which selects the bit affected by the operation, while 'f' represents the address of the file in which the bit is located.

For **literal and control** operations, 'k' represents an eight or eleven-bit constant or literal value

One instruction cycle consists of four oscillator periods; for an oscillator frequency of 4 MHz, this gives a normal instruction execution time of 1  $\mu$ s. All instructions are executed within a single instruction cycle, unless a conditional test is true, or the program counter is changed as a result of an instruction. When this occurs, the execution takes two instruction cycles with the second cycle executed as a NOP.

| Note: | To maintain upward compatibility with  |  |  |  |  |  |  |  |

|-------|----------------------------------------|--|--|--|--|--|--|--|

|       | future PIC16F87XA products, do not use |  |  |  |  |  |  |  |

|       | the OPTION and TRIS instructions.      |  |  |  |  |  |  |  |

All instruction examples use the format '0xhh' to represent a hexadecimal number, where 'h' signifies a hexadecimal digit.

#### 15.1 READ-MODIFY-WRITE OPERATIONS

Any instruction that specifies a file register as part of the instruction performs a Read-Modify-Write (R-M-W) operation. The register is read, the data is modified, and the result is stored according to either the instruction or the destination designator 'd'. A read operation is performed on a register even if the instruction writes to that register. For example, a "CLRF PORTB" instruction will read PORTB, clear all the data bits, then write the result back to PORTB. This example would have the unintended result that the condition that sets the RBIF flag would be cleared.

### TABLE 15-1: OPCODE FIELD DESCRIPTIONS

| Field | Description                                                                                                                                                                       |

|-------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| f     | Register file address (0x00 to 0x7F)                                                                                                                                              |

| W     | Working register (accumulator)                                                                                                                                                    |

| b     | Bit address within an 8-bit file register                                                                                                                                         |

| k     | Literal field, constant data or label                                                                                                                                             |

| x     | Don't care location (= $0$ or 1).<br>The assembler will generate code with x = $0$ .<br>It is the recommended form of use for<br>compatibility with all Microchip software tools. |

| d     | Destination select; $d = 0$ : store result in W,<br>d = 1: store result in file register f.<br>Default is $d = 1$ .                                                               |

| PC    | Program Counter                                                                                                                                                                   |

| ТО    | Time-out bit                                                                                                                                                                      |

| PD    | Power-down bit                                                                                                                                                                    |

### FIGURE 15-1: GENERAL FORMAT FOR INSTRUCTIONS

| TABLE 15-2: PIC16 | F87XA INSTRUCTION SET |

|-------------------|-----------------------|

|-------------------|-----------------------|

| Mnemonic,                              |          | Description                                    | Cycles        |       | 14-Bit | Status | Notes |          |       |

|----------------------------------------|----------|------------------------------------------------|---------------|-------|--------|--------|-------|----------|-------|

| Oper                                   | Operands |                                                | Cycles        | MSb   |        |        | LSb   | Affected | Notes |

| BYTE-ORIENTED FILE REGISTER OPERATIONS |          |                                                |               |       |        |        |       |          |       |

| ADDWF                                  | f, d     | Add W and f                                    | 1             | 00    | 0111   | dfff   | ffff  | C,DC,Z   | 1,2   |

| ANDWF                                  | f, d     | AND W with f                                   | 1             | 00    | 0101   | dfff   | ffff  | Z        | 1,2   |

| CLRF                                   | f        | Clear f                                        | 1             | 00    | 0001   | lfff   | ffff  | Z        | 2     |

| CLRW                                   | -        | Clear W                                        | 1             | 00    | 0001   | 0xxx   | xxxx  | Z        |       |

| COMF                                   | f, d     | Complement f                                   | 1             | 00    | 1001   | dfff   | ffff  | Z        | 1,2   |

| DECF                                   | f, d     | Decrement f                                    | 1             | 00    | 0011   | dfff   | ffff  | Z        | 1,2   |

| DECFSZ                                 | f, d     | Decrement f, Skip if 0                         | 1(2)          | 00    | 1011   | dfff   | ffff  |          | 1,2,3 |

| INCF                                   | f, d     | Increment f                                    | 1             | 00    | 1010   | dfff   | ffff  | Z        | 1,2   |

| INCFSZ                                 | f, d     | Increment f, Skip if 0                         | 1(2)          | 00    | 1111   | dfff   | ffff  |          | 1,2,3 |

| IORWF                                  | f, d     | Inclusive OR W with f                          | 1             | 00    | 0100   | dfff   | ffff  | Z        | 1,2   |

| MOVF                                   | f, d     | Move f                                         | 1             | 00    | 1000   | dfff   | ffff  | Z        | 1,2   |

| MOVWF                                  | f        | Move W to f                                    | 1             | 00    | 0000   | lfff   | ffff  |          |       |

| NOP                                    | -        | No Operation                                   | 1             | 00    | 0000   | 0xx0   | 0000  |          |       |

| RLF                                    | f, d     | Rotate Left f through Carry                    | 1             | 00    | 1101   | dfff   | ffff  | С        | 1,2   |

| RRF                                    | f, d     | Rotate Right f through Carry                   | 1             | 00    | 1100   | dfff   | ffff  | С        | 1,2   |

| SUBWF                                  | f, d     | Subtract W from f                              | 1             | 00    | 0010   | dfff   | ffff  | C,DC,Z   | 1,2   |

| SWAPF                                  | f, d     | Swap nibbles in f                              | 1             | 00    | 1110   | dfff   | ffff  |          | 1,2   |

| XORWF                                  | f, d     | Exclusive OR W with f                          | 1             | 00    | 0110   | dfff   | ffff  | Z        | 1,2   |

|                                        |          | BIT-ORIENTED FILE                              | REGISTER OPER | ATION | ١S     |        |       |          |       |

| BCF                                    | f, b     | Bit Clear f                                    | 1             | 01    | 00bb   | bfff   | ffff  |          | 1,2   |

| BSF                                    | f, b     | Bit Set f                                      | 1             | 01    | 01bb   | bfff   | ffff  |          | 1,2   |

| BTFSC                                  | f, b     | Bit Test f, Skip if Clear                      | 1 (2)         | 01    | 10bb   | bfff   | ffff  |          | 3     |

| BTFSS                                  | f, b     | Bit Test f, Skip if Set                        | 1 (2)         | 01    | 11bb   | bfff   | ffff  |          | 3     |

|                                        |          | LITERAL AND CO                                 | NTROL OPERAT  | IONS  |        |        |       |          |       |

| ADDLW                                  | k        | Add Literal and W                              | 1             | 11    | 111x   | kkkk   | kkkk  | C,DC,Z   |       |

| ANDLW                                  | k        | AND Literal with W                             | 1             | 11    | 1001   | kkkk   | kkkk  | Z        |       |

| CALL                                   | k        | Call Subroutine                                | 2             | 10    | 0kkk   | kkkk   | kkkk  |          |       |

| CLRWDT                                 | -        | Clear Watchdog Timer                           | 1             | 00    | 0000   | 0110   | 0100  | TO,PD    |       |

| GOTO                                   | k        | Go to Address                                  | 2             | 10    | 1kkk   | kkkk   | kkkk  | -        |       |

| IORLW                                  | k        | Inclusive OR Literal with W                    | 1             | 11    | 1000   | kkkk   | kkkk  | Z        |       |

| MOVLW                                  | k        | Move Literal to W                              | 1             | 11    | 00xx   | kkkk   | kkkk  |          |       |

| RETFIE                                 | -        | Return from Interrupt                          | 2             | 00    | 0000   | 0000   | 1001  |          |       |

| RETLW                                  | k        | Return with Literal in W                       | 2             | 11    | 01xx   | kkkk   |       |          |       |

| RETURN                                 | -        | Return from Subroutine                         | 2             | 00    | 0000   | 0000   | 1000  |          |       |

| SLEEP                                  | -        | Go into Standby mode                           | 1             | 00    | 0000   | 0110   | 0011  | TO,PD    |       |

| SUBLW                                  | k        | Subtract W from Literal                        | 1             | 11    |        | kkkk   |       | C,DC,Z   |       |

| XORLW                                  | k        | Exclusive OR Literal with W                    | 1             | 11    | 1010   | kkkk   |       | Z        |       |

| Note 1:                                |          | I/O register is modified as a function of itse |               |       |        |        |       |          |       |

Note 1: When an I/O register is modified as a function of itself (e.g., MOVF PORTE, 1), the value used will be that value present on the pins themselves. For example, if the data latch is '1' for a pin configured as input and is driven low by an external device, the data will be written back with a '0'.

2: If this instruction is executed on the TMR0 register (and where applicable, d = 1), the prescaler will be cleared if assigned to the Timer0 module.

3: If Program Counter (PC) is modified, or a conditional test is true, the instruction requires two cycles. The second cycle is executed as a NOP.

**Note:** Additional information on the mid-range instruction set is available in the PIC<sup>®</sup> Mid-Range MCU Family Reference Manual (DS33023).

#### 16.9 MPLAB ICE 2000 High Performance Universal In-Circuit Emulator

The MPLAB ICE 2000 universal in-circuit emulator is intended to provide the product development engineer with a complete microcontroller design tool set for PIC microcontrollers. Software control of the MPLAB ICE 2000 in-circuit emulator is advanced by the MPLAB Integrated Development Environment, which allows editing, building, downloading and source debugging from a single environment.

The MPLAB ICE 2000 is a full-featured emulator system with enhanced trace, trigger and data monitoring features. Interchangeable processor modules allow the system to be easily reconfigured for emulation of different processors. The universal architecture of the MPLAB ICE in-circuit emulator allows expansion to support new PIC microcontrollers.

The MPLAB ICE 2000 in-circuit emulator system has been designed as a real-time emulation system with advanced features that are typically found on more expensive development tools. The PC platform and Microsoft<sup>®</sup> Windows 32-bit operating system were chosen to best make these features available in a simple, unified application.

#### 16.10 MPLAB ICE 4000 High Performance Universal In-Circuit Emulator

The MPLAB ICE 4000 universal in-circuit emulator is intended to provide the product development engineer with a complete microcontroller design tool set for highend PIC microcontrollers. Software control of the MPLAB ICE in-circuit emulator is provided by the MPLAB Integrated Development Environment, which allows editing, building, downloading and source debugging from a single environment.

The MPLAB ICD 4000 is a premium emulator system, providing the features of MPLAB ICE 2000, but with increased emulation memory and high speed performance for dsPIC30F and PIC18XXXX devices. Its advanced emulator features include complex triggering and timing, up to 2 Mb of emulation memory, and the ability to view variables in real-time.

The MPLAB ICE 4000 in-circuit emulator system has been designed as a real-time emulation system with advanced features that are typically found on more expensive development tools. The PC platform and Microsoft Windows 32-bit operating system were chosen to best make these features available in a simple, unified application.

#### 16.11 MPLAB ICD 2 In-Circuit Debugger

Microchip's In-Circuit Debugger, MPLAB ICD 2, is a powerful, low-cost, run-time development tool, connecting to the host PC via an RS-232 or high-speed USB interface. This tool is based on the Flash PIC MCUs and can be used to develop for these and other PIC microcontrollers. The MPLAB ICD 2 utilizes the incircuit debugging capability built into the Flash devices. This feature, along with Microchip's In-Circuit Serial Programming<sup>™</sup> (ICSP<sup>™</sup>) protocol, offers cost effective in-circuit Flash debugging from the graphical user interface of the MPLAB Integrated Development Environment. This enables a designer to develop and debug source code by setting breakpoints, singlestepping and watching variables, CPU status and peripheral registers. Running at full speed enables testing hardware and applications in real-time. MPLAB ICD 2 also serves as a development programmer for selected PIC devices.

#### 16.12 PRO MATE II Universal Device Programmer

The PRO MATE II is a universal, CE compliant device programmer with programmable voltage verification at VDDMIN and VDDMAX for maximum reliability. It features an LCD display for instructions and error messages and a modular detachable socket assembly to support various package types. In Stand-Alone mode, the PRO MATE II device programmer can read, verify, and program PIC devices without a PC connection. It can also set code protection in this mode.

#### 16.13 PICSTART Plus Development Programmer

The PICSTART Plus development programmer is an easy-to-use, low-cost, prototype programmer. It connects to the PC via a COM (RS-232) port. MPLAB Integrated Development Environment software makes using the programmer simple and efficient. The PICSTART Plus development programmer supports most PIC devices up to 40 pins. Larger pin count devices, such as the PIC16C92X and PIC17C76X, may be supported with an adapter socket. The PICSTART Plus development programmer is CE compliant.

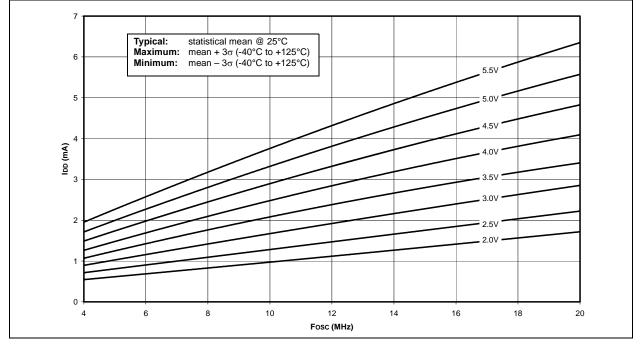

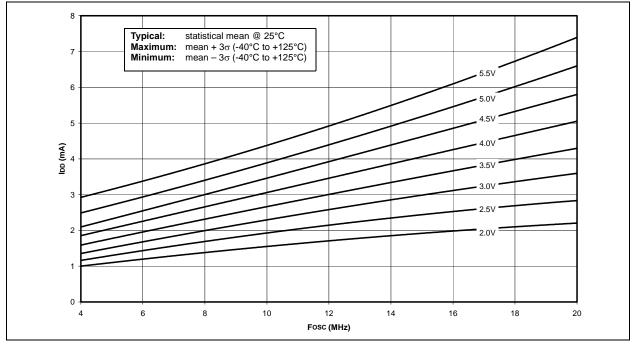

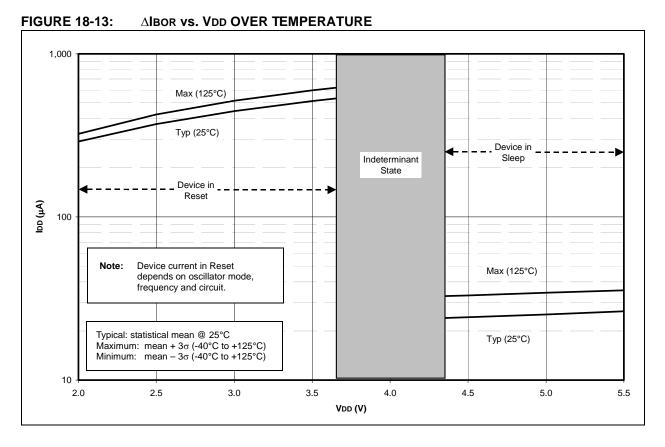

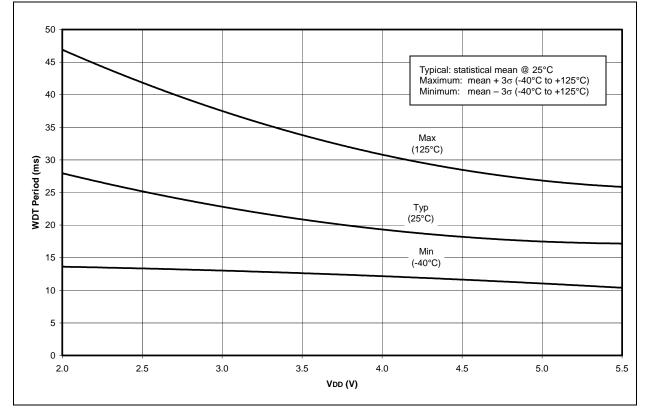

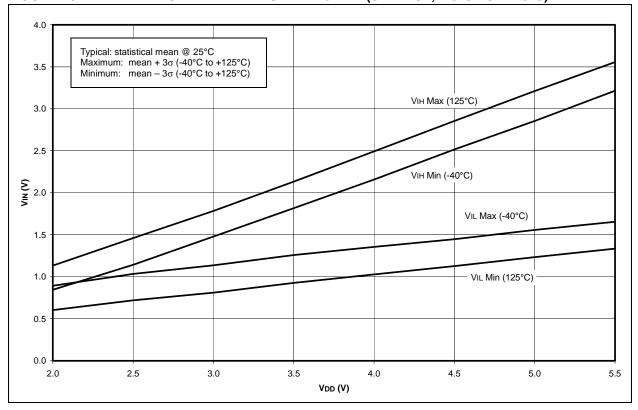

#### 18.0 DC AND AC CHARACTERISTICS GRAPHS AND TABLES

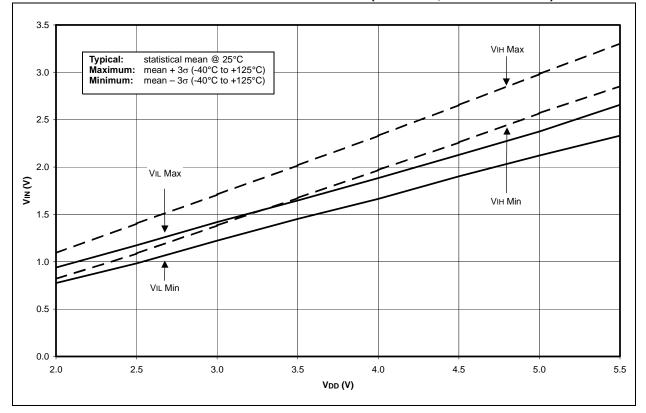

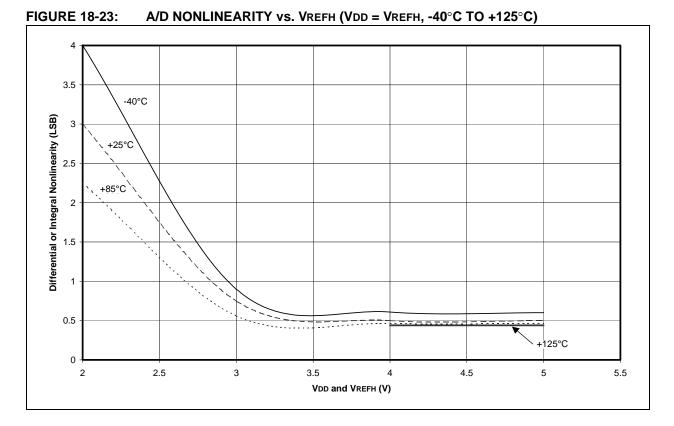

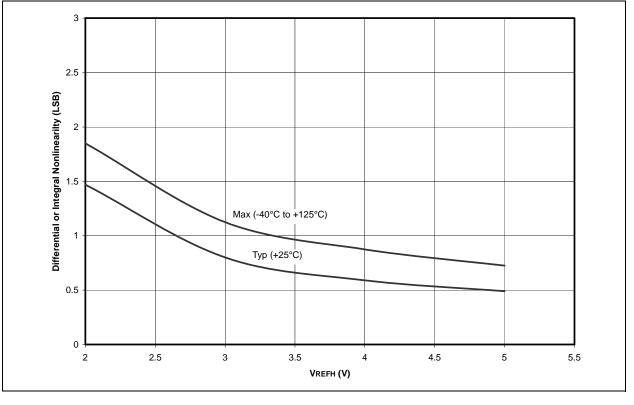

**Note:** The graphs and tables provided following this note are a statistical summary based on a limited number of samples and are provided for informational purposes only. The performance characteristics listed herein are not tested or guaranteed. In some graphs or tables, the data presented may be outside the specified operating range (e.g., outside specified power supply range) and therefore, outside the warranted range.

"Typical" represents the mean of the distribution at 25°C. "Maximum" or "minimum" represents (mean +  $3\sigma$ ) or (mean -  $3\sigma$ ) respectively, where  $\sigma$  is a standard deviation, over the whole temperature range.

© 2001-2013 Microchip Technology Inc.

FIGURE 18-21: MINIMUM AND MAXIMUM VIN vs. VDD (ST INPUT, -40°C TO +125°C)

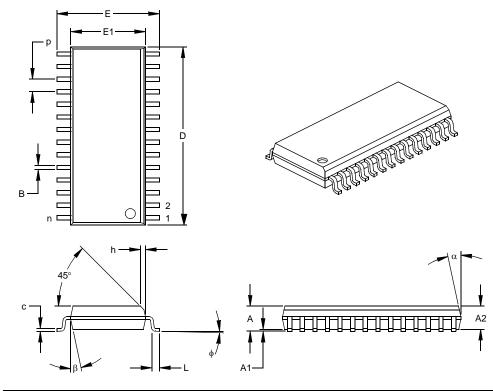

#### 28-Lead Plastic Small Outline (SO) – Wide, 300 mil (SOIC)

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

|                          |             | INCHES* |      | MILLIMETERS |       |       |       |

|--------------------------|-------------|---------|------|-------------|-------|-------|-------|

| Dimens                   | sion Limits | MIN     | NOM  | MAX         | MIN   | NOM   | MAX   |

| Number of Pins           | n           |         | 28   |             |       | 28    |       |

| Pitch                    | р           |         | .050 |             |       | 1.27  |       |

| Overall Height           | А           | .093    | .099 | .104        | 2.36  | 2.50  | 2.64  |

| Molded Package Thickness | A2          | .088    | .091 | .094        | 2.24  | 2.31  | 2.39  |

| Standoff §               | A1          | .004    | .008 | .012        | 0.10  | 0.20  | 0.30  |

| Overall Width            | E           | .394    | .407 | .420        | 10.01 | 10.34 | 10.67 |

| Molded Package Width     | E1          | .288    | .295 | .299        | 7.32  | 7.49  | 7.59  |

| Overall Length           | D           | .695    | .704 | .712        | 17.65 | 17.87 | 18.08 |

| Chamfer Distance         | h           | .010    | .020 | .029        | 0.25  | 0.50  | 0.74  |

| Foot Length              | L           | .016    | .033 | .050        | 0.41  | 0.84  | 1.27  |

| Foot Angle Top           | φ           | 0       | 4    | 8           | 0     | 4     | 8     |

| Lead Thickness           | С           | .009    | .011 | .013        | 0.23  | 0.28  | 0.33  |

| Lead Width               | В           | .014    | .017 | .020        | 0.36  | 0.42  | 0.51  |

| Mold Draft Angle Top     | α           | 0       | 12   | 15          | 0     | 12    | 15    |

| Mold Draft Angle Bottom  | β           | 0       | 12   | 15          | 0     | 12    | 15    |

\* Controlling Parameter § Significant Characteristic

Notes:

Dimensions D and E1 do not include mold flash or protrusions. Mold flash or protrusions shall not exceed .010" (0.254mm) per side. JEDEC Equivalent: MS-013

Drawing No. C04-052

| Special Function Registers<br>Special Function Registers (SFRs) |     |

|-----------------------------------------------------------------|-----|

| Speed, Operating                                                |     |

| SPI Mode                                                        |     |

| Associated Registers                                            | 79  |

| Bus Mode Compatibility                                          |     |

| Effects of a Reset                                              |     |

| Enabling SPI I/O                                                | 75  |

| Master Mode                                                     |     |

| Master/Slave Connection                                         |     |

| Serial Clock                                                    |     |

| Serial Data In                                                  |     |

| Serial Data Out                                                 |     |

| Slave Select                                                    |     |

| Slave Select Synchronization                                    |     |

| Sleep Operation                                                 |     |

| SPI Clock                                                       |     |

| Typical Connection                                              |     |

| SPI Mode Requirements                                           |     |

| SS                                                              | 71  |

| SSP                                                             |     |

| SPI Master/Slave Connection                                     |     |

| SSPADD Register                                                 |     |

| SSPBUF Register                                                 |     |

| SSPCON Register                                                 |     |

| SSPCON2 Register<br>SSPIF                                       |     |

|                                                                 | -   |

| SSPOV                                                           |     |

| SSPSTAT Register                                                |     |

| R/W Bit                                                         |     |

| Overflows                                                       |     |

| Underflow                                                       |     |

| Status Register                                                 |     |

| C Bit                                                           | 22  |

| DC Bit                                                          |     |

| IRP Bit                                                         |     |

| PD Bit                                                          |     |

| RP1:RP0 Bits                                                    | ,   |

| TO Bit                                                          |     |

| Z Bit                                                           |     |

| Synchronous Master Reception                                    |     |

| Associated Registers                                            | 123 |

| Synchronous Master Transmission                                 |     |

| Associated Registers                                            | 122 |

| Synchronous Serial Port Interrupt                               |     |

| Synchronous Slave Reception                                     |     |

| Associated Registers                                            | 125 |

| Synchronous Slave Transmission                                  |     |

| Associated Registers                                            | 125 |

| -                                                               |     |

| т                                                               |     |

| T1CKPS0 Bit                                                     |     |

| T1CKPS1 Bit                                                     | -   |

| T1CON Register                                                  |     |

| T1OSCEN Bit                                                     |     |

| T1SYNC Bit                                                      |     |

| T2CKPS0 Bit                                                     |     |

| T2CKPS1 Bit                                                     | 61  |

T2CON Register

19

TAD

131

Time-out Sequence

148

| Timer0                                        | 53  |

|-----------------------------------------------|-----|

| Associated Registers                          | 55  |

| Clock Source Edge Select (T0SE Bit)           | 23  |

| Clock Source Select (T0CS Bit)                | 23  |

| External Clock                                | 54  |

| Interrupt                                     |     |

| Overflow Enable (TMR0IE Bit)                  |     |

| Overflow Flag (TMR0IF Bit)                    |     |

| Overflow Interrupt                            |     |

| Prescaler                                     |     |

| Т0СКІ                                         |     |

| Timer0 and Timer1 External Clock Requirements |     |

| Timer1                                        |     |

| Associated Registers                          |     |

| Asynchronous Counter Mode                     |     |

| Reading and Writing to                        |     |

| Counter Operation                             |     |

| Operation in Timer Mode                       |     |

| Oscillator<br>Capacitor Selection             |     |

|                                               |     |

| Prescaler<br>Resetting of Timer1 Registers    |     |

| Resetting Timer1 Using a CCP Trigger Output . |     |

| Synchronized Counter Mode                     |     |

| TMR1H                                         |     |

| TMR1L                                         |     |

| Timer2                                        |     |

| Associated Registers                          |     |

| Output                                        |     |

| Postscaler                                    |     |

| Prescaler                                     |     |

| Prescaler and Postscaler                      |     |

| Timing Diagrams                               |     |

| A/D Conversion                                | 195 |

| Acknowledge Sequence                          |     |

| Asynchronous Master Transmission              |     |

| Asynchronous Master Transmission              | -   |

| (Back to Back)                                | 116 |

| Asynchronous Reception                        |     |

| Asynchronous Reception with                   |     |

| Address Byte First                            | 120 |

| Asynchronous Reception with                   |     |

| Address Detect                                | 120 |

| Baud Rate Generator with Clock Arbitration    | 98  |

| BRG Reset Due to SDA Arbitration During       |     |

| Start Condition                               | 107 |

| Brown-out Reset                               | 184 |

| Bus Collision During a Repeated               |     |

| Start Condition (Case 1)                      | 108 |

| Bus Collision During Repeated                 |     |

| Start Condition (Case 2)                      | 108 |

| Bus Collision During Start Condition          |     |

| (SCL = 0)                                     | 107 |

| Bus Collision During Start Condition          |     |

| (SDA Only)                                    | 106 |

| Bus Collision During Stop Condition           |     |

| (Case 1)                                      | 109 |

| Bus Collision During Stop Condition           |     |

| (Case 2)                                      |     |

| Bus Collision for Transmit and Acknowledge    |     |

| Capture/Compare/PWM (CCP1 and CCP2)           |     |

| CLKO and I/O                                  |     |

| Clock Synchronization                         |     |

| External Clock                                |     |

| First Start Bit                               | 99  |