Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                           |

|----------------------------|---------------------------------------------------------------------------|

| Product Status             | Active                                                                    |

| Core Processor             | PIC                                                                       |

| Core Size                  | 8-Bit                                                                     |

| Speed                      | 20MHz                                                                     |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                         |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                     |

| Number of I/O              | 22                                                                        |

| Program Memory Size        | 14KB (8K x 14)                                                            |

| Program Memory Type        | FLASH                                                                     |

| EEPROM Size                | 256 x 8                                                                   |

| RAM Size                   | 368 x 8                                                                   |

| Voltage - Supply (Vcc/Vdd) | 4V ~ 5.5V                                                                 |

| Data Converters            | A/D 5x10b                                                                 |

| Oscillator Type            | External                                                                  |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                        |

| Mounting Type              | Through Hole                                                              |

| Package / Case             | 28-DIP (0.300", 7.62mm)                                                   |

| Supplier Device Package    | 28-SPDIP                                                                  |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16f876a-e-sp |

|                            |                                                                           |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

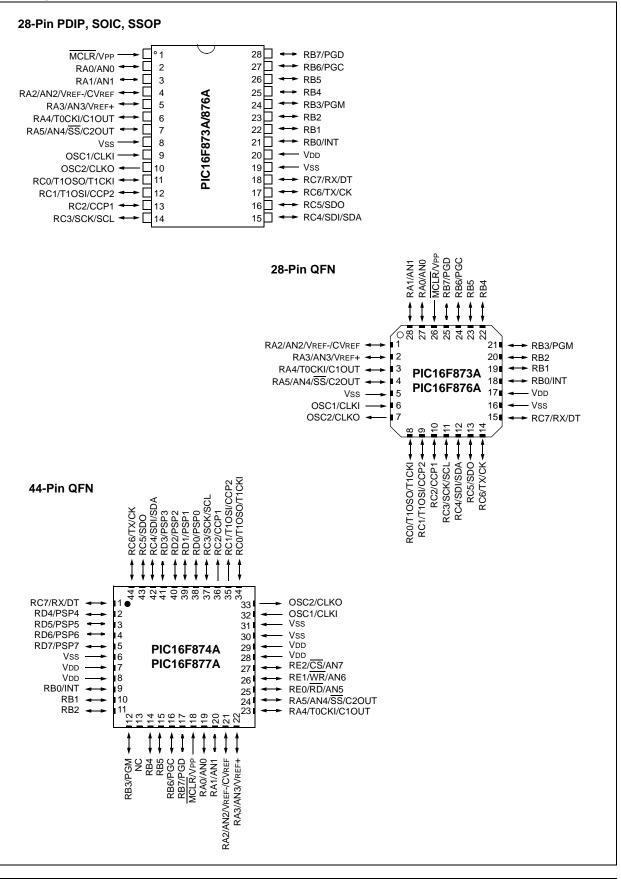

### **Pin Diagrams**

## 1.0 DEVICE OVERVIEW

This document contains device specific information about the following devices:

- PIC16F873A

- PIC16F874A

- PIC16F876A

- PIC16F877A

PIC16F873A/876A devices are available only in 28-pin packages, while PIC16F874A/877A devices are available in 40-pin and 44-pin packages. All devices in the PIC16F87XA family share common architecture with the following differences:

- The PIC16F873A and PIC16F874A have one-half of the total on-chip memory of the PIC16F876A and PIC16F877A

- The 28-pin devices have three I/O ports, while the 40/44-pin devices have five

- The 28-pin devices have fourteen interrupts, while the 40/44-pin devices have fifteen

- The 28-pin devices have five A/D input channels, while the 40/44-pin devices have eight

- The Parallel Slave Port is implemented only on the 40/44-pin devices

The available features are summarized in Table 1-1. Block diagrams of the PIC16F873A/876A and PIC16F874A/877A devices are provided in Figure 1-1 and Figure 1-2, respectively. The pinouts for these device families are listed in Table 1-2 and Table 1-3.

Additional information may be found in the PIC<sup>®</sup> Mid-Range Reference Manual (DS33023), which may be obtained from your local Microchip Sales Representative or downloaded from the Microchip web site. The Reference Manual should be considered a complementary document to this data sheet and is highly recommended reading for a better understanding of the device architecture and operation of the peripheral modules.

| Key Features                           | PIC16F873A                                              | PIC16F874A                                              | PIC16F876A                                              | PIC16F877A                                              |

|----------------------------------------|---------------------------------------------------------|---------------------------------------------------------|---------------------------------------------------------|---------------------------------------------------------|

| Operating Frequency                    | DC – 20 MHz                                             |

| Resets (and Delays)                    | POR, BOR<br>(PWRT, OST)                                 | POR, BOR<br>(PWRT, OST)                                 | POR, BOR<br>(PWRT, OST)                                 | POR, BOR<br>(PWRT, OST)                                 |

| Flash Program Memory<br>(14-bit words) | 4K                                                      | 4K                                                      | 8K                                                      | 8K                                                      |

| Data Memory (bytes)                    | 192                                                     | 192                                                     | 368                                                     | 368                                                     |

| EEPROM Data Memory (bytes)             | 128                                                     | 128                                                     | 256                                                     | 256                                                     |

| Interrupts                             | 14                                                      | 15                                                      | 14                                                      | 15                                                      |

| I/O Ports                              | Ports A, B, C                                           | Ports A, B, C, D, E                                     | Ports A, B, C                                           | Ports A, B, C, D, E                                     |

| Timers                                 | 3                                                       | 3                                                       | 3                                                       | 3                                                       |

| Capture/Compare/PWM modules            | 2                                                       | 2                                                       | 2                                                       | 2                                                       |

| Serial Communications                  | MSSP, USART                                             | MSSP, USART                                             | MSSP, USART                                             | MSSP, USART                                             |

| Parallel Communications                | —                                                       | PSP                                                     | _                                                       | PSP                                                     |

| 10-bit Analog-to-Digital Module        | 5 input channels                                        | 8 input channels                                        | 5 input channels                                        | 8 input channels                                        |

| Analog Comparators                     | 2                                                       | 2                                                       | 2                                                       | 2                                                       |

| Instruction Set                        | 35 Instructions                                         | 35 Instructions                                         | 35 Instructions                                         | 35 Instructions                                         |

| Packages                               | 28-pin PDIP<br>28-pin SOIC<br>28-pin SSOP<br>28-pin QFN | 40-pin PDIP<br>44-pin PLCC<br>44-pin TQFP<br>44-pin QFN | 28-pin PDIP<br>28-pin SOIC<br>28-pin SSOP<br>28-pin QFN | 40-pin PDIP<br>44-pin PLCC<br>44-pin TQFP<br>44-pin QFN |

#### TABLE 1-1:PIC16F87XA DEVICE FEATURES

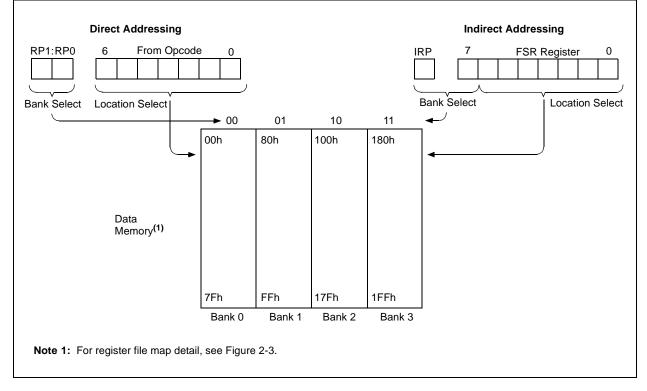

## 2.5 Indirect Addressing, INDF and FSR Registers

The INDF register is not a physical register. Addressing the INDF register will cause indirect addressing.

Indirect addressing is possible by using the INDF register. Any instruction using the INDF register actually accesses the register pointed to by the File Select Register, FSR. Reading the INDF register itself, indirectly (FSR = 0) will read 00h. Writing to the INDF register indirectly results in a no operation (although status bits may be affected). An effective 9-bit address is obtained by concatenating the 8-bit FSR register and the IRP bit (Status<7>) as shown in Figure 2-6. A simple program to clear RAM locations 20h-2Fh using indirect addressing is shown in Example 2-2.

### EXAMPLE 2-2: INDIRECT ADDRESSING

|          | MOVLW | 0x20  | ;initialize pointer  |

|----------|-------|-------|----------------------|

|          | MOVWF | FSR   | ;to RAM              |

| NEXT     | CLRF  | INDF  | clear INDF register; |

|          | INCF  | FSR,F | ;inc pointer         |

|          | BTFSS | FSR,4 | ;all done?           |

|          | GOTO  | NEXT  | ;no clear next       |

| CONTINUE |       |       |                      |

|          | :     |       | ;yes continue        |

| 1        |       |       |                      |

| Name                   | Bit#  | Buffer                | Function                                                                                                                                          |

|------------------------|-------|-----------------------|---------------------------------------------------------------------------------------------------------------------------------------------------|

| RB0/INT                | bit 0 | TTL/ST <sup>(1)</sup> | Input/output pin or external interrupt input. Internal software programmable weak pull-up.                                                        |

| RB1                    | bit 1 | TTL                   | Input/output pin. Internal software programmable weak pull-up.                                                                                    |

| RB2                    | bit 2 | TTL                   | Input/output pin. Internal software programmable weak pull-up.                                                                                    |

| RB3/PGM <sup>(3)</sup> | bit 3 | TTL                   | Input/output pin or programming pin in LVP mode. Internal software programmable weak pull-up.                                                     |

| RB4                    | bit 4 | TTL                   | Input/output pin (with interrupt-on-change). Internal software programmable weak pull-up.                                                         |

| RB5                    | bit 5 | TTL                   | Input/output pin (with interrupt-on-change). Internal software programmable weak pull-up.                                                         |

| RB6/PGC                | bit 6 | TTL/ST <sup>(2)</sup> | Input/output pin (with interrupt-on-change) or in-circuit debugger pin.<br>Internal software programmable weak pull-up. Serial programming clock. |

| RB7/PGD                | bit 7 | TTL/ST <sup>(2)</sup> | Input/output pin (with interrupt-on-change) or in-circuit debugger pin.<br>Internal software programmable weak pull-up. Serial programming data.  |

### TABLE 4-3:PORTB FUNCTIONS

**Legend:** TTL = TTL input, ST = Schmitt Trigger input

**Note 1:** This buffer is a Schmitt Trigger input when configured as the external interrupt.

2: This buffer is a Schmitt Trigger input when used in Serial Programming mode or in-circuit debugger.

**3:** Low-Voltage ICSP Programming (LVP) is enabled by default which disables the RB3 I/O function. LVP must be disabled to enable RB3 as an I/O pin and allow maximum compatibility to the other 28-pin and 40-pin mid-range devices.

| TABLE 4-4: S | SUMMARY OF REGISTERS ASSOCIATED WITH PORTB |

|--------------|--------------------------------------------|

|--------------|--------------------------------------------|

| Address   | Name       | Bit 7 | Bit 6                        | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0  | Value<br>POR, I |      | Valu<br>all o<br>Res | ther |

|-----------|------------|-------|------------------------------|-------|-------|-------|-------|-------|--------|-----------------|------|----------------------|------|

| 06h, 106h | PORTB      | RB7   | RB6                          | RB5   | RB4   | RB3   | RB2   | RB1   | RB0    | XXXX :          | xxxx | uuuu                 | uuuu |

| 86h, 186h | TRISB      | PORTB | ORTB Data Direction Register |       |       |       |       |       | 1111 1 | 1111            | 1111 | 1111                 |      |

| 81h, 181h | OPTION_REG | RBPU  | INTEDG                       | TOCS  | T0SE  | PSA   | PS2   | PS1   | PS0    | 1111 1          | 1111 | 1111                 | 1111 |

|           |            |       |                              |       |       |       |       |       |        |                 |      |                      |      |

**Legend:** x = unknown, u = unchanged. Shaded cells are not used by PORTB.

## 6.0 TIMER1 MODULE

The Timer1 module is a 16-bit timer/counter consisting of two 8-bit registers (TMR1H and TMR1L) which are readable and writable. The TMR1 register pair (TMR1H:TMR1L) increments from 0000h to FFFFh and rolls over to 0000h. The TMR1 interrupt, if enabled, is generated on overflow which is latched in interrupt flag bit, TMR1IF (PIR1<0>). This interrupt can be enabled/disabled by setting/clearing TMR1 interrupt enable bit, TMR1IE (PIE1<0>).

Timer1 can operate in one of two modes:

- As a Timer

- As a Counter

The operating mode is determined by the clock select bit, TMR1CS (T1CON<1>).

In Timer mode, Timer1 increments every instruction cycle. In Counter mode, it increments on every rising edge of the external clock input.

Timer1 can be enabled/disabled by setting/clearing control bit, TMR1ON (T1CON<0>).

Timer1 also has an internal "Reset input". This Reset can be generated by either of the two CCP modules (Section 8.0 "Capture/Compare/PWM Modules"). Register 6-1 shows the Timer1 Control register.

When the Timer1 oscillator is enabled (T1OSCEN is set), the RC1/T1OSI/CCP2 and RC0/T1OSO/T1CKI pins become inputs. That is, the TRISC<1:0> value is ignored and these pins read as '0'.

Additional information on timer modules is available in the PIC<sup>®</sup> Mid-Range MCU Family Reference Manual (DS33023).

| ER 6-1: | T1CON: TI                      | MER1 CO                                                                                                                                            | ONTROL R                        | EGISTER (     | ADDRESS 1      | 0h)       |               |        |  |  |

|---------|--------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------|---------------|----------------|-----------|---------------|--------|--|--|

|         | U-0                            | U-0                                                                                                                                                | R/W-0                           | R/W-0         | R/W-0          | R/W-0     | R/W-0         | R/W-0  |  |  |

|         |                                | —                                                                                                                                                  | T1CKPS1                         | T1CKPS0       | T1OSCEN        | T1SYNC    | TMR1CS        | TMR10N |  |  |

|         | bit 7                          |                                                                                                                                                    |                                 |               |                |           |               | bit 0  |  |  |

| bit 7-6 | Unimpleme                      | ented: Rea                                                                                                                                         | ad as '0'                       |               |                |           |               |        |  |  |

| bit 5-4 | T1CKPS1:                       | T1CKPS1:T1CKPS0: Timer1 Input Clock Prescale Select bits                                                                                           |                                 |               |                |           |               |        |  |  |

|         | 10 = 1:4 pre<br>01 = 1:2 pre   | 11 = 1:8 prescale value<br>10 = 1:4 prescale value<br>01 = 1:2 prescale value<br>00 = 1:1 prescale value                                           |                                 |               |                |           |               |        |  |  |

| bit 3   | T1OSCEN:                       | Timer1 O                                                                                                                                           | scillator Ena                   | ble Control b | it             |           |               |        |  |  |

|         |                                | <ul> <li>1 = Oscillator is enabled</li> <li>0 = Oscillator is shut-off (the oscillator inverter is turned off to eliminate power drain)</li> </ul> |                                 |               |                |           |               |        |  |  |

| bit 2   | T1SYNC: T                      | imer1 Exte                                                                                                                                         | ernal Clock I                   | nput Synchro  | nization Contr | ol bit    |               |        |  |  |

|         | 0 = Synchro<br><u>When TMR</u> | synchroniz<br>onize exter<br><u>1CS = 0</u> :                                                                                                      | ze external c<br>rnal clock inp | out           |                |           |               |        |  |  |

|         | -                              |                                                                                                                                                    |                                 |               | ck when TMR?   | 1CS = 0.  |               |        |  |  |

| bit 1   | 1 = Externa                    | <b>TMR1CS</b> : Timer1 Clock Source Select bit<br>1 = External clock from pin RC0/T1OSO/T1CKI (on the rising edge)<br>0 = Internal clock (Fosc/4)  |                                 |               |                |           |               |        |  |  |

| bit 0   | TMR1ON: 7                      | Fimer1 On                                                                                                                                          | bit                             |               |                |           |               |        |  |  |

|         |                                | 1 = Enables Timer1<br>0 = Stops Timer1                                                                                                             |                                 |               |                |           |               |        |  |  |

|         | Legend:                        |                                                                                                                                                    |                                 |               |                |           |               |        |  |  |

|         | R = Reada                      | ole bit                                                                                                                                            | W = V                           | Vritable bit  | U = Unimpl     | emented b | it, read as ' | )'     |  |  |

|         | - n = Value                    | at POR                                                                                                                                             | '1' = E                         | Bit is set    | '0' = Bit is c | leared    | x = Bit is ur | nknown |  |  |

|         |                                |                                                                                                                                                    |                                 |               |                |           |               |        |  |  |

## REGISTER 6-1: T1CON: TIMER1 CONTROL REGISTER (ADDRESS 10h)

| <b>REGISTER 9-3:</b> | SSPSTAT:                                                                                        | MSSP STA                                                                                      | TUS REG      | SISTER (I <sup>2</sup> | C MODE)                    | (ADDRESS      | 6 94h)         |         |  |

|----------------------|-------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------|--------------|------------------------|----------------------------|---------------|----------------|---------|--|

|                      | R/W-0                                                                                           | R/W-0                                                                                         | R-0          | R-0                    | R-0                        | R-0           | R-0            | R-0     |  |

|                      | SMP                                                                                             | CKE                                                                                           | D/A          | Р                      | S                          | R/W           | UA             | BF      |  |

|                      | bit 7                                                                                           |                                                                                               |              |                        |                            |               |                | bit 0   |  |

| bit 7                | SMP: Slew                                                                                       | Rate Contro                                                                                   | l bit        |                        |                            |               |                |         |  |

|                      |                                                                                                 | or Slave mode                                                                                 |              |                        |                            |               |                |         |  |

|                      |                                                                                                 | ate control dis                                                                               |              |                        |                            |               | 1 MHz)         |         |  |

| bit 6                |                                                                                                 | ate control en                                                                                |              | gn-speed n             | 100e (400 K                | ΠΖ)           |                |         |  |

| bit 0                |                                                                                                 | or Slave mode                                                                                 | <i>.</i>     |                        |                            |               |                |         |  |

|                      | 1 = Enable                                                                                      | SMBus spec                                                                                    | ific inputs  |                        |                            |               |                |         |  |

|                      |                                                                                                 | e SMBus spe                                                                                   | cific inputs |                        |                            |               |                |         |  |

| bit 5                |                                                                                                 | Address bit                                                                                   |              |                        |                            |               |                |         |  |

|                      | <u>In Master n</u><br>Reserved.                                                                 | node:                                                                                         |              |                        |                            |               |                |         |  |

|                      | In Slave me                                                                                     |                                                                                               |              |                        |                            |               |                |         |  |

|                      |                                                                                                 | es that the las                                                                               | -            |                        |                            |               |                |         |  |

| bit 4                |                                                                                                 | es that the las                                                                               | si byte rece |                        | Smilleu was                | audiess       |                |         |  |

| 511 4                | •                                                                                               | <ul> <li>P: Stop bit</li> <li>1 = Indicates that a Stop bit has been detected last</li> </ul> |              |                        |                            |               |                |         |  |

|                      |                                                                                                 | t was not det                                                                                 |              |                        |                            |               |                |         |  |

|                      | Note:                                                                                           | This bit is clo                                                                               | eared on Re  | eset and wh            | nen SSPEN                  | is cleared.   |                |         |  |

| bit 3                | S: Start bit                                                                                    |                                                                                               |              |                        |                            |               |                |         |  |

|                      |                                                                                                 | es that a Star<br>t was not det                                                               |              | en detectec            | llast                      |               |                |         |  |

|                      | Note:                                                                                           | This bit is cl                                                                                |              | eset and wh            | nen SSPEN                  | is cleared    |                |         |  |

| bit 2                | _                                                                                               | Write bit info                                                                                |              |                        |                            |               |                |         |  |

| 511 2                | In Slave me                                                                                     |                                                                                               |              |                        | y)                         |               |                |         |  |

|                      | 1 = Read                                                                                        |                                                                                               |              |                        |                            |               |                |         |  |

|                      | 0 = Write                                                                                       |                                                                                               |              |                        |                            |               |                | <b></b> |  |

|                      | Note:                                                                                           | This bit hold<br>only valid fro                                                               |              |                        |                            |               |                |         |  |

|                      | In Master mode:                                                                                 |                                                                                               |              |                        |                            |               |                |         |  |

|                      | 1 = Transmit is in progress<br>0 = Transmit is not in progress                                  |                                                                                               |              |                        |                            |               |                |         |  |

|                      | <b>Note:</b> ORing this bit with SEN, RSEN, PEN, RCEN or ACKEN will indicate if the MSSP is     |                                                                                               |              |                        |                            |               |                |         |  |

|                      | in Idle mode.                                                                                   |                                                                                               |              |                        |                            |               |                |         |  |

| bit 1                | UA: Update Address (10-bit Slave mode only)                                                     |                                                                                               |              |                        |                            |               |                |         |  |

|                      | 1 = Indicates that the user needs to update the address in the SSPADD register                  |                                                                                               |              |                        |                            |               |                |         |  |

|                      | <ul> <li>0 = Address does not need to be updated</li> <li>BF: Buffer Full Status bit</li> </ul> |                                                                                               |              |                        |                            |               |                |         |  |

| bit 0                |                                                                                                 |                                                                                               | t            |                        |                            |               |                |         |  |

|                      | In Transmit mode:<br>1 = Receive complete, SSPBUF is full                                       |                                                                                               |              |                        |                            |               |                |         |  |

|                      | 0 = Receiv                                                                                      | e not comple                                                                                  | te, SSPBUI   | is empty               |                            |               |                |         |  |

|                      | In Receive                                                                                      |                                                                                               | aroog (dog   | o not includ           | $a + b = \overline{A C K}$ | and Stop hits |                | o full  |  |

|                      |                                                                                                 | ransmit in pro<br>ransmit comp                                                                |              |                        |                            |               |                |         |  |

|                      | Legend:                                                                                         |                                                                                               |              |                        |                            |               |                |         |  |

|                      | R = Reada                                                                                       | ble bit                                                                                       | W = W        | ritable bit            | U = Unir                   | nplemented    | bit, read as ' | 0'      |  |

|                      | - n = Value                                                                                     |                                                                                               | '1' = Bi     |                        |                            | is cleared    | x = Bit is u   |         |  |

|                      |                                                                                                 |                                                                                               |              |                        |                            |               |                |         |  |

#### 9.4.3.2 Reception

When the  $R/\overline{W}$  bit of the address byte is clear and an address match occurs, the  $R/\overline{W}$  bit of the SSPSTAT register is cleared. The received address is loaded into the SSPBUF register and the SDA line is held low (ACK).

When the address byte overflow condition exists, then the No Acknowledge (ACK) pulse is given. An overflow condition is defined as either bit BF (SSPSTAT<0>) is set or bit SSPOV (SSPCON<6>) is set.

An MSSP interrupt is generated for each data transfer byte. Flag bit SSPIF (PIR1<3>) must be cleared in software. The SSPSTAT register is used to determine the status of the byte.

If SEN is enabled (SSPCON<0> = 1), RC3/SCK/SCL will be held low (clock stretch) following each data transfer. The clock must be released by setting bit CKP (SSPCON<4>). See **Section 9.4.4** "**Clock Stretching**" for more detail.

#### 9.4.3.3 Transmission

When the R/W bit of the incoming address byte is set and an address match occurs, the R/W bit of the SSPSTAT register is set. The received address is loaded into the SSPBUF register. The ACK pulse will be sent on the ninth bit and pin RC3/SCK/SCL is held low regardless of SEN (see **Section 9.4.4 "Clock Stretching"** for more detail). By stretching the clock, the master will be unable to assert another clock pulse until the slave is done preparing the transmit data. The transmit data must be loaded into the SSPBUF register, which also loads the SSPSR register. Then pin RC3/SCK/SCL should be enabled by setting bit CKP (SSPCON<4>). The eight data bits are shifted out on the falling edge of the SCL input. This ensures that the SDA signal is valid during the SCL high time (Figure 9-9).

The ACK pulse from the master-receiver is latched on the rising edge of the ninth SCL input pulse. If the SDA line is high (not ACK), then the data transfer is complete. In this case, when the ACK is latched by the slave, the slave logic is reset (resets SSPSTAT register) and the slave monitors for another occurrence of the Start bit. If the SDA line was low (ACK), the next transmit data must be loaded into the SSPBUF register. Again, pin RC3/SCK/SCL must be enabled by setting bit CKP.

An MSSP interrupt is generated for each data transfer byte. The SSPIF bit must be cleared in software and the SSPSTAT register is used to determine the status of the byte. The SSPIF bit is set on the falling edge of the ninth clock pulse.

### 9.4.4 CLOCK STRETCHING

Both 7 and 10-bit Slave modes implement automatic clock stretching during a transmit sequence.

The SEN bit (SSPCON2<0>) allows clock stretching to be enabled during receives. Setting SEN will cause the SCL pin to be held low at the end of each data receive sequence.

#### 9.4.4.1 Clock Stretching for 7-bit Slave Receive Mode (SEN = 1)

In 7-bit Slave Receive mode, <u>on the falling edge of the</u> ninth clock at the end of the ACK sequence, if the BF bit is set, the CKP bit in the SSPCON register is automatically cleared, forcing the SCL output to be held low. The CKP bit being cleared to '0' will assert the SCL line low. The CKP bit must be set in the user's ISR before reception is allowed to continue. By holding the SCL line low, the user has time to service the ISR and read the contents of the SSPBUF before the master device can initiate another receive sequence. This will prevent buffer overruns from occurring (see Figure 9-13).

- Note 1: If the user reads the contents of the SSPBUF before the falling edge of the ninth clock, thus clearing the BF bit, the CKP bit will not be cleared and clock stretching will not occur.

- 2: The CKP bit can be set in software regardless of the state of the BF bit. The user should be careful to clear the BF bit in the ISR before the next receive sequence in order to prevent an overflow condition.

#### 9.4.4.2 Clock Stretching for 10-bit Slave Receive Mode (SEN = 1)

In 10-bit Slave Receive mode, during the address sequence, clock stretching automatically takes place but CKP is not cleared. During this time, if the UA bit is set after the ninth clock, clock stretching is initiated. The UA bit is set after receiving the upper byte of the 10-bit address and following the receive of the second byte of the 10-bit address, with the R/W bit cleared to '0'. The release of the clock line occurs upon updating SSPADD. Clock stretching will occur on each data receive sequence as described in 7-bit mode.

**Note:** If the user polls the UA bit and clears it by updating the SSPADD register before the falling edge of the ninth clock occurs and if the user hasn't cleared the BF bit by reading the SSPBUF register before that time, then the CKP bit will still NOT be asserted low. Clock stretching, on the basis of the state of the BF bit, only occurs during a data sequence, not an address sequence.

### 9.4.4.3 Clock Stretching for 7-bit Slave Transmit Mode

7-bit Slave Transmit mode implements clock stretching by clearing the CKP bit after the falling edge of the ninth clock, if the BF bit is clear. This occurs regardless of the state of the SEN bit.

The user's ISR must set the CKP bit before transmission is allowed to continue. By holding the SCL line low, the user has time to service the ISR and load the contents of the SSPBUF before the master device can initiate another transmit sequence (see Figure 9-9).

| Note 1: | If the user loads the contents of SSPBUF,     |  |  |  |  |  |  |

|---------|-----------------------------------------------|--|--|--|--|--|--|

|         | setting the BF bit before the falling edge of |  |  |  |  |  |  |

|         | the ninth clock, the CKP bit will not be      |  |  |  |  |  |  |

|         | cleared and clock stretching will not occur.  |  |  |  |  |  |  |

| 2:      | The CKP bit can be set in software            |  |  |  |  |  |  |

# regardless of the state of the BF bit.9.4.4.4Clock Stretching for 10-bit Slave

Transmit Mode In 10-bit Slave Transmit mode, clock stretching is controlled during the first two address sequences by the state of the UA bit, just as it is in 10-bit Slave Receive mode. The first two addresses are followed by a third address sequence, which contains the high order bits of the 10-bit address and the R/W bit set to '1'. After the third address sequence is performed, the UA bit is not set, the module is now configured in Transmit mode and clock stretching is controlled by the BF flag as in 7-bit Slave Transmit mode (see Figure 9-11).

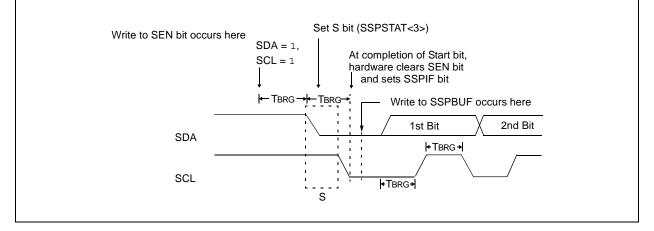

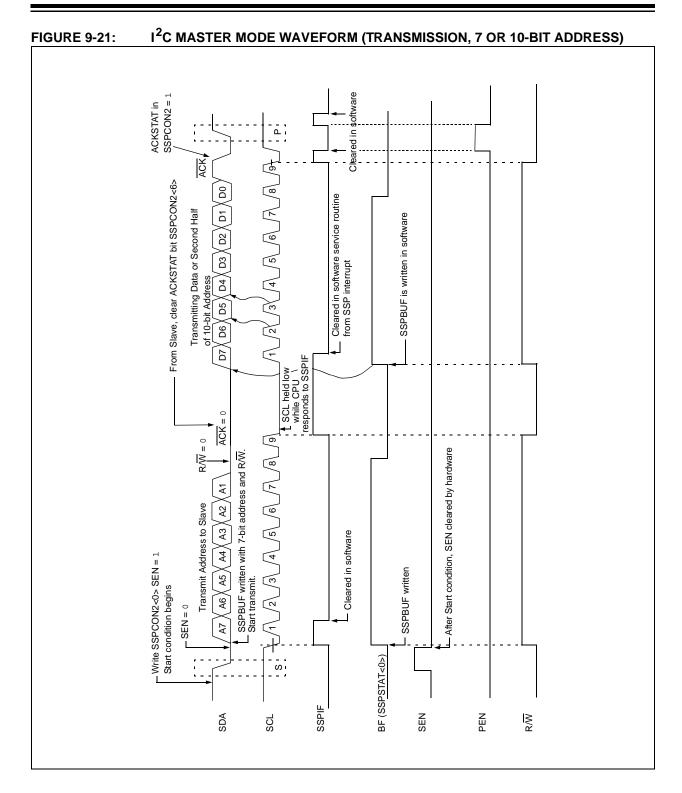

## 9.4.8 I<sup>2</sup>C MASTER MODE START CONDITION TIMING

To initiate a Start condition, the user sets the Start condition enable bit, SEN (SSPCON2<0>). If the SDA and SCL pins are sampled high, the Baud Rate Generator is reloaded with the contents of SSPADD<6:0> and starts its count. If SCL and SDA are both sampled high when the Baud Rate Generator times out (TBRG), the SDA pin is driven low. The action of the SDA being driven low, while SCL is high, is the Start condition and causes the S bit (SSPSTAT<3>) to be set. Following this, the Baud Rate Generator is reloaded with the contents of SSPADD<6:0> and resumes its count. When the Baud Rate Generator times out (TBRG), the SEN bit (SSPCON2<0>) will be automatically cleared by hardware, the Baud Rate Generator is suspended, leaving the SDA line held low and the Start condition is complete.

**Note:** If at the beginning of the Start condition, the SDA and SCL pins are already sampled low, or if during the Start condition, the SCL line is sampled low before the SDA line is driven low, a bus collision occurs, the Bus Collision Interrupt Flag (BCLIF) is set, the Start condition is aborted and the I<sup>2</sup>C module is reset into its Idle state.

## 9.4.8.1 WCOL Status Flag

If the user writes the SSPBUF when a Start sequence is in progress, the WCOL is set and the contents of the buffer are unchanged (the write doesn't occur).

Note: Because queueing of events is not allowed, writing to the lower 5 bits of SSPCON2 is disabled until the Start condition is complete.

## FIGURE 9-19: FIRST START BIT TIMING

|       | SPEN                                                                                                                                               | DVO                        |               |              |              |               |               |            |  |

|-------|----------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------|---------------|--------------|--------------|---------------|---------------|------------|--|

|       |                                                                                                                                                    | RX9                        | SREN          | CREN         | ADDEN        | FERR          | OERR          | RX9D       |  |

|       | bit 7                                                                                                                                              |                            |               |              |              |               |               | bit (      |  |

| bit 7 | SPEN: Ser                                                                                                                                          | ial Port Ena               | ble bit       |              |              |               |               |            |  |

|       | -                                                                                                                                                  | ort enabled                |               | RC7/RX/D     | T and RC6/T  | X/CK pins a   | as serial por | t pins)    |  |

| bit 6 | <b>RX9</b> : 9-bit l                                                                                                                               | Receive Ena                | able bit      |              |              |               |               |            |  |

|       |                                                                                                                                                    | 9-bit recep<br>8-bit recep |               |              |              |               |               |            |  |

| bit 5 | SREN: Sing                                                                                                                                         | gle Receive                | Enable bit    |              |              |               |               |            |  |

|       | <u>Asynchron</u><br>Don't care.                                                                                                                    | ous mode:                  |               |              |              |               |               |            |  |

|       |                                                                                                                                                    | <u>us mode – I</u>         |               |              |              |               |               |            |  |

|       |                                                                                                                                                    | es single rec              |               |              |              |               |               |            |  |

|       |                                                                                                                                                    |                            | reception is  | s complete.  |              |               |               |            |  |

|       | <u>Synchrono</u><br>Don't care.                                                                                                                    | <u>us mode – S</u>         | <u>Slave:</u> |              |              |               |               |            |  |

| bit 4 | CREN: Cor                                                                                                                                          | ntinuous Re                | ceive Enable  | e bit        |              |               |               |            |  |

|       | Asynchronous mode:                                                                                                                                 |                            |               |              |              |               |               |            |  |

|       | <ul> <li>1 = Enables continuous receive</li> <li>0 = Disables continuous receive</li> </ul>                                                        |                            |               |              |              |               |               |            |  |

|       | Synchronous mode:                                                                                                                                  |                            |               |              |              |               |               |            |  |

|       | <ul> <li>1 = Enables continuous receive until enable bit CREN is cleared (CREN overrides SREN)</li> <li>0 = Disables continuous receive</li> </ul> |                            |               |              |              |               |               |            |  |

| bit 3 | ADDEN: Address Detect Enable bit                                                                                                                   |                            |               |              |              |               |               |            |  |

|       | Asynchronous mode 9-bit (RX9 = 1):<br>1 = Enables address detection, enables interrupt and load of the receive buffer when RSR<8>                  |                            |               |              |              |               |               |            |  |

|       | is set<br>0 = Disables address detection, all bytes are received and ninth bit can be used as parity bit                                           |                            |               |              |              |               |               |            |  |

| bit 2 | FERR: Fra                                                                                                                                          |                            |               |              |              |               |               |            |  |

|       |                                                                                                                                                    | g error (can               |               | by reading   | RCREG reg    | ister and red | ceive next v  | alid byte) |  |

| bit 1 | OERR: Ov                                                                                                                                           | errun Error                | bit           |              |              |               |               |            |  |

|       | 1 = Overru<br>0 = No ove                                                                                                                           |                            | be cleared    | by clearing  | bit CREN)    |               |               |            |  |

| bit 0 | <b>RX9D:</b> 9th                                                                                                                                   | bit of Rece                | ived Data (c  | an be parity | bit but must | be calculat   | ed by user f  | irmware)   |  |

| Legend:            |                  |                      |                    |

|--------------------|------------------|----------------------|--------------------|

| R = Readable bit   | W = Writable bit | U = Unimplemented    | bit, read as '0'   |

| - n = Value at POR | '1' = Bit is set | '0' = Bit is cleared | x = Bit is unknown |

## 10.3 USART Synchronous Master Mode

In Synchronous Master mode, the data is transmitted in a half-duplex manner (i.e., transmission and reception do not occur at the same time). When transmitting data, the reception is inhibited and vice versa. Synchronous mode is entered by setting bit, SYNC (TXSTA<4>). In addition, enable bit, SPEN (RCSTA<7>), is set in order to configure the RC6/TX/CK and RC7/RX/DT I/O pins to CK (clock) and DT (data) lines, respectively. The Master mode indicates that the processor transmits the master clock on the CK line. The Master mode is entered by setting bit, CSRC (TXSTA<7>).

#### 10.3.1 USART SYNCHRONOUS MASTER TRANSMISSION

The USART transmitter block diagram is shown in Figure 10-6. The heart of the transmitter is the Transmit (Serial) Shift Register (TSR). The shift register obtains its data from the Read/Write Transmit Buffer register, TXREG. The TXREG register is loaded with data in software. The TSR register is not loaded until the last bit has been transmitted from the previous load. As soon as the last bit is transmitted, the TSR is loaded with new data from the TXREG (if available). Once the TXREG register transfers the data to the TSR register (occurs in one TCYCLE), the TXREG is empty and interrupt bit, TXIF (PIR1<4>), is set. The interrupt can be enabled/disabled by setting/clearing enable bit TXIE (PIE1<4>). Flag bit TXIF will be set regardless of the state of enable bit TXIE and cannot be cleared in software. It will reset only when new data is loaded into the TXREG register. While flag bit TXIF indicates the status of the TXREG register, another bit, TRMT (TXSTA<1>), shows the status of the TSR register. TRMT is a readonly bit which is set when the TSR is empty. No interrupt logic is tied to this bit so the user has to poll this bit in order to determine if the TSR register is empty. The TSR is not mapped in data memory so it is not available to the user.

Transmission is enabled by setting enable bit, TXEN (TXSTA<5>). The actual transmission will not occur until the TXREG register has been loaded with data. The first data bit will be shifted out on the next available rising edge of the clock on the CK line. Data out is stable around the falling edge of the synchronous clock (Figure 10-9). The transmission can also be started by first loading the TXREG register and then setting bit TXEN (Figure 10-10). This is advantageous when slow baud rates are selected since the BRG is kept in Reset when bits TXEN, CREN and SREN are clear. Setting enable bit TXEN will start the BRG, creating a shift clock immediately. Normally, when transmission is first started, the TSR register is empty so a transfer to the TXREG register will result in an immediate transfer to TSR, resulting in an empty TXREG. Back-to-back transfers are possible.

Clearing enable bit TXEN during a transmission will cause the transmission to be aborted and will reset the transmitter. The DT and CK pins will revert to highimpedance. If either bit CREN or bit SREN is set during a transmission, the transmission is aborted and the DT pin reverts to a high-impedance state (for a reception). The CK pin will remain an output if bit CSRC is set (internal clock). The transmitter logic, however, is not reset, although it is disconnected from the pins. In order to reset the transmitter, the user has to clear bit TXEN. If bit SREN is set (to interrupt an on-going transmission and receive a single word), then after the single word is received, bit SREN will be cleared and the serial port will revert back to transmitting since bit TXEN is still set. The DT line will immediately switch from High-Impedance Receive mode to transmit and start driving. To avoid this, bit TXEN should be cleared.

In order to select 9-bit transmission, the TX9 (TXSTA<6>) bit should be set and the ninth bit should be written to bit TX9D (TXSTA<0>). The ninth bit must be written before writing the 8-bit data to the TXREG register. This is because a data write to the TXREG can result in an immediate transfer of the data to the TSR register (if the TSR is empty). If the TSR was empty and the TXREG was written before writing the "new" TX9D, the "present" value of bit TX9D is loaded.

Steps to follow when setting up a Synchronous Master Transmission:

- 1. Initialize the SPBRG register for the appropriate baud rate (Section 10.1 "USART Baud Rate Generator (BRG)").

- 2. Enable the synchronous master serial port by setting bits SYNC, SPEN and CSRC.

- 3. If interrupts are desired, set enable bit TXIE.

- 4. If 9-bit transmission is desired, set bit TX9.

- 5. Enable the transmission by setting bit TXEN.

- 6. If 9-bit transmission is selected, the ninth bit should be loaded in bit TX9D.

- 7. Start transmission by loading data to the TXREG register.

- 8. If using interrupts, ensure that GIE and PEIE (bits 7 and 6) of the INTCON register are set.

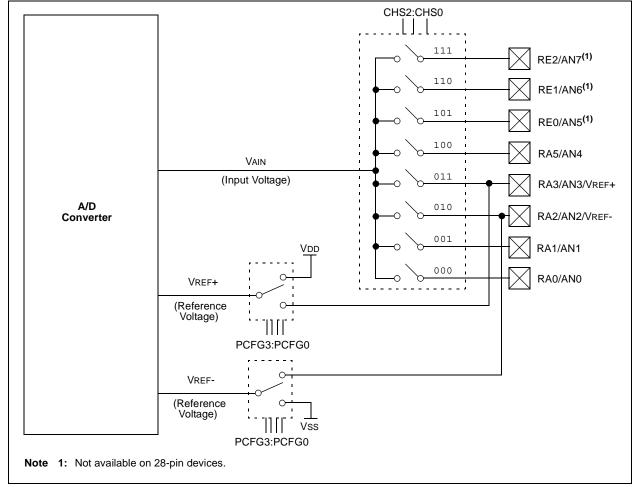

## 11.0 ANALOG-TO-DIGITAL CONVERTER (A/D) MODULE

The Analog-to-Digital (A/D) Converter module has five inputs for the 28-pin devices and eight for the 40/44-pin devices.

The conversion of an analog input signal results in a corresponding 10-bit digital number. The A/D module has high and low-voltage reference input that is software selectable to some combination of VDD, Vss, RA2 or RA3.

The A/D converter has a unique feature of being able to operate while the device is in Sleep mode. To operate in Sleep, the A/D clock must be derived from the A/D's internal RC oscillator. The A/D module has four registers. These registers are:

- A/D Result High Register (ADRESH)

- A/D Result Low Register (ADRESL)

- A/D Control Register 0 (ADCON0)

- A/D Control Register 1 (ADCON1)

The ADCON0 register, shown in Register 11-1, controls the operation of the A/D module. The ADCON1 register, shown in Register 11-2, configures the functions of the port pins. The port pins can be configured as analog inputs (RA3 can also be the voltage reference) or as digital I/O.

Additional information on using the A/D module can be found in the PIC<sup>®</sup> Mid-Range MCU Family Reference Manual (DS33023).

| REGISTER 11-1: | ADCON0 REGISTER (ADDRESS 1Fh |

|----------------|------------------------------|

|----------------|------------------------------|

| R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0   | U-0 | R/W-0 |

|-------|-------|-------|-------|-------|---------|-----|-------|

| ADCS1 | ADCS0 | CHS2  | CHS1  | CHS0  | GO/DONE | Ι   | ADON  |

| bit 7 |       |       |       |       |         |     | bit 0 |

bit 7-6 ADCS1:ADCS0: A/D Conversion Clock Select bits (ADCON0 bits in **bold**)

| ADCON1<br><adcs2></adcs2> | ADCON0<br><adcs1:adcs0></adcs1:adcs0> | Clock Conversion                                        |  |  |

|---------------------------|---------------------------------------|---------------------------------------------------------|--|--|

| 0                         | 00                                    | Fosc/2                                                  |  |  |

| 0                         | 01                                    | Fosc/8                                                  |  |  |

| 0                         | 10                                    | Fosc/32                                                 |  |  |

| 0 11                      |                                       | FRC (clock derived from the internal A/D RC oscillator) |  |  |

| 1                         | 00                                    | Fosc/4                                                  |  |  |

| 1                         | 01                                    | Fosc/16                                                 |  |  |

| 1                         | 10                                    | Fosc/64                                                 |  |  |

| 1                         | 11                                    | FRC (clock derived from the internal A/D RC oscillator) |  |  |

bit 5-3 CHS2:CHS0: Analog Channel Select bits

- 000 = Channel 0 (AN0)

- 001 = Channel 1 (AN1)

- 010 = Channel 2 (AN2)

- 011 = Channel 3 (AN3)

- 100 = Channel 4 (AN4)

- 101 = Channel 5 (AN5)

- 110 = Channel 6 (AN6)

- 111 = Channel 7 (AN7)

- **Note:** The PIC16F873A/876A devices only implement A/D channels 0 through 4; the unimplemented selections are reserved. Do not select any unimplemented channels with these devices.

bit 2 GO/DONE: A/D Conversion Status bit

<u>When ADON = 1:</u>

- 1 = A/D conversion in progress (setting this bit starts the A/D conversion which is automatically cleared by hardware when the A/D conversion is complete)

- 0 = A/D conversion not in progress

- bit 1 Unimplemented: Read as '0'

#### bit 0 ADON: A/D On bit

1 = A/D converter module is powered up

0 = A/D converter module is shut-off and consumes no operating current

## Legend:

| Legend:            |                  |                      |                    |

|--------------------|------------------|----------------------|--------------------|

| R = Readable bit   | W = Writable bit | U = Unimplemented    | l bit, read as '0' |

| - n = Value at POR | '1' = Bit is set | '0' = Bit is cleared | x = Bit is unknown |

The ADRESH:ADRESL registers contain the 10-bit result of the A/D conversion. When the A/D conversion is complete, the result is loaded into this A/D Result register pair, the GO/DONE bit (ADCON0<2>) is cleared and the A/D interrupt flag bit ADIF is set. The block diagram of the A/D module is shown in Figure 11-1.

After the A/D module has been configured as desired, the selected channel must be acquired before the conversion is started. The analog input channels must have their corresponding TRIS bits selected as inputs.

To determine sample time, see **Section 11.1 "A/D Acquisition Requirements"**. After this acquisition time has elapsed, the A/D conversion can be started.

To do an A/D Conversion, follow these steps:

- 1. Configure the A/D module:

- Configure analog pins/voltage reference and digital I/O (ADCON1)

- Select A/D input channel (ADCON0)

- Select A/D conversion clock (ADCON0)

- Turn on A/D module (ADCON0)

- 2. Configure A/D interrupt (if desired):

- Clear ADIF bit

- Set ADIE bit

- Set PEIE bit

- · Set GIE bit

- 3. Wait the required acquisition time.

- 4. Start conversion:

- Set GO/DONE bit (ADCON0)

- 5. Wait for A/D conversion to complete by either:

- Polling for the GO/DONE bit to be cleared (interrupts disabled); OR

- Waiting for the A/D interrupt

- 6. Read A/D Result register pair (ADRESH:ADRESL), clear bit ADIF if required.

- 7. For the next conversion, go to step 1 or step 2 as required. The A/D conversion time per bit is defined as TAD.

## FIGURE 11-1: A/D BLOCK DIAGRAM

## 14.0 SPECIAL FEATURES OF THE CPU

All PIC16F87XA devices have a host of features intended to maximize system reliability, minimize cost through elimination of external components, provide power saving operating modes and offer code protection. These are:

- Oscillator Selection

- Reset

- Power-on Reset (POR)

- Power-up Timer (PWRT)

- Oscillator Start-up Timer (OST)

- Brown-out Reset (BOR)

- Interrupts

- Watchdog Timer (WDT)

- Sleep

- Code Protection

- ID Locations

- In-Circuit Serial Programming

- Low-Voltage In-Circuit Serial Programming

- In-Circuit Debugger

PIC16F87XA devices have a Watchdog Timer which can be shut-off only through configuration bits. It runs off its own RC oscillator for added reliability.

There are two timers that offer necessary delays on power-up. One is the Oscillator Start-up Timer (OST), intended to keep the chip in Reset until the crystal oscillator is stable. The other is the Power-up Timer (PWRT), which provides a fixed delay of 72 ms (nominal) on power-up only. It is designed to keep the part in Reset while the power supply stabilizes. With these two timers on-chip, most applications need no external Reset circuitry. Sleep mode is designed to offer a very low current power-down mode. The user can wake-up from Sleep through external Reset, Watchdog Timer wake-up or through an interrupt.

Several oscillator options are also made available to allow the part to fit the application. The RC oscillator option saves system cost while the LP crystal option saves power. A set of configuration bits is used to select various options.

Additional information on special features is available in the PIC<sup>®</sup> Mid-Range MCU Family Reference Manual (DS33023).

## 14.1 Configuration Bits

The configuration bits can be programmed (read as '0'), or left unprogrammed (read as '1') to select various device configurations. The erased or unprogrammed value of the Configuration Word register is 3FFFh. These bits are mapped in program memory location 2007h.

It is important to note that address 2007h is beyond the user program memory space which can be accessed only during programming.

## 17.3 Timing Parameter Symbology

The timing parameter symbols have been created following one of the following formats:

| 1. TppS2ppS           |                                     | 3. Tcc:st | (I <sup>2</sup> C specifications only) |

|-----------------------|-------------------------------------|-----------|----------------------------------------|

| 2. TppS               |                                     | 4. Ts     | (I <sup>2</sup> C specifications only) |

| Т                     |                                     |           |                                        |

| F                     | Frequency                           | Т         | Time                                   |

| Lowerca               | se letters (pp) and their meanings: |           |                                        |

| рр                    |                                     |           |                                        |

| CC                    | CCP1                                | OSC       | OSC1                                   |

| ck                    | CLKO                                | rd        | RD                                     |

| CS                    | CS                                  | rw        | RD or WR                               |

| di                    | SDI                                 | SC        | SCK                                    |

| do                    | SDO                                 | SS        | SS                                     |

| dt                    | Data in                             | tO        | TOCKI                                  |

| io                    | I/O port                            | t1        | T1CKI                                  |

| mc                    | MCLR                                | wr        | WR                                     |

|                       | se letters and their meanings:      |           |                                        |

| S                     |                                     |           |                                        |

| F                     | Fall                                | Р         | Period                                 |

| Н                     | High                                | R         | Rise                                   |

| I                     | Invalid (High-impedance)            | V         | Valid                                  |

| L                     | Low                                 | Z         | High-impedance                         |

| I <sup>2</sup> C only |                                     |           |                                        |

| AA                    | output access                       | High      | High                                   |

| BUF                   | Bus free                            | Low       | Low                                    |

| Tcc:st (I             | <sup>2</sup> C specifications only) |           |                                        |

| CC                    |                                     |           |                                        |

| HD                    | Hold                                | SU        | Setup                                  |

| ST                    |                                     |           |                                        |

| DAT                   | Data input hold                     | STO       | Stop condition                         |

| STA                   | Start condition                     |           |                                        |

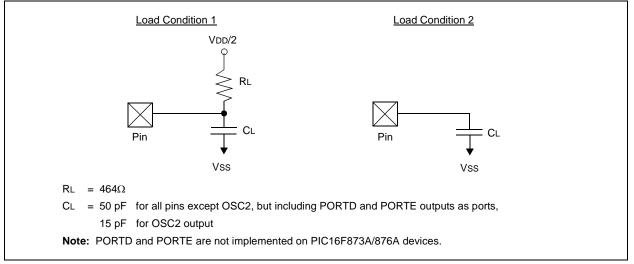

## FIGURE 17-3: LOAD CONDITIONS

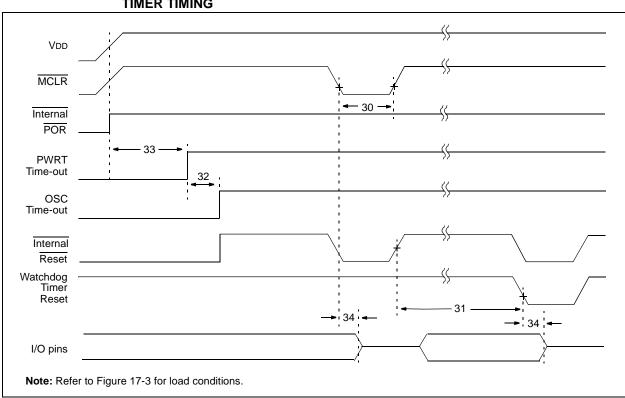

## FIGURE 17-6: RESET, WATCHDOG TIMER, OSCILLATOR START-UP TIMER AND POWER-UP TIMER TIMING

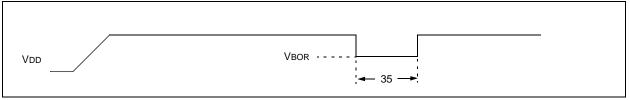

### FIGURE 17-7: BROWN-OUT RESET TIMING

## TABLE 17-5:RESET, WATCHDOG TIMER, OSCILLATOR START-UP TIMER, POWER-UP TIMER<br/>AND BROWN-OUT RESET REQUIREMENTS

| Param<br>No. | Symbol | Characteristic                                           | Min | Тур†      | Max | Units | Conditions               |

|--------------|--------|----------------------------------------------------------|-----|-----------|-----|-------|--------------------------|

| 30           | TMCL   | MCLR Pulse Width (low)                                   | 2   | _         | -   | μS    | VDD = 5V, -40°C to +85°C |

| 31*          | Twdt   | Watchdog Timer Time-out Period<br>(no prescaler)         | 7   | 18        | 33  | ms    | VDD = 5V, -40°C to +85°C |

| 32           | Tost   | Oscillation Start-up Timer Period                        | —   | 1024 Tosc | _   | _     | Tosc = OSC1 period       |

| 33*          | TPWRT  | Power-up Timer Period                                    | 28  | 72        | 132 | ms    | VDD = 5V, -40°C to +85°C |

| 34           | Tıoz   | I/O High-Impedance from MCLR Low or Watchdog Timer Reset | —   | _         | 2.1 | μS    |                          |

| 35           | TBOR   | Brown-out Reset Pulse Width                              | 100 | —         | _   | μS    | $VDD \leq VBOR (D005)$   |

\* These parameters are characterized but not tested.

† Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

## APPENDIX A: REVISION HISTORY

## **Revision A (November 2001)**

Original data sheet for PIC16F87XA devices. The devices presented are enhanced versions of the PIC16F87X microcontrollers discussed in the *"PIC16F87X Data Sheet"* (DS30292).

## **Revision B (October 2003)**

This revision includes the DC and AC Characteristics Graphs and Tables. The Electrical Specifications in **Section 17.0 "Electrical Characteristics"** have been updated and there have been minor corrections to the data sheet text.

## Revision C (January 2013)

Added a note to each package outline drawing.

## APPENDIX B: DEVICE DIFFERENCES

The differences between the devices in this data sheet are listed in Table B-1.

|                                        | PIC16F873A                                              | PIC16F874A                                              | PIC16F876A                                              | PIC16F877A                                              |

|----------------------------------------|---------------------------------------------------------|---------------------------------------------------------|---------------------------------------------------------|---------------------------------------------------------|

| Flash Program Memory<br>(14-bit words) | 4K                                                      | 4K                                                      | 8K                                                      | 8K                                                      |

| Data Memory (bytes)                    | 192                                                     | 192                                                     | 368                                                     | 368                                                     |

| EEPROM Data Memory (bytes)             | 128                                                     | 128                                                     | 256                                                     | 256                                                     |

| Interrupts                             | 14                                                      | 15                                                      | 14                                                      | 15                                                      |

| I/O Ports                              | Ports A, B, C                                           | Ports A, B, C, D, E                                     | Ports A, B, C                                           | Ports A, B, C, D, E                                     |

| Serial Communications                  | MSSP, USART                                             | MSSP, USART                                             | MSSP, USART                                             | MSSP, USART                                             |

| Parallel Slave Port                    | No                                                      | Yes                                                     | No                                                      | Yes                                                     |

| 10-bit Analog-to-Digital Module        | 5 input channels                                        | 8 input channels                                        | 5 input channels                                        | 8 input channels                                        |

| Packages                               | 28-pin PDIP<br>28-pin SOIC<br>28-pin SSOP<br>28-pin QFN | 40-pin PDIP<br>44-pin PLCC<br>44-pin TQFP<br>44-pin QFN | 28-pin PDIP<br>28-pin SOIC<br>28-pin SSOP<br>28-pin QFN | 40-pin PDIP<br>44-pin PLCC<br>44-pin TQFP<br>44-pin QFN |

| Capture/Compare/PWM Requirements           |            |

|--------------------------------------------|------------|

| (CCP1 and CCP2)                            |            |

| CCP. See Capture/Compare/PWM.              |            |

| CCP1CON Register                           |            |

| CCP2CON Register                           |            |

| CCPR1H Register                            |            |

| CCPR1L Register                            | 19, 63     |

| CCPR2H Register                            |            |

| CCPR2L Register                            |            |

| CCPxM0 Bit                                 |            |

| CCPxM1 Bit                                 | 64         |

| CCPxM2 Bit                                 | 64         |

| CCPxM3 Bit                                 | 64         |

| CCPxX Bit                                  | 64         |

| CCPxY Bit                                  |            |

| CLKO and I/O Timing Requirements           | 183        |

| CMCON Register                             | 20         |

| Code Examples                              |            |

| Call of a Subroutine in Page 1 from Page 0 |            |

| Indirect Addressing                        |            |

| Initializing PORTA                         |            |

| Loading the SSPBUF (SSPSR) Register        |            |

| Reading Data EEPROM                        | 35         |

| Reading Flash Program Memory               |            |

| Saving Status, W and PCLATH Registers      |            |

| in RAM                                     |            |

| Writing to Data EEPROM                     |            |

| Writing to Flash Program Memory            |            |

| Code Protection                            | . 143, 157 |

| Comparator Module                          | 135        |

| Analog Input Connection                    |            |

| Considerations                             |            |

| Associated Registers                       |            |

| Configuration                              | 136        |

| Effects of a Reset                         | 139        |

| Interrupts                                 | 138        |

| Operation                                  |            |

| Operation During Sleep                     | 139        |

| Outputs                                    |            |

| Reference                                  |            |

| Response Time                              |            |

| Comparator Specifications                  |            |

| Comparator Voltage Reference               |            |

| Associated Registers                       |            |

| Computed GOTO                              |            |

| Configuration Bits                         | 143        |

| Configuration Word                         |            |

| Conversion Considerations                  |            |

| CVRCON Register                            |            |