Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                    |

|----------------------------|---------------------------------------------------------------------------|

| Core Processor             | PIC                                                                       |

| Core Size                  | 8-Bit                                                                     |

| Speed                      | 20MHz                                                                     |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                         |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                     |

| Number of I/O              | 22                                                                        |

| Program Memory Size        | 14KB (8K x 14)                                                            |

| Program Memory Type        | FLASH                                                                     |

| EEPROM Size                | 256 x 8                                                                   |

| RAM Size                   | 368 x 8                                                                   |

| Voltage - Supply (Vcc/Vdd) | 4V ~ 5.5V                                                                 |

| Data Converters            | A/D 5x10b                                                                 |

| Oscillator Type            | External                                                                  |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                         |

| Mounting Type              | Surface Mount                                                             |

| Package / Case             | 28-VQFN Exposed Pad                                                       |

| Supplier Device Package    | 28-QFN (6x6)                                                              |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16f876a-i-ml |

|                            |                                                                           |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

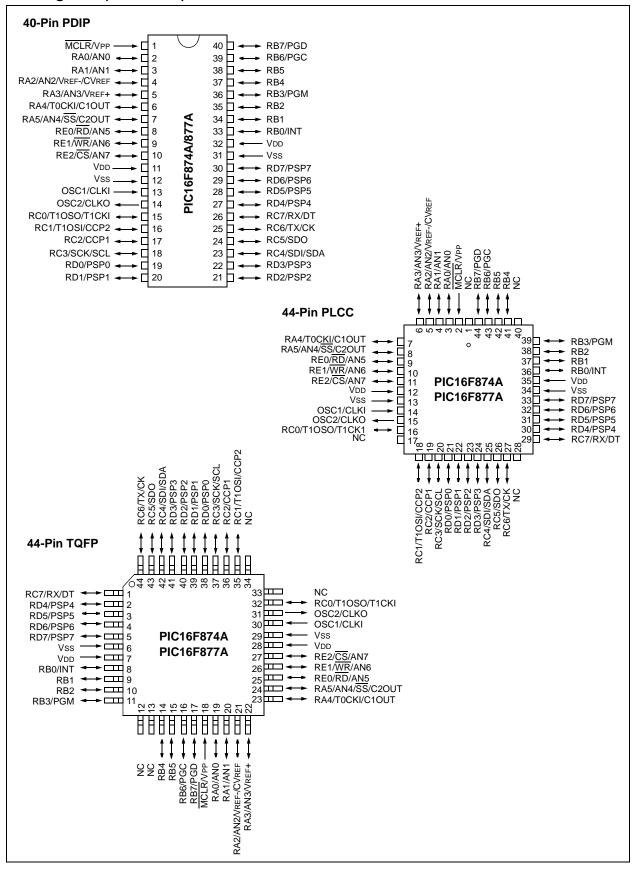

# **Pin Diagrams (Continued)**

| 1 1 4 1 | սու | 2-3: |  |

|---------|-----|------|--|

## PIC16F876A/877A REGISTER FILE MAP

| Indirect addr.(*)    | 00h         | Indirect addr.(*)             |           | Indirect addr.(*)   | 100h          | Indirect addr.(*)       | 10 |

|----------------------|-------------|-------------------------------|-----------|---------------------|---------------|-------------------------|----|

| TMR0                 | 00n<br>01h  | OPTION REG                    | 80h       | TMR0                | 100h          | OPTION_REG              | 18 |

| PCL                  | 01h<br>02h  |                               | 81h       | PCL                 | 10111<br>102h |                         | 18 |

|                      | 02n<br>03h  | PCL<br>STATUS                 | 82h       | STATUS              | 10211<br>103h | PCL<br>STATUS           | 18 |

| STATUS               | 03n<br>04h  |                               | 83h       | FSR                 | 103n<br>104h  |                         | 18 |

| FSR                  |             | FSR                           | 84h       | FSR                 | 1041<br>105h  | FSR                     | 18 |

| PORTA                | 05h<br>06h  | TRISA                         | 85h       | DODTD               | 105h          | TRISB                   | 18 |

| PORTB                |             | TRISB                         | 86h       | PORTB               | 106n<br>107h  | TRISB                   | 18 |

|                      | 07h         | TRISC<br>TRISD <sup>(1)</sup> | 87h       |                     | 1071<br>108h  |                         | 18 |

| PORTD <sup>(1)</sup> | 08h         | TRISD <sup>(1)</sup>          | 88h       |                     | 109h          |                         | 18 |

| PORTE <sup>(1)</sup> | 09h         |                               | 89h       | PCLATH              | 1091<br>10Ah  | PCLATH                  | 18 |

| PCLATH               | 0Ah         | PCLATH                        | 8Ah       |                     | 10An<br>10Bh  | INTCON                  | 18 |

| INTCON               | 0Bh         | INTCON                        | 8Bh       | INTCON              | 10Bn<br>10Ch  | EECON1                  | 18 |

| PIR1                 | 0Ch         | PIE1                          | 8Ch       | EEDATA              |               |                         | 18 |

| PIR2                 | 0Dh         | PIE2                          | 8Dh       | EEADR               | 10Dh          | EECON2                  | 18 |

| TMR1L                | 0Eh         | PCON                          | 8Eh       | EEDATH              | 10Eh          | Reserved <sup>(2)</sup> | 18 |

| TMR1H                | 0Fh         |                               | 8Fh       | EEADRH              | 10Fh          | Reserved <sup>(2)</sup> | 18 |

| T1CON                | 10h         |                               | 90h       |                     | 110h          |                         | 19 |

| TMR2                 | 11h         | SSPCON2                       | 91h       |                     | 111h          |                         | 19 |

| T2CON                | 12h         | PR2                           | 92h       |                     | 112h          |                         | 19 |

| SSPBUF               | 13h         | SSPADD                        | 93h       |                     | 113h          |                         | 19 |

| SSPCON               | 14h         | SSPSTAT                       | 94h       |                     | 114h          |                         | 19 |

| CCPR1L               | 15h         |                               | 95h       |                     | 115h          |                         | 19 |

| CCPR1H               | 16h         |                               | 96h       | Conorol             | 116h          | Conorol                 | 19 |

| CCP1CON              | 17h         |                               | 97h       | General<br>Purpose  | 117h          | General<br>Purpose      | 19 |

| RCSTA                | 18h         | TXSTA                         | 98h       | Register            | 118h          | Register                | 19 |

| TXREG                | 19h         | SPBRG                         | 99h       | 16 Bytes            | 119h          | 16 Bytes                | 19 |

| RCREG                | 1Ah         |                               | 9Ah       |                     | 11Ah          |                         | 19 |

| CCPR2L               | 1Bh         |                               | 9Bh       |                     | 11Bh          |                         | 19 |

| CCPR2H               | 1Ch         | CMCON                         | 9Ch       |                     | 11Ch          |                         | 19 |

| CCP2CON              | 1Dh         | CVRCON                        | 9Dh       |                     | 11Dh          |                         | 19 |

| ADRESH               | 1Eh         | ADRESL                        | 9Eh       |                     | 11Eh          |                         | 19 |

| ADCON0               | 1Fh         | ADCON1                        | 9Fh       |                     | 11Fh          |                         | 19 |

|                      | 20h         |                               | A0h       |                     | 120h          |                         | 1A |

|                      |             | General                       |           | General             |               | General                 |    |

| General              |             | Purpose                       |           | Purpose             |               | Purpose                 |    |

| Purpose              |             | Register                      |           | Register            |               | Register                |    |

| Register             |             | 80 Bytes                      |           | 80 Bytes            |               | 80 Bytes                |    |

| 96 Bytes             |             |                               | EFh       |                     | 16Fh          |                         | 1E |

|                      |             | accesses                      | F0h       | 200005005           | 170h          | accesses                | 1F |

|                      |             | 70h-7Fh                       |           | accesses<br>70h-7Fh |               | 70h - 7Fh               |    |

| <b>_</b>             | 7Fh         |                               | FFh       |                     | 17Fh          |                         | 1F |

| Bank 0               |             | Bank 1                        |           | Bank 2              |               | Bank 3                  |    |

| Unimple              | mented d    | ata memory locati             | ons. read | <b>as</b> '0'.      |               |                         |    |

|                      | iysical reg | -                             |           |                     |               |                         |    |

# PIC16F87XA

| Address              | Name       | Bit 7                | Bit 6         | Bit 5                     | Bit 4          | Bit 3        | Bit 2            | Bit 1         | Bit 0        | Value on:<br>POR, BOR | Details<br>on page |

|----------------------|------------|----------------------|---------------|---------------------------|----------------|--------------|------------------|---------------|--------------|-----------------------|--------------------|

| Bank 1               |            |                      |               |                           |                |              |                  |               |              |                       |                    |

| 80h <sup>(3)</sup>   | INDF       | Addressing           | this locatio  | n uses cont               | ents of FSR t  | o address d  | ata memory (     | not a physic  | al register) | 0000 0000             | 31, 150            |

| 81h                  | OPTION_REG | RBPU                 | INTEDG        | TOCS                      | T0SE           | PSA          | PS2              | PS1           | PS0          | 1111 1111             | 23, 150            |

| 82h <sup>(3)</sup>   | PCL        | Program C            | ounter (PC)   | Least Sign                | ificant Byte   |              |                  |               |              | 0000 0000             | 30, 150            |

| 83h <sup>(3)</sup>   | STATUS     | IRP                  | RP1           | RP0                       | TO             | PD           | Z                | DC            | С            | 0001 1xxx             | 22, 150            |

| 84h <sup>(3)</sup>   | FSR        | Indirect Da          | ta Memory     | Address Po                | inter          |              |                  |               |              | xxxx xxxx             | 31, 150            |

| 85h                  | TRISA      |                      |               | PORTA Da                  | ta Direction F | Register     |                  |               |              | 11 1111               | 43, 150            |

| 86h                  | TRISB      | PORTB Da             | ata Direction | Register                  |                |              |                  |               |              | 1111 1111             | 45, 150            |

| 87h                  | TRISC      | PORTC Da             | ata Directior | Register                  |                |              |                  |               |              | 1111 1111             | 47, 150            |

| 88h <sup>(4)</sup>   | TRISD      | PORTD Da             | ata Directior | n Register                |                |              |                  |               |              | 1111 1111             | 48, 151            |

| 89h <sup>(4)</sup>   | TRISE      | IBF                  | OBF           | IBOV                      | PSPMODE        |              | PORTE Dat        | a Direction I | bits         | 0000 -111             | 50, 151            |

| 8Ah <sup>(1,3)</sup> | PCLATH     | —                    |               |                           | Write Buffer   | for the uppe | er 5 bits of the | e Program C   | Counter      | 0 0000                | 30, 150            |

| 8Bh <sup>(3)</sup>   | INTCON     | GIE                  | PEIE          | TMR0IE                    | INTE           | RBIE         | TMR0IF           | INTF          | RBIF         | 0000 000x             | 24, 150            |

| 8Ch                  | PIE1       | PSPIE <sup>(2)</sup> | ADIE          | RCIE                      | TXIE           | SSPIE        | CCP1IE           | TMR2IE        | TMR1IE       | 0000 0000             | 25, 151            |

| 8Dh                  | PIE2       | —                    | CMIE          |                           | EEIE           | BCLIE        | —                | _             | CCP2IE       | -0-0 00               | 27, 151            |

| 8Eh                  | PCON       | _                    |               |                           | _              |              | _                | POR           | BOR          | dd                    | 29, 151            |

| 8Fh                  | —          | Unimpleme            | ented         |                           |                |              |                  |               |              | —                     |                    |

| 90h                  | —          | Unimpleme            | ented         |                           |                |              |                  |               |              | _                     | _                  |

| 91h                  | SSPCON2    | GCEN                 | ACKSTAT       | ACKDT                     | ACKEN          | RCEN         | PEN              | RSEN          | SEN          | 0000 0000             | 83, 151            |

| 92h                  | PR2        | Timer2 Per           | riod Registe  | r                         |                |              |                  |               |              | 1111 1111             | 62, 151            |

| 93h                  | SSPADD     | Synchrono            | us Serial Po  | ort (I <sup>2</sup> C mod | e) Address R   | egister      |                  |               |              | 0000 0000             | 79, 151            |

| 94h                  | SSPSTAT    | SMP                  | CKE           | D/A                       | Р              | S            | R/W              | UA            | BF           | 0000 0000             | 79, 151            |

| 95h                  | —          | Unimpleme            | ented         |                           | •              |              |                  |               | •            | —                     |                    |

| 96h                  |            | Unimpleme            | ented         |                           |                |              |                  |               |              | —                     |                    |

| 97h                  | —          | Unimpleme            | ented         |                           |                |              |                  |               |              | —                     |                    |

| 98h                  | TXSTA      | CSRC                 | TX9           | TXEN                      | SYNC           | _            | BRGH             | TRMT          | TX9D         | 0000 -010             | 111, 151           |

| 99h                  | SPBRG      | Baud Rate            | Generator     | Register                  |                |              |                  |               |              | 0000 0000             | 113, 151           |

| 9Ah                  | —          | Unimpleme            | ented         |                           |                |              |                  |               |              | _                     | _                  |

| 9Bh                  | _          | Unimpleme            | ented         |                           |                |              |                  |               |              | _                     | —                  |

| 9Ch                  | CMCON      | C2OUT                | C1OUT         | C2INV                     | C1INV          | CIS          | CM2              | CM1           | CM0          | 0000 0111             | 135, 151           |

| 9Dh                  | CVRCON     | CVREN                | CVROE         | CVRR                      | _              | CVR3         | CVR2             | CVR1          | CVR0         | 000- 0000             | 141, 151           |

| 9Eh                  | ADRESL     | A/D Result           | Register Lo   | w Byte                    |                |              |                  |               |              | xxxx xxxx             | 133, 151           |

| 9Fh                  | ADCON1     | ADFM                 | ADCS2         | _                         | _              | PCFG3        | PCFG2            | PCFG1         | PCFG0        | 00 0000               | 128, 151           |

####

x = unknown, u = unchanged, q = value depends on condition, - = unimplemented, read as '0', r = reserved. Legend: Shaded locations are unimplemented, read as '0'.

Note 1: The upper byte of the program counter is not directly accessible. PCLATH is a holding register for the PC<12:8>, whose contents are transferred to the upper byte of the program counter.

2: Bits PSPIE and PSPIF are reserved on PIC16F873A/876A devices; always maintain these bits clear.

3: These registers can be addressed from any bank.

4: PORTD, PORTE, TRISD and TRISE are not implemented on PIC16F873A/876A devices, read as '0'.

5: Bit 4 of EEADRH implemented only on the PIC16F876A/877A devices.

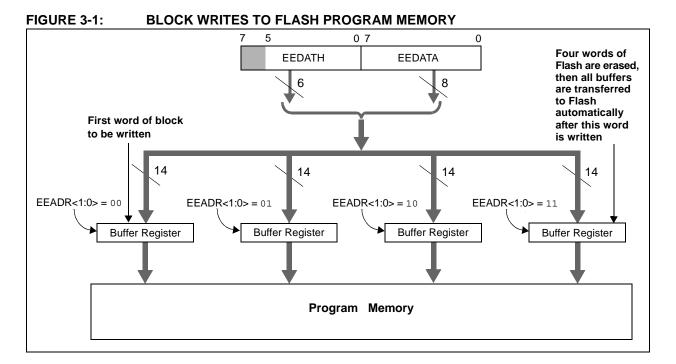

# 3.6 Writing to Flash Program Memory

Flash program memory may only be written to if the destination address is in a segment of memory that is not write-protected, as defined in bits WRT1:WRT0 of the device configuration word (Register 14-1). Flash program memory must be written in four-word blocks. A block consists of four words with sequential addresses, with a lower boundary defined by an address, where EEADR<1:0> = 00. At the same time, all block writes to program memory are done as erase and write operations. The write operation is edge-aligned and cannot occur across boundaries.

To write program data, it must first be loaded into the buffer registers (see Figure 3-1). This is accomplished by first writing the destination address to EEADR and EEADRH and then writing the data to EEDATA and EEDATH. After the address and data have been set up, then the following sequence of events must be executed:

- 1. Set the EEPGD control bit (EECON1<7>).

- 2. Write 55h, then AAh, to EECON2 (Flash programming sequence).

- 3. Set the WR control bit (EECON1<1>).

All four buffer register locations **MUST** be written to with correct data. If only one, two or three words are being written to in the block of four words, then a read from the program memory location(s) not being written to must be performed. This takes the data from the program location(s) not being written and loads it into the EEDATA and EEDATH registers. Then the sequence of events to transfer data to the buffer registers must be executed. To transfer data from the buffer registers to the program memory, the EEADR and EEADRH must point to the last location in the four-word block (EEADR<1:0> = 11). Then the following sequence of events must be executed:

- 1. Set the EEPGD control bit (EECON1<7>).

- 2. Write 55h, then AAh, to EECON2 (Flash programming sequence).

- Set control bit WR (EECON1<1>) to begin the write operation.

The user must follow the same specific sequence to initiate the write for each word in the program block, writing each program word in sequence (00, 01, 10, 11). When the write is performed on the last word (EEADR<1:0> = 11), the block of four words are automatically erased and the contents of the buffer registers are written into the program memory.

After the "BSF EECON1, WR" instruction, the processor requires two cycles to set up the erase/write operation. The user must place two NOP instructions after the WR bit is set. Since data is being written to buffer registers, the writing of the first three words of the block appears to occur immediately. The processor will halt internal operations for the typical 4 ms, only during the cycle in which the erase takes place (i.e., the last word of the four-word block). This is not Sleep mode as the clocks and peripherals will continue to run. After the write cycle, the processor will resume operation with the third instruction after the EECON1 write instruction. If the sequence is performed to any other location, the action is ignored.

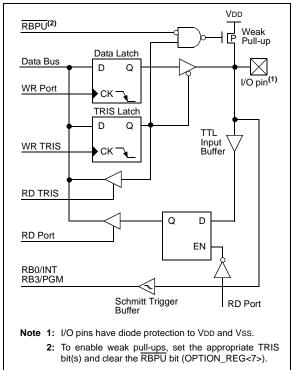

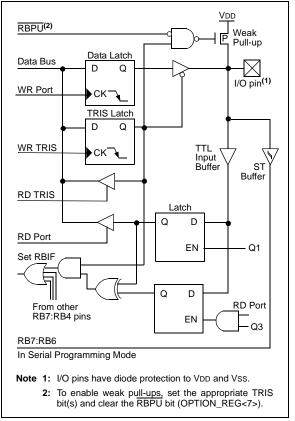

# 4.2 **PORTB and the TRISB Register**

PORTB is an 8-bit wide, bidirectional port. The corresponding data direction register is TRISB. Setting a TRISB bit (= 1) will make the corresponding PORTB pin an input (i.e., put the corresponding output driver in a High-Impedance mode). Clearing a TRISB bit (= 0) will make the corresponding PORTB pin an output (i.e., put the contents of the output latch on the selected pin).

Three pins of PORTB are multiplexed with the In-Circuit Debugger and Low-Voltage Programming function: RB3/PGM, RB6/PGC and RB7/PGD. The alternate functions of these pins are described in **Section 14.0 "Special Features of the CPU"**.

Each of the PORTB pins has a weak internal pull-up. A single control bit can turn on all the pull-ups. This is performed by clearing bit RBPU (OPTION\_REG<7>). The weak pull-up is automatically turned off when the port pin is configured as an output. The pull-ups are disabled on a Power-on Reset.

Four of the PORTB pins, RB7:RB4, have an interrupton-change feature. Only pins configured as inputs can cause this interrupt to occur (i.e., any RB7:RB4 pin configured as an output is excluded from the interrupton-change comparison). The input pins (of RB7:RB4) are compared with the old value latched on the last read of PORTB. The "mismatch" outputs of RB7:RB4 are OR'ed together to generate the RB port change interrupt with flag bit RBIF (INTCON<0>). This interrupt can wake the device from Sleep. The user, in the Interrupt Service Routine, can clear the interrupt in the following manner:

- a) Any read or write of PORTB. This will end the mismatch condition.

- b) Clear flag bit RBIF.

A mismatch condition will continue to set flag bit RBIF. Reading PORTB will end the mismatch condition and allow flag bit RBIF to be cleared.

The interrupt-on-change feature is recommended for wake-up on key depression operation and operations where PORTB is only used for the interrupt-on-change feature. Polling of PORTB is not recommended while using the interrupt-on-change feature.

This interrupt-on-mismatch feature, together with software configurable pull-ups on these four pins, allow easy interface to a keypad and make it possible for wake-up on key depression. Refer to the application note, *AN552, "Implementing Wake-up on Key Stroke*" (DS00552).

RB0/INT is an external interrupt input pin and is configured using the INTEDG bit (OPTION\_REG<6>).

RB0/INT is discussed in detail in **Section 14.11.1 "INT Interrupt**".

## BLOCK DIAGRAM OF RB7:RB4 PINS

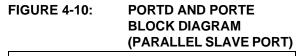

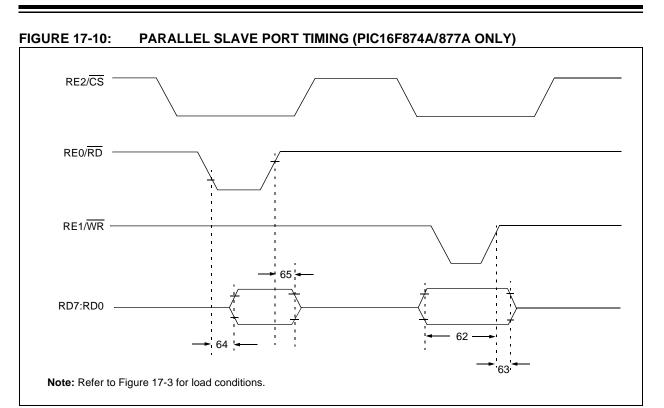

# 4.6 Parallel Slave Port

The Parallel Slave Port (PSP) is not implemented on the PIC16F873A or PIC16F876A.

PORTD operates as an 8-bit wide Parallel Slave Port, or microprocessor port, when control bit PSPMODE (TRISE<4>) is set. In Slave mode, it is asynchronously readable and writable by the external world through RD control input pin, RE0/RD/AN5, and WR control input pin, RE1/WR/AN6.

The PSP can directly interface to an 8-bit microprocessor data bus. The external microprocessor can read or write the PORTD latch as an 8-bit latch. Setting bit PSPMODE enables port pin RE0/RD/AN5 to be the RD input, RE1/WR/AN6 to be the WR input and RE2/CS/AN7 to be the CS (Chip Select) input. For this functionality, the corresponding data direction bits of the TRISE register (TRISE<2:0>) must be configured as inputs (set). The A/D port configuration bits, PCFG3:PCFG0 (ADCON1<3:0>), must be set to configure pins RE2:RE0 as digital I/O.

There are actually two 8-bit latches: one for data output and one for data input. The user writes 8-bit data to the PORTD data latch and reads data from the port pin latch (note that they have the same address). In this mode, the TRISD register is ignored since the external device is controlling the direction of data flow.

A write to the PSP occurs when both the  $\overline{CS}$  and  $\overline{WR}$ lines are first detected low. When either the  $\overline{CS}$  or  $\overline{WR}$ lines become high (level triggered), the Input Buffer Full (IBF) status flag bit (TRISE<7>) is set on the Q4 clock cycle, following the next Q2 cycle, to signal the write is complete (Figure 4-11). The interrupt flag bit, PSPIF (PIR1<7>), is also set on the same Q4 clock cycle. IBF can only be cleared by reading the PORTD input latch. The Input Buffer Overflow (IBOV) status flag bit (TRISE<5>) is set if a second write to the PSP is attempted when the previous byte has not been read out of the buffer.

A read from the PSP occurs when both the CS and RD lines are first detected low. The Output Buffer Full (OBF) status flag bit (TRISE<6>) is cleared immediately (Figure 4-12), indicating that the PORTD latch is waiting to be read by the external bus. When either the CS or RD pin becomes high (level triggered), the interrupt flag bit PSPIF is set on the Q4 clock cycle, following the next Q2 cycle, indicating that the read is complete. OBF remains low until data is written to PORTD by the user firmware. When not in PSP mode, the IBF and OBF bits are held clear. However, if flag bit IBOV was previously set, it must be cleared in firmware.

An interrupt is generated and latched into flag bit PSPIF when a read or write operation is completed. PSPIF must be cleared by the user in firmware and the interrupt can be disabled by clearing the interrupt enable bit PSPIE (PIE1<7>).

| ER 9-2: | SSPCON1: MSSP CONTROL REGISTER 1 (SPI MODE) (ADDRESS 14h)                             |                                                                                                                                                                      |                                                               |                                                |                             |               |             |               |  |

|---------|---------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------|------------------------------------------------|-----------------------------|---------------|-------------|---------------|--|

|         | R/W-0                                                                                 | R/W-0                                                                                                                                                                | R/W-0                                                         | R/W-0                                          | R/W-0                       | R/W-0         | R/W-0       | R/W-0         |  |

|         | WCOL                                                                                  | SSPOV                                                                                                                                                                | SSPEN                                                         | CKP                                            | SSPM3                       | SSPM2         | SSPM1       | SSPM0         |  |

|         | bit 7                                                                                 |                                                                                                                                                                      |                                                               |                                                |                             |               |             | bit 0         |  |

| bit 7   |                                                                                       | /rite Collision                                                                                                                                                      | -                                                             |                                                |                             |               |             |               |  |

|         |                                                                                       | SSPBUF reg<br>ed in software<br>ollision                                                                                                                             |                                                               | en while it i                                  | s still transm              | nitting the p | revious wor | d. (Must be   |  |

| bit 6   | SSPOV: R                                                                              | Receive Over                                                                                                                                                         | flow Indicato                                                 | or bit                                         |                             |               |             |               |  |

|         | <u>SPI Slave</u>                                                                      | mode:                                                                                                                                                                |                                                               |                                                |                             |               |             |               |  |

|         | of ove<br>must<br>cleare                                                              | v byte is rece<br>erflow, the da<br>read the SSI<br>ed in software                                                                                                   | ata in SSPSF<br>PBUF, even                                    | R is lost. Ov                                  | verflow can o               | only occur in | Slave mod   | e. The user   |  |

|         | 0 = No ov                                                                             |                                                                                                                                                                      |                                                               |                                                |                             |               |             |               |  |

|         | Note:                                                                                 |                                                                                                                                                                      |                                                               |                                                | t is not set<br>to the SSPE |               |             | eption (and   |  |

| bit 5   | SSPEN: S                                                                              | Synchronous                                                                                                                                                          | Serial Port E                                                 | Enable bit                                     |                             |               |             |               |  |

|         |                                                                                       | 1 = Enables serial port and configures SCK, SDO, SDI, and $\overline{SS}$ as serial port pins<br>0 = Disables serial port and configures these pins as I/O port pins |                                                               |                                                |                             |               |             |               |  |

|         | <b>Note:</b> When enabled, these pins must be properly configured as input or output. |                                                                                                                                                                      |                                                               |                                                |                             |               |             |               |  |

| bit 4   | CKP: Cloo                                                                             | ck Polarity Se                                                                                                                                                       | elect bit                                                     |                                                |                             |               |             |               |  |

|         |                                                                                       | ate for clock<br>ate for clock                                                                                                                                       | •                                                             |                                                |                             |               |             |               |  |

| bit 3-0 | SSPM3:S                                                                               | SPM0: Sync                                                                                                                                                           | hronous Ser                                                   | ial Port Mod                                   | de Select bits              | 5             |             |               |  |

|         | 0100 = SF<br>0011 = SF<br>0010 = SF<br>0001 = SF                                      | PI Slave mod<br>PI Slave mod<br>PI Master mod<br>PI Master mod<br>PI Master mod                                                                                      | le, clock = S<br>ode, clock =<br>ode, clock =<br>ode, clock = | CK pin. SS<br>TMR2 outpu<br>Fosc/64<br>Fosc/16 | pin control e               |               | can be usec | l as I/O pin. |  |

|         |                                                                                       | PI Master mo                                                                                                                                                         |                                                               |                                                |                             |               |             |               |  |

|         | Note:                                                                                 | Bit combin<br>I <sup>2</sup> C mode o                                                                                                                                |                                                               | becifically lis                                | sted here are               | either rese   | rved or imp | lemented in   |  |

|         |                                                                                       |                                                                                                                                                                      |                                                               |                                                |                             |               |             |               |  |

|         | I a manual.                                                                           |                                                                                                                                                                      |                                                               |                                                |                             |               |             |               |  |

| Legend:            |                  |                      |                    |

|--------------------|------------------|----------------------|--------------------|

| R = Readable bit   | W = Writable bit | U = Unimplemented    | bit, read as '0'   |

| - n = Value at POR | '1' = Bit is set | '0' = Bit is cleared | x = Bit is unknown |

# REGISTER 9-2: SSPCON1: MSSP CONTROL REGISTER 1 (SPI MODE) (ADDRESS 14h)

# PIC16F87XA

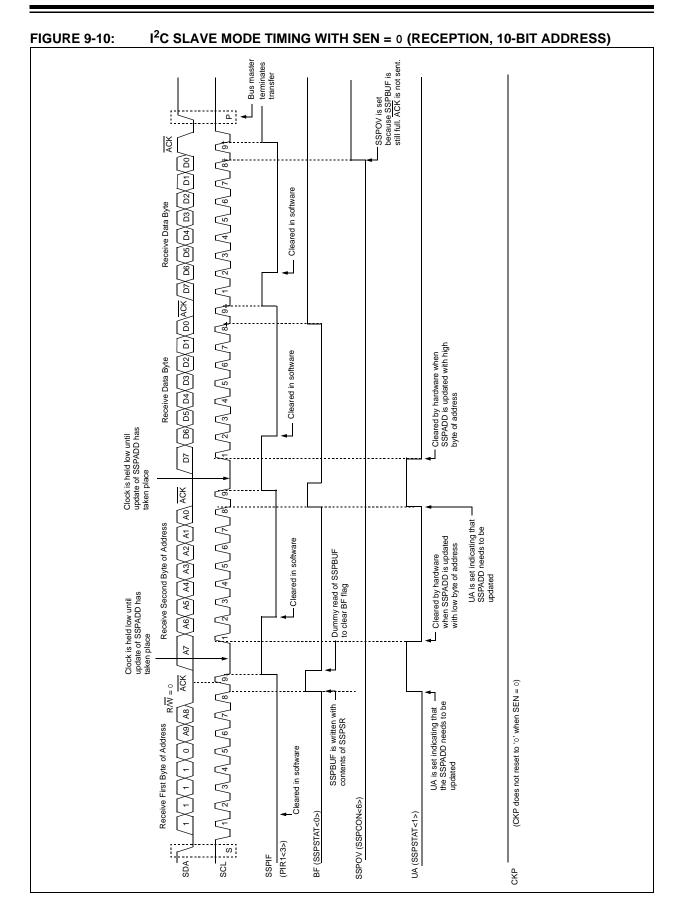

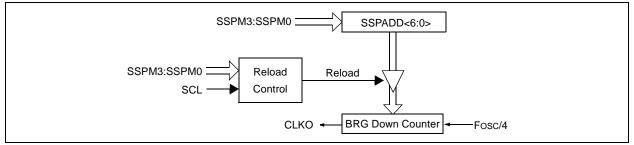

## 9.4.7 BAUD RATE GENERATOR

In I<sup>2</sup>C Master mode, the Baud Rate Generator (BRG) reload value is placed in the lower 7 bits of the SSPADD register (Figure 9-17). When a write occurs to SSPBUF, the Baud Rate Generator will automatically begin counting. The BRG counts down to 0 and stops until another reload has taken place. The BRG count is decremented twice per instruction cycle (Tcr) on the Q2 and Q4 clocks. In I<sup>2</sup>C Master mode, the BRG is reloaded automatically.

Once the given operation is complete (i.e., transmission of the last data bit is followed by ACK), the internal clock will automatically stop counting and the SCL pin will remain in its last state.

Table 9-3 demonstrates clock rates based on instruction cycles and the BRG value loaded into SSPADD.

## FIGURE 9-17: BAUD RATE GENERATOR BLOCK DIAGRAM

# TABLE 9-3: I<sup>2</sup>C CLOCK RATE W/BRG

| Fcy    | Fcy*2 BRG Value |     | FscL<br>(2 Rollovers of BRG) |

|--------|-----------------|-----|------------------------------|

| 10 MHz | 20 MHz          | 19h | 400 kHz <sup>(1)</sup>       |

| 10 MHz | 20 MHz          | 20h | 312.5 kHz                    |

| 10 MHz | 20 MHz          | 3Fh | 100 kHz                      |

| 4 MHz  | 8 MHz           | 0Ah | 400 kHz <sup>(1)</sup>       |

| 4 MHz  | 8 MHz           | 0Dh | 308 kHz                      |

| 4 MHz  | 8 MHz           | 28h | 100 kHz                      |

| 1 MHz  | 2 MHz           | 03h | 333 kHz <sup>(1)</sup>       |

| 1 MHz  | 2 MHz           | 0Ah | 100 kHz                      |

| 1 MHz  | 2 MHz           | 00h | 1 MHz <sup>(1)</sup>         |

**Note 1:** The I<sup>2</sup>C interface does not conform to the 400 kHz I<sup>2</sup>C specification (which applies to rates greater than 100 kHz) in all details, but may be used with care where higher rates are required by the application.

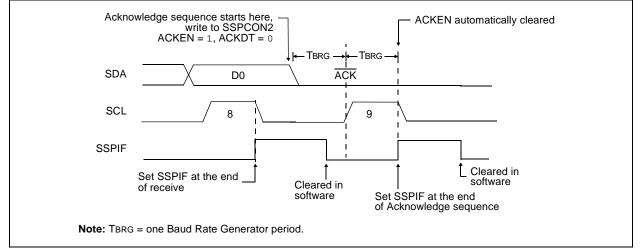

#### 9.4.12 ACKNOWLEDGE SEQUENCE TIMING

An Acknowledge sequence is enabled by setting the Acknowledge Sequence Enable bit. ACKEN (SSPCON2<4>). When this bit is set, the SCL pin is pulled low and the contents of the Acknowledge data bit are presented on the SDA pin. If the user wishes to generate an Acknowledge, then the ACKDT bit should be cleared. If not, the user should set the ACKDT bit before starting an Acknowledge sequence. The Baud Rate Generator then counts for one rollover period (TBRG) and the SCL pin is deasserted (pulled high). When the SCL pin is sampled high (clock arbitration), the Baud Rate Generator counts for TBRG. The SCL pin is then pulled low. Following this, the ACKEN bit is automatically cleared, the baud rate generator is turned off and the MSSP module then goes into Idle mode (Figure 9-23).

# 9.4.12.1 WCOL Status Flag

If the user writes the SSPBUF when an Acknowledge sequence is in progress, then WCOL is set and the contents of the buffer are unchanged (the write doesn't occur).

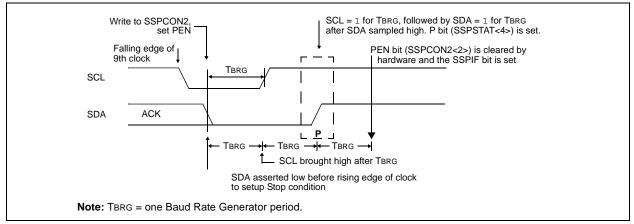

# 9.4.13 STOP CONDITION TIMING

A Stop bit is asserted on the SDA pin at the end of a receive/transmit by setting the Stop Sequence Enable bit, PEN (SSPCON2<2>). At the end of a receive/ transmit, the SCL line is held low after the falling edge of the ninth clock. When the PEN bit is set, the master will assert the SDA line low. When the SDA line is sampled low, the Baud Rate Generator is reloaded and counts down to 0. When the Baud Rate Generator times out, the SCL pin will be brought high and one TBRG (Baud Rate Generator rollover count) later, the SDA pin will be deasserted. When the SDA pin is sampled high while SCL is high, the P bit (SSPSTAT<4>) is set. A TBRG later, the PEN bit is cleared and the SSPIF bit is set (Figure 9-24).

# 9.4.13.1 WCOL Status Flag

If the user writes the SSPBUF when a Stop sequence is in progress, then the WCOL bit is set and the contents of the buffer are unchanged (the write doesn't occur).

# FIGURE 9-23: ACKNOWLEDGE SEQUENCE WAVEFORM

# FIGURE 9-24: STOP CONDITION RECEIVE OR TRANSMIT MODE

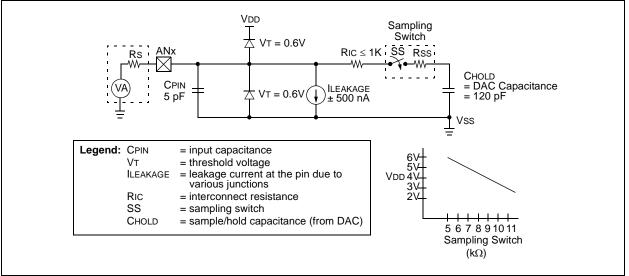

# 11.1 A/D Acquisition Requirements

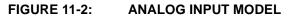

For the A/D converter to meet its specified accuracy, the charge holding capacitor (CHOLD) must be allowed to fully charge to the input channel voltage level. The analog input model is shown in Figure 11-2. The source impedance (Rs) and the internal sampling switch impedance (Rss) directly affect the time required to charge the capacitor CHOLD. The sampling switch (Rss) impedance varies over the device voltage (VDD); see Figure 11-2. The maximum recommended impedance for analog sources is 2.5 k $\Omega$ . As the impedance is decreased, the acquisition time may be

## EQUATION 11-1: ACQUISITION TIME

decreased. After the analog input channel is selected (changed), this acquisition must be done before the conversion can be started.

To calculate the minimum acquisition time, Equation 11-1 may be used. This equation assumes that 1/2 LSb error is used (1024 steps for the A/D). The 1/2 LSb error is the maximum error allowed for the A/D to meet its specified resolution.

To calculate the minimum acquisition time, TACQ, see the PIC<sup>®</sup> Mid-Range MCU Family Reference Manual (DS33023).

| TACQ | = Amplifier Settling Time + Hold Capacitor Charging Time + Temperature Coefficient                                                                                                                                                                                |

|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Тс   | = TAMP + TC + TCOFF<br>= $2 \mu s + TC + [(Temperature - 25^{\circ}C)(0.05 \mu s/^{\circ}C)]$<br>= CHOLD (RIC + RSs + RS) In(1/2047)<br>= $-120 \text{ pF} (1 \text{ k}\Omega + 7 \text{ k}\Omega + 10 \text{ k}\Omega) \text{ In}(0.0004885)$<br>= $16.47 \mu s$ |

| TACQ | = $2 \ \mu s + 16.47 \ \mu s + [(50^{\circ}C - 25^{\circ}C)(0.05 \ \mu s/^{\circ}C)]$<br>= $19.72 \ \mu s$                                                                                                                                                        |

Note 1: The reference voltage (VREF) has no effect on the equation since it cancels itself out.

- 2: The charge holding capacitor (CHOLD) is not discharged after each conversion.

- **3:** The maximum recommended impedance for analog sources is 2.5 k $\Omega$ . This is required to meet the pin leakage specification.

# 14.14 Power-down Mode (Sleep)

Power-down mode is entered by executing a  $\ensuremath{\mathtt{SLEEP}}$  instruction.

If enabled, the Watchdog Timer will be cleared but keeps running, the PD bit (Status<3>) is cleared, the TO (Status<4>) bit is set and the oscillator driver is turned off. The I/O ports maintain the status they had before the SLEEP instruction was executed (driving high, low or high-impedance).

For lowest current consumption in this mode, place all I/O pins at either VDD or VSS, ensure no external circuitry is drawing current from the I/O pin, powerdown the A/D and disable external clocks. Pull all I/O pins that are high-impedance inputs, high or low externally, to avoid switching currents caused by floating inputs. The TOCKI input should also be at VDD or VSS for lowest current consumption. The contribution from on-chip pull-ups on PORTB should also be considered.

The MCLR pin must be at a logic high level (VIHMC).

#### 14.14.1 WAKE-UP FROM SLEEP

The device can wake-up from Sleep through one of the following events:

- 1. External Reset input on  $\overline{\text{MCLR}}$  pin.

- 2. Watchdog Timer wake-up (if WDT was enabled).

- 3. Interrupt from INT pin, RB port change or peripheral interrupt.

External MCLR Reset will cause a device Reset. All other events are considered a continuation of program execution and cause a "wake-up". The TO and PD bits in the Status register can be used to determine the cause of device Reset. The PD bit, which is set on power-up, is cleared when Sleep is invoked. The TO bit is cleared if a WDT time-out occurred and caused wake-up.

The following peripheral interrupts can wake the device from Sleep:

- 1. PSP read or write (PIC16F874/877 only).

- 2. TMR1 interrupt. Timer1 must be operating as an asynchronous counter.

- 3. CCP Capture mode interrupt.

- 4. Special event trigger (Timer1 in Asynchronous mode using an external clock).

- 5. SSP (Start/Stop) bit detect interrupt.

- 6. SSP transmit or receive in Slave mode (SPI/I<sup>2</sup>C).

- 7. USART RX or TX (Synchronous Slave mode).

- 8. A/D conversion (when A/D clock source is RC).

- 9. EEPROM write operation completion.

- 10. Comparator output changes state.

Other peripherals cannot generate interrupts since during Sleep, no on-chip clocks are present.

When the SLEEP instruction is being executed, the next instruction (PC + 1) is prefetched. For the device to wake-up through an interrupt event, the corresponding interrupt enable bit must be set (enabled). Wake-up is regardless of the state of the GIE bit. If the GIE bit is clear (disabled), the device continues execution at the instruction after the SLEEP instruction. If the GIE bit is set (enabled), the device executes the instruction after the SLEEP instruction and then branches to the interrupt address (0004h). In cases where the execution of the instruction following SLEEP is not desirable, the user should have a NOP after the SLEEP instruction.

## 14.14.2 WAKE-UP USING INTERRUPTS

When global interrupts are disabled (GIE cleared) and any interrupt source has both its interrupt enable bit and interrupt flag bit set, one of the following will occur:

- If the interrupt occurs **before** the execution of a SLEEP instruction, the SLEEP instruction will complete as a NOP. Therefore, the WDT and WDT postscaler will not be cleared, the TO bit will not be set and PD bits will not be cleared.

- If the interrupt occurs during or after the execution of a SLEEP instruction, the device will immediately wake-up from Sleep. The SLEEP instruction will be completely executed before the wake-up. Therefore, the WDT and WDT postscaler will be cleared, the TO bit will be set and the PD bit will be cleared.

Even if the flag bits were checked before executing a SLEEP instruction, it may be possible for flag bits to become set before the SLEEP instruction completes. To determine whether a SLEEP instruction executed, test the PD bit. If the PD bit is set, the SLEEP instruction was executed as a NOP.

To ensure that the WDT is cleared, a CLRWDT instruction should be executed before a SLEEP instruction.

# 15.0 INSTRUCTION SET SUMMARY

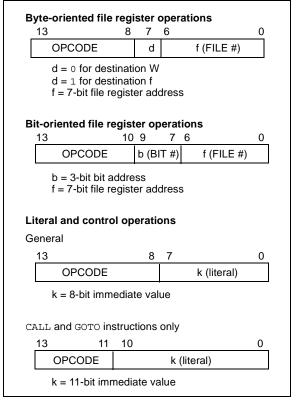

The PIC16 instruction set is highly orthogonal and is comprised of three basic categories:

- Byte-oriented operations

- Bit-oriented operations

- Literal and control operations

Each PIC16 instruction is a 14-bit word divided into an **opcode** which specifies the instruction type and one or more **operands** which further specify the operation of the instruction. The formats for each of the categories is presented in Figure 15-1, while the various opcode fields are summarized in Table 15-1.

Table 15-2 lists the instructions recognized by the MPASM<sup>™</sup> Assembler. A complete description of each instruction is also available in the PIC<sup>®</sup> Mid-Range MCU Family Reference Manual (DS33023).

For **byte-oriented** instructions, 'f' represents a file register designator and 'd' represents a destination designator. The file register designator specifies which file register is to be used by the instruction.

The destination designator specifies where the result of the operation is to be placed. If 'd' is zero, the result is placed in the W register. If 'd' is one, the result is placed in the file register specified in the instruction.

For **bit-oriented** instructions, 'b' represents a bit field designator which selects the bit affected by the operation, while 'f' represents the address of the file in which the bit is located.

For **literal and control** operations, 'k' represents an eight or eleven-bit constant or literal value

One instruction cycle consists of four oscillator periods; for an oscillator frequency of 4 MHz, this gives a normal instruction execution time of 1  $\mu$ s. All instructions are executed within a single instruction cycle, unless a conditional test is true, or the program counter is changed as a result of an instruction. When this occurs, the execution takes two instruction cycles with the second cycle executed as a NOP.

| Note: | To maintain upward compatibility with  |  |  |  |  |  |  |  |

|-------|----------------------------------------|--|--|--|--|--|--|--|

|       | future PIC16F87XA products, do not use |  |  |  |  |  |  |  |

|       | the OPTION and TRIS instructions.      |  |  |  |  |  |  |  |

All instruction examples use the format '0xhh' to represent a hexadecimal number, where 'h' signifies a hexadecimal digit.

# 15.1 READ-MODIFY-WRITE OPERATIONS

Any instruction that specifies a file register as part of the instruction performs a Read-Modify-Write (R-M-W) operation. The register is read, the data is modified, and the result is stored according to either the instruction or the destination designator 'd'. A read operation is performed on a register even if the instruction writes to that register. For example, a "CLRF PORTB" instruction will read PORTB, clear all the data bits, then write the result back to PORTB. This example would have the unintended result that the condition that sets the RBIF flag would be cleared.

# TABLE 15-1: OPCODE FIELD DESCRIPTIONS

| Field | Description                                                                                                                                                                       |

|-------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| f     | Register file address (0x00 to 0x7F)                                                                                                                                              |

| W     | Working register (accumulator)                                                                                                                                                    |

| b     | Bit address within an 8-bit file register                                                                                                                                         |

| k     | Literal field, constant data or label                                                                                                                                             |

| х     | Don't care location (= $0$ or 1).<br>The assembler will generate code with x = $0$ .<br>It is the recommended form of use for<br>compatibility with all Microchip software tools. |

| d     | Destination select; $d = 0$ : store result in W,<br>d = 1: store result in file register f.<br>Default is $d = 1$ .                                                               |

| PC    | Program Counter                                                                                                                                                                   |

| ТО    | Time-out bit                                                                                                                                                                      |

| PD    | Power-down bit                                                                                                                                                                    |

# FIGURE 15-1: GENERAL FORMAT FOR INSTRUCTIONS

# TABLE 17-1: COMPARATOR SPECIFICATIONS

| Operating Conditions:3.0V < VDD < 5.5V, -40°C < TA < +85°C (unless otherwise stated)4.0V < VDD < 5.5V, -40°C < TA < +125°C (unless otherwise stated) |        |                                            |     |       |            |          |                           |  |

|------------------------------------------------------------------------------------------------------------------------------------------------------|--------|--------------------------------------------|-----|-------|------------|----------|---------------------------|--|

| Param<br>No.                                                                                                                                         | Sym    | Characteristics                            | Min | Тур   | Max        | Units    | Comments                  |  |

| D300                                                                                                                                                 | VIOFF  | Input Offset Voltage                       | _   | ± 5.0 | ± 10       | mV       |                           |  |

| D301                                                                                                                                                 | VICM   | Input Common Mode Voltage*                 | 0   | -     | Vdd - 1.5  | V        |                           |  |

| D302                                                                                                                                                 | CMRR   | Common Mode Rejection Ratio*               | 55  | -     | _          | dB       |                           |  |

| 300<br>300A                                                                                                                                          | TRESP  | Response Time <sup>*(1)</sup>              | —   | 150   | 400<br>600 | ns<br>ns | PIC16F87XA<br>PIC16LF87XA |  |

| 301                                                                                                                                                  | TMC2OV | Comparator Mode Change to<br>Output Valid* | _   | —     | 10         | μS       |                           |  |

These parameters are characterized but not tested.

Note 1: Response time measured with one comparator input at (VDD - 1.5)/2 while the other input transitions from Vss to VDD.

# TABLE 17-2: VOLTAGE REFERENCE SPECIFICATIONS

| Operating   | Operating Conditions:3.0V < VDD < 5.5V, -40°C < TA < +85°C (unless otherwise stated)4.0V < VDD < 5.5V, -40°C < TA < +125°C (unless otherwise stated) |                               |        |     |            |            |                                             |  |  |

|-------------|------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------|--------|-----|------------|------------|---------------------------------------------|--|--|

| Spec<br>No. | Sym                                                                                                                                                  | Characteristics               | Min    | Тур | Мах        | Units      | Comments                                    |  |  |

| D310        | VRES                                                                                                                                                 | Resolution                    | Vdd/24 | —   | Vdd/32     | LSb        |                                             |  |  |

| D311        | VRAA                                                                                                                                                 | Absolute Accuracy             | _      | _   | 1/2<br>1/2 | LSb<br>LSb | Low Range (VRR = 1)<br>High Range (VRR = 0) |  |  |

| D312        | VRur                                                                                                                                                 | Unit Resistor Value (R)*      | —      | 2k  | —          | Ω          |                                             |  |  |

| 310         | TSET                                                                                                                                                 | Settling Time* <sup>(1)</sup> | —      | —   | 10         | μS         |                                             |  |  |

\* These parameters are characterized but not tested.

Note 1: Settling time measured while VRR = 1 and VR<3:0> transitions from '0000' to '1111'.

# TABLE 17-8: PARALLEL SLAVE PORT REQUIREMENTS (PIC16F874A/877A ONLY)

| Param<br>No. | Symbol   | Characteristic                                                                          |              |    | Тур† | Max | Units | Conditions |

|--------------|----------|-----------------------------------------------------------------------------------------|--------------|----|------|-----|-------|------------|

| 62           | TdtV2wrH | Data In Valid before $\overline{WR} \uparrow$ or $\overline{CS} \uparrow$ (setup time)  |              |    | _    |     | ns    |            |

| 63*          | TwrH2dtI | $\overline{WR}$ $\uparrow$ or $\overline{CS}$ $\uparrow$ to Data–in Invalid (hold time) | Standard(F)  | 20 | _    | _   | ns    |            |

|              |          |                                                                                         | Extended(LF) | 35 | _    | _   | ns    |            |

| 64           | TrdL2dtV | $\overline{RD} \downarrow$ and $\overline{CS} \downarrow$ to Data–out Valid             |              |    | _    | 80  | ns    |            |

| 65           | TrdH2dtI | $\overline{RD}$ $\uparrow$ or $\overline{CS}$ $\downarrow$ to Data–out Invalid          |              |    | —    | 30  | ns    |            |

These parameters are characterized but not tested.

† Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

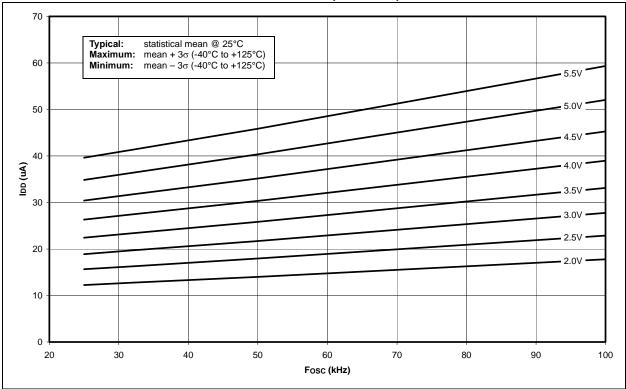

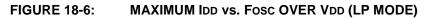

FIGURE 18-5: TYPICAL IDD vs. Fosc OVER VDD (LP MODE)

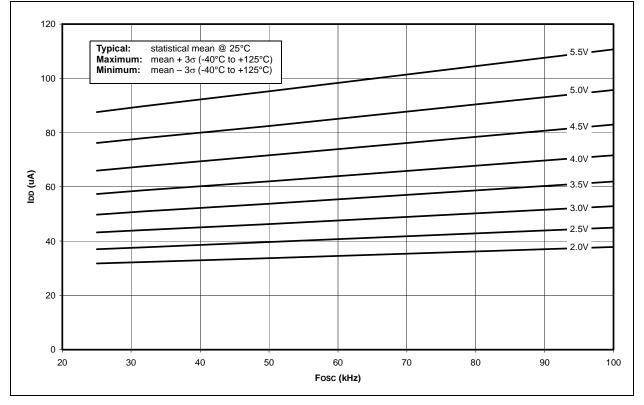

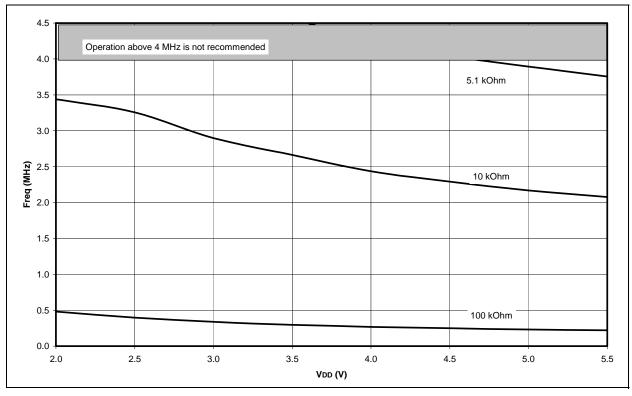

## FIGURE 18-8: AVERAGE Fosc vs. VDD FOR VARIOUS VALUES OF R (RC MODE, C = 100 pF, +25°C)

# PIC16F87XA

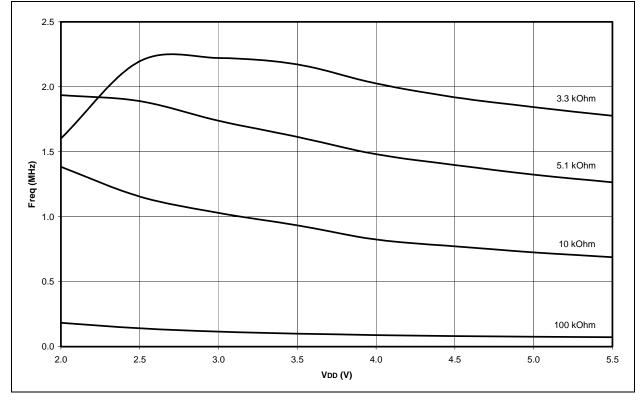

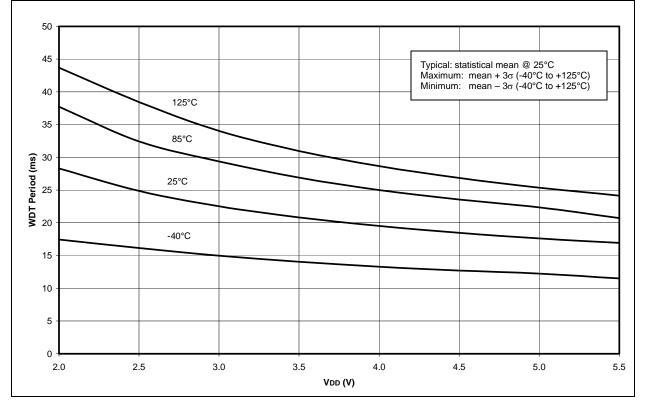

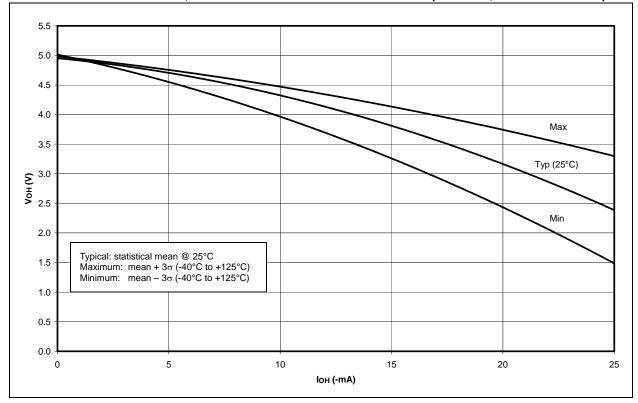

FIGURE 18-16: TYPICAL, MINIMUM AND MAXIMUM VOH vs. IOH (VDD = 5V, -40°C TO +125°C)

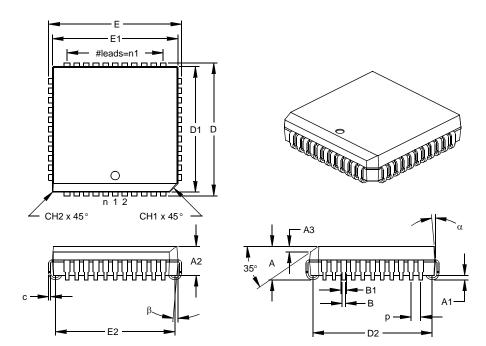

# 44-Lead Plastic Leaded Chip Carrier (L) – Square (PLCC)

Note: For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

|                           | INCHES* |      |      | MILLIMETERS |       |       |       |

|---------------------------|---------|------|------|-------------|-------|-------|-------|

| Dimensio                  | MIN     | NOM  | MAX  | MIN         | NOM   | MAX   |       |

| Number of Pins            | n       |      | 44   |             |       | 44    |       |

| Pitch                     | р       |      | .050 |             |       | 1.27  |       |

| Pins per Side             | n1      |      | 11   |             |       | 11    |       |

| Overall Height            | А       | .165 | .173 | .180        | 4.19  | 4.39  | 4.57  |

| Molded Package Thickness  | A2      | .145 | .153 | .160        | 3.68  | 3.87  | 4.06  |

| Standoff §                | A1      | .020 | .028 | .035        | 0.51  | 0.71  | 0.89  |

| Side 1 Chamfer Height     | A3      | .024 | .029 | .034        | 0.61  | 0.74  | 0.86  |

| Corner Chamfer 1          | CH1     | .040 | .045 | .050        | 1.02  | 1.14  | 1.27  |

| Corner Chamfer (others)   | CH2     | .000 | .005 | .010        | 0.00  | 0.13  | 0.25  |

| Overall Width             | Е       | .685 | .690 | .695        | 17.40 | 17.53 | 17.65 |

| Overall Length            | D       | .685 | .690 | .695        | 17.40 | 17.53 | 17.65 |

| Molded Package Width      | E1      | .650 | .653 | .656        | 16.51 | 16.59 | 16.66 |

| Molded Package Length     | D1      | .650 | .653 | .656        | 16.51 | 16.59 | 16.66 |

| Footprint Width           | E2      | .590 | .620 | .630        | 14.99 | 15.75 | 16.00 |

| Footprint Length          | D2      | .590 | .620 | .630        | 14.99 | 15.75 | 16.00 |

| Lead Thickness            | С       | .008 | .011 | .013        | 0.20  | 0.27  | 0.33  |

| Upper Lead Width          | B1      | .026 | .029 | .032        | 0.66  | 0.74  | 0.81  |

| Lower Lead Width          |         | .013 | .020 | .021        | 0.33  | 0.51  | 0.53  |

| Mold Draft Angle Top      |         | 0    | 5    | 10          | 0     | 5     | 10    |

| Mold Draft Angle Bottom β |         | 0    | 5    | 10          | 0     | 5     | 10    |

\* Controlling Parameter § Significant Characteristic

Notes:

Dimensions D and E1 do not include mold flash or protrusions. Mold flash or protrusions shall not exceed .010" (0.254mm) per side.

JEDEC Equivalent: MO-047

Drawing No. C04-048

NOTES: