Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                           |

|----------------------------|---------------------------------------------------------------------------|

| Product Status             | Active                                                                    |

| Core Processor             | PIC                                                                       |

| Core Size                  | 8-Bit                                                                     |

| Speed                      | 20MHz                                                                     |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                         |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                     |

| Number of I/O              | 22                                                                        |

| Program Memory Size        | 14KB (8K x 14)                                                            |

| Program Memory Type        | FLASH                                                                     |

| EEPROM Size                | 256 x 8                                                                   |

| RAM Size                   | 368 x 8                                                                   |

| Voltage - Supply (Vcc/Vdd) | 4V ~ 5.5V                                                                 |

| Data Converters            | A/D 5x10b                                                                 |

| Oscillator Type            | External                                                                  |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                         |

| Mounting Type              | Surface Mount                                                             |

| Package / Case             | 28-SOIC (0.295", 7.50mm Width)                                            |

| Supplier Device Package    | 28-SOIC                                                                   |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16f876a-i-so |

|                            |                                                                           |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

### 3.0 DATA EEPROM AND FLASH PROGRAM MEMORY

The data EEPROM and Flash program memory is readable and writable during normal operation (over the full VDD range). This memory is not directly mapped in the register file space. Instead, it is indirectly addressed through the Special Function Registers. There are six SFRs used to read and write this memory:

- EECON1

- EECON2

- EEDATA

- EEDATH

- EEADR

- EEADRH

When interfacing to the data memory block, EEDATA holds the 8-bit data for read/write and EEADR holds the address of the EEPROM location being accessed. These devices have 128 or 256 bytes of data EEPROM (depending on the device), with an address range from 00h to FFh. On devices with 128 bytes, addresses from 80h to FFh are unimplemented and will wraparound to the beginning of data EEPROM memory. When writing to unimplemented locations, the on-chip charge pump will be turned off.

When interfacing the program memory block, the EEDATA and EEDATH registers form a two-byte word that holds the 14-bit data for read/write and the EEADR and EEADRH registers form a two-byte word that holds the 13-bit address of the program memory location being accessed. These devices have 4 or 8K words of program Flash, with an address range from 0000h to 0FFFh for the PIC16F873A/874A and 0000h to 1FFFh for the PIC16F876A/877A. Addresses above the range of the respective device will wraparound to the beginning of program memory.

The EEPROM data memory allows single-byte read and write. The Flash program memory allows single-word reads and four-word block writes. Program memory write operations automatically perform an erase-before-write on blocks of four words. A byte write in data EEPROM memory automatically erases the location and writes the new data (erase-before-write).

The write time is controlled by an on-chip timer. The write/erase voltages are generated by an on-chip charge pump, rated to operate over the voltage range of the device for byte or word operations.

When the device is code-protected, the CPU may continue to read and write the data EEPROM memory. Depending on the settings of the write-protect bits, the device may or may not be able to write certain blocks of the program memory; however, reads of the program memory are allowed. When code-protected, the device programmer can no longer access data or program memory; this does NOT inhibit internal reads or writes.

### 3.1 EEADR and EEADRH

The EEADRH:EEADR register pair can address up to a maximum of 256 bytes of data EEPROM or up to a maximum of 8K words of program EEPROM. When selecting a data address value, only the LSByte of the address is written to the EEADR register. When selecting a program address value, the MSByte of the address is written to the EEADRH register and the LSByte is written to the EEADR register.

If the device contains less memory than the full address reach of the address register pair, the Most Significant bits of the registers are not implemented. For example, if the device has 128 bytes of data EEPROM, the Most Significant bit of EEADR is not implemented on access to data EEPROM.

### 3.2 EECON1 and EECON2 Registers

EECON1 is the control register for memory accesses.

Control bit, EEPGD, determines if the access will be a program or data memory access. When clear, as it is when reset, any subsequent operations will operate on the data memory. When set, any subsequent operations will operate on the program memory.

Control bits, RD and WR, initiate read and write or erase, respectively. These bits cannot be cleared, only set, in software. They are cleared in hardware at completion of the read or write operation. The inability to clear the WR bit in software prevents the accidental, premature termination of a write operation.

The WREN bit, when set, will allow a write or erase operation. On power-up, the WREN bit is clear. The WRERR bit is set when a write (or erase) operation is interrupted by a  $\overline{\text{MCLR}}$  or a WDT Time-out Reset during normal operation. In these situations, following Reset, the user can check the WRERR bit and rewrite the location. The data and address will be unchanged in the EEDATA and EEADR registers.

Interrupt flag bit, EEIF in the PIR2 register, is set when the write is complete. It must be cleared in software.

EECON2 is not a physical register. Reading EECON2 will read all '0's. The EECON2 register is used exclusively in the EEPROM write sequence.

Note: The self-programming mechanism for Flash program memory has been changed. On previous PIC16F87X devices, Flash programming was done in single-word erase/ write cycles. The newer PIC18F87XA devices use a four-word erase/write cycle. See Section 3.6 "Writing to Flash Program Memory" for more information.

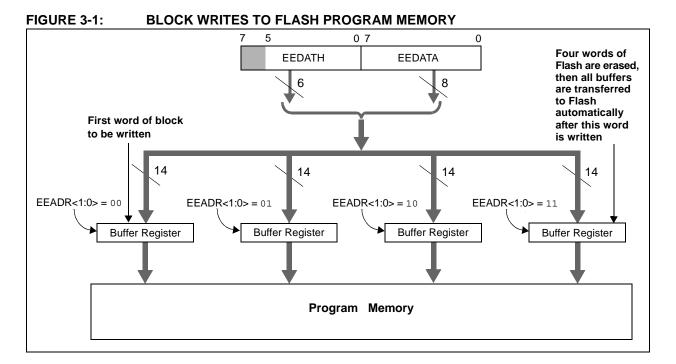

### 3.6 Writing to Flash Program Memory

Flash program memory may only be written to if the destination address is in a segment of memory that is not write-protected, as defined in bits WRT1:WRT0 of the device configuration word (Register 14-1). Flash program memory must be written in four-word blocks. A block consists of four words with sequential addresses, with a lower boundary defined by an address, where EEADR<1:0> = 00. At the same time, all block writes to program memory are done as erase and write operations. The write operation is edge-aligned and cannot occur across boundaries.

To write program data, it must first be loaded into the buffer registers (see Figure 3-1). This is accomplished by first writing the destination address to EEADR and EEADRH and then writing the data to EEDATA and EEDATH. After the address and data have been set up, then the following sequence of events must be executed:

- 1. Set the EEPGD control bit (EECON1<7>).

- 2. Write 55h, then AAh, to EECON2 (Flash programming sequence).

- 3. Set the WR control bit (EECON1<1>).

All four buffer register locations **MUST** be written to with correct data. If only one, two or three words are being written to in the block of four words, then a read from the program memory location(s) not being written to must be performed. This takes the data from the program location(s) not being written and loads it into the EEDATA and EEDATH registers. Then the sequence of events to transfer data to the buffer registers must be executed. To transfer data from the buffer registers to the program memory, the EEADR and EEADRH must point to the last location in the four-word block (EEADR<1:0> = 11). Then the following sequence of events must be executed:

- 1. Set the EEPGD control bit (EECON1<7>).

- 2. Write 55h, then AAh, to EECON2 (Flash programming sequence).

- Set control bit WR (EECON1<1>) to begin the write operation.

The user must follow the same specific sequence to initiate the write for each word in the program block, writing each program word in sequence (00, 01, 10, 11). When the write is performed on the last word (EEADR<1:0> = 11), the block of four words are automatically erased and the contents of the buffer registers are written into the program memory.

After the "BSF EECON1, WR" instruction, the processor requires two cycles to set up the erase/write operation. The user must place two NOP instructions after the WR bit is set. Since data is being written to buffer registers, the writing of the first three words of the block appears to occur immediately. The processor will halt internal operations for the typical 4 ms, only during the cycle in which the erase takes place (i.e., the last word of the four-word block). This is not Sleep mode as the clocks and peripherals will continue to run. After the write cycle, the processor will resume operation with the third instruction after the EECON1 write instruction. If the sequence is performed to any other location, the action is ignored.

NOTES:

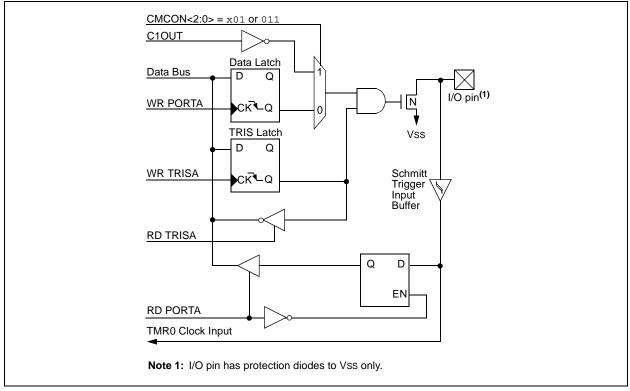

### FIGURE 4-2: BLOCK DIAGRAM OF RA4/T0CKI PIN

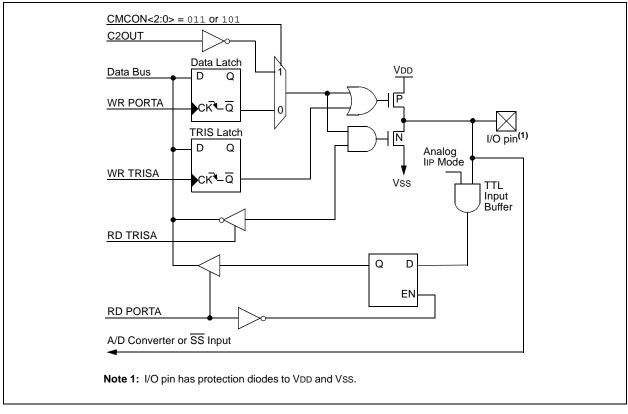

### FIGURE 4-3: BLOCK DIAGRAM OF RA5 PIN

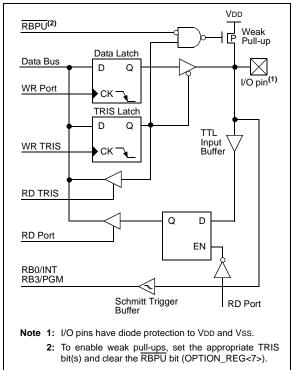

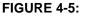

### 4.2 **PORTB and the TRISB Register**

PORTB is an 8-bit wide, bidirectional port. The corresponding data direction register is TRISB. Setting a TRISB bit (= 1) will make the corresponding PORTB pin an input (i.e., put the corresponding output driver in a High-Impedance mode). Clearing a TRISB bit (= 0) will make the corresponding PORTB pin an output (i.e., put the contents of the output latch on the selected pin).

Three pins of PORTB are multiplexed with the In-Circuit Debugger and Low-Voltage Programming function: RB3/PGM, RB6/PGC and RB7/PGD. The alternate functions of these pins are described in **Section 14.0 "Special Features of the CPU"**.

Each of the PORTB pins has a weak internal pull-up. A single control bit can turn on all the pull-ups. This is performed by clearing bit RBPU (OPTION\_REG<7>). The weak pull-up is automatically turned off when the port pin is configured as an output. The pull-ups are disabled on a Power-on Reset.

Four of the PORTB pins, RB7:RB4, have an interrupton-change feature. Only pins configured as inputs can cause this interrupt to occur (i.e., any RB7:RB4 pin configured as an output is excluded from the interrupton-change comparison). The input pins (of RB7:RB4) are compared with the old value latched on the last read of PORTB. The "mismatch" outputs of RB7:RB4 are OR'ed together to generate the RB port change interrupt with flag bit RBIF (INTCON<0>). This interrupt can wake the device from Sleep. The user, in the Interrupt Service Routine, can clear the interrupt in the following manner:

- a) Any read or write of PORTB. This will end the mismatch condition.

- b) Clear flag bit RBIF.

A mismatch condition will continue to set flag bit RBIF. Reading PORTB will end the mismatch condition and allow flag bit RBIF to be cleared.

The interrupt-on-change feature is recommended for wake-up on key depression operation and operations where PORTB is only used for the interrupt-on-change feature. Polling of PORTB is not recommended while using the interrupt-on-change feature.

This interrupt-on-mismatch feature, together with software configurable pull-ups on these four pins, allow easy interface to a keypad and make it possible for wake-up on key depression. Refer to the application note, *AN552, "Implementing Wake-up on Key Stroke*" (DS00552).

RB0/INT is an external interrupt input pin and is configured using the INTEDG bit (OPTION\_REG<6>).

RB0/INT is discussed in detail in **Section 14.11.1 "INT Interrupt**".

### BLOCK DIAGRAM OF RB7:RB4 PINS

| REGISTER 8-1: | CCP1CON                                                                                                                                | I REGISTE                                                                                                                          | ER/CCP2C                                                                                                                          | ON REGIS                                                                                           | STER (ADDF                                                                                              | RESS 17h                                     | /1Dh)         |            |

|---------------|----------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------|----------------------------------------------|---------------|------------|

|               | U-0                                                                                                                                    | U-0                                                                                                                                | R/W-0                                                                                                                             | R/W-0                                                                                              | R/W-0                                                                                                   | R/W-0                                        | R/W-0         | R/W-0      |

|               | —                                                                                                                                      | _                                                                                                                                  | CCPxX                                                                                                                             | CCPxY                                                                                              | CCPxM3                                                                                                  | CCPxM2                                       | CCPxM1        | CCPxM0     |

|               | bit 7                                                                                                                                  |                                                                                                                                    |                                                                                                                                   |                                                                                                    |                                                                                                         |                                              |               | bit 0      |

| bit 7-6       | Unimplem                                                                                                                               | ented: Rea                                                                                                                         | <b>d as</b> '0'                                                                                                                   |                                                                                                    |                                                                                                         |                                              |               |            |

| bit 5-4       | CCPxX:CC                                                                                                                               | PxY: PWM                                                                                                                           | Least Sign                                                                                                                        | ificant bits                                                                                       |                                                                                                         |                                              |               |            |

|               | <u>Capture mo</u><br>Unused.                                                                                                           | ode:                                                                                                                               |                                                                                                                                   |                                                                                                    |                                                                                                         |                                              |               |            |

|               | <u>Compare n</u><br>Unused.                                                                                                            | <u>node:</u>                                                                                                                       |                                                                                                                                   |                                                                                                    |                                                                                                         |                                              |               |            |

|               | <u>PWM mode</u><br>These bits                                                                                                          |                                                                                                                                    | LSbs of the                                                                                                                       | e PWM duty                                                                                         | cycle. The eig                                                                                          | jht MSbs ar                                  | e found in C  | CPRxL.     |

| bit 3-0       | CCPxM3:C                                                                                                                               | CPxM0: C                                                                                                                           | CPx Mode S                                                                                                                        | Select bits                                                                                        |                                                                                                         |                                              |               |            |

|               | 0100 = Ca<br>0101 = Ca<br>0110 = Ca<br>0111 = Ca<br>1000 = Co<br>1001 = Co<br>1010 = Co<br>una<br>1011 = Co<br>res<br>ena<br>11xx = PW | pture mode<br>pture mode<br>pture mode<br>mpare mode<br>mpare mode<br>mpare mode<br>affected)<br>mpare mode<br>ets TMR1;<br>abled) | , every fallir<br>, every risin<br>, every 4th r<br>, every 16th<br>e, set outpu<br>e, clear outp<br>e, generate<br>e, trigger sp | ng edge<br>g edge<br>rising edge<br>t on match (<br>out on match<br>software int<br>ecial event (f | ets CCPx mod<br>CCPxIF bit is<br>a (CCPxIF bit i<br>errupt on mat<br>CCPxIF bit is s<br>and starts an A | set)<br>is set)<br>ch (CCPxIF<br>set, CCPx p | in is unaffec | ted); CCP1 |

|               | Legend:                                                                                                                                |                                                                                                                                    |                                                                                                                                   |                                                                                                    |                                                                                                         |                                              |               |            |

|               | R = Reada                                                                                                                              | ble bit                                                                                                                            |                                                                                                                                   | Vritable bit                                                                                       | •                                                                                                       |                                              | oit, read as  | ʻ0'        |

|               | - n = Value                                                                                                                            | at POR                                                                                                                             | '1' = E                                                                                                                           | Bit is set                                                                                         | '0' = Bit is                                                                                            | cleared                                      | x = Bit is u  | nknown     |

| ER 9-2: | SSPCON                                           | 1: MSSP C                                                                       | ONTROL F                                                      | REGISTER                                       | 1 (SPI MC                   | DE) (ADD      | RESS 14h      | )             |

|---------|--------------------------------------------------|---------------------------------------------------------------------------------|---------------------------------------------------------------|------------------------------------------------|-----------------------------|---------------|---------------|---------------|

|         | R/W-0                                            | R/W-0                                                                           | R/W-0                                                         | R/W-0                                          | R/W-0                       | R/W-0         | R/W-0         | R/W-0         |

|         | WCOL                                             | SSPOV                                                                           | SSPEN                                                         | CKP                                            | SSPM3                       | SSPM2         | SSPM1         | SSPM0         |

|         | bit 7                                            |                                                                                 |                                                               |                                                |                             |               |               | bit 0         |

| bit 7   |                                                  | /rite Collision                                                                 | -                                                             |                                                |                             |               |               |               |

|         |                                                  | SSPBUF reg<br>ed in software<br>ollision                                        |                                                               | en while it i                                  | s still transm              | nitting the p | revious wor   | d. (Must be   |

| bit 6   | SSPOV: R                                         | Receive Over                                                                    | flow Indicato                                                 | or bit                                         |                             |               |               |               |

|         | <u>SPI Slave</u>                                 | mode:                                                                           |                                                               |                                                |                             |               |               |               |

|         | of ove<br>must<br>cleare                         | v byte is rece<br>erflow, the da<br>read the SSI<br>ed in software              | ata in SSPSF<br>PBUF, even                                    | R is lost. Ov                                  | verflow can o               | only occur in | Slave mod     | e. The user   |

|         | 0 = No ov                                        |                                                                                 |                                                               |                                                |                             |               |               |               |

|         | Note:                                            |                                                                                 |                                                               |                                                | t is not set<br>to the SSPE |               |               | eption (and   |

| bit 5   | SSPEN: S                                         | Synchronous                                                                     | Serial Port E                                                 | Enable bit                                     |                             |               |               |               |

|         |                                                  | es serial port<br>les serial por                                                |                                                               |                                                |                             |               | ial port pins |               |

|         | Note:                                            | When enal                                                                       | oled, these p                                                 | oins must be                                   | e properly co               | nfigured as   | input or out  | put.          |

| bit 4   | CKP: Cloo                                        | ck Polarity Se                                                                  | elect bit                                                     |                                                |                             |               |               |               |

|         |                                                  | ate for clock<br>ate for clock                                                  | •                                                             |                                                |                             |               |               |               |

| bit 3-0 | SSPM3:S                                          | SPM0: Sync                                                                      | hronous Ser                                                   | ial Port Mod                                   | de Select bits              | 5             |               |               |

|         | 0100 = SF<br>0011 = SF<br>0010 = SF<br>0001 = SF | PI Slave mod<br>PI Slave mod<br>PI Master mod<br>PI Master mod<br>PI Master mod | le, clock = S<br>ode, clock =<br>ode, clock =<br>ode, clock = | CK pin. SS<br>TMR2 outpu<br>Fosc/64<br>Fosc/16 | pin control e               |               | can be usec   | l as I/O pin. |

|         |                                                  | PI Master mo                                                                    |                                                               |                                                |                             |               |               |               |

|         | Note:                                            | Bit combin<br>I <sup>2</sup> C mode o                                           |                                                               | becifically lis                                | sted here are               | either rese   | rved or imp   | lemented in   |

|         |                                                  |                                                                                 |                                                               |                                                |                             |               |               |               |

|         | I a manual.                                      |                                                                                 |                                                               |                                                |                             |               |               |               |

| Legend:            |                  |                      |                    |

|--------------------|------------------|----------------------|--------------------|

| R = Readable bit   | W = Writable bit | U = Unimplemented    | bit, read as '0'   |

| - n = Value at POR | '1' = Bit is set | '0' = Bit is cleared | x = Bit is unknown |

## REGISTER 9-2: SSPCON1: MSSP CONTROL REGISTER 1 (SPI MODE) (ADDRESS 14h)

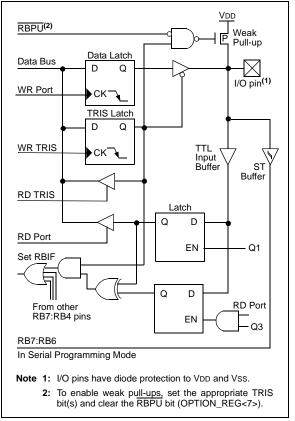

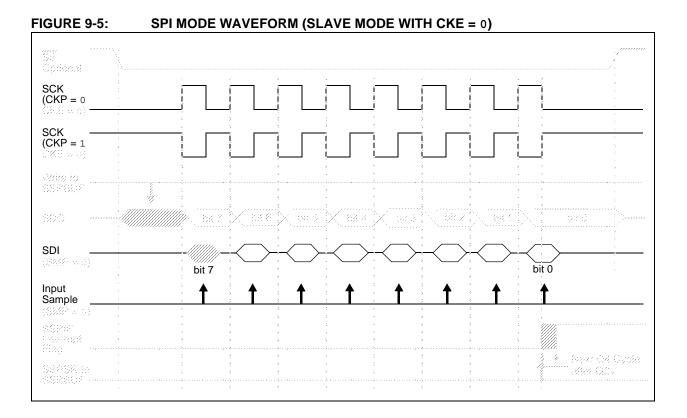

### FIGURE 9-6: SPI MODE WAVEFORM (SLAVE MODE WITH CKE = 1)

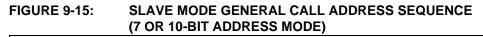

#### 9.4.5 GENERAL CALL ADDRESS SUPPORT

The addressing procedure for the  $I^2C$  bus is such that the first byte after the Start condition usually determines which device will be the slave addressed by the master. The exception is the general call address which can address all devices. When this address is used, all devices should, in theory, respond with an Acknowledge.

The general call address is one of eight addresses reserved for specific purposes by the  $I^2C$  protocol. It consists of all '0's with R/W = 0.

The general call address is recognized when the General Call Enable bit (GCEN) is enabled (SSPCON2<7> set). Following a Start bit detect, 8 bits are shifted into the SSPSR and the address is compared against the SSPADD. It is also compared to the general call address and fixed in hardware.

If the general call address matches, the SSPSR is transferred to the SSPBUF, the BF flag bit is set (eighth bit) and on the falling edge of the ninth bit (ACK bit), the SSPIF interrupt flag bit is set.

When the interrupt is serviced, the source for the interrupt can be checked by reading the contents of the SSPBUF. The value can be used to determine if the address was device specific or a general call address.

In 10-bit mode, the SSPADD is required to be updated for the second half of the address to match and the UA bit is set (SSPSTAT<1>). If the general call address is sampled when the GCEN bit is set, while the slave is configured in 10-bit Address mode, then the second half of the address is not necessary, the UA bit will not be set and the slave will begin receiving data after the Acknowledge (Figure 9-15).

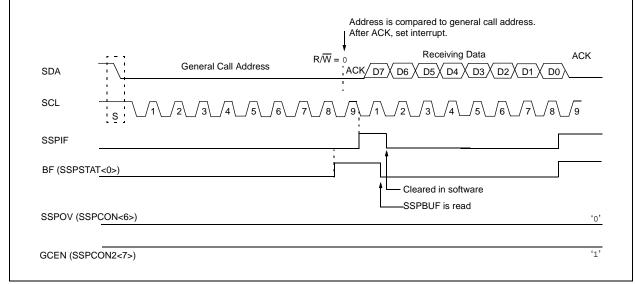

### 9.4.7.1 Clock Arbitration

Clock arbitration occurs when the master, during any receive, transmit or Repeated Start/Stop condition, deasserts the SCL pin (SCL allowed to float high). When the SCL pin is allowed to float high, the Baud Rate Generator (BRG) is suspended from counting until the SCL pin is actually sampled high. When the

SCL pin is sampled high, the Baud Rate Generator is reloaded with the contents of SSPADD<6:0> and begins counting. This ensures that the SCL high time will always be at least one BRG rollover count, in the event that the clock is held low by an external device (Figure 9-17).

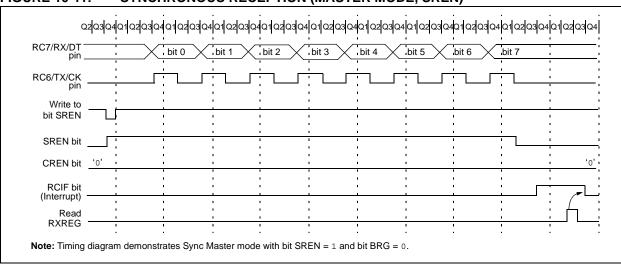

### FIGURE 10-11: SYNCHRONOUS RECEPTION (MASTER MODE, SREN)

### 10.4 USART Synchronous Slave Mode

Synchronous Slave mode differs from the Master mode in the fact that the shift clock is supplied externally at the RC6/TX/CK pin (instead of being supplied internally in Master mode). This allows the device to transfer or receive data while in Sleep mode. Slave mode is entered by clearing bit, CSRC (TXSTA<7>).

### 10.4.1 USART SYNCHRONOUS SLAVE TRANSMIT

The operation of the Synchronous Master and Slave modes is identical, except in the case of the Sleep mode.

If two words are written to the TXREG and then the SLEEP instruction is executed, the following will occur:

- a) The first word will immediately transfer to the TSR register and transmit.

- b) The second word will remain in TXREG register.

- c) Flag bit TXIF will not be set.

- d) When the first word has been shifted out of TSR, the TXREG register will transfer the second word to the TSR and flag bit TXIF will now be set.

- e) If enable bit TXIE is set, the interrupt will wake the chip from Sleep and if the global interrupt is enabled, the program will branch to the interrupt vector (0004h).

When setting up a Synchronous Slave Transmission, follow these steps:

- 1. Enable the synchronous slave serial port by setting bits SYNC and SPEN and clearing bit CSRC.

- 2. Clear bits CREN and SREN.

- 3. If interrupts are desired, then set enable bit TXIE.

- 4. If 9-bit transmission is desired, then set bit TX9.

- 5. Enable the transmission by setting enable bit TXEN.

- 6. If 9-bit transmission is selected, the ninth bit should be loaded in bit TX9D.

- 7. Start transmission by loading data to the TXREG register.

- 8. If using interrupts, ensure that GIE and PEIE (bits 7 and 6) of the INTCON register are set.

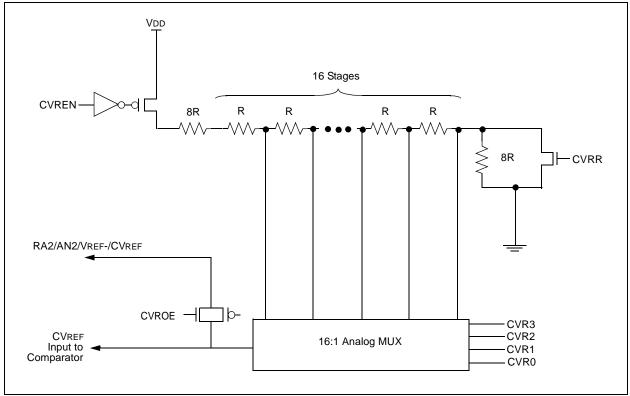

| TABLE 13-1: | REGISTERS ASSOCIATED WITH COMPARATOR VOLTAGE REFERENCE |

|-------------|--------------------------------------------------------|

|-------------|--------------------------------------------------------|

| Address | Name   | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 | Value on<br>POR | Value on<br>all other<br>Resets |

|---------|--------|-------|-------|-------|-------|-------|-------|-------|-------|-----------------|---------------------------------|

| 9Dh     | CVRCON | CVREN | CVROE | CVRR  |       | CVR3  | CVR2  | CVR1  | CVR0  | 000- 0000       | 000- 0000                       |

| 9Ch     | CMCON  | C2OUT | C10UT | C2INV | C1INV | CIS   | CM2   | CM1   | CM0   | 0000 0111       | 0000 0111                       |

**Legend:** x = unknown, u = unchanged, - = unimplemented, read as '0'. Shaded cells are not used with the comparator voltage reference.

| CALL             | Call Subroutine                                                                                                                                                                                                                             |

|------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [ <i>label</i> ] CALL k                                                                                                                                                                                                                     |

| Operands:        | $0 \le k \le 2047$                                                                                                                                                                                                                          |

| Operation:       | $\begin{array}{l} (PC)+1 \rightarrow TOS, \\ k \rightarrow PC < 10:0>, \\ (PCLATH < 4:3>) \rightarrow PC < 12:11> \end{array}$                                                                                                              |

| Status Affected: | None                                                                                                                                                                                                                                        |

| Description:     | Call Subroutine. First, return<br>address (PC+1) is pushed onto<br>the stack. The eleven-bit<br>immediate address is loaded into<br>PC bits <10:0>. The upper bits of<br>the PC are loaded from PCLATH.<br>CALL is a two-cycle instruction. |

| CLRWDT                         | Clear Watchdog Timer                                                                                                                                                                 |

|--------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:                        | [label] CLRWDT                                                                                                                                                                       |

| Operands:                      | None                                                                                                                                                                                 |

| Operation:<br>Status Affected: | $\begin{array}{l} 00h \rightarrow WDT \\ 0 \rightarrow WDT \ prescaler, \\ 1 \rightarrow \overline{TO} \\ 1 \rightarrow \overline{PD} \\ \overline{TO}, \ \overline{PD} \end{array}$ |

| Description:                   | CLRWDT instruction resets the<br>Watchdog Timer. It also resets the<br>prescaler of the WDT. Status bits,<br>TO and PD, are set.                                                     |

| CLRF             | Clear f                                                               |

|------------------|-----------------------------------------------------------------------|

| Syntax:          | [label] CLRF f                                                        |

| Operands:        | $0 \leq f \leq 127$                                                   |

| Operation:       | $\begin{array}{l} 00h \rightarrow (f) \\ 1 \rightarrow Z \end{array}$ |

| Status Affected: | Z                                                                     |

| Description:     | The contents of register 'f' are cleared and the Z bit is set.        |

| COMF             | Complement f                                                                                                                                                   |

|------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [label] COMF f,d                                                                                                                                               |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ d \in [0,1] \end{array}$                                                                                                |

| Operation:       | $(\overline{f}) \rightarrow (destination)$                                                                                                                     |

| Status Affected: | Z                                                                                                                                                              |

| Description:     | The contents of register 'f' are<br>complemented. If 'd' is '0', the<br>result is stored in W. If 'd' is '1',<br>the result is stored back in<br>register 'f'. |

| CLRW             | Clear W                                     | DECF             | Decrement f                                                                                                                                       |

|------------------|---------------------------------------------|------------------|---------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [label] CLRW                                | Syntax:          | [label] DECF f,d                                                                                                                                  |

| Operands:        | None                                        | Operands:        | $0 \le f \le 127$                                                                                                                                 |

| Operation:       | $00h \rightarrow (W)$                       |                  | d ∈ [0,1]                                                                                                                                         |

| ·                | $1 \rightarrow Z$                           | Operation:       | (f) - 1 $\rightarrow$ (destination)                                                                                                               |

| Status Affected: | Z                                           | Status Affected: | Z                                                                                                                                                 |

| Description:     | W register is cleared. Zero bit (Z) is set. | Description:     | Decrement register 'f'. If 'd' is '0',<br>the result is stored in the W<br>register. If 'd' is '1', the result is<br>stored back in register 'f'. |

#### 17.2 DC Characteristics: PIC16F873A/874A/876A/877A (Industrial, Extended) PIC16LF873A/874A/876A/877A (Industrial)

| DC CHARACTERISTICS |       |                                         | $\begin{array}{l} \mbox{Standard Operating Conditions (unless otherwise stated)}\\ \mbox{Operating temperature} & -40^{\circ}C \leq TA \leq +85^{\circ}C \ \ for industrial \\ -40^{\circ}C \leq TA \leq +125^{\circ}C \ \ for extended \\ \mbox{Operating voltage VDD range as described in DC specification} \\ \mbox{(Section 17.1)} \end{array}$ |      |          |       |                                                             |  |  |

|--------------------|-------|-----------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|----------|-------|-------------------------------------------------------------|--|--|

| Param<br>No.       | Sym   | Characteristic                          | Min                                                                                                                                                                                                                                                                                                                                                  | Тур† | Max      | Units | Conditions                                                  |  |  |

|                    | VIL   | Input Low Voltage                       |                                                                                                                                                                                                                                                                                                                                                      |      |          |       |                                                             |  |  |

|                    |       | I/O ports:                              |                                                                                                                                                                                                                                                                                                                                                      |      |          |       |                                                             |  |  |

| D030               |       | with TTL buffer                         | Vss                                                                                                                                                                                                                                                                                                                                                  | —    | 0.15 Vdd | V     | For entire VDD range                                        |  |  |

| D030A              |       |                                         | Vss                                                                                                                                                                                                                                                                                                                                                  | —    | 0.8V     | V     | $4.5V \le V\text{DD} \le 5.5V$                              |  |  |

| D031               |       | with Schmitt Trigger buffer             | Vss                                                                                                                                                                                                                                                                                                                                                  | —    | 0.2 Vdd  | V     |                                                             |  |  |

| D032               |       | MCLR, OSC1 (in RC mode)                 | Vss                                                                                                                                                                                                                                                                                                                                                  | —    | 0.2 Vdd  | V     |                                                             |  |  |

| D033               |       | OSC1 (in XT and LP modes)               | Vss                                                                                                                                                                                                                                                                                                                                                  | —    | 0.3V     | V     | (Note 1)                                                    |  |  |

|                    |       | OSC1 (in HS mode)                       | Vss                                                                                                                                                                                                                                                                                                                                                  | —    | 0.3 Vdd  | V     |                                                             |  |  |

|                    |       | Ports RC3 and RC4:                      |                                                                                                                                                                                                                                                                                                                                                      | —    |          |       |                                                             |  |  |

| D034               |       | with Schmitt Trigger buffer             | Vss                                                                                                                                                                                                                                                                                                                                                  | —    | 0.3 Vdd  | V     | For entire VDD range                                        |  |  |

| D034A              |       | with SMBus                              | -0.5                                                                                                                                                                                                                                                                                                                                                 | —    | 0.6      | V     | For VDD = 4.5 to 5.5V                                       |  |  |

|                    | VIH   | Input High Voltage                      |                                                                                                                                                                                                                                                                                                                                                      |      | -        |       |                                                             |  |  |

|                    |       | I/O ports:                              |                                                                                                                                                                                                                                                                                                                                                      | —    |          |       |                                                             |  |  |

| D040               |       | with TTL buffer                         | 2.0                                                                                                                                                                                                                                                                                                                                                  | —    | Vdd      | V     | $4.5V \leq V\text{DD} \leq 5.5V$                            |  |  |

| D040A              |       |                                         | 0.25 VDD<br>+ 0.8V                                                                                                                                                                                                                                                                                                                                   |      | Vdd      | V     | For entire VDD range                                        |  |  |

| D041               |       | with Schmitt Trigger buffer             | 0.8 Vdd                                                                                                                                                                                                                                                                                                                                              | —    | Vdd      | V     | For entire VDD range                                        |  |  |

| D042               |       | MCLR                                    | 0.8 Vdd                                                                                                                                                                                                                                                                                                                                              | —    | Vdd      | V     |                                                             |  |  |

| D042A              |       | OSC1 (in XT and LP modes)               | 1.6V                                                                                                                                                                                                                                                                                                                                                 | —    | Vdd      | V     | (Note 1)                                                    |  |  |

|                    |       | OSC1 (in HS mode)                       | 0.7 Vdd                                                                                                                                                                                                                                                                                                                                              | —    | Vdd      | V     |                                                             |  |  |

| D043               |       | OSC1 (in RC mode)                       | 0.9 Vdd                                                                                                                                                                                                                                                                                                                                              | —    | Vdd      | V     |                                                             |  |  |

|                    |       | Ports RC3 and RC4:                      |                                                                                                                                                                                                                                                                                                                                                      |      |          |       |                                                             |  |  |

| D044               |       | with Schmitt Trigger buffer             | 0.7 Vdd                                                                                                                                                                                                                                                                                                                                              | —    | Vdd      | V     | For entire VDD range                                        |  |  |

| D044A              |       | with SMBus                              | 1.4                                                                                                                                                                                                                                                                                                                                                  | —    | 5.5      | V     | For VDD = 4.5 to 5.5V                                       |  |  |

| D070               | Ipurb | PORTB Weak Pull-up Current              | 50                                                                                                                                                                                                                                                                                                                                                   | 250  | 400      | μA    | Vdd = 5V, Vpin = Vss,<br>-40°С то +85°С                     |  |  |

|                    | lı∟   | Input Leakage Current <sup>(2, 3)</sup> |                                                                                                                                                                                                                                                                                                                                                      |      |          |       |                                                             |  |  |

| D060               |       | I/O ports                               | _                                                                                                                                                                                                                                                                                                                                                    | _    | ±1       | μA    | $Vss \le VPIN \le VDD,$ pin at high-impedance               |  |  |

| D061               |       | MCLR, RA4/T0CKI                         | _                                                                                                                                                                                                                                                                                                                                                    | —    | ±5       | μA    | $Vss \leq V \text{PIN} \leq V \text{DD}$                    |  |  |

| D063               |       | OSC1                                    | _                                                                                                                                                                                                                                                                                                                                                    | —    | ±5       | μA    | Vss $\leq$ VPIN $\leq$ VDD, XT, HS and LP osc configuration |  |  |

† Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

Note 1: In RC oscillator configuration, the OSC1/CLKI pin is a Schmitt Trigger input. It is not recommended that the PIC16F87XA be driven with external clock in RC mode.

2: The leakage current on the MCLR pin is strongly dependent on the applied voltage level. The specified levels represent normal operating conditions. Higher leakage current may be measured at different input voltages.

3: Negative current is defined as current sourced by the pin.

| Param<br>No. | Sym     | Characte                      | eristic      | Min         | Max  | Units | Conditions                                                    |

|--------------|---------|-------------------------------|--------------|-------------|------|-------|---------------------------------------------------------------|

| 100          | Тнідн   | Clock High Time               | 100 kHz mode | 4.0         | _    | μs    |                                                               |

|              |         |                               | 400 kHz mode | 0.6         | _    | μs    |                                                               |

|              |         |                               | SSP Module   | 0.5 TCY     | _    |       |                                                               |

| 101          | TLOW    | Clock Low Time                | 100 kHz mode | 4.7         | _    | μs    |                                                               |

|              |         |                               | 400 kHz mode | 1.3         | _    | μs    |                                                               |

|              |         |                               | SSP Module   | 0.5 TCY     | _    |       |                                                               |

| 102          | TR      | SDA and SCL Rise<br>Time      | 100 kHz mode | —           | 1000 | ns    |                                                               |

|              |         |                               | 400 kHz mode | 20 + 0.1 Св | 300  | ns    | Cb is specified to be from 10 to 400 pF                       |

| 103          | TF      | SDA and SCL Fall<br>Time      | 100 kHz mode | —           | 300  | ns    |                                                               |

|              |         |                               | 400 kHz mode | 20 + 0.1 Св | 300  | ns    | CB is specified to be from 10 to 400 pF                       |

| 90           | TSU:STA | Start Condition Setup<br>Time | 100 kHz mode | 4.7         | _    | μs    | Only relevant for Repeated Start condition                    |

|              |         |                               | 400 kHz mode | 0.6         | _    | μs    |                                                               |

| 91           | THD:STA | Start Condition Hold<br>Time  | 100 kHz mode | 4.0         | _    | μs    | After this period, the first clock pulse is generated         |

|              |         |                               | 400 kHz mode | 0.6         | _    | μs    |                                                               |

| 106          | THD:DAT | Data Input Hold Time          | 100 kHz mode | 0           | _    | ns    |                                                               |

|              |         |                               | 400 kHz mode | 0           | 0.9  | μs    |                                                               |

| 107          | TSU:DAT | Data Input Setup Time         | 100 kHz mode | 250         | _    | ns    | (Note 2)                                                      |

|              |         |                               | 400 kHz mode | 100         |      | ns    |                                                               |

| 92           | TSU:STO | Stop Condition Setup<br>Time  | 100 kHz mode | 4.7         | _    | μs    |                                                               |

|              |         |                               | 400 kHz mode | 0.6         | _    | μs    |                                                               |

| 109          | ΤΑΑ     | Output Valid from<br>Clock    | 100 kHz mode | _           | 3500 | ns    | (Note 1)                                                      |

|              |         |                               | 400 kHz mode | —           | —    | ns    |                                                               |

| 110          | TBUF    | Bus Free Time                 | 100 kHz mode | 4.7         | _    | μs    | Time the bus must be free before a new transmission can start |

|              |         |                               | 400 kHz mode | 1.3         | _    | μs    |                                                               |

|              | Св      | Bus Capacitive Loading        | _            | 400         | pF   |       |                                                               |

### TABLE 17-11: I<sup>2</sup>C BUS DATA REQUIREMENTS

**Note 1:** As a transmitter, the device must provide this internal minimum delay time to bridge the undefined region (min. 300 ns) of the falling edge of SCL to avoid unintended generation of Start or Stop conditions.

2: A fast mode (400 kHz) I<sup>2</sup>C bus device can be used in a standard mode (100 kHz) I<sup>2</sup>C bus system, but the requirement that, TSU:DAT ≥ 250 ns, must then be met. This will automatically be the case if the device does not stretch the LOW period of the SCL signal. If such a device does stretch the LOW period of the SCL signal, it must output the next data bit to the SDA line, TR MAX. + TSU:DAT = 1000 + 250 = 1250 ns (according to the standard mode I<sup>2</sup>C bus specification), before the SCL line is released.

## APPENDIX C: CONVERSION CONSIDERATIONS

Considerations for converting from previous versions of devices to the ones listed in this data sheet are listed in Table C-1.

| TABLE C-1: CONVERSION CONSIDERATION |

|-------------------------------------|

|-------------------------------------|

| Characteristic                     | PIC16C7X                                         | PIC16F87X                                               | PIC16F87XA                                               |

|------------------------------------|--------------------------------------------------|---------------------------------------------------------|----------------------------------------------------------|

| Pins                               | 28/40                                            | 28/40                                                   | 28/40                                                    |

| Timers                             | 3                                                | 3                                                       | 3                                                        |

| Interrupts                         | 11 or 12                                         | 13 or 14                                                | 14 or 15                                                 |

| Communication                      | PSP, USART, SSP<br>(SPI, I <sup>2</sup> C Slave) | PSP, USART, SSP<br>(SPI, I <sup>2</sup> C Master/Slave) | PSP, USART, SSP<br>(SPI, I <sup>2</sup> C Master/Slave)  |

| Frequency                          | 20 MHz                                           | 20 MHz                                                  | 20 MHz                                                   |

| Voltage                            | 2.5V-5.5V                                        | 2.2V-5.5V                                               | 2.0V-5.5V                                                |

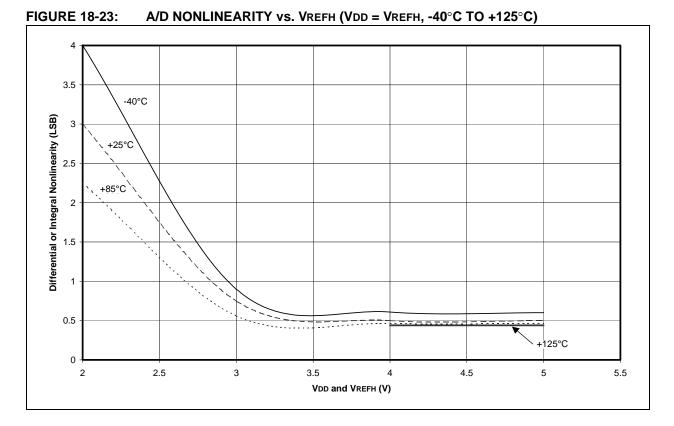

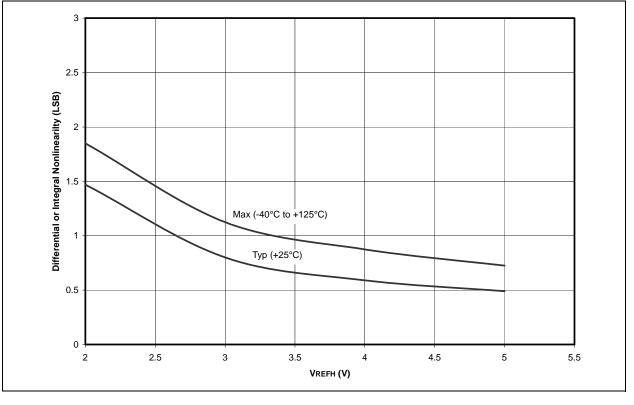

| A/D                                | 8-bit,<br>4 conversion clock selects             | 10-bit,<br>4 conversion clock selects                   | 10-bit,<br>7 conversion clock selects                    |

| CCP                                | 2                                                | 2                                                       | 2                                                        |

| Comparator                         | _                                                | _                                                       | 2                                                        |

| Comparator Voltage<br>Reference    | _                                                | _                                                       | Yes                                                      |

| Program Memory                     | 4K, 8K EPROM                                     | 4K, 8K Flash<br>(Erase/Write on<br>single-word)         | 4K, 8K Flash<br>(Erase/Write on<br>four-word blocks)     |

| RAM                                | 192, 368 bytes                                   | 192, 368 bytes                                          | 192, 368 bytes                                           |

| EEPROM Data                        | None                                             | 128, 256 bytes                                          | 128, 256 bytes                                           |

| Code Protection                    | On/Off                                           | Segmented, starting at end<br>of program memory         | On/Off                                                   |

| Program Memory<br>Write Protection | _                                                | On/Off                                                  | Segmented, starting at<br>beginning of<br>program memory |

| Other                              |                                                  | In-Circuit Debugger,<br>Low-Voltage Programming         | In-Circuit Debugger,<br>Low-Voltage Programming          |

| Special Function Registers<br>Special Function Registers (SFRs) |     |

|-----------------------------------------------------------------|-----|

| Speed, Operating                                                |     |

| SPI Mode                                                        |     |

| Associated Registers                                            | 79  |

| Bus Mode Compatibility                                          |     |

| Effects of a Reset                                              |     |

| Enabling SPI I/O                                                | 75  |

| Master Mode                                                     |     |

| Master/Slave Connection                                         |     |

| Serial Clock                                                    |     |

| Serial Data In                                                  |     |

| Serial Data Out                                                 |     |

| Slave Select                                                    |     |

| Slave Select Synchronization                                    |     |

| Sleep Operation                                                 |     |

| SPI Clock                                                       |     |

| Typical Connection                                              |     |

| SPI Mode Requirements                                           |     |

| SS                                                              | 71  |

| SSP                                                             |     |

| SPI Master/Slave Connection                                     |     |

| SSPADD Register                                                 |     |

| SSPBUF Register                                                 |     |

| SSPCON Register                                                 |     |

| SSPCON2 Register<br>SSPIF                                       |     |

|                                                                 | -   |

| SSPOV                                                           |     |

| SSPSTAT Register                                                |     |

| R/W Bit                                                         |     |

| Overflows                                                       |     |

| Underflow                                                       |     |

| Status Register                                                 |     |

| C Bit                                                           | 22  |

| DC Bit                                                          |     |

| IRP Bit                                                         |     |

| PD Bit                                                          |     |

| RP1:RP0 Bits                                                    | ,   |

| TO Bit                                                          |     |

| Z Bit                                                           |     |

| Synchronous Master Reception                                    |     |

| Associated Registers                                            | 123 |

| Synchronous Master Transmission                                 |     |

| Associated Registers                                            | 122 |

| Synchronous Serial Port Interrupt                               |     |

| Synchronous Slave Reception                                     |     |

| Associated Registers                                            | 125 |

| Synchronous Slave Transmission                                  |     |

| Associated Registers                                            | 125 |

| -                                                               |     |

| т                                                               |     |

| T1CKPS0 Bit                                                     |     |

| T1CKPS1 Bit                                                     | -   |

| T1CON Register                                                  |     |

| T1OSCEN Bit                                                     |     |

| T1SYNC Bit                                                      |     |

| T2CKPS0 Bit                                                     |     |

| T2CKPS1 Bit                                                     | 61  |

T2CON Register

19

TAD

131

Time-out Sequence

148

| Timer0                                        | 53  |

|-----------------------------------------------|-----|

| Associated Registers                          | 55  |

| Clock Source Edge Select (T0SE Bit)           | 23  |

| Clock Source Select (T0CS Bit)                | 23  |

| External Clock                                | 54  |

| Interrupt                                     |     |

| Overflow Enable (TMR0IE Bit)                  |     |

| Overflow Flag (TMR0IF Bit)                    |     |

| Overflow Interrupt                            |     |

| Prescaler                                     |     |

| TOCKI                                         |     |

| Timer0 and Timer1 External Clock Requirements |     |

| Timer1                                        |     |

| Associated Registers                          |     |

| Asynchronous Counter Mode                     |     |

| Reading and Writing to                        |     |

| Counter Operation                             |     |

| Operation in Timer Mode                       |     |

| Oscillator<br>Capacitor Selection             |     |

|                                               |     |

| Prescaler<br>Resetting of Timer1 Registers    |     |

| Resetting Timer1 Using a CCP Trigger Output   |     |

| Synchronized Counter Mode                     |     |

| TMR1H                                         |     |

| TMR1L                                         |     |

| Timer2                                        |     |

| Associated Registers                          |     |

| Output                                        |     |

| Postscaler                                    |     |

| Prescaler                                     |     |

| Prescaler and Postscaler                      |     |

| Timing Diagrams                               |     |

| A/D Conversion                                | 195 |

| Acknowledge Sequence                          |     |

| Asynchronous Master Transmission              |     |

| Asynchronous Master Transmission              | -   |

| (Back to Back)                                | 116 |

| Asynchronous Reception                        |     |

| Asynchronous Reception with                   |     |

| Address Byte First                            | 120 |

| Asynchronous Reception with                   |     |

| Address Detect                                | 120 |

| Baud Rate Generator with Clock Arbitration    | 98  |

| BRG Reset Due to SDA Arbitration During       |     |

| Start Condition                               | 107 |

| Brown-out Reset                               | 184 |

| Bus Collision During a Repeated               |     |

| Start Condition (Case 1)                      | 108 |

| Bus Collision During Repeated                 |     |

| Start Condition (Case 2)                      | 108 |

| Bus Collision During Start Condition          |     |

| (SCL = 0)                                     | 107 |

| Bus Collision During Start Condition          |     |

| (SDA Only)                                    | 106 |

| Bus Collision During Stop Condition           |     |

| (Case 1)                                      | 109 |

| Bus Collision During Stop Condition           |     |

| (Case 2)                                      |     |