Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                           |

|----------------------------|---------------------------------------------------------------------------|

| Product Status             | Active                                                                    |

| Core Processor             | PIC                                                                       |

| Core Size                  | 8-Bit                                                                     |

| Speed                      | 20MHz                                                                     |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                         |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                     |

| Number of I/O              | 22                                                                        |

| Program Memory Size        | 14KB (8K x 14)                                                            |

| Program Memory Type        | FLASH                                                                     |

| EEPROM Size                | 256 x 8                                                                   |

| RAM Size                   | 368 x 8                                                                   |

| Voltage - Supply (Vcc/Vdd) | 4V ~ 5.5V                                                                 |

| Data Converters            | A/D 5x10b                                                                 |

| Oscillator Type            | External                                                                  |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                         |

| Mounting Type              | Through Hole                                                              |

| Package / Case             | 28-DIP (0.300", 7.62mm)                                                   |

| Supplier Device Package    | 28-SPDIP                                                                  |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16f876a-i-sp |

|                            |                                                                           |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| 1 1 4 1 | սու | 2-3: |  |

|---------|-----|------|--|

#### PIC16F876A/877A REGISTER FILE MAP

| Indirect addr.(*)    | 00h         | Indirect addr.(*)             |           | Indirect addr.(*)   | 100h          | Indirect addr.(*)       | 10 |

|----------------------|-------------|-------------------------------|-----------|---------------------|---------------|-------------------------|----|

| TMR0                 | 00n<br>01h  | OPTION REG                    | 80h       | TMR0                | 100h          | OPTION_REG              | 18 |

| PCL                  | 01h<br>02h  |                               | 81h       | PCL                 | 10111<br>102h |                         | 18 |

|                      | 02n<br>03h  | PCL<br>STATUS                 | 82h       | STATUS              | 10211<br>103h | PCL<br>STATUS           | 18 |

| STATUS               | 03n<br>04h  |                               | 83h       | FSR                 | 103n<br>104h  |                         | 18 |

| FSR                  |             | FSR                           | 84h       | FSR                 | 1041<br>105h  | FSR                     | 18 |

| PORTA                | 05h<br>06h  | TRISA                         | 85h       | DODTD               | 105h          | TRISB                   | 18 |

| PORTB                |             | TRISB                         | 86h       | PORTB               | 106n<br>107h  | TRISB                   | 18 |

|                      | 07h         | TRISC<br>TRISD <sup>(1)</sup> | 87h       |                     | 1071<br>108h  |                         | 18 |

| PORTD <sup>(1)</sup> | 08h         | TRISD <sup>(1)</sup>          | 88h       |                     | 109h          |                         | 18 |

| PORTE <sup>(1)</sup> | 09h         |                               | 89h       | PCLATH              | 1091<br>10Ah  | PCLATH                  | 18 |

| PCLATH               | 0Ah         | PCLATH                        | 8Ah       |                     | 10An<br>10Bh  | INTCON                  | 18 |

| INTCON               | 0Bh         | INTCON                        | 8Bh       | INTCON              | 10Bn<br>10Ch  | EECON1                  | 18 |

| PIR1                 | 0Ch         | PIE1                          | 8Ch       | EEDATA              |               |                         | 18 |

| PIR2                 | 0Dh         | PIE2                          | 8Dh       | EEADR               | 10Dh          | EECON2                  | 18 |

| TMR1L                | 0Eh         | PCON                          | 8Eh       | EEDATH              | 10Eh          | Reserved <sup>(2)</sup> | 18 |

| TMR1H                | 0Fh         |                               | 8Fh       | EEADRH              | 10Fh          | Reserved <sup>(2)</sup> | 18 |

| T1CON                | 10h         |                               | 90h       |                     | 110h          |                         | 19 |

| TMR2                 | 11h         | SSPCON2                       | 91h       |                     | 111h          |                         | 19 |

| T2CON                | 12h         | PR2                           | 92h       |                     | 112h          |                         | 19 |

| SSPBUF               | 13h         | SSPADD                        | 93h       |                     | 113h          |                         | 19 |

| SSPCON               | 14h         | SSPSTAT                       | 94h       |                     | 114h          |                         | 19 |

| CCPR1L               | 15h         |                               | 95h       |                     | 115h          |                         | 19 |

| CCPR1H               | 16h         |                               | 96h       | Conorol             | 116h          | Conorol                 | 19 |

| CCP1CON              | 17h         |                               | 97h       | General<br>Purpose  | 117h          | General<br>Purpose      | 19 |

| RCSTA                | 18h         | TXSTA                         | 98h       | Register            | 118h          | Register                | 19 |

| TXREG                | 19h         | SPBRG                         | 99h       | 16 Bytes            | 119h          | 16 Bytes                | 19 |

| RCREG                | 1Ah         |                               | 9Ah       |                     | 11Ah          |                         | 19 |

| CCPR2L               | 1Bh         |                               | 9Bh       |                     | 11Bh          |                         | 19 |

| CCPR2H               | 1Ch         | CMCON                         | 9Ch       |                     | 11Ch          |                         | 19 |

| CCP2CON              | 1Dh         | CVRCON                        | 9Dh       |                     | 11Dh          |                         | 19 |

| ADRESH               | 1Eh         | ADRESL                        | 9Eh       |                     | 11Eh          |                         | 19 |

| ADCON0               | 1Fh         | ADCON1                        | 9Fh       |                     | 11Fh          |                         | 19 |

|                      | 20h         |                               | A0h       |                     | 120h          |                         | 1A |

|                      |             | General                       |           | General             |               | General                 |    |

| General              |             | Purpose                       |           | Purpose             |               | Purpose                 |    |

| Purpose              |             | Register                      |           | Register            |               | Register                |    |

| Register             |             | 80 Bytes                      |           | 80 Bytes            |               | 80 Bytes                |    |

| 96 Bytes             |             |                               | EFh       |                     | 16Fh          |                         | 1E |

|                      |             | accesses                      | F0h       | 200005005           | 170h          | accesses                | 1F |

|                      |             | 70h-7Fh                       |           | accesses<br>70h-7Fh |               | 70h - 7Fh               |    |

| <b>_</b>             | 7Fh         |                               | FFh       |                     | 17Fh          |                         | 1F |

| Bank 0               |             | Bank 1                        |           | Bank 2              |               | Bank 3                  |    |

| Unimple              | mented d    | ata memory locati             | ons. read | <b>as</b> '0'.      |               |                         |    |

|                      | iysical reg | -                             |           |                     |               |                         |    |

|                      | File<br>Address               | <i>I</i>                                                              | File<br>Address | <i>I</i>          | File<br>Address |                         | File<br>Addres |

|----------------------|-------------------------------|-----------------------------------------------------------------------|-----------------|-------------------|-----------------|-------------------------|----------------|

| ndirect addr.(       | *) 00h                        | Indirect addr.(*)                                                     | 80h             | Indirect addr.(*) | 100h            | Indirect addr.(*)       | 180h           |

| TMR0                 | 01h                           | OPTION_REG                                                            | 81h             | TMR0              | 101h            | OPTION_REG              | 181h           |

| PCL                  | 02h                           | PCL                                                                   | 82h             | PCL               | 102h            | PCL                     | 182h           |

| STATUS               | 03h                           | STATUS                                                                | 83h             | STATUS            | 103h            | STATUS                  | 183h           |

| FSR                  | 04h                           | FSR                                                                   | 84h             | FSR               | 104h            | FSR                     | 184h           |

| PORTA                | 05h                           | TRISA                                                                 | 85h             |                   | 105h            |                         | 185h           |

| PORTB                | 06h                           | TRISB                                                                 | 86h             | PORTB             | 106h            | TRISB                   | 186h           |

| PORTC                | 07h                           | TRISC                                                                 | 87h             |                   | 107h            |                         | 187h           |

| PORTD <sup>(1)</sup> | 08h                           | TRISD <sup>(1)</sup>                                                  | 88h             |                   | 108h            |                         | 188h           |

| PORTE <sup>(1)</sup> | 09h                           | TRISE <sup>(1)</sup>                                                  | 89h             |                   | 109h            |                         | 189h           |

| PCLATH               | 0Ah                           | PCLATH                                                                | 8Ah             | PCLATH            | 10Ah            | PCLATH                  | 18Ah           |

| INTCON               | 0Bh                           | INTCON                                                                | 8Bh             | INTCON            | 10Bh            | INTCON                  | 18Bh           |

| PIR1                 | 0Ch                           | PIE1                                                                  | 8Ch             | EEDATA            | 10Ch            | EECON1                  | 18Ch           |

| PIR2                 | 0Dh                           | PIE2                                                                  | 8Dh             | EEADR             | 10Dh            | EECON2                  | 18Dh           |

| TMR1L                | 0Eh                           | PCON                                                                  | 8Eh             | EEDATH            | 10Eh            | Reserved <sup>(2)</sup> | 18Eh           |

| TMR1H                | 0Fh                           |                                                                       | 8Fh             | EEADRH            | 10Fh            | Reserved <sup>(2)</sup> | 18Fh           |

| T1CON                | 10h                           |                                                                       | 90h             |                   | 110h            |                         | 190h           |

| TMR2                 | 11h                           | SSPCON2                                                               | 91h             |                   |                 |                         |                |

| T2CON                | 12h                           | PR2                                                                   | 92h             |                   |                 |                         |                |

| SSPBUF               | 13h                           | SSPADD                                                                | 93h             |                   |                 |                         |                |

| SSPCON               | 14h                           | SSPSTAT                                                               | 94h             |                   |                 |                         |                |

| CCPR1L               | 15h                           |                                                                       | 95h             |                   |                 |                         |                |

| CCPR1H               | 16h                           |                                                                       | 96h             |                   |                 |                         |                |

| CCP1CON              | 17h                           |                                                                       | 97h             |                   |                 |                         |                |

| RCSTA                | 18h                           | TXSTA                                                                 | 98h             |                   |                 |                         |                |

| TXREG                | 19h                           | SPBRG                                                                 | 99h             |                   |                 |                         |                |

| RCREG                | 1Ah                           |                                                                       | 9Ah             |                   |                 |                         |                |

| CCPR2L               | 1Bh                           |                                                                       | 9Bh             |                   |                 |                         |                |

| CCPR2H               | 1Ch                           | CMCON                                                                 | 9Ch             |                   |                 |                         |                |

| CCP2CON              | 1Dh                           | CVRCON                                                                | 9Dh             |                   |                 |                         |                |

| ADRESH               | 1Eh                           | ADRESL                                                                | 9Eh             |                   |                 |                         |                |

| ADCON0               | 1Fh                           | ADCON1                                                                | 9Fh             |                   | 120h            |                         | 1A0h           |

| General              | 20h                           | General                                                               | A0h             |                   | 12011           |                         |                |

| Purpose              |                               | Purpose                                                               |                 | accesses          |                 | accesses                |                |

| Register             |                               | Register                                                              |                 | 20h-7Fh           |                 | A0h - FFh               |                |

| 96 Bytes             |                               | 96 Bytes                                                              |                 |                   | 16Fh            |                         | 1EFh           |

|                      |                               | -                                                                     |                 |                   | 170h            |                         | 1F0h           |

|                      |                               |                                                                       |                 |                   |                 |                         |                |

| <b>D</b> 1 2         | 7Fh                           |                                                                       | FFh             | David C           | 17Fh            | Dersta 0                | 1FFh           |

| Bank 0               |                               | Bank 1                                                                |                 | Bank 2            |                 | Bank 3                  |                |

| * Not<br>ote 1: The  | a physical re<br>se registers | data memory loca<br>egister.<br>are not implemen<br>are reserved; mai | ted on the      | PIC16F873A.       |                 |                         |                |

#### 2.2.2.2 OPTION\_REG Register

The OPTION\_REG Register is a readable and writable register, which contains various control bits to configure the TMR0 prescaler/WDT postscaler (single assignable register known also as the prescaler), the external INT interrupt, TMR0 and the weak pull-ups on PORTB.

**Note:** To achieve a 1:1 prescaler assignment for the TMR0 register, assign the prescaler to the Watchdog Timer.

|         | ••••••      |                                                            |                    |               | ,,               |             |               |          |  |  |  |  |

|---------|-------------|------------------------------------------------------------|--------------------|---------------|------------------|-------------|---------------|----------|--|--|--|--|

|         | R/W-1       | R/W-1                                                      | R/W-1              | R/W-1         | R/W-1            | R/W-1       | R/W-1         | R/W-1    |  |  |  |  |

|         | RBPU        | INTEDG                                                     | TOCS               | TOSE          | PSA              | PS2         | PS1           | PS0      |  |  |  |  |

|         | bit 7       |                                                            |                    |               |                  |             |               | bit 0    |  |  |  |  |

|         |             |                                                            |                    |               |                  |             |               |          |  |  |  |  |

| bit 7   |             | DRTB Pull-up                                               |                    |               |                  |             |               |          |  |  |  |  |

|         |             | B pull-ups ar                                              |                    | ov individual | port latch value | 26          |               |          |  |  |  |  |

| bit 6   |             | PORTB pull-ups are enabled by individual port latch values |                    |               |                  |             |               |          |  |  |  |  |

| DIL U   |             | pt on rising e                                             |                    |               |                  |             |               |          |  |  |  |  |

|         |             | pt on falling                                              |                    |               |                  |             |               |          |  |  |  |  |

| bit 5   | TOCS: TM    | R0 Clock So                                                | urce Select        | t bit         |                  |             |               |          |  |  |  |  |

|         |             | tion on RA4/                                               |                    |               |                  |             |               |          |  |  |  |  |

|         | 0 = Interna | al instruction                                             | cycle clock        | (CLKO)        |                  |             |               |          |  |  |  |  |

| bit 4   |             | R0 Source E                                                | •                  |               |                  |             |               |          |  |  |  |  |

|         |             | nent on high-                                              |                    |               |                  |             |               |          |  |  |  |  |

| hit 0   |             | nent on low-t                                              |                    | Sition on RA  | 4/TUCKI pin      |             |               |          |  |  |  |  |

| bit 3   |             | caler Assign<br>aler is assign                             |                    |               |                  |             |               |          |  |  |  |  |

|         |             | aler is assign                                             |                    |               | le               |             |               |          |  |  |  |  |

| bit 2-0 |             | Prescaler R                                                |                    |               |                  |             |               |          |  |  |  |  |

|         | Bit Value   | TMR0 Rate                                                  | WDT Rate           | e             |                  |             |               |          |  |  |  |  |

|         | 000         | 1:2                                                        | 1:1                |               |                  |             |               |          |  |  |  |  |

|         | 001<br>010  | 1:4                                                        | 1:2<br>1:4         |               |                  |             |               |          |  |  |  |  |

|         | 010         | 1:8<br>1:16                                                | 1:8                |               |                  |             |               |          |  |  |  |  |

|         | 100<br>101  | 1:32                                                       | 1 : 16<br>1 : 32   |               |                  |             |               |          |  |  |  |  |

|         | 110         | 1:64<br>1:128                                              | 1:64               |               |                  |             |               |          |  |  |  |  |

|         | 111         | 1 : 256                                                    | 1 : 128            |               |                  |             |               |          |  |  |  |  |

|         | 1           |                                                            |                    |               |                  |             |               | 1        |  |  |  |  |

|         | Legend:     |                                                            | 10/ 1/             |               |                  |             | :             | 21       |  |  |  |  |

|         | R = Reada   |                                                            |                    | Vritable bit  | U = Unimple      |             |               |          |  |  |  |  |

|         | - n = Value | e at POR                                                   | 1 <sup>°</sup> = E | Bit is set    | '0' = Bit is c   | lieared     | x = Bit is ur | IKNOWN   |  |  |  |  |

|         | Note:       | When using                                                 | I ow-Volta         | ne ICSP Pro   | gramming (LVP    | ) and the n | ull-ups on F  | ORTR are |  |  |  |  |

|         |             |                                                            |                    |               | r must be clear  |             |               |          |  |  |  |  |

|         |             | and ensure                                                 | the proper         | operation of  | the device       |             |               |          |  |  |  |  |

#### **REGISTER 2-2: OPTION\_REG REGISTER (ADDRESS 81h, 181h)**

NOTES:

### 6.4 Timer1 Operation in Asynchronous Counter Mode

If control bit  $\overline{T1SYNC}$  (T1CON<2>) is set, the external clock input is not synchronized. The timer continues to increment asynchronous to the internal phase clocks. The timer will continue to run during Sleep and can generate an interrupt-on-overflow which will wake-up the processor. However, special precautions in software are needed to read/write the timer.

In Asynchronous Counter mode, Timer1 cannot be used as a time base for capture or compare operations.

#### 6.4.1 READING AND WRITING TIMER1 IN ASYNCHRONOUS COUNTER MODE

Reading TMR1H or TMR1L while the timer is running from an external asynchronous clock will ensure a valid read (taken care of in hardware). However, the user should keep in mind that reading the 16-bit timer in two 8-bit values itself, poses certain problems, since the timer may overflow between the reads.

For writes, it is recommended that the user simply stop the timer and write the desired values. A write contention may occur by writing to the timer registers while the register is incrementing. This may produce an unpredictable value in the timer register.

Reading the 16-bit value requires some care. Examples 12-2 and 12-3 in the PIC<sup>®</sup> Mid-Range MCU Family Reference Manual (DS33023) show how to read and write Timer1 when it is running in Asynchronous mode.

## 6.5 Timer1 Oscillator

A crystal oscillator circuit is built-in between pins T1OSI (input) and T1OSO (amplifier output). It is enabled by setting control bit, T1OSCEN (T1CON<3>). The oscillator is a low-power oscillator, rated up to 200 kHz. It will continue to run during Sleep. It is primarily intended for use with a 32 kHz crystal. Table 6-1 shows the capacitor selection for the Timer1 oscillator.

The Timer1 oscillator is identical to the LP oscillator. The user must provide a software time delay to ensure proper oscillator start-up.

## TABLE 6-1:CAPACITOR SELECTION FOR<br/>THE TIMER1 OSCILLATOR

| Freq.                          | C1                                                                                    | C2                                                                                                                                                   |  |  |

|--------------------------------|---------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| 32 kHz                         | 33 pF                                                                                 | 33 pF                                                                                                                                                |  |  |

| 100 kHz                        | 15 pF                                                                                 | 15 pF                                                                                                                                                |  |  |

| 200 kHz                        | 15 pF                                                                                 | 15 pF                                                                                                                                                |  |  |

| lues are for o                 | design guida                                                                          | nce only.                                                                                                                                            |  |  |

| Crystals                       | Tested:                                                                               |                                                                                                                                                      |  |  |

| Epson C-00                     | 1R32.768K-A                                                                           | ± 20 PPM                                                                                                                                             |  |  |

| Epson C-2 100.00 KC-P ± 20 PPM |                                                                                       |                                                                                                                                                      |  |  |

| STD XTL 2                      | 200.000 kHz                                                                           | ± 20 PPM                                                                                                                                             |  |  |

|                                | 32 kHz<br>100 kHz<br>200 kHz<br>Iues are for o<br>Crystals<br>Epson C-00<br>Epson C-2 | 32 kHz     33 pF       100 kHz     15 pF       200 kHz     15 pF       lues are for design guidat       Crystals Tested:       Epson C-001R32.768K-A |  |  |

**Note 1:** Higher capacitance increases the stability of oscillator but also increases the start-up time.

2: Since each resonator/crystal has its own characteristics, the user should consult the resonator/crystal manufacturer for appropriate values of external components.

### 6.6 Resetting Timer1 Using a CCP Trigger Output

If the CCP1 or CCP2 module is configured in Compare mode to generate a "special event trigger" (CCP1M3:CCP1M0 = 1011), this signal will reset Timer1.

| Note: | The special event triggers from the CCP1 |

|-------|------------------------------------------|

|       | and CCP2 modules will not set interrupt  |

|       | flag bit, TMR1IF (PIR1<0>).              |

Timer1 must be configured for either Timer or Synchronized Counter mode to take advantage of this feature. If Timer1 is running in Asynchronous Counter mode, this Reset operation may not work.

In the event that a write to Timer1 coincides with a special event trigger from CCP1 or CCP2, the write will take precedence.

In this mode of operation, the CCPRxH:CCPRxL register pair effectively becomes the period register for Timer1.

| ER 9-2: | SSPCON                                                                                                                                                                                                                                                                                                                                       | 1: MSSP C                                                          | ONTROL F                   | REGISTER        | 1 (SPI MC                   | DE) (ADD      | RESS 14h      | )           |  |  |  |  |

|---------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------|----------------------------|-----------------|-----------------------------|---------------|---------------|-------------|--|--|--|--|

|         | R/W-0                                                                                                                                                                                                                                                                                                                                        | R/W-0                                                              | R/W-0                      | R/W-0           | R/W-0                       | R/W-0         | R/W-0         | R/W-0       |  |  |  |  |

|         | WCOL                                                                                                                                                                                                                                                                                                                                         | SSPOV                                                              | SSPEN                      | CKP             | SSPM3                       | SSPM2         | SSPM1         | SSPM0       |  |  |  |  |

|         | bit 7                                                                                                                                                                                                                                                                                                                                        |                                                                    |                            |                 |                             |               |               | bit 0       |  |  |  |  |

| bit 7   |                                                                                                                                                                                                                                                                                                                                              | /rite Collision                                                    | -                          |                 |                             |               |               |             |  |  |  |  |

|         |                                                                                                                                                                                                                                                                                                                                              | SSPBUF reg<br>ed in software<br>ollision                           |                            | en while it i   | s still transm              | nitting the p | revious wor   | d. (Must be |  |  |  |  |

| bit 6   | SSPOV: R                                                                                                                                                                                                                                                                                                                                     | Receive Over                                                       | flow Indicato              | or bit          |                             |               |               |             |  |  |  |  |

|         | <u>SPI Slave</u>                                                                                                                                                                                                                                                                                                                             | mode:                                                              |                            |                 |                             |               |               |             |  |  |  |  |

|         | of ove<br>must<br>cleare                                                                                                                                                                                                                                                                                                                     | v byte is rece<br>erflow, the da<br>read the SSI<br>ed in software | ata in SSPSF<br>PBUF, even | R is lost. Ov   | verflow can o               | only occur in | Slave mod     | e. The user |  |  |  |  |

|         | 0 = No ov                                                                                                                                                                                                                                                                                                                                    | 0 = No overflow                                                    |                            |                 |                             |               |               |             |  |  |  |  |

|         | Note:                                                                                                                                                                                                                                                                                                                                        |                                                                    |                            |                 | t is not set<br>to the SSPE |               |               | eption (and |  |  |  |  |

| bit 5   | SSPEN: S                                                                                                                                                                                                                                                                                                                                     | Synchronous                                                        | Serial Port E              | Enable bit      |                             |               |               |             |  |  |  |  |

|         |                                                                                                                                                                                                                                                                                                                                              | es serial port<br>les serial por                                   |                            |                 |                             |               | ial port pins |             |  |  |  |  |

|         | Note:                                                                                                                                                                                                                                                                                                                                        | When enal                                                          | oled, these p              | oins must be    | e properly co               | nfigured as   | input or out  | put.        |  |  |  |  |

| bit 4   | CKP: Cloo                                                                                                                                                                                                                                                                                                                                    | ck Polarity Se                                                     | elect bit                  |                 |                             |               |               |             |  |  |  |  |

|         |                                                                                                                                                                                                                                                                                                                                              | ate for clock<br>ate for clock                                     | •                          |                 |                             |               |               |             |  |  |  |  |

| bit 3-0 | SSPM3:S                                                                                                                                                                                                                                                                                                                                      | SPM0: Sync                                                         | hronous Ser                | ial Port Mod    | de Select bits              | 5             |               |             |  |  |  |  |

|         | <ul> <li>0101 = SPI Slave mode, clock = SCK pin. SS pin control disabled. SS can be used as I/O</li> <li>0100 = SPI Slave mode, clock = SCK pin. SS pin control enabled.</li> <li>0011 = SPI Master mode, clock = TMR2 output/2</li> <li>0010 = SPI Master mode, clock = Fosc/64</li> <li>0001 = SPI Master mode, clock = Fosc/16</li> </ul> |                                                                    |                            |                 |                             |               |               |             |  |  |  |  |

|         |                                                                                                                                                                                                                                                                                                                                              | PI Master mo                                                       |                            |                 |                             |               |               |             |  |  |  |  |

|         | Note:                                                                                                                                                                                                                                                                                                                                        | Bit combin<br>I <sup>2</sup> C mode o                              |                            | becifically lis | sted here are               | either rese   | rved or imp   | lemented in |  |  |  |  |

|         |                                                                                                                                                                                                                                                                                                                                              |                                                                    |                            |                 |                             |               |               |             |  |  |  |  |

|         | I a manual.                                                                                                                                                                                                                                                                                                                                  |                                                                    |                            |                 |                             |               |               |             |  |  |  |  |

| Legend:            |                  |                      |                    |

|--------------------|------------------|----------------------|--------------------|

| R = Readable bit   | W = Writable bit | U = Unimplemented    | bit, read as '0'   |

| - n = Value at POR | '1' = Bit is set | '0' = Bit is cleared | x = Bit is unknown |

## REGISTER 9-2: SSPCON1: MSSP CONTROL REGISTER 1 (SPI MODE) (ADDRESS 14h)

#### 9.3.6 SLAVE MODE

In Slave mode, the data is transmitted and received as the external clock pulses appear on SCK. When the last bit is latched, the SSPIF interrupt flag bit is set.

While in Slave mode, the external clock is supplied by the external clock source on the SCK pin. This external clock must meet the minimum high and low times as specified in the electrical specifications.

While in Sleep mode, the slave can transmit/receive data. When a byte is received, the device will wake-up from Sleep.

#### 9.3.7 SLAVE SELECT SYNCHRONIZATION

The  $\overline{SS}$  pin allows a Synchronous Slave mode. The SPI must be in Slave mode with  $\overline{SS}$  pin control enabled (SSPCON<3:0> = 04h). The pin must not be driven low for the  $\overline{SS}$  pin to function as an input. The data latch must be high. When the  $\overline{SS}$  pin is low, transmission and reception are enabled and the SDO pin is driven. When

the  $\overline{SS}$  pin goes high, the SDO pin is no longer driven even if in the middle of a transmitted byte and becomes a floating output. External pull-up/pull-down resistors may be desirable, depending on the application.

| Note 1: | When the SPI is in Slave mode with $\overline{SS}$ pin      |

|---------|-------------------------------------------------------------|

|         | control enabled (SSPCON< $3:0> = 0100$ ),                   |

|         | the SPI module will reset if the $\overline{SS}$ pin is set |

|         | to VDD.                                                     |

2: If the SPI is used in Slave Mode with CKE set, then the SS pin control must be enabled.

When the SPI module resets, the bit counter is forced to '0'. This can be done by either forcing the  $\overline{SS}$  pin to a high level or clearing the SSPEN bit.

To emulate two-wire communication, the SDO pin can be connected to the SDI pin. When the SPI needs to operate as a receiver, the SDO pin can be configured as an input. This disables transmissions from the SDO. The SDI can always be left as an input (SDI function) since it cannot create a bus conflict.

##

#### FIGURE 9-4: SLAVE SYNCHRONIZATION WAVEFORM

| REGISTER 9-4: | SSPCON1                                                                                                                                                                                                                                                                                                                                                                                      | : MSSP C                                   |                | EGISTER        | 1 (I <sup>2</sup> C MO | DE) (ADD      | RESS 14h      |               |  |

|---------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------|----------------|----------------|------------------------|---------------|---------------|---------------|--|

|               | R/W-0                                                                                                                                                                                                                                                                                                                                                                                        | R/W-0                                      | R/W-0          | R/W-0          | R/W-0                  | R/W-0         | R/W-0         | R/W-0         |  |

|               | WCOL                                                                                                                                                                                                                                                                                                                                                                                         | SSPOV                                      | SSPEN          | CKP            | SSPM3                  | SSPM2         | SSPM1         | SSPM0         |  |

|               | bit 7                                                                                                                                                                                                                                                                                                                                                                                        |                                            |                |                |                        |               |               | bit 0         |  |

| bit 7         | WCOL: Wr                                                                                                                                                                                                                                                                                                                                                                                     | rite Collision                             | Detect bit     |                |                        |               |               |               |  |

|               |                                                                                                                                                                                                                                                                                                                                                                                              | Fransmit mo                                |                |                |                        |               |               |               |  |

|               |                                                                                                                                                                                                                                                                                                                                                                                              | e to the SSP<br>smission to t<br>Ilision   |                |                |                        |               | itions were   | not valid for |  |

|               | 1 = The S                                                                                                                                                                                                                                                                                                                                                                                    | ansmit mode<br>SPBUF regi<br>d in software | ster is writte | en while it is | s still transm         | nitting the p | revious wor   | d. (Must be   |  |

|               |                                                                                                                                                                                                                                                                                                                                                                                              | mode (Masi                                 | ter or Slave   | modes):        |                        |               |               |               |  |

|               |                                                                                                                                                                                                                                                                                                                                                                                              | lon't care" bi                             |                |                |                        |               |               |               |  |

| bit 6         |                                                                                                                                                                                                                                                                                                                                                                                              | eceive Over                                | flow Indicato  | r bit          |                        |               |               |               |  |

|               | -                                                                                                                                                                                                                                                                                                                                                                                            | e is received<br>d in software             |                | SPBUF reg      | ister is still h       | nolding the p | previous byt  | e. (Must be   |  |

|               | <u>In Transmi</u><br>This is a "d                                                                                                                                                                                                                                                                                                                                                            | <u>t mode:</u><br>Ion't care" bi           | t in Transmit  | mode.          |                        |               |               |               |  |

| bit 5         |                                                                                                                                                                                                                                                                                                                                                                                              | ynchronous                                 |                |                |                        |               |               |               |  |

|               |                                                                                                                                                                                                                                                                                                                                                                                              | es the serial pes the serial               |                |                |                        |               | ne serial por | t pins        |  |

|               | Note:                                                                                                                                                                                                                                                                                                                                                                                        | When enab                                  | led, the SDA   | and SCL pi     | ns must be p           | roperly confi | gured as inp  | ut or output. |  |

| bit 4         | CKP: SCK                                                                                                                                                                                                                                                                                                                                                                                     | Release Co                                 | ontrol bit     |                |                        |               |               |               |  |

|               | In Slave m<br>1 = Releas<br>0 = Holds o                                                                                                                                                                                                                                                                                                                                                      |                                            | ock stretch).  | (Used to er    | nsure data s           | etup time.)   |               |               |  |

|               | <u>In Master r</u><br>Unused in                                                                                                                                                                                                                                                                                                                                                              |                                            |                |                |                        |               |               |               |  |

| bit 3-0       | SSPM3:SS                                                                                                                                                                                                                                                                                                                                                                                     | SPM0: Synch                                | nronous Ser    | ial Port Moc   | le Select bits         | 5             |               |               |  |

|               | 1111 = $I^2C$ Slave mode, 10-bit address with Start and Stop bit interrupts enabled<br>1110 = $I^2C$ Slave mode, 7-bit address with Start and Stop bit interrupts enabled<br>1011 = $I^2C$ Firmware Controlled Master mode (Slave Idle)<br>1000 = $I^2C$ Master mode, clock = Fosc/(4 * (SSPADD + 1))<br>0111 = $I^2C$ Slave mode, 10-bit address<br>0110 = $I^2C$ Slave mode, 7-bit address |                                            |                |                |                        |               |               |               |  |

|               | <b>Note:</b> Bit combinations not specifically listed here are either reserved or implemented in SPI mode only.                                                                                                                                                                                                                                                                              |                                            |                |                |                        |               |               |               |  |

|               | Legend:                                                                                                                                                                                                                                                                                                                                                                                      |                                            |                |                |                        |               |               | ]             |  |

|               | R = Reada                                                                                                                                                                                                                                                                                                                                                                                    | ble bit                                    | W = W          | ritable bit    | U = Unim               | plemented     | bit, read as  | '0'           |  |

|                |     |                  |                      | ,                  |

|----------------|-----|------------------|----------------------|--------------------|

| - n = Value at | POR | '1' = Bit is set | '0' = Bit is cleared | x = Bit is unknown |

|       | R/W-0                                                                                                                                                    | R/W-0                                              | R/W-0                    | R/W-0         | R/W-0         | R/W-0        | R/W-0        | R/W-0       |

|-------|----------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------|--------------------------|---------------|---------------|--------------|--------------|-------------|

|       | GCEN                                                                                                                                                     | ACKSTAT                                            | ACKDT                    | ACKEN         | RCEN          | PEN          | RSEN         | SEN         |

|       | bit 7                                                                                                                                                    | 1                                                  |                          | I             |               | I            | I            | bit 0       |

| bit 7 |                                                                                                                                                          | eneral Call En                                     |                          | -             | -             |              |              |             |

|       |                                                                                                                                                          | e interrupt whe<br>ral call address                |                          | call address  | (0000h) is    | received in  | the SSPSF    | 2           |

| bit 6 | bit 6 ACKSTAT: Acknowledge Status bit (Master Transmit mode only)                                                                                        |                                                    |                          |               |               |              |              |             |

|       |                                                                                                                                                          | wledge was n<br>wledge was re                      |                          |               |               |              |              |             |

| bit 5 | ACKDT: A                                                                                                                                                 | Acknowledge [                                      | Data bit (Mas            | ster Receive  | mode only)    |              |              |             |

|       | 1 = Not A<br>0 = Ackno                                                                                                                                   | cknowledge<br>wledge                               |                          |               |               |              |              |             |

|       | Note:                                                                                                                                                    | Value that w the end of a                          |                          | itted when th | e user initia | tes an Ackr  | nowledge se  | equence at  |

| bit 4 | ACKEN:                                                                                                                                                   | Acknowledge                                        | Sequence E               | nable bit (Ma | ster Receiv   | e mode on    | ly)          |             |

|       | 1 = Initiat<br>Autor                                                                                                                                     | e Acknowledg<br>matically cleare<br>owledge seque  | e sequence<br>d by hardw | e on SDA ar   |               |              |              | T data bit. |

| bit 3 | RCEN: R                                                                                                                                                  | eceive Enable                                      | bit (Master i            | mode only)    |               |              |              |             |

|       | 1 = Enabl<br>0 = Recei                                                                                                                                   | es Receive mo<br>ve Idle                           | ode for I <sup>2</sup> C |               |               |              |              |             |

| bit 2 | PEN: Stop                                                                                                                                                | o Condition En                                     | able bit (Ma             | ster mode or  | nly)          |              |              |             |

|       |                                                                                                                                                          | e Stop conditio                                    | n on SDA a               | nd SCL pins.  | Automatica    | ally cleared | by hardwa    | re.         |

| bit 1 | RSEN: Repeated Start Condition Enabled bit (Master mode only)                                                                                            |                                                    |                          |               |               |              |              |             |

|       | <ul> <li>1 = Initiate Repeated Start condition on SDA and SCL pins. Automatically cleared by hardv</li> <li>0 = Repeated Start condition Idle</li> </ul> |                                                    |                          |               | hardware.     |              |              |             |

| bit 0 | SEN: Star                                                                                                                                                | t Condition En                                     | abled/Streto             | h Enabled bi  | t             |              |              |             |

|       | <u>In Master mode:</u><br>1 = Initiate Start condition on SDA and SCL pins. Automatically cleared by hardware.<br>0 = Start condition Idle               |                                                    |                          |               |               |              |              |             |

|       |                                                                                                                                                          | <u>node:</u><br>stretching is e<br>stretching is e |                          |               |               |              |              | nabled)     |

|       | Legend:                                                                                                                                                  |                                                    |                          |               |               |              |              |             |

|       | R = Read                                                                                                                                                 |                                                    |                          | itable bit    | -             |              | bit, read as |             |

|       | - n = Valu                                                                                                                                               | e at POR                                           | '1' = Bit                | is set        | '0' = Bit is  | cleared      | x = Bit is ι | unknown     |

**Note:** For bits ACKEN, RCEN, PEN, RSEN, SEN: If the I<sup>2</sup>C module is not in the Idle mode, this bit may not be set (no spooling) and the SSPBUF may not be written (or writes to the SSPBUF are disabled).

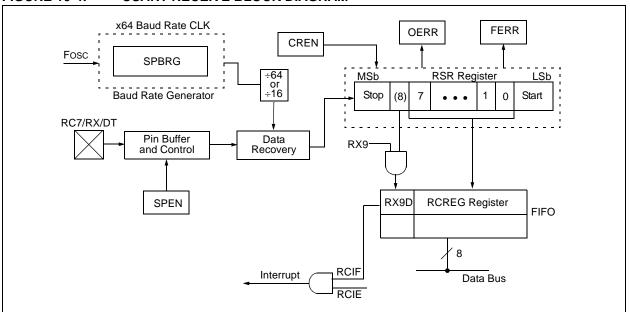

#### 10.2.2 USART ASYNCHRONOUS RECEIVER

The receiver block diagram is shown in Figure 10-4. The data is received on the RC7/RX/DT pin and drives the data recovery block. The data recovery block is actually a high-speed shifter, operating at x16 times the baud rate; whereas the main receive serial shifter operates at the bit rate or at Fosc.

Once Asynchronous mode is selected, reception is enabled by setting bit CREN (RCSTA<4>).

The heart of the receiver is the Receive (Serial) Shift Register (RSR). After sampling the Stop bit, the received data in the RSR is transferred to the RCREG register (if it is empty). If the transfer is complete, flag bit, RCIF (PIR1<5>), is set. The actual interrupt can be enabled/disabled by setting/clearing enable bit, RCIE (PIE1<5>). Flag bit RCIF is a read-only bit which is cleared by the hardware. It is cleared when the RCREG register has been read and is empty. The RCREG is a double-buffered register (i.e., it is a two-deep FIFO). It is possible for two bytes of data to be received and transferred to the RCREG FIFO and a third byte to begin shifting to the RSR register. On the detection of the Stop bit of the third byte, if the RCREG register is still full, the Overrun Error bit, OERR (RCSTA<1>), will be set. The word in the RSR will be lost. The RCREG register can be read twice to retrieve the two bytes in the FIFO. Overrun bit OERR has to be cleared in software. This is done by resetting the receive logic (CREN is cleared and then set). If bit OERR is set, transfers from the RSR register to the RCREG register are inhibited and no further data will be received. It is, therefore, essential to clear error bit OERR if it is set. Framing error bit, FERR (RCSTA<2>), is set if a Stop bit is detected as clear. Bit FERR and the 9th receive bit are buffered the same way as the receive data. Reading the RCREG will load bits RX9D and FERR with new values, therefore, it is essential for the user to read the RCSTA register before reading the RCREG register in order not to lose the old FERR and RX9D information.

FIGURE 10-4: USART RECEIVE BLOCK DIAGRAM

| RLF              | Rotate Left f through Carry                                                                                                                                                                                       |  |  |  |  |

|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| Syntax:          | [ <i>label</i> ] RLF f,d                                                                                                                                                                                          |  |  |  |  |

| Operands:        | $\begin{array}{l} 0\leq f\leq 127\\ d\in [0,1] \end{array}$                                                                                                                                                       |  |  |  |  |

| Operation:       | See description below                                                                                                                                                                                             |  |  |  |  |

| Status Affected: | С                                                                                                                                                                                                                 |  |  |  |  |

| Description:     | The contents of register 'f' are<br>rotated one bit to the left through the<br>Carry flag. If 'd' is '0', the result is<br>placed in the W register. If 'd' is '1',<br>the result is stored back in register 'f'. |  |  |  |  |

| Syntax:          | [label] SLEEP                                                                                                                                                                                                                          |

|------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Operands:        | None                                                                                                                                                                                                                                   |

| Operation:       | $\begin{array}{l} 00h \rightarrow WDT, \\ 0 \rightarrow WDT \ \text{prescaler}, \\ 1 \rightarrow \overline{TO}, \\ 0 \rightarrow \overline{PD} \end{array}$                                                                            |

| Status Affected: | TO, PD                                                                                                                                                                                                                                 |

| Description:     | The power-down status bit, $\overline{PD}$ ,<br>is cleared. Time-out status bit,<br>$\overline{TO}$ , is set. Watchdog Timer and<br>its prescaler are cleared.<br>The processor is put into Sleep<br>mode with the oscillator stopped. |

| RETURN           | Return from Subroutine                                                                                                                                     |  |  |  |  |  |

|------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| Syntax:          | [label] RETURN                                                                                                                                             |  |  |  |  |  |

| Operands:        | None                                                                                                                                                       |  |  |  |  |  |

| Operation:       | $TOS \rightarrow PC$                                                                                                                                       |  |  |  |  |  |

| Status Affected: | None                                                                                                                                                       |  |  |  |  |  |

| Description:     | Return from subroutine. The stack<br>is POPed and the top of the stack<br>(TOS) is loaded into the program<br>counter. This is a two-cycle<br>instruction. |  |  |  |  |  |

| SUBLW            | Subtract W from Literal                                                                                                      |  |  |  |  |  |

|------------------|------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|