Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                    |

|----------------------------|---------------------------------------------------------------------------|

| Core Processor             | PIC                                                                       |

| Core Size                  | 8-Bit                                                                     |

| Speed                      | 20MHz                                                                     |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                         |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                     |

| Number of I/O              | 22                                                                        |

| Program Memory Size        | 14KB (8K x 14)                                                            |

| Program Memory Type        | FLASH                                                                     |

| EEPROM Size                | 256 x 8                                                                   |

| RAM Size                   | 368 x 8                                                                   |

| Voltage - Supply (Vcc/Vdd) | 4V ~ 5.5V                                                                 |

| Data Converters            | A/D 5x10b                                                                 |

| Oscillator Type            | External                                                                  |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                         |

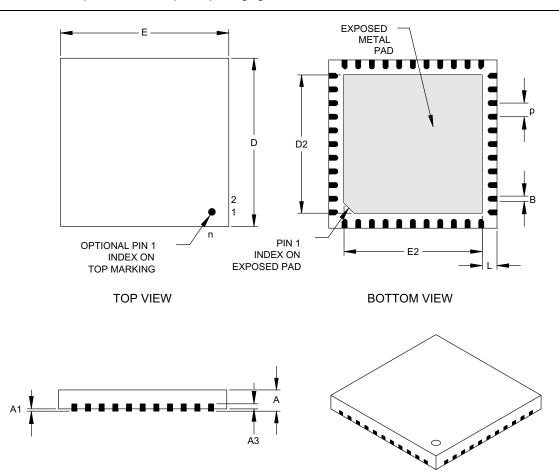

| Mounting Type              | Surface Mount                                                             |

| Package / Case             | 28-SSOP (0.209", 5.30mm Width)                                            |

| Supplier Device Package    | 28-SSOP                                                                   |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16f876a-i-ss |

|                            |                                                                           |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| Pin Name                                                 | QFN<br>Pin# | I/O/P<br>Type    | Buffer<br>Type | Description           |                                                                                     |  |  |  |

|----------------------------------------------------------|-------------|------------------|----------------|-----------------------|-------------------------------------------------------------------------------------|--|--|--|

|                                                          |             |                  |                |                       | PORTB is a bidirectional I/O port. PORTB can be software                            |  |  |  |

|                                                          |             |                  |                |                       | programmed for internal weak pull-ups on all inputs.                                |  |  |  |

| RB0/INT                                                  | 21          | 18               |                | TTL/ST <sup>(1)</sup> |                                                                                     |  |  |  |

| RB0                                                      |             |                  | I/O            |                       | Digital I/O.                                                                        |  |  |  |

| INT                                                      |             |                  | I              |                       | External interrupt.                                                                 |  |  |  |

| RB1                                                      | 22          | 19               | I/O            | TTL                   | Digital I/O.                                                                        |  |  |  |

| RB2                                                      | 23          | 20               | I/O            | TTL                   | Digital I/O.                                                                        |  |  |  |

| RB3/PGM                                                  | 24          | 21               |                | TTL                   |                                                                                     |  |  |  |

| RB3                                                      |             |                  | I/O            |                       | Digital I/O.                                                                        |  |  |  |

| PGM                                                      |             |                  | I              |                       | Low-voltage (single-supply) ICSP programming enable pir                             |  |  |  |

| RB4                                                      | 25          | 22               | I/O            | TTL                   | Digital I/O.                                                                        |  |  |  |

| RB5                                                      | 26          | 23               | I/O            | TTL                   | Digital I/O.                                                                        |  |  |  |

| RB6/PGC                                                  | 27          | 24               |                | TTL/ST <sup>(2)</sup> |                                                                                     |  |  |  |

| RB6                                                      |             |                  | I/O            |                       | Digital I/O.                                                                        |  |  |  |

| PGC                                                      |             |                  | I              |                       | In-circuit debugger and ICSP programming clock.                                     |  |  |  |

| PGC I I In-circui<br>RB7/PGD 28 25 TTL/ST <sup>(2)</sup> |             |                  |                |                       |                                                                                     |  |  |  |

| RB7<br>PGD<br>RC0/T1OSO/T1CKI 11                         |             | -                | I/O            |                       | Digital I/O.                                                                        |  |  |  |

| PGD                                                      |             |                  | I/O            |                       | In-circuit debugger and ICSP programming data.                                      |  |  |  |

|                                                          |             |                  |                |                       | PORTC is a bidirectional I/O port.                                                  |  |  |  |

| RC0/T1OSO/T1CKI                                          | 11          | 8                |                | ST                    |                                                                                     |  |  |  |

| RC0                                                      |             | -                | I/O            |                       | Digital I/O.                                                                        |  |  |  |

| T1OSO                                                    |             |                  | 0              |                       | Timer1 oscillator output.                                                           |  |  |  |

| T1CKI                                                    |             |                  | I              |                       | Timer1 external clock input.                                                        |  |  |  |

| RC1/T1OSI/CCP2                                           | 12          | 9                |                | ST                    |                                                                                     |  |  |  |

| RC1                                                      |             |                  | I/O            |                       | Digital I/O.                                                                        |  |  |  |

| T1OSI                                                    |             |                  | 1              |                       | Timer1 oscillator input.                                                            |  |  |  |

| CCP2                                                     |             |                  | I/O            |                       | Capture2 input, Compare2 output, PWM2 output.                                       |  |  |  |

| RC2/CCP1                                                 | 13          | 10               |                | ST                    |                                                                                     |  |  |  |

| RC2                                                      |             |                  | I/O            |                       | Digital I/O.                                                                        |  |  |  |

| CCP1                                                     |             |                  | I/O            |                       | Capture1 input, Compare1 output, PWM1 output.                                       |  |  |  |

| RC3/SCK/SCL                                              | 14          | 11               | 1/0            | ST                    | District VO                                                                         |  |  |  |

| RC3<br>SCK                                               |             |                  | I/O<br>I/O     |                       | Digital I/O.<br>Synchronous serial clock input/output for SPI mode.                 |  |  |  |

| SCL                                                      |             |                  | 1/O            |                       | Synchronous serial clock input/output for Sr I mode.                                |  |  |  |

| RC4/SDI/SDA                                              | 15          | 12               | ., 0           | ST                    |                                                                                     |  |  |  |

| RC4                                                      | 15          | 12               | I/O            | 51                    | Digital I/O.                                                                        |  |  |  |

| SDI                                                      |             |                  | ., c           |                       | SPI data in.                                                                        |  |  |  |

| SDA                                                      |             |                  | I/O            |                       | I <sup>2</sup> C data I/O.                                                          |  |  |  |

| RC5/SDO                                                  | 16          | 13               |                | ST                    |                                                                                     |  |  |  |

| RC5                                                      |             |                  | I/O            |                       | Digital I/O.                                                                        |  |  |  |

| SDO                                                      |             |                  | 0              |                       | SPI data out.                                                                       |  |  |  |

| RC6/TX/CK                                                | 17          | 14               |                | ST                    |                                                                                     |  |  |  |

| RC6                                                      |             |                  | I/O            |                       | Digital I/O.                                                                        |  |  |  |

| TX                                                       |             |                  | 0              |                       | USART asynchronous transmit.                                                        |  |  |  |

| CK                                                       |             |                  | I/O            |                       | USART1 synchronous clock.                                                           |  |  |  |

| RC7/RX/DT                                                | 18          | 15               |                | ST                    |                                                                                     |  |  |  |

| RC7                                                      |             | I/O Digital I/O. |                | 5                     |                                                                                     |  |  |  |

| RX<br>DT                                                 |             |                  | I/O            |                       | USART asynchronous receive.                                                         |  |  |  |

|                                                          | 0.40        | <b>F A</b>       |                |                       | USART synchronous data.                                                             |  |  |  |

| Vss                                                      | 8, 19<br>20 | 5,6              | P              |                       | Ground reference for logic and I/O pins.<br>Positive supply for logic and I/O pins. |  |  |  |

| Vdd                                                      |             | 17               | Р              |                       |                                                                                     |  |  |  |

| TABLE 1-2: PIC16F873A/876A PINOUT DESCRIPTION (CONTINUE |

|---------------------------------------------------------|

|---------------------------------------------------------|

**Note 1:** This buffer is a Schmitt Trigger input when configured as the external interrupt.

2: This buffer is a Schmitt Trigger input when used in Serial Programming mode.

3: This buffer is a Schmitt Trigger input when configured in RC Oscillator mode and a CMOS input otherwise.

# PIC16F87XA

NOTES:

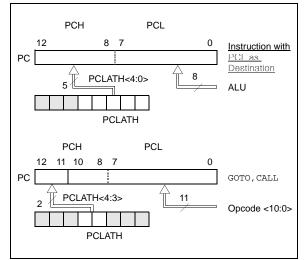

# 2.3 PCL and PCLATH

The Program Counter (PC) is 13 bits wide. The low byte comes from the PCL register which is a readable and writable register. The upper bits (PC<12:8>) are not readable, but are indirectly writable through the PCLATH register. On any Reset, the upper bits of the PC will be cleared. Figure 2-5 shows the two situations for the loading of the PC. The upper example in the figure shows how the PC is loaded on a write to PCL (PCLATH<4:0>  $\rightarrow$  PCH). The lower example in the figure shows how the PC is loaded during a CALL or GOTO instruction (PCLATH<4:3>  $\rightarrow$  PCH).

#### FIGURE 2-5: LOADING OF PC IN DIFFERENT SITUATIONS

## 2.3.1 COMPUTED GOTO

A computed GOTO is accomplished by adding an offset to the program counter (ADDWF PCL). When doing a table read using a computed GOTO method, care should be exercised if the table location crosses a PCL memory boundary (each 256-byte block). Refer to the application note, *AN556, "Implementing a Table Read"* (DS00556).

## 2.3.2 STACK

The PIC16F87XA family has an 8-level deep x 13-bit wide hardware stack. The stack space is not part of either program or data space and the stack pointer is not readable or writable. The PC is PUSHed onto the stack when a CALL instruction is executed, or an interrupt causes a branch. The stack is POP'ed in the event of a RETURN, RETLW or a RETFIE instruction execution. PCLATH is not affected by a PUSH or POP operation.

The stack operates as a circular buffer. This means that after the stack has been PUSHed eight times, the ninth push overwrites the value that was stored from the first push. The tenth push overwrites the second push (and so on).

- **Note 1:** There are no status bits to indicate stack overflow or stack underflow conditions.

- 2: There are no instructions/mnemonics called PUSH or POP. These are actions that occur from the execution of the CALL, RETURN, RETLW and RETFIE instructions or the vectoring to an interrupt address.

# 2.4 Program Memory Paging

All PIC16F87XA devices are capable of addressing a continuous 8K word block of program memory. The CALL and GOTO instructions provide only 11 bits of address to allow branching within any 2K program memory page. When doing a CALL or GOTO instruction, the upper 2 bits of the address are provided by PCLATH<4:3>. When doing a CALL or GOTO instruction, the user must ensure that the page select bits are programmed so that the desired program memory page is addressed. If a return from a CALL instruction (or interrupt) is executed, the entire 13-bit PC is popped off the stack. Therefore, manipulation of the PCLATH<4:3> bits is not required for the RETURN instructions (which POPs the address from the stack).

| Note: | The contents of the PCLATH register are    |

|-------|--------------------------------------------|

|       | unchanged after a RETURN or RETFIE         |

|       | instruction is executed. The user must     |

|       | rewrite the contents of the PCLATH regis-  |

|       | ter for any subsequent subroutine calls or |

|       | GOTO instructions.                         |

Example 2-1 shows the calling of a subroutine in page 1 of the program memory. This example assumes that PCLATH is saved and restored by the Interrupt Service Routine (if interrupts are used).

#### EXAMPLE 2-1: CALL OF A SUBROUTINE IN PAGE 1 FROM PAGE 0

|         | ORG 0x500    |                     |

|---------|--------------|---------------------|

|         | BCF PCLATH,4 |                     |

|         | BSF PCLATH,3 | ;Select page 1      |

|         |              | ; (800h-FFFh)       |

|         | CALL SUB1_P1 | ;Call subroutine in |

|         | :            | ;page 1 (800h-FFFh) |

|         | :            |                     |

|         | ORG 0x900    | ;page 1 (800h-FFFh) |

| SUB1_P1 |              |                     |

|         | :            | ;called subroutine  |

|         |              | ;page 1 (800h-FFFh) |

|         | :            |                     |

|         | RETURN       | ;return to          |

|         |              | ;Call subroutine    |

|         |              | ;in page 0          |

|         |              | ;(000h-7FFh)        |

|         |              |                     |

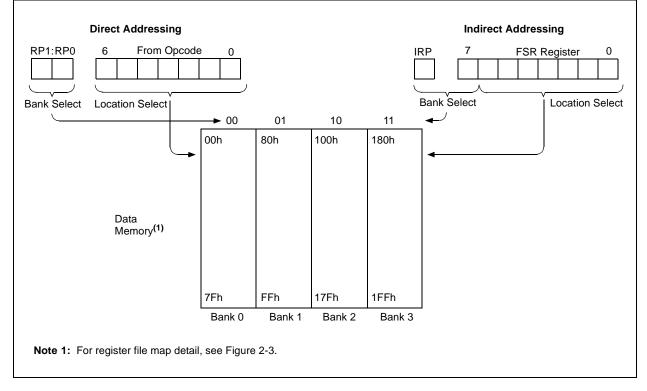

## 2.5 Indirect Addressing, INDF and FSR Registers

The INDF register is not a physical register. Addressing the INDF register will cause indirect addressing.

Indirect addressing is possible by using the INDF register. Any instruction using the INDF register actually accesses the register pointed to by the File Select Register, FSR. Reading the INDF register itself, indirectly (FSR = 0) will read 00h. Writing to the INDF register indirectly results in a no operation (although status bits may be affected). An effective 9-bit address is obtained by concatenating the 8-bit FSR register and the IRP bit (Status<7>) as shown in Figure 2-6. A simple program to clear RAM locations 20h-2Fh using indirect addressing is shown in Example 2-2.

## EXAMPLE 2-2: INDIRECT ADDRESSING

|          | MOVLW | 0x20  | ;initialize pointer  |

|----------|-------|-------|----------------------|

|          | MOVWF | FSR   | ;to RAM              |

| NEXT     | CLRF  | INDF  | clear INDF register; |

|          | INCF  | FSR,F | ;inc pointer         |

|          | BTFSS | FSR,4 | ;all done?           |

|          | GOTO  | NEXT  | ;no clear next       |

| CONTINUE |       |       |                      |

|          | :     |       | ;yes continue        |

| 1        |       |       |                      |

# 4.0 I/O PORTS

Some pins for these I/O ports are multiplexed with an alternate function for the peripheral features on the device. In general, when a peripheral is enabled, that pin may not be used as a general purpose I/O pin.

Additional information on I/O ports may be found in the PIC<sup>®</sup> Mid-Range Reference Manual (DS33023).

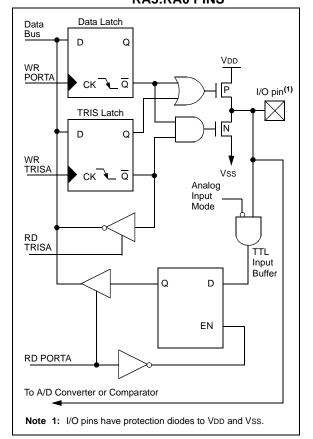

## 4.1 PORTA and the TRISA Register

PORTA is a 6-bit wide, bidirectional port. The corresponding data direction register is TRISA. Setting a TRISA bit (= 1) will make the corresponding PORTA pin an input (i.e., put the corresponding output driver in a High-Impedance mode). Clearing a TRISA bit (= 0) will make the corresponding PORTA pin an output (i.e., put the contents of the output latch on the selected pin).

Reading the PORTA register reads the status of the pins, whereas writing to it will write to the port latch. All write operations are read-modify-write operations. Therefore, a write to a port implies that the port pins are read, the value is modified and then written to the port data latch.

Pin RA4 is multiplexed with the Timer0 module clock input to become the RA4/T0CKI pin. The RA4/T0CKI pin is a Schmitt Trigger input and an open-drain output. All other PORTA pins have TTL input levels and full CMOS output drivers.

Other PORTA pins are multiplexed with analog inputs and the analog VREF input for both the A/D converters and the comparators. The operation of each pin is selected by clearing/setting the appropriate control bits in the ADCON1 and/or CMCON registers.

| Note: | On a Power-on Reset, these pins are con-  |

|-------|-------------------------------------------|

|       | figured as analog inputs and read as '0'. |

|       | The comparators are in the off (digital)  |

|       | state.                                    |

The TRISA register controls the direction of the port pins even when they are being used as analog inputs. The user must ensure the bits in the TRISA register are maintained set when using them as analog inputs.

#### EXAMPLE 4-1: INITIALIZING PORTA

| BCF   | STATUS, |     | ;                       |

|-------|---------|-----|-------------------------|

| BCF   | STATUS, | RP1 | ; Bank0                 |

| CLRF  | PORTA   |     | ; Initialize PORTA by   |

|       |         |     | ; clearing output       |

|       |         |     | ; data latches          |

| BSF   | STATUS, | RP0 | ; Select Bank 1         |

| MOVLW | 0x06    |     | ; Configure all pins    |

| MOVWF | ADCON1  |     | ; as digital inputs     |

| MOVLW | 0xCF    |     | ; Value used to         |

|       |         |     | ; initialize data       |

|       |         |     | ; direction             |

| MOVWF | TRISA   |     | ; Set RA<3:0> as inputs |

|       |         |     | ; RA<5:4> as outputs    |

|       |         |     | ; TRISA<7:6>are always  |

|       |         |     | ; read as '0'.          |

|       |         |     |                         |

BLOCK DIAGRAM OF RA3:RA0 PINS

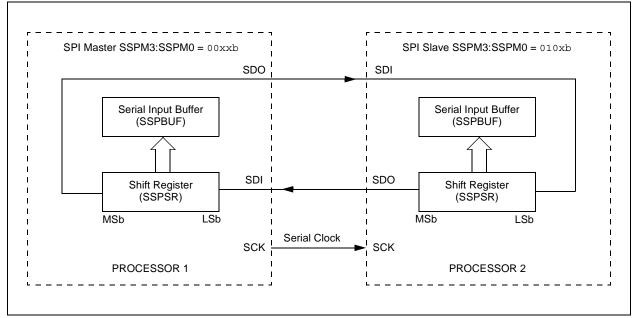

#### 9.3.3 ENABLING SPI I/O

To enable the serial port, SSP Enable bit, SSPEN (SSPCON<5>), must be set. To reset or reconfigure SPI mode, clear the SSPEN bit, re-initialize the SSPCON registers and then set the SSPEN bit. This configures the SDI, SDO, SCK and SS pins as serial port pins. For the pins to behave as the serial port function, some must have their data direction bits (in the TRIS register) appropriately programmed. That is:

- SDI is automatically controlled by the SPI module

- SDO must have TRISC<5> bit cleared

- SCK (Master mode) must have TRISC<3> bit cleared

- SCK (Slave mode) must have TRISC<3> bit set

- SS must have TRISC<4> bit set

Any serial port function that is not desired may be overridden by programming the corresponding data direction (TRIS) register to the opposite value.

## 9.3.4 TYPICAL CONNECTION

Figure 9-2 shows a typical connection between two microcontrollers. The master controller (Processor 1) initiates the data transfer by sending the SCK signal. Data is shifted out of both shift registers on their programmed clock edge and latched on the opposite edge of the clock. Both processors should be programmed to the same Clock Polarity (CKP), then both controllers would send and receive data at the same time. Whether the data is meaningful (or dummy data) depends on the application software. This leads to three scenarios for data transmission:

- Master sends data Slave sends dummy data

- Master sends data Slave sends data

- Master sends dummy data Slave sends data

#### FIGURE 9-2: SPI MASTER/SLAVE CONNECTION

#### 9.3.5 MASTER MODE

The master can initiate the data transfer at any time because it controls the SCK. The master determines when the slave (Processor 2, Figure 9-2) is to broadcast data by the software protocol.

In Master mode, the data is transmitted/received as soon as the SSPBUF register is written to. If the SPI is only going to receive, the SDO output could be disabled (programmed as an input). The SSPSR register will continue to shift in the signal present on the SDI pin at the programmed clock rate. As each byte is received, it will be loaded into the SSPBUF register as if a normal received byte (interrupts and status bits appropriately set). This could be useful in receiver applications as a "Line Activity Monitor" mode.

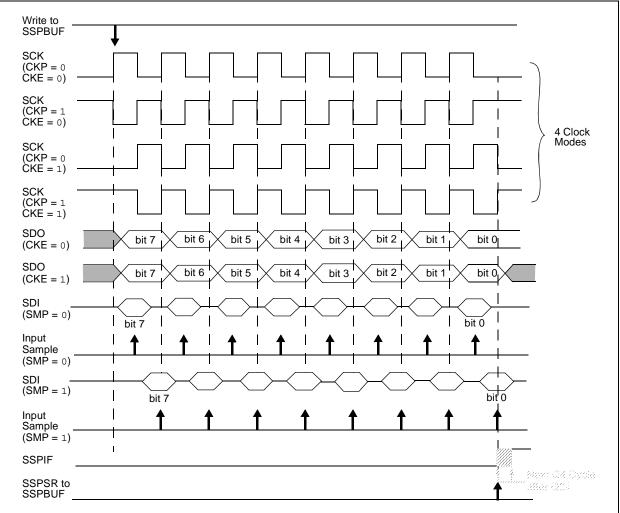

The clock polarity is selected by appropriately programming the CKP bit (SSPCON<4>). This then, would give waveforms for SPI communication as shown in Figure 9-3, Figure 9-5 and Figure 9-6, where the MSB is transmitted first. In Master mode, the SPI clock rate (bit rate) is user programmable to be one of the following:

- Fosc/4 (or Tcy)

- Fosc/16 (or 4 Tcy)

- Fosc/64 (or 16 Tcy)

- Timer2 output/2

This allows a maximum data rate (at 40 MHz) of 10.00 Mbps.

Figure 9-3 shows the waveforms for Master mode. When the CKE bit is set, the SDO data is valid before there is a clock edge on SCK. The change of the input sample is shown based on the state of the SMP bit. The time when the SSPBUF is loaded with the received data is shown.

## FIGURE 9-3: SPI MODE WAVEFORM (MASTER MODE)

|       | R/W-0                  | R/W-0                                                                                                                                            | R/W-0                    | R/W-0          | R/W-0         | R/W-0        | R/W-0        | R/W-0       |  |  |  |  |

|-------|------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------|----------------|---------------|--------------|--------------|-------------|--|--|--|--|

|       | GCEN                   | ACKSTAT                                                                                                                                          | ACKDT                    | ACKEN          | RCEN          | PEN          | RSEN         | SEN         |  |  |  |  |

|       | bit 7                  | 1                                                                                                                                                |                          | I              |               | I            | I            | bit 0       |  |  |  |  |

| bit 7 |                        | eneral Call En                                                                                                                                   |                          | -              | -             |              |              |             |  |  |  |  |

|       |                        | <ul> <li>1 = Enable interrupt when a general call address (0000h) is received in the SSPSR</li> <li>0 = General call address disabled</li> </ul> |                          |                |               |              |              |             |  |  |  |  |

| bit 6 | ACKSTA                 | ACKSTAT: Acknowledge Status bit (Master Transmit mode only)                                                                                      |                          |                |               |              |              |             |  |  |  |  |

|       |                        | <ul> <li>1 = Acknowledge was not received from slave</li> <li>0 = Acknowledge was received from slave</li> </ul>                                 |                          |                |               |              |              |             |  |  |  |  |

| bit 5 | ACKDT: A               | Acknowledge [                                                                                                                                    | Data bit (Mas            | ster Receive   | mode only)    |              |              |             |  |  |  |  |

|       | 1 = Not A<br>0 = Ackno | cknowledge<br>wledge                                                                                                                             |                          |                |               |              |              |             |  |  |  |  |

|       | Note:                  | Value that w the end of a                                                                                                                        |                          | itted when th  | e user initia | tes an Ackr  | nowledge se  | equence at  |  |  |  |  |

| bit 4 | ACKEN:                 | Acknowledge                                                                                                                                      | Sequence E               | nable bit (Ma  | ster Receiv   | e mode on    | ly)          |             |  |  |  |  |

|       | 1 = Initiat<br>Autor   | e Acknowledg<br>matically cleare<br>owledge seque                                                                                                | e sequence<br>d by hardw | e on SDA ar    |               |              |              | T data bit. |  |  |  |  |

| bit 3 | RCEN: R                | eceive Enable                                                                                                                                    | bit (Master i            | mode only)     |               |              |              |             |  |  |  |  |

|       | 1 = Enabl<br>0 = Recei | es Receive mo<br>ve Idle                                                                                                                         | ode for I <sup>2</sup> C |                |               |              |              |             |  |  |  |  |

| bit 2 | PEN: Stop              | o Condition En                                                                                                                                   | able bit (Ma             | ster mode or   | nly)          |              |              |             |  |  |  |  |

|       |                        | e Stop conditio                                                                                                                                  | n on SDA a               | nd SCL pins.   | Automatica    | ally cleared | by hardwa    | re.         |  |  |  |  |

| bit 1 | RSEN: Re               | epeated Start (                                                                                                                                  | Condition Er             | nabled bit (Ma | aster mode    | only)        |              |             |  |  |  |  |

|       |                        | e Repeated Sta<br>ated Start cond                                                                                                                |                          | on SDA and S   | SCL pins. A   | utomatically | y cleared by | hardware.   |  |  |  |  |

| bit 0 | SEN: Star              | t Condition En                                                                                                                                   | abled/Streto             | h Enabled bi   | t             |              |              |             |  |  |  |  |

|       |                        | <u>mode:</u><br>e Start conditic<br>condition Idle                                                                                               | on on SDA a              | nd SCL pins.   | Automatica    | ally cleared | by hardwa    | re.         |  |  |  |  |

|       |                        | <u>node:</u><br>stretching is e<br>stretching is e                                                                                               |                          |                |               |              |              | nabled)     |  |  |  |  |

|       | Legend:                |                                                                                                                                                  |                          |                |               |              |              |             |  |  |  |  |

|       | R = Read               |                                                                                                                                                  |                          | itable bit     | -             |              | bit, read as |             |  |  |  |  |

|       | - n = Valu             | e at POR                                                                                                                                         | '1' = Bit                | is set         | '0' = Bit is  | cleared      | x = Bit is ι | unknown     |  |  |  |  |

**Note:** For bits ACKEN, RCEN, PEN, RSEN, SEN: If the I<sup>2</sup>C module is not in the Idle mode, this bit may not be set (no spooling) and the SSPBUF may not be written (or writes to the SSPBUF are disabled).

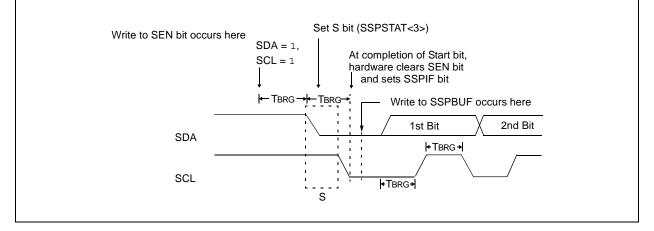

## 9.4.8 I<sup>2</sup>C MASTER MODE START CONDITION TIMING

To initiate a Start condition, the user sets the Start condition enable bit, SEN (SSPCON2<0>). If the SDA and SCL pins are sampled high, the Baud Rate Generator is reloaded with the contents of SSPADD<6:0> and starts its count. If SCL and SDA are both sampled high when the Baud Rate Generator times out (TBRG), the SDA pin is driven low. The action of the SDA being driven low, while SCL is high, is the Start condition and causes the S bit (SSPSTAT<3>) to be set. Following this, the Baud Rate Generator is reloaded with the contents of SSPADD<6:0> and resumes its count. When the Baud Rate Generator times out (TBRG), the SEN bit (SSPCON2<0>) will be automatically cleared by hardware, the Baud Rate Generator is suspended, leaving the SDA line held low and the Start condition is complete.

**Note:** If at the beginning of the Start condition, the SDA and SCL pins are already sampled low, or if during the Start condition, the SCL line is sampled low before the SDA line is driven low, a bus collision occurs, the Bus Collision Interrupt Flag (BCLIF) is set, the Start condition is aborted and the I<sup>2</sup>C module is reset into its Idle state.

## 9.4.8.1 WCOL Status Flag

If the user writes the SSPBUF when a Start sequence is in progress, the WCOL is set and the contents of the buffer are unchanged (the write doesn't occur).

Note: Because queueing of events is not allowed, writing to the lower 5 bits of SSPCON2 is disabled until the Start condition is complete.

# FIGURE 9-19: FIRST START BIT TIMING

## 9.4.10 I<sup>2</sup>C MASTER MODE TRANSMISSION

Transmission of a data byte, a 7-bit address or the other half of a 10-bit address is accomplished by simply writing a value to the SSPBUF register. This action will set the Buffer Full flag bit, BF, and allow the Baud Rate Generator to begin counting and start the next transmission. Each bit of address/data will be shifted out onto the SDA pin after the falling edge of SCL is asserted (see data hold time specification, parameter #106). SCL is held low for one Baud Rate Generator rollover count (TBRG). Data should be valid before SCL is released high (see data setup time specification, parameter #107). When the SCL pin is released high, it is held that way for TBRG. The data on the SDA pin must remain stable for that duration and some hold time after the next falling edge of SCL. After the eighth bit is shifted out (the falling edge of the eighth clock), the BF flag is cleared and the master releases SDA. This allows the slave device being addressed to respond with an ACK bit during the ninth bit time, if an address match occurred or if data was received properly. The status of ACK is written into the ACKDT bit on the falling edge of the ninth clock. If the master receives an Acknowledge, the Acknowledge Status bit, ACKSTAT, is cleared. If not, the bit is set. After the ninth clock, the SSPIF bit is set and the master clock (Baud Rate Generator) is suspended until the next data byte is loaded into the SSPBUF, leaving SCL low and SDA unchanged (Figure 9-21).

After the write to the SSPBUF, each bit of address will be shifted out on the falling edge of SCL, until all seven address bits and the R/W bit are completed. On the falling edge of the eighth clock, the master will deassert the SDA pin, allowing the slave to respond with an Acknowledge. On the falling edge of the ninth clock, the master will sample the SDA pin to see if the address was recognized by a slave. The status of the ACK bit is loaded into the ACKSTAT status bit (SSPCON2<6>). Following the falling edge of the ninth clock transmission of the address, the SSPIF is set, the BF flag is cleared and the Baud Rate Generator is turned off until another write to the SSPBUF takes place, holding SCL low and allowing SDA to float.

## 9.4.10.1 BF Status Flag

In Transmit mode, the BF bit (SSPSTAT<0>) is set when the CPU writes to SSPBUF and is cleared when all eight bits are shifted out.

## 9.4.10.2 WCOL Status Flag

If the user writes the SSPBUF when a transmit is already in progress (i.e., SSPSR is still shifting out a data byte), the WCOL is set and the contents of the buffer are unchanged (the write doesn't occur).

WCOL must be cleared in software.

## 9.4.10.3 ACKSTAT Status Flag

In Transmit mode, the ACKSTAT bit (SSPCON2<6>) is cleared when the slave has sent an Acknowledge  $(\overline{ACK} = 0)$  and is set when the slave does Not Acknowledge  $(\overline{ACK} = 1)$ . A slave sends an Acknowledge when it has recognized its address (including a general call) or when the slave has properly received its data.

## 9.4.11 I<sup>2</sup>C MASTER MODE RECEPTION

Master mode reception is enabled by programming the Receive Enable bit, RCEN (SSPCON2<3>).

Note: The MSSP module must be in an Idle state before the RCEN bit is set or the RCEN bit will be disregarded.

The Baud Rate Generator begins counting and on each rollover, the state of the SCL pin changes (high to low/ low to high) and data is shifted into the SSPSR. After the falling edge of the eighth clock, the receive enable flag is automatically cleared, the contents of the SSPSR are loaded into the SSPBUF, the BF flag bit is set, the SSPIF flag bit is set and the Baud Rate Generator is suspended from counting, holding SCL low. The MSSP is now in Idle state, awaiting the next command. When the buffer is read by the CPU, the BF flag bit is automatically cleared. The user can then send an Acknowledge bit at the end of reception by setting the Acknowledge Sequence Enable bit, ACKEN (SSPCON2<4>).

## 9.4.11.1 BF Status Flag

In receive operation, the BF bit is set when an address or data byte is loaded into SSPBUF from SSPSR. It is cleared when the SSPBUF register is read.

## 9.4.11.2 SSPOV Status Flag

In receive operation, the SSPOV bit is set when 8 bits are received into the SSPSR and the BF flag bit is already set from a previous reception.

#### 9.4.11.3 WCOL Status Flag

If the user writes the SSPBUF when a receive is already in progress (i.e., SSPSR is still shifting in a data byte), the WCOL bit is set and the contents of the buffer are unchanged (the write doesn't occur).

# PIC16F87XA

NOTES:

#### 10.3.2 USART SYNCHRONOUS MASTER RECEPTION

Once Synchronous mode is selected, reception is enabled by setting either enable bit, SREN (RCSTA<5>), or enable bit, CREN (RCSTA<4>). Data is sampled on the RC7/RX/DT pin on the falling edge of the clock. If enable bit SREN is set, then only a single word is received. If enable bit CREN is set, the reception is continuous until CREN is cleared. If both bits are set, CREN takes precedence. After clocking the last bit, the received data in the Receive Shift Register (RSR) is transferred to the RCREG register (if it is empty). When the transfer is complete, interrupt flag bit, RCIF (PIR1<5>), is set. The actual interrupt can be enabled/ disabled by setting/clearing enable bit, RCIE (PIE1<5>). Flag bit RCIF is a read-only bit which is reset by the hardware. In this case, it is reset when the RCREG register has been read and is empty. The RCREG is a double-buffered register (i.e., it is a twodeep FIFO). It is possible for two bytes of data to be received and transferred to the RCREG FIFO and a third byte to begin shifting into the RSR register. On the clocking of the last bit of the third byte, if the RCREG register is still full, then Overrun Error bit, OERR (RCSTA<1>), is set. The word in the RSR will be lost. The RCREG register can be read twice to retrieve the two bytes in the FIFO. Bit OERR has to be cleared in software (by clearing bit CREN). If bit OERR is set, transfers from the RSR to the RCREG are inhibited so it is essential to clear bit OERR if it is set. The ninth receive bit is buffered the same way as the receive

data. Reading the RCREG register will load bit RX9D with a new value, therefore, it is essential for the user to read the RCSTA register before reading RCREG in order not to lose the old RX9D information.

When setting up a Synchronous Master Reception:

- 1. Initialize the SPBRG register for the appropriate baud rate (Section 10.1 "USART Baud Rate Generator (BRG)").

- 2. Enable the synchronous master serial port by setting bits SYNC, SPEN and CSRC.

- 3. Ensure bits CREN and SREN are clear.

- 4. If interrupts are desired, then set enable bit RCIE.

- 5. If 9-bit reception is desired, then set bit RX9.

- 6. If a single reception is required, set bit SREN. For continuous reception, set bit CREN.

- Interrupt flag bit RCIF will be set when reception is complete and an interrupt will be generated if enable bit RCIE was set.

- 8. Read the RCSTA register to get the ninth bit (if enabled) and determine if any error occurred during reception.

- 9. Read the 8-bit received data by reading the RCREG register.

- 10. If any error occurred, clear the error by clearing bit CREN.

- 11. If using interrupts, ensure that GIE and PEIE (bits 7 and 6) of the INTCON register are set.

| ABEE 10-9. REGISTERS ASSOCIATED WITT STRETIKONOOS MASTER RECEPTION |                                                           |                                                                                                     |                                                                                                          |                                                                                                                                                                                                  |                                                                                                                                                                                              |                                                                                                                                                                                                                                                             |                                                                                                                                                                                                                                                      |                                                                                                                                                                                                                                                                               |                                                                                                                                                                                                                                                                                                            |                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |  |

|--------------------------------------------------------------------|-----------------------------------------------------------|-----------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| Name                                                               | Bit 7                                                     | Bit 6                                                                                               | Bit 5                                                                                                    | Bit 4                                                                                                                                                                                            | Bit 4 Bit 3 Bit 2 Bit 1 Bit 0                                                                                                                                                                |                                                                                                                                                                                                                                                             | Bit 1 Bit 0                                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                               | Value on:<br>POR, BOR                                                                                                                                                                                                                                                                                      | Value on<br>all other<br>Resets                                                                                                                                                                                                                                                                                                                                                                        |  |  |  |

| INTCON                                                             | GIE                                                       | PEIE                                                                                                | TMR0IE                                                                                                   | INTE                                                                                                                                                                                             | RBIE                                                                                                                                                                                         | TMR0IF                                                                                                                                                                                                                                                      | INTF                                                                                                                                                                                                                                                 | R0IF                                                                                                                                                                                                                                                                          | 0000 000x                                                                                                                                                                                                                                                                                                  | 0000 000u                                                                                                                                                                                                                                                                                                                                                                                              |  |  |  |

| PIR1                                                               | PSPIF <sup>(1)</sup>                                      | ADIF                                                                                                | RCIF                                                                                                     | TXIF                                                                                                                                                                                             | SSPIF                                                                                                                                                                                        | CCP1IF                                                                                                                                                                                                                                                      | TMR2IF                                                                                                                                                                                                                                               | TMR1IF                                                                                                                                                                                                                                                                        | 0000 0000                                                                                                                                                                                                                                                                                                  | 0000 0000                                                                                                                                                                                                                                                                                                                                                                                              |  |  |  |

| RCSTA                                                              | SPEN                                                      | RX9                                                                                                 | SREN                                                                                                     | CREN                                                                                                                                                                                             |                                                                                                                                                                                              | FERR                                                                                                                                                                                                                                                        | OERR                                                                                                                                                                                                                                                 | RX9D                                                                                                                                                                                                                                                                          | 0000 -00x                                                                                                                                                                                                                                                                                                  | 0000 -00x                                                                                                                                                                                                                                                                                                                                                                                              |  |  |  |

| RCREG                                                              | USART Re                                                  | eceive Re                                                                                           | gister                                                                                                   |                                                                                                                                                                                                  |                                                                                                                                                                                              |                                                                                                                                                                                                                                                             |                                                                                                                                                                                                                                                      |                                                                                                                                                                                                                                                                               | 0000 0000                                                                                                                                                                                                                                                                                                  | 0000 0000                                                                                                                                                                                                                                                                                                                                                                                              |  |  |  |

| PIE1                                                               | PSPIE <sup>(1)</sup>                                      | ADIE                                                                                                | RCIE                                                                                                     | TXIE                                                                                                                                                                                             | SSPIE                                                                                                                                                                                        | CCP1IE                                                                                                                                                                                                                                                      | TMR2IE                                                                                                                                                                                                                                               | TMR1IE                                                                                                                                                                                                                                                                        | 0000 0000                                                                                                                                                                                                                                                                                                  | 0000 0000                                                                                                                                                                                                                                                                                                                                                                                              |  |  |  |

| TXSTA                                                              | CSRC                                                      | TX9                                                                                                 | TXEN                                                                                                     | SYNC                                                                                                                                                                                             |                                                                                                                                                                                              | BRGH                                                                                                                                                                                                                                                        | TRMT                                                                                                                                                                                                                                                 | TX9D                                                                                                                                                                                                                                                                          | 0000 -010                                                                                                                                                                                                                                                                                                  | 0000 -010                                                                                                                                                                                                                                                                                                                                                                                              |  |  |  |

| SPBRG                                                              | Baud Rate                                                 | Generato                                                                                            | or Register                                                                                              | r                                                                                                                                                                                                |                                                                                                                                                                                              |                                                                                                                                                                                                                                                             |                                                                                                                                                                                                                                                      |                                                                                                                                                                                                                                                                               | 0000 0000                                                                                                                                                                                                                                                                                                  | 0000 0000                                                                                                                                                                                                                                                                                                                                                                                              |  |  |  |

|                                                                    | Name<br>INTCON<br>PIR1<br>RCSTA<br>RCREG<br>PIE1<br>TXSTA | NameBit 7INTCONGIEPIR1PSPIF <sup>(1)</sup> RCSTASPENRCREGUSART RePIE1PSPIE <sup>(1)</sup> TXSTACSRC | NameBit 7Bit 6INTCONGIEPEIEPIR1PSPIF(1)ADIFRCSTASPENRX9RCREGUSART Receive RePIE1PSPIE(1)ADIETXSTACSRCTX9 | NameBit 7Bit 6Bit 5INTCONGIEPEIETMR0IEPIR1PSPIF <sup>(1)</sup> ADIFRCIFRCSTASPENRX9SRENRCREGUSART Receive RegisterPIE1PSPIE <sup>(1)</sup> ADIEPIE1PSPIE <sup>(1)</sup> ADIERCIETXSTACSRCTX9TXEN | NameBit 7Bit 6Bit 5Bit 4INTCONGIEPEIETMROIEINTEPIR1PSPIF <sup>(1)</sup> ADIFRCIFTXIFRCSTASPENRX9SRENCRENRCREGUSART Receive RegisterFIE1PSPIE <sup>(1)</sup> ADIERCIETXIETXSTACSRCTX9TXENSYNC | NameBit 7Bit 6Bit 5Bit 4Bit 3INTCONGIEPEIETMROIEINTERBIEPIR1PSPIF <sup>(1)</sup> ADIFRCIFTXIFSSPIFRCSTASPENRX9SRENCREN—RCREGUSART Receive RegisterFIE1PSPIE <sup>(1)</sup> ADIERCIETXIESSPIEPIE1PSPIE <sup>(1)</sup> ADIERCIETXIESSPIETXSTACSRCTX9TXENSYNC— | NameBit 7Bit 6Bit 5Bit 4Bit 3Bit 2INTCONGIEPEIETMR0IEINTERBIETMR0IFPIR1PSPIF <sup>(1)</sup> ADIFRCIFTXIFSSPIFCCP1IFRCSTASPENRX9SRENCREN—FERRRCREGUSART Receive RegisterFFFFPIE1PSPIE <sup>(1)</sup> ADIERCIETXIESSPIECCP1IETXSTACSRCTX9TXENSYNC—BRGH | NameBit 7Bit 6Bit 5Bit 4Bit 3Bit 2Bit 1INTCONGIEPEIETMROIEINTERBIETMROIFINTFPIR1PSPIF <sup>(1)</sup> ADIFRCIFTXIFSSPIFCCP1IFTMR2IFRCSTASPENRX9SRENCREN—FERROERRRCREGUSART Receive RegisterFIE1PSPIE <sup>(1)</sup> ADIERCIETXIESSPIECCP1IETMR2IETXSTACSRCTX9TXENSYNC—BRGHTRMT | NameBit 7Bit 6Bit 5Bit 4Bit 3Bit 2Bit 1Bit 0INTCONGIEPEIETMROIEINTERBIETMROIFINTFROIFPIR1PSPIF <sup>(1)</sup> ADIFRCIFTXIFSSPIFCCP1IFTMR2IFTMR1IFRCSTASPENRX9SRENCREN—FERROERRRX9DRCREGUSART Receive RegisterFIE1PSPIE <sup>(1)</sup> ADIERCIETXIESSPIECCP1IETMR2IETMR1IETXSTACSRCTX9TXENSYNC—BRGHTRMTTX9D | NameBit 7Bit 6Bit 5Bit 4Bit 3Bit 2Bit 1Bit 0Value on:<br>POR, BORINTCONGIEPEIETMROIEINTERBIETMROIFINTFROIF0000000xPIR1PSPIF <sup>(1)</sup> ADIFRCIFTXIFSSPIFCCP1IFTMR2IFTMR1IF00000000RCSTASPENRX9SRENCREN—FERROERRRX9D0000-00xRCREGUSART Receive RegisterSYPIECCP1IETMR2IETMR1IE00000000PIE1PSPIE <sup>(1)</sup> ADIERCIETXIESSPIECCP1IETMR2IETMR1IE00000000TXSTACSRCTX9TXENSYNC—BRGHTRMTTX9D0000-011 |  |  |  |

## TABLE 10-9: REGISTERS ASSOCIATED WITH SYNCHRONOUS MASTER RECEPTION

Legend: x = unknown, - = unimplemented, read as '0'. Shaded cells are not used for synchronous master reception.

Note 1: Bits PSPIE and PSPIF are reserved on 28-pin devices; always maintain these bits clear.

## 11.5 A/D Operation During Sleep

The A/D module can operate during Sleep mode. This requires that the A/D clock source be set to RC (ADCS1:ADCS0 = 11). When the RC clock source is selected, the A/D module waits one instruction cycle before starting the conversion. This allows the SLEEP instruction to be executed which eliminates all digital switching noise from the conversion. When the conversion is completed, the GO/DONE bit will be cleared and the result loaded into the ADRES register. If the A/D interrupt is enabled, the device will wake-up from Sleep. If the A/D interrupt is not enabled, the ADON bit will remain set.

When the A/D clock source is another clock option (not RC), a SLEEP instruction will cause the present conversion to be aborted and the A/D module to be turned off, though the ADON bit will remain set.

Turning off the A/D places the A/D module in its lowest current consumption state.

| Note: | For the A/D module to operate in Sleep,   |

|-------|-------------------------------------------|

|       | the A/D clock source must be set to RC    |

|       | (ADCS1:ADCS0 = 11). To allow the con-     |

|       | version to occur during Sleep, ensure the |

|       | SLEEP instruction immediately follows the |

|       | instruction that sets the GO/DONE bit.    |

## 11.6 Effects of a Reset

A device Reset forces all registers to their Reset state. This forces the A/D module to be turned off and any conversion is aborted. All A/D input pins are configured as analog inputs.

The value that is in the ADRESH:ADRESL registers is not modified for a Power-on Reset. The ADRESH:ADRESL registers will contain unknown data after a Power-on Reset.

| Address               | Name   | Bit 7                | Bit 6      | Bit 5                                    | Bit 4                                               | Bit 3 | Bit 2   | Bit 1  | Bit 0  | Value<br>POR, |      |      | e on<br>, WDT |

|-----------------------|--------|----------------------|------------|------------------------------------------|-----------------------------------------------------|-------|---------|--------|--------|---------------|------|------|---------------|

| 0Bh,8Bh,<br>10Bh,18Bh | INTCON | GIE                  | PEIE       | TMR0IE                                   | INTE                                                | RBIE  | TMR0IF  | INTF   | RBIF   | 0000          | 000x | 0000 | 000u          |

| 0Ch                   | PIR1   | PSPIF <sup>(1)</sup> | ADIF       | RCIF                                     | TXIF                                                | SSPIF | CCP1IF  | TMR2IF | TMR1IF | 0000          | 0000 | 0000 | 0000          |

| 8Ch                   | PIE1   | PSPIE <sup>(1)</sup> | ADIE       | RCIE                                     | TXIE                                                | SSPIE | CCP1IE  | TMR2IE | TMR1IE | 0000          | 0000 | 0000 | 0000          |

| 1Eh                   | ADRESH | A/D Resu             | lt Registe | r High Byte                              | e                                                   |       | xxxx    | xxxx   | uuuu   | uuuu          |      |      |               |

| 9Eh                   | ADRESL | A/D Resu             | lt Registe | r Low Byte                               | ;                                                   |       |         |        |        | xxxx          | xxxx | uuuu | uuuu          |

| 1Fh                   | ADCON0 | ADCS1                | ADCS0      | CHS2                                     | CHS1                                                | CHS0  | GO/DONE | _      | ADON   | 0000          | 00-0 | 0000 | 00-0          |

| 9Fh                   | ADCON1 | ADFM                 | ADCS2      | —                                        | _                                                   | PCFG3 | PCFG2   | PCFG1  | PCFG0  | 00            | 0000 | 00   | 0000          |

| 85h                   | TRISA  | —                    | _          | PORTA D                                  | PORTA Data Direction Register                       |       |         |        |        |               |      | 11   | 1111          |

| 05h                   | PORTA  | —                    | _          | PORTA D                                  | PORTA Data Latch when written: PORTA pins when read |       |         |        |        |               |      | 0u   | 0000          |

| 89h <sup>(1)</sup>    | TRISE  | IBF                  | OBF        | IBOV PSPMODE — PORTE Data Direction bits |                                                     |       |         |        |        |               | -111 | 0000 | -111          |

| 09h <sup>(1)</sup>    | PORTE  |                      | _          | _                                        | _                                                   | _     | RE2     | RE1    | RE0    |               | -xxx |      | -uuu          |

TABLE 11-2: REGISTERS/BITS ASSOCIATED WITH A/D

Legend: x = unknown, u = unchanged, - = unimplemented, read as '0'. Shaded cells are not used for A/D conversion.

Note 1: These registers are not available on 28-pin devices.

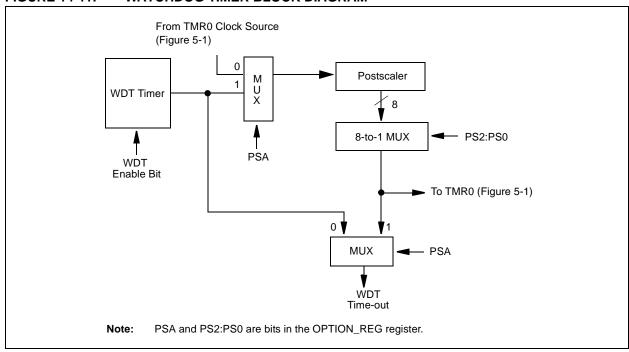

## 14.13 Watchdog Timer (WDT)

The Watchdog Timer is a free running, on-chip RC oscillator which does not require any external components. This RC oscillator is separate from the RC oscillator of the OSC1/CLKI pin. That means that the WDT will run even if the clock on the OSC1/CLKI and OSC2/CLKO pins of the device has been stopped, for example, by execution of a SLEEP instruction.

During normal operation, a WDT time-out generates a device Reset (Watchdog Timer Reset). If the device is in Sleep mode, a WDT time-out causes the device to wake-up and continue with normal operation (Watchdog Timer Wake-up). The TO bit in the Status register will be cleared upon a Watchdog Timer time-out.

The WDT can be permanently disabled by clearing configuration bit, WDTE (Section 14.1 "Configuration Bits").

WDT time-out period values may be found in **Section 17.0** "**Electrical Characteristics**" under parameter #31. Values for the WDT prescaler (actually a postscaler but shared with the Timer0 prescaler) may be assigned using the OPTION\_REG register.

- **Note 1:** The CLRWDT and SLEEP instructions clear the WDT and the postscaler, if assigned to the WDT and prevent it from timing out and generating a device Reset condition.

- 2: When a CLRWDT instruction is executed and the prescaler is assigned to the WDT, the prescaler count will be cleared but the prescaler assignment is not changed.

## FIGURE 14-11: WATCHDOG TIMER BLOCK DIAGRAM

#### TABLE 14-7: SUMMARY OF WATCHDOG TIMER REGISTERS

| Address   | Name         | Bit 7 | Bit 6                | Bit 5 | Bit 4 | Bit 3                | Bit 2 | Bit 1 | Bit 0 |

|-----------|--------------|-------|----------------------|-------|-------|----------------------|-------|-------|-------|

| 2007h     | Config. bits | (1)   | BODEN <sup>(1)</sup> | CP1   | CP0   | PWRTE <sup>(1)</sup> | WDTE  | Fosc1 | Fosc0 |

| 81h, 181h | OPTION_REG   | RBPU  | INTEDG               | TOCS  | TOSE  | PSA                  | PS2   | PS1   | PS0   |

Legend: Shaded cells are not used by the Watchdog Timer.

Note 1: See Register 14-1 for operation of these bits.

# PIC16F87XA

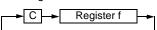

| RLF              | Rotate Left f through Carry                                                                                                                                                                                       |

|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [ <i>label</i> ] RLF f,d                                                                                                                                                                                          |

| Operands:        | $\begin{array}{l} 0\leq f\leq 127\\ d\in [0,1] \end{array}$                                                                                                                                                       |

| Operation:       | See description below                                                                                                                                                                                             |

| Status Affected: | С                                                                                                                                                                                                                 |

| Description:     | The contents of register 'f' are<br>rotated one bit to the left through the<br>Carry flag. If 'd' is '0', the result is<br>placed in the W register. If 'd' is '1',<br>the result is stored back in register 'f'. |

| Syntax:          | [label] SLEEP                                                                                                                                                                                                                          |

|------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Operands:        | None                                                                                                                                                                                                                                   |