Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                                            |

|----------------------------|----------------------------------------------------------------------------|

| Product Status             | Active                                                                     |

| Core Processor             | PIC                                                                        |

| Core Size                  | 8-Bit                                                                      |

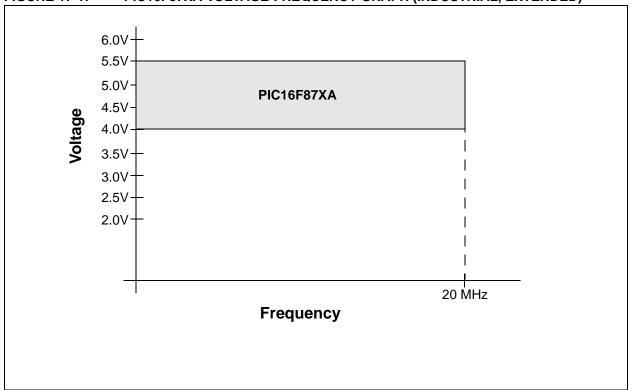

| Speed                      | 20MHz                                                                      |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                          |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                      |

| Number of I/O              | 22                                                                         |

| Program Memory Size        | 14KB (8K x 14)                                                             |

| Program Memory Type        | FLASH                                                                      |

| EEPROM Size                | 256 x 8                                                                    |

| RAM Size                   | 368 x 8                                                                    |

| Voltage - Supply (Vcc/Vdd) | 4V ~ 5.5V                                                                  |

| Data Converters            | A/D 5x10b                                                                  |

| Oscillator Type            | External                                                                   |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                         |

| Mounting Type              | Surface Mount                                                              |

| Package / Case             | 28-SSOP (0.209", 5.30mm Width)                                             |

| Supplier Device Package    | 28-SSOP                                                                    |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16f876at-e-ss |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

### **Table of Contents**

| 1.0   | Device Overview                                                             | 5    |

|-------|-----------------------------------------------------------------------------|------|

| 2.0   | Memory Organization                                                         | . 15 |

| 3.0   | Data EEPROM and Flash Program Memory                                        | . 33 |

| 4.0   | I/O Ports                                                                   | . 41 |

| 5.0   | Timer0 Module                                                               | . 53 |

| 6.0   | Timer1 Module                                                               | . 57 |

| 7.0   | Timer2 Module                                                               | . 61 |

| 8.0   | Capture/Compare/PWM Modules                                                 | . 63 |

| 9.0   | Master Synchronous Serial Port (MSSP) Module                                | . 71 |

| 10.0  | Addressable Universal Synchronous Asynchronous Receiver Transmitter (USART) | 111  |

| 11.0  | Analog-to-Digital Converter (A/D) Module                                    | 127  |

| 12.0  | Comparator Module                                                           | 135  |

| 13.0  | Comparator Voltage Reference Module                                         | 141  |

| 14.0  | Special Features of the CPU                                                 | 143  |

| 15.0  | Instruction Set Summary                                                     | 159  |

| 16.0  | Development Support                                                         | 167  |

| 17.0  | Electrical Characteristics                                                  | 173  |

| 18.0  | DC and AC Characteristics Graphs and Tables                                 | 197  |

| 19.0  | Packaging Information                                                       | 209  |

| Appe  | ndix A: Revision History                                                    | 219  |

|       | ndix B: Device Differences                                                  |      |

| Appe  | ndix C: Conversion Considerations                                           | 220  |

| Index |                                                                             | 221  |

| On-Li | ne Support                                                                  | 229  |

| Syste | ems Information and Upgrade Hot Line                                        | 229  |

| Read  | er Response                                                                 | 230  |

| PIC1  | 6F87XA Product Identification System                                        | 231  |

### TO OUR VALUED CUSTOMERS

It is our intention to provide our valued customers with the best documentation possible to ensure successful use of your Microchip products. To this end, we will continue to improve our publications to better suit your needs. Our publications will be refined and enhanced as new volumes and updates are introduced.

If you have any questions or comments regarding this publication, please contact the Marketing Communications Department via E-mail at **docerrors@mail.microchip.com** or fax the **Reader Response Form** in the back of this data sheet to (480) 792-4150. We welcome your feedback.

### Most Current Data Sheet

To obtain the most up-to-date version of this data sheet, please register at our Worldwide Web site at:

http://www.microchip.com

You can determine the version of a data sheet by examining its literature number found on the bottom outside corner of any page. The last character of the literature number is the version number, (e.g., DS30000A is version A of document DS30000).

#### **Errata**

An errata sheet, describing minor operational differences from the data sheet and recommended workarounds, may exist for current devices. As device/documentation issues become known to us, we will publish an errata sheet. The errata will specify the revision of silicon and revision of document to which it applies.

To determine if an errata sheet exists for a particular device, please check with one of the following:

- Microchip's Worldwide Web site; http://www.microchip.com

- Your local Microchip sales office (see last page)

- The Microchip Corporate Literature Center; U.S. FAX: (480) 792-7277

When contacting a sales office or the literature center, please specify which device, revision of silicon and data sheet (include literature number) you are using.

### **Customer Notification System**

Register on our Web site at www.microchip.com/cn to receive the most current information on all of our products.

**TABLE 1-3:** PIC16F874A/877A PINOUT DESCRIPTION (CONTINUED)

| Pin Name                                 | PDIP<br>Pin# | PLCC<br>Pin# | TQFP<br>Pin# | QFN<br>Pin# | I/O/P<br>Type   | Buffer<br>Type | Description                                                                         |

|------------------------------------------|--------------|--------------|--------------|-------------|-----------------|----------------|-------------------------------------------------------------------------------------|

|                                          |              |              |              |             |                 |                | PORTC is a bidirectional I/O port.                                                  |

| RC0/T1OSO/T1CKI<br>RC0<br>T1OSO<br>T1CKI | 15           | 16           | 32           | 34          | I/O<br>O<br>I   | ST             | Digital I/O.<br>Timer1 oscillator output.<br>Timer1 external clock input.           |

| RC1/T1OSI/CCP2<br>RC1<br>T1OSI<br>CCP2   | 16           | 18           | 35           | 35          | I/O<br>I<br>I/O | ST             | Digital I/O. Timer1 oscillator input. Capture2 input, Compare2 output, PWM2 output. |

| RC2/CCP1<br>RC2<br>CCP1                  | 17           | 19           | 36           | 36          | I/O<br>I/O      | ST             | Digital I/O. Capture1 input, Compare1 output, PWM1 output.                          |

| RC3/SCK/SCL<br>RC3<br>SCK                | 18           | 20           | 37           | 37          | I/O<br>I/O      | ST             | Digital I/O. Synchronous serial clock input/output for SPI mode.                    |

| SCL                                      |              |              |              |             | I/O             |                | Synchronous serial clock input/output for I <sup>2</sup> C mode.                    |

| RC4/SDI/SDA<br>RC4<br>SDI<br>SDA         | 23           | 25           | 42           | 42          | I/O<br>I<br>I/O | ST             | Digital I/O.<br>SPI data in.<br>I <sup>2</sup> C data I/O.                          |

| RC5/SDO<br>RC5<br>SDO                    | 24           | 26           | 43           | 43          | I/O<br>O        | ST             | Digital I/O.<br>SPI data out.                                                       |

| RC6/TX/CK<br>RC6<br>TX<br>CK             | 25           | 27           | 44           | 44          | I/O<br>O<br>I/O | ST             | Digital I/O. USART asynchronous transmit. USART1 synchronous clock.                 |

| RC7/RX/DT<br>RC7<br>RX<br>DT             | 26           | 29           | 1            | 1           | I/O<br>I<br>I/O | ST             | Digital I/O. USART asynchronous receive. USART synchronous data.                    |

Legend:

I = input

O = output

I/O = input/output

P = power

— = Not used

TTL = TTL input ST = Schmitt Trigger input

Note 1: This buffer is a Schmitt Trigger input when configured as the external interrupt.

This buffer is a Schmitt Trigger input when used in Serial Programming mode.

This buffer is a Schmitt Trigger input when configured in RC Oscillator mode and a CMOS input otherwise.

**NOTES:**

**TABLE 4-3: PORTB FUNCTIONS**

| Name                   | Bit#  | Buffer                | Function                                                                                                                                       |

|------------------------|-------|-----------------------|------------------------------------------------------------------------------------------------------------------------------------------------|

| RB0/INT                | bit 0 | TTL/ST <sup>(1)</sup> | Input/output pin or external interrupt input. Internal software programmable weak pull-up.                                                     |

| RB1                    | bit 1 | TTL                   | Input/output pin. Internal software programmable weak pull-up.                                                                                 |

| RB2                    | bit 2 | TTL                   | Input/output pin. Internal software programmable weak pull-up.                                                                                 |

| RB3/PGM <sup>(3)</sup> | bit 3 | TTL                   | Input/output pin or programming pin in LVP mode. Internal software programmable weak pull-up.                                                  |

| RB4                    | bit 4 | TTL                   | Input/output pin (with interrupt-on-change). Internal software programmable weak pull-up.                                                      |

| RB5                    | bit 5 | TTL                   | Input/output pin (with interrupt-on-change). Internal software programmable weak pull-up.                                                      |

| RB6/PGC                | bit 6 | TTL/ST <sup>(2)</sup> | Input/output pin (with interrupt-on-change) or in-circuit debugger pin. Internal software programmable weak pull-up. Serial programming clock. |

| RB7/PGD                | bit 7 | TTL/ST <sup>(2)</sup> | Input/output pin (with interrupt-on-change) or in-circuit debugger pin. Internal software programmable weak pull-up. Serial programming data.  |

**Legend:** TTL = TTL input, ST = Schmitt Trigger input

- **Note 1:** This buffer is a Schmitt Trigger input when configured as the external interrupt.

- 2: This buffer is a Schmitt Trigger input when used in Serial Programming mode or in-circuit debugger.

- 3: Low-Voltage ICSP Programming (LVP) is enabled by default which disables the RB3 I/O function. LVP must be disabled to enable RB3 as an I/O pin and allow maximum compatibility to the other 28-pin and 40-pin mid-range devices.

TABLE 4-4: SUMMARY OF REGISTERS ASSOCIATED WITH PORTB

| Address   | Name       | Bit 7 | Bit 6                        | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 | Value on:<br>POR, BOR |      | Valu<br>all o<br>Res | ther |

|-----------|------------|-------|------------------------------|-------|-------|-------|-------|-------|-------|-----------------------|------|----------------------|------|

| 06h, 106h | PORTB      | RB7   | RB6                          | RB5   | RB4   | RB3   | RB2   | RB1   | RB0   | xxxx                  | xxxx | uuuu                 | uuuu |

| 86h, 186h | TRISB      | PORTB | ORTB Data Direction Register |       |       |       |       |       |       | 1111                  | 1111 | 1111                 | 1111 |

| 81h, 181h | OPTION_REG | RBPU  | INTEDG                       | T0CS  | T0SE  | PSA   | PS2   | PS1   | PS0   | 1111                  | 1111 | 1111                 | 1111 |

**Legend:** x = unknown, u = unchanged. Shaded cells are not used by PORTB.

TABLE 4-5: PORTC FUNCTIONS

| Name            | Bit#  | Buffer Type | Function                                                                                        |

|-----------------|-------|-------------|-------------------------------------------------------------------------------------------------|

| RC0/T1OSO/T1CKI | bit 0 | ST          | Input/output port pin or Timer1 oscillator output/Timer1 clock input.                           |

| RC1/T1OSI/CCP2  | bit 1 | ST          | Input/output port pin or Timer1 oscillator input or Capture2 input/Compare2 output/PWM2 output. |

| RC2/CCP1        | bit 2 | ST          | Input/output port pin or Capture1 input/Compare1 output/PWM1 output.                            |

| RC3/SCK/SCL     | bit 3 | ST          | RC3 can also be the synchronous serial clock for both SPI and I <sup>2</sup> C modes.           |

| RC4/SDI/SDA     | bit 4 | ST          | RC4 can also be the SPI data in (SPI mode) or data I/O (I <sup>2</sup> C mode).                 |

| RC5/SDO         | bit 5 | ST          | Input/output port pin or Synchronous Serial Port data output.                                   |

| RC6/TX/CK       | bit 6 | ST          | Input/output port pin or USART asynchronous transmit or synchronous clock.                      |

| RC7/RX/DT       | bit 7 | ST          | Input/output port pin or USART asynchronous receive or synchronous data.                        |

**Legend:** ST = Schmitt Trigger input

TABLE 4-6: SUMMARY OF REGISTERS ASSOCIATED WITH PORTC

| Address | Name  | Bit 7 | Bit 6                      | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 | Value on:<br>POR, BOR | Value on<br>all other<br>Resets |

|---------|-------|-------|----------------------------|-------|-------|-------|-------|-------|-------|-----------------------|---------------------------------|

| 07h     | PORTC | RC7   | RC6                        | RC5   | RC4   | RC3   | RC2   | RC1   | RC0   | xxxx xxxx             | uuuu uuuu                       |

| 87h     | TRISC | PORTC | TC Data Direction Register |       |       |       |       |       |       | 1111 1111             | 1111 1111                       |

**Legend:** x = unknown, u = unchanged

**NOTES:**

### 9.3.1 REGISTERS

The MSSP module has four registers for SPI mode operation. These are:

- MSSP Control Register (SSPCON)

- MSSP Status Register (SSPSTAT)

- Serial Receive/Transmit Buffer Register (SSPBUF)

- MSSP Shift Register (SSPSR) Not directly accessible

SSPCON and SSPSTAT are the control and status registers in SPI mode operation. The SSPCON register is readable and writable. The lower six bits of the SSPSTAT are read-only. The upper two bits of the SSPSTAT are read/write.

SSPSR is the shift register used for shifting data in or out. SSPBUF is the buffer register to which data bytes are written to or read from.

In receive operations, SSPSR and SSPBUF together create a double-buffered receiver. When SSPSR receives a complete byte, it is transferred to SSPBUF and the SSPIF interrupt is set.

During transmission, the SSPBUF is not doublebuffered. A write to SSPBUF will write to both SSPBUF and SSPSR.

### REGISTER 9-1: SSPSTAT: MSSP STATUS REGISTER (SPI MODE) (ADDRESS 94h)

| R/W-0 | R/W-0 | R-0 | R-0 | R-0 | R-0 | R-0 | R-0   |

|-------|-------|-----|-----|-----|-----|-----|-------|

| SMP   | CKE   | D/A | Р   | S   | R/W | UA  | BF    |

| bit 7 |       |     |     |     |     |     | bit 0 |

bit 7 SMP: Sample bit

SPI Master mode:

1 = Input data sampled at end of data output time

0 = Input data sampled at middle of data output time

SPI Slave mode:

SMP must be cleared when SPI is used in Slave mode.

bit 6 CKE: SPI Clock Select bit

1 = Transmit occurs on transition from active to Idle clock state

0 = Transmit occurs on transition from Idle to active clock state

Note: Polarity of clock state is set by the CKP bit (SSPCON1<4>).

bit 5 **D/A:** Data/Address bit

Used in I<sup>2</sup>C mode only.

bit 4 **P:** Stop bit

Used in I<sup>2</sup>C mode only. This bit is cleared when the MSSP module is disabled, SSPEN is cleared.

bit 3 S: Start bit

Used in I<sup>2</sup>C mode only.

bit 2 **R/W**: Read/Write bit information

Used in I<sup>2</sup>C mode only.

bit 1 UA: Update Address bit

Used in I<sup>2</sup>C mode only.

bit 0 **BF:** Buffer Full Status bit (Receive mode only)

1 = Receive complete, SSPBUF is full

0 = Receive not complete, SSPBUF is empty

| Ī | Legend:            |                  |                      |                    |

|---|--------------------|------------------|----------------------|--------------------|

|   | R = Readable bit   | W = Writable bit | U = Unimplemented b  | oit, read as '0'   |

|   | - n = Value at POR | '1' = Bit is set | '0' = Bit is cleared | x = Bit is unknown |

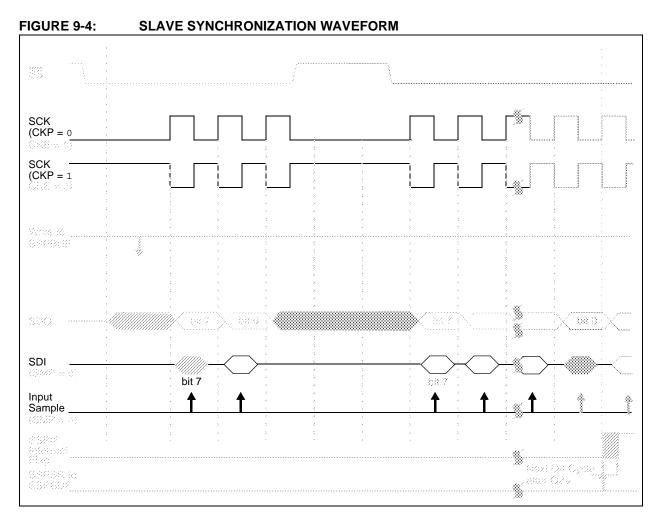

#### 9.3.6 SLAVE MODE

In Slave mode, the data is transmitted and received as the external clock pulses appear on SCK. When the last bit is latched, the SSPIF interrupt flag bit is set.

While in Slave mode, the external clock is supplied by the external clock source on the SCK pin. This external clock must meet the minimum high and low times as specified in the electrical specifications.

While in Sleep mode, the slave can transmit/receive data. When a byte is received, the device will wake-up from Sleep.

## 9.3.7 SLAVE SELECT SYNCHRONIZATION

The  $\overline{SS}$  pin allows a Synchronous Slave mode. The SPI must be in Slave mode with  $\overline{SS}$  pin control enabled (SSPCON<3:0> = 04h). The pin must not be driven low for the  $\overline{SS}$  pin to function as an input. The data latch must be high. When the  $\overline{SS}$  pin is low, transmission and reception are enabled and the SDO pin is driven. When

the  $\overline{SS}$  pin goes high, the SDO pin is no longer driven even if in the middle of a transmitted byte and becomes a floating output. External pull-up/pull-down resistors may be desirable, depending on the application.

- Note 1: When the SPI is in Slave mode with  $\overline{SS}$  pin control enabled (SSPCON<3:0> = 0100), the SPI module will reset if the  $\overline{SS}$  pin is set to VDD.

- 2: If the SPI is used in Slave Mode with CKE set, then the SS pin control must be enabled.

When the SPI module resets, the bit counter is forced to '0'. This can be done by either forcing the SS pin to a high level or clearing the SSPEN bit.

To emulate two-wire communication, the SDO pin can be connected to the SDI pin. When the SPI needs to operate as a receiver, the SDO pin can be configured as an input. This disables transmissions from the SDO. The SDI can always be left as an input (SDI function) since it cannot create a bus conflict.

## 9.4.6.1 I<sup>2</sup>C Master Mode Operation

The master device generates all of the serial clock pulses and the Start and Stop conditions. A transfer is ended with a Stop condition or with a Repeated Start condition. Since the Repeated Start condition is also the beginning of the next serial transfer, the I<sup>2</sup>C bus will not be released.

In Master Transmitter mode, serial data is output through SDA while SCL outputs the serial clock. The first byte transmitted contains the slave <u>address</u> of the receiving device (7 bits) and the Read/Write (R/W) bit. In this case, the R/W bit will be logic '0'. Serial data is transmitted 8 bits at a time. After each byte is transmitted, an Acknowledge bit is received. Start and Stop conditions are output to indicate the beginning and the end of a serial transfer.

In Master Receive mode, the first byte transmitted contains the slave address of the transmitting device (7 bits) and the R/W bit. In this case, the R/W bit will be logic '1'. Thus, the first byte transmitted is a 7-bit slave address followed by a '1' to indicate the receive bit. Serial data is received via SDA while SCL outputs the serial clock. Serial data is received 8 bits at a time. After each byte is received, an Acknowledge bit is transmitted. Start and Stop conditions indicate the beginning and end of transmission.

The baud rate generator used for the SPI mode operation is used to set the SCL clock frequency for either 100 kHz, 400 kHz or 1 MHz I<sup>2</sup>C operation. See **Section 9.4.7 "Baud Rate Generator"** for more detail.

A typical transmit sequence would go as follows:

- 1. The user generates a Start condition by setting the Start Enable bit, SEN (SSPCON2<0>).

- SSPIF is set. The MSSP module will wait the required Start time before any other operation takes place.

- 3. The user loads the SSPBUF with the slave address to transmit.

- Address is shifted out the SDA pin until all 8 bits are transmitted.

- The MSSP module shifts in the ACK bit from the slave device and writes its value into the SSPCON2 register (SSPCON2<6>).

- The MSSP module generates an interrupt at the end of the ninth clock cycle by setting the SSPIF bit.

- The user loads the SSPBUF with eight bits of data.

- Data is shifted out the SDA pin until all 8 bits are transmitted.

- The MSSP module shifts in the ACK bit from the slave device and writes its value into the SSPCON2 register (SSPCON2<6>).

- The MSSP module generates an interrupt at the end of the ninth clock cycle by setting the SSPIF bit.

- 11. The user generates a Stop condition by setting the Stop Enable bit, PEN (SSPCON2<2>).

- Interrupt is generated once the Stop condition is complete.

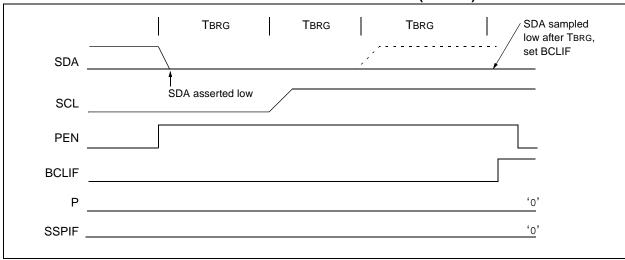

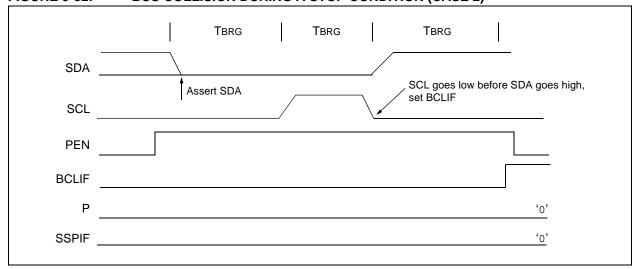

## 9.4.17.3 Bus Collision During a Stop Condition

Bus collision occurs during a Stop condition if:

- After the SDA pin has been deasserted and allowed to float high, SDA is sampled low after the BRG has timed out.

- b) After the SCL pin is deasserted, SCL is sampled low before SDA goes high.

The Stop condition begins with SDA asserted low. When SDA is sampled low, the SCL pin is allowed to float. When the pin is sampled high (clock arbitration), the Baud Rate Generator is loaded with SSPADD<6:0> and counts down to 0. After the BRG times out, SDA is sampled. If SDA is sampled low, a bus collision has occurred. This is due to another master attempting to drive a data '0' (Figure 9-31). If the SCL pin is sampled low before SDA is allowed to float high, a bus collision occurs. This is another case of another master attempting to drive a data '0' (Figure 9-32).

FIGURE 9-31: BUS COLLISION DURING A STOP CONDITION (CASE 1)

FIGURE 9-32: BUS COLLISION DURING A STOP CONDITION (CASE 2)

## REGISTER 11-2: ADCON1 REGISTER (ADDRESS 9Fh)

| R/W-0 | R/W-0 | U-0 | U-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 |

|-------|-------|-----|-----|-------|-------|-------|-------|

| ADFM  | ADCS2 |     | 1   | PCFG3 | PCFG2 | PCFG1 | PCFG0 |

bit 7 bit 0

bit 7 ADFM: A/D Result Format Select bit

1 = Right justified. Six (6) Most Significant bits of ADRESH are read as '0'.

0 = Left justified. Six (6) Least Significant bits of ADRESL are read as '0'.

bit 6 ADCS2: A/D Conversion Clock Select bit (ADCON1 bits in shaded area and in **bold**)

| ADCON1<br><adcs2></adcs2> | ADCON0<br><adcs1:adcs0></adcs1:adcs0> | Clock Conversion                                        |

|---------------------------|---------------------------------------|---------------------------------------------------------|

| 0                         | 0.0                                   | Fosc/2                                                  |

| 0                         | 01                                    | Fosc/8                                                  |

| 0                         | 10                                    | Fosc/32                                                 |

| 0                         | 11                                    | FRC (clock derived from the internal A/D RC oscillator) |

| 1                         | 00                                    | Fosc/4                                                  |

| 1                         | 01                                    | Fosc/16                                                 |

| 1                         | 10                                    | Fosc/64                                                 |

| 1                         | 11                                    | FRC (clock derived from the internal A/D RC oscillator) |

bit 5-4 Unimplemented: Read as '0'

bit 3-0 PCFG3:PCFG0: A/D Port Configuration Control bits

| PCFG <3:0> | AN7 | AN6 | AN5 | AN4 | AN3   | AN2   | AN1 | AN0 | VREF+ | VREF- | C/R |

|------------|-----|-----|-----|-----|-------|-------|-----|-----|-------|-------|-----|

| 0000       | Α   | Α   | Α   | Α   | Α     | Α     | Α   | Α   | Vdd   | Vss   | 8/0 |

| 0001       | Α   | Α   | Α   | Α   | VREF+ | Α     | Α   | Α   | AN3   | Vss   | 7/1 |

| 0010       | D   | D   | D   | Α   | Α     | Α     | Α   | Α   | Vdd   | Vss   | 5/0 |

| 0011       | D   | D   | D   | Α   | VREF+ | Α     | Α   | Α   | AN3   | Vss   | 4/1 |

| 0100       | D   | D   | D   | D   | Α     | D     | Α   | Α   | Vdd   | Vss   | 3/0 |

| 0101       | D   | D   | D   | D   | VREF+ | D     | Α   | Α   | AN3   | Vss   | 2/1 |

| 011x       | D   | D   | D   | D   | D     | D     | D   | D   | _     | _     | 0/0 |

| 1000       | Α   | Α   | Α   | Α   | VREF+ | VREF- | Α   | Α   | AN3   | AN2   | 6/2 |

| 1001       | D   | D   | Α   | Α   | Α     | Α     | Α   | Α   | Vdd   | Vss   | 6/0 |

| 1010       | D   | D   | Α   | Α   | VREF+ | Α     | Α   | Α   | AN3   | Vss   | 5/1 |

| 1011       | D   | D   | Α   | Α   | VREF+ | VREF- | Α   | Α   | AN3   | AN2   | 4/2 |

| 1100       | D   | D   | D   | Α   | VREF+ | VREF- | Α   | Α   | AN3   | AN2   | 3/2 |

| 1101       | D   | D   | D   | D   | VREF+ | VREF- | Α   | Α   | AN3   | AN2   | 2/2 |

| 1110       | D   | D   | D   | D   | D     | D     | D   | Α   | Vdd   | Vss   | 1/0 |

| 1111       | D   | D   | D   | D   | VREF+ | VREF- | D   | Α   | AN3   | AN2   | 1/2 |

A = Analog input D = Digital I/O

C/R = # of analog input channels/# of A/D voltage references

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0' - n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

**Note:** On any device Reset, the port pins that are multiplexed with analog functions (ANx) are forced to be an analog input.

## 12.7 Comparator Operation During Sleep

When a comparator is active and the device is placed in Sleep mode, the comparator remains active and the interrupt is functional if enabled. This interrupt will wake-up the device from Sleep mode when enabled. While the comparator is powered up, higher Sleep currents than shown in the power-down current specification will occur. Each operational comparator will consume additional current as shown in the comparator specifications. To minimize power consumption while in Sleep mode, turn off the comparators, CM<2:0> = 111, before entering Sleep. If the device wakes up from Sleep, the contents of the CMCON register are not affected.

### 12.8 Effects of a Reset

A device Reset forces the CMCON register to its Reset state, causing the comparator module to be in the Comparator Off mode, CM<2:0>=111. This ensures compatibility to the PIC16F87X devices.

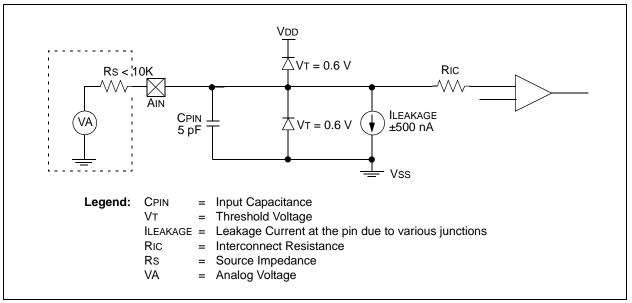

## 12.9 Analog Input Connection Considerations

A simplified circuit for an analog input is shown in Figure 12-4. Since the analog pins are connected to a digital output, they have reverse biased diodes to VDD and Vss. The analog input, therefore, must be between Vss and VDD. If the input voltage deviates from this range by more than 0.6V in either direction, one of the diodes is forward biased and a latch-up condition may occur. A maximum source impedance of 10  $k\Omega$  is recommended for the analog sources. Any external component connected to an analog input pin, such as a capacitor or a Zener diode, should have very little leakage current.

FIGURE 12-4: ANALOG INPUT MODEL

TABLE 14-6: INITIALIZATION CONDITIONS FOR ALL REGISTERS (CONTINUED)

| Register | Devices |     |     | Power-on Reset,<br>Brown-out Reset | MCLR Resets,<br>WDT Reset | Wake-up via WDT or<br>Interrupt |           |

|----------|---------|-----|-----|------------------------------------|---------------------------|---------------------------------|-----------|

| TRISD    | 73A     | 74A | 76A | 77A                                | 1111 1111                 | 1111 1111                       | uuuu uuuu |

| TRISE    | 73A     | 74A | 76A | 77A                                | 0000 -111                 | 0000 -111                       | uuuu -uuu |

| PIE1     | 73A     | 74A | 76A | 77A                                | r000 0000                 | r000 0000                       | ruuu uuuu |

|          | 73A     | 74A | 76A | 77A                                | 0000 0000                 | 0000 0000                       | uuuu uuuu |

| PIE2     | 73A     | 74A | 76A | 77A                                | -0-0 00                   | -0-0 00                         | -u-u uu   |

| PCON     | 73A     | 74A | 76A | 77A                                | qq                        | uu                              | uu        |

| SSPCON2  | 73A     | 74A | 76A | 77A                                | 0000 0000                 | 0000 0000                       | uuuu uuuu |

| PR2      | 73A     | 74A | 76A | 77A                                | 1111 1111                 | 1111 1111                       | 1111 1111 |

| SSPADD   | 73A     | 74A | 76A | 77A                                | 0000 0000                 | 0000 0000                       | uuuu uuuu |

| SSPSTAT  | 73A     | 74A | 76A | 77A                                | 00 0000                   | 00 0000                         | uu uuuu   |

| TXSTA    | 73A     | 74A | 76A | 77A                                | 0000 -010                 | 0000 -010                       | uuuu -uuu |

| SPBRG    | 73A     | 74A | 76A | 77A                                | 0000 0000                 | 0000 0000                       | uuuu uuuu |

| CMCON    | 73A     | 974 | 76A | 77A                                | 0000 0111                 | 0000 0111                       | uuuu uuuu |

| CVRCON   | 73A     | 74A | 76A | 77A                                | 000- 0000                 | 000- 0000                       | uuu- uuuu |

| ADRESL   | 73A     | 74A | 76A | 77A                                | xxxx xxxx                 | uuuu uuuu                       | uuuu uuuu |

| ADCON1   | 73A     | 74A | 76A | 77A                                | 00 0000                   | 00 0000                         | uu uuuu   |

| EEDATA   | 73A     | 74A | 76A | 77A                                | xxxx xxxx                 | uuuu uuuu                       | uuuu uuuu |

| EEADR    | 73A     | 74A | 76A | 77A                                | xxxx xxxx                 | uuuu uuuu                       | uuuu uuuu |

| EEDATH   | 73A     | 74A | 76A | 77A                                | xxxx xxxx                 | uuuu uuuu                       | uuuu uuuu |

| EEADRH   | 73A     | 74A | 76A | 77A                                | xxxx xxxx                 | uuuu uuuu                       | uuuu uuuu |

| EECON1   | 73A     | 74A | 76A | 77A                                | x x000                    | u u000                          | u uuuu    |

| EECON2   | 73A     | 74A | 76A | 77A                                |                           |                                 |           |

**Legend:** u = unchanged, x = unknown, - = unimplemented bit, read as '0', <math>q = value depends on condition, r = reserved, maintain clear. Shaded cells indicate conditions do not apply for the designated device.

- Note 1: One or more bits in INTCON, PIR1 and/or PIR2 will be affected (to cause wake-up).

- 2: When the wake-up is due to an interrupt and the GIE bit is set, the PC is loaded with the interrupt vector (0004h).

- 3: See Table 14-5 for Reset value for specific condition.

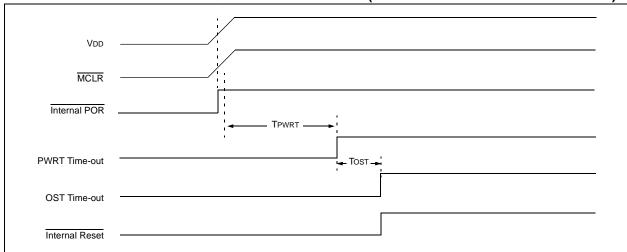

FIGURE 14-6: TIME-OUT SEQUENCE ON POWER-UP (MCLR TIED TO VDD VIA RC NETWORK)

### 14.11.1 INT INTERRUPT

External interrupt on the RB0/INT pin is edge triggered, either rising if bit INTEDG (OPTION\_REG<6>) is set or falling if the INTEDG bit is clear. When a valid edge appears on the RB0/INT pin, flag bit, INTF (INTCON<1>), is set. This interrupt can be disabled by clearing enable bit, INTE (INTCON<4>). Flag bit INTF must be cleared in software in the Interrupt Service Routine before re-enabling this interrupt. The INT interrupt can wake-up the processor from Sleep if bit INTE was set prior to going into Sleep. The status of global interrupt enable bit, GIE, decides whether or not the processor branches to the interrupt vector following wake-up. See Section 14.14 "Power-down Mode (Sleep)" for details on Sleep mode.

### 14.11.2 TMR0 INTERRUPT

An overflow (FFh  $\rightarrow$  00h) in the TMR0 register will set flag bit, TMR0IF (INTCON<2>). The interrupt can be enabled/disabled by setting/clearing enable bit, TMR0IE (INTCON<5>). See **Section 5.0 "Timer0 Module"**.

#### 14.11.3 PORTB INTCON CHANGE

An input change on PORTB<7:4> sets flag bit, RBIF (INTCON<0>). The interrupt can be enabled/disabled by setting/clearing enable bit, RBIE (INTCON<4>). See Section 4.2 "PORTB and the TRISB Register".

## 14.12 Context Saving During Interrupts

During an interrupt, only the return PC value is saved on the stack. Typically, users may wish to save key registers during an interrupt (i.e., W register and Status register). This will have to be implemented in software.

For the PIC16F873A/874A devices, the register W\_TEMP must be defined in both Banks 0 and 1 and must be defined at the same offset from the bank base address (i.e., If W\_TEMP is defined at 0x20 in Bank 0, it must also be defined at 0xA0 in Bank 1). The registers, PCLATH\_TEMP and STATUS\_TEMP, are only defined in Bank 0.

Since the upper 16 bytes of each bank are common in the PIC16F876A/877A devices, temporary holding registers, W\_TEMP, STATUS\_TEMP and PCLATH\_TEMP, should be placed in here. These 16 locations don't require banking and therefore, make it easier for context save and restore. The same code shown in Example 14-1 can be used.

### EXAMPLE 14-1: SAVING STATUS, W AND PCLATH REGISTERS IN RAM

```

W TEMP

;Copy W to TEMP register

MOVWF

SWAPF

STATUS, W

;Swap status to be saved into W

STATUS

; bank 0, regardless of current bank, Clears IRP, RP1, RP0

CLRF

MOVWF

STATUS TEMP

; Save status to bank zero STATUS TEMP register

MOVE

PCLATH, W

;Only required if using pages 1, 2 and/or 3

MOVWF

PCLATH TEMP

;Save PCLATH into W

CLRF

PCLATH

; Page zero, regardless of current page

:(ISR)

; (Insert user code here)

MOVF

PCLATH TEMP, W

; Restore PCLATH

MOVWF

PCLATH

; Move W into PCLATH

SWAPF

STATUS TEMP, W

;Swap STATUS TEMP register into W

; (sets bank to original state)

STATUS

MOVWF

; Move W into STATUS register

SWAPE

W TEMP, F

; Swap W TEMP

SWAPF

W TEMP, W

;Swap W TEMP into W

```

| CALL                 | Call Subroutine                                                                                                                                                                                                           | CLRWDT                        | Clear Watchdog Timer                                                                                                                               |

|----------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:              | [label] CALL k                                                                                                                                                                                                            | Syntax:                       | [label] CLRWDT                                                                                                                                     |

| Operands:            | $0 \leq k \leq 2047$                                                                                                                                                                                                      | Operands:                     | None                                                                                                                                               |

| Operation:           | (PC)+ 1 $\rightarrow$ TOS,<br>k $\rightarrow$ PC<10:0>,<br>(PCLATH<4:3>) $\rightarrow$ PC<12:11>                                                                                                                          | Operation:                    | 00h → WDT<br>0 → WDT prescaler,<br>1 → $\overline{TO}$                                                                                             |

| Status Affected:     | None                                                                                                                                                                                                                      |                               | 1 → PD                                                                                                                                             |

| Description:         | Call Subroutine. First, return address (PC+1) is pushed onto the stack. The eleven-bit immediate address is loaded into PC bits <10:0>. The upper bits of the PC are loaded from PCLATH. CALL is a two-cycle instruction. | Status Affected: Description: | TO, PD  CLRWDT instruction resets the Watchdog Timer. It also resets the prescaler of the WDT. Status bits, TO and PD, are set.                    |

| CLRF                 | Clear f                                                                                                                                                                                                                   | COMF                          | Complement f                                                                                                                                       |

| Syntax:              | [label] CLRF f                                                                                                                                                                                                            | Syntax:                       | [ label ] COMF f,d                                                                                                                                 |

| Operands:            | $0 \leq f \leq 127$                                                                                                                                                                                                       | Operands:                     | $0 \leq f \leq 127$                                                                                                                                |

| Operation:           | $00h \rightarrow (f)$                                                                                                                                                                                                     |                               | d ∈ [0,1]                                                                                                                                          |

|                      | $1 \rightarrow Z$                                                                                                                                                                                                         | Operation:                    | $(\bar{f}) \rightarrow (destination)$                                                                                                              |

| Status Affected:     | Z                                                                                                                                                                                                                         | Status Affected:              | Z                                                                                                                                                  |

| Description:         | The contents of register 'f' are cleared and the Z bit is set.                                                                                                                                                            | Description:                  | The contents of register 'f' are complemented. If 'd' is '0', the result is stored in W. If 'd' is '1', the result is stored back in register 'f'. |

| CLRW                 | Clear W                                                                                                                                                                                                                   | DECF                          | Decrement f                                                                                                                                        |

| Syntax:              | [ label ] CLRW                                                                                                                                                                                                            | Syntax:                       | [ label ] DECF f,d                                                                                                                                 |

| Operands: Operation: | None $00h \rightarrow (W)$                                                                                                                                                                                                | Operands:                     | $0 \le f \le 127$<br>$d \in [0,1]$                                                                                                                 |

| Operation.           | $1 \to Z$                                                                                                                                                                                                                 | Operation:                    | (f) - 1 → (destination)                                                                                                                            |

| Status Affected:     | Z                                                                                                                                                                                                                         | Status Affected:              | Z                                                                                                                                                  |

| Description:         | W register is cleared. Zero bit (Z) is set.                                                                                                                                                                               | Description:                  | Decrement register 'f'. If 'd' is '0', the result is stored in the W register. If 'd' is '1', the result is stored back in register 'f'.           |

### 16.0 DEVELOPMENT SUPPORT

The PIC® microcontrollers are supported with a full range of hardware and software development tools:

- · Integrated Development Environment

- MPLAB® IDE Software

- · Assemblers/Compilers/Linkers

- MPASM™ Assembler

- MPLAB C17 and MPLAB C18 C Compilers

- MPLINK™ Object Linker/ MPLIB™ Object Librarian

- MPLAB C30 C Compiler

- MPLAB ASM30 Assembler/Linker/Library

- Simulators

- MPLAB SIM Software Simulator

- MPLAB dsPIC30 Software Simulator

- Emulators

- MPLAB ICE 2000 In-Circuit Emulator

- MPLAB ICE 4000 In-Circuit Emulator

- · In-Circuit Debugger

- MPLAB ICD 2

- Device Programmers

- PRO MATE® II Universal Device Programmer

- PICSTART® Plus Development Programmer

- Low Cost Demonstration Boards

- PICDEM™ 1 Demonstration Board

- PICDEM.net™ Demonstration Board

- PICDEM 2 Plus Demonstration Board

- PICDEM 3 Demonstration Board

- PICDEM 4 Demonstration Board

- PICDEM 17 Demonstration Board

- PICDEM 18R Demonstration Board

- PICDEM LIN Demonstration Board

- PICDEM USB Demonstration Board

- Evaluation Kits

- KEELOQ®

- PICDEM MSC

- microID®

- CAN

- PowerSmart®

- Analog

## 16.1 MPLAB Integrated Development Environment Software

The MPLAB IDE software brings an ease of software development previously unseen in the 8/16-bit micro-controller market. The MPLAB IDE is a Windows® based application that contains:

- · An interface to debugging tools

- simulator

- programmer (sold separately)

- emulator (sold separately)

- in-circuit debugger (sold separately)

- · A full-featured editor with color coded context

- A multiple project manager

- Customizable data windows with direct edit of contents

- · High level source code debugging

- · Mouse over variable inspection

- · Extensive on-line help

The MPLAB IDE allows you to:

- Edit your source files (either assembly or C)

- One touch assemble (or compile) and download to PIC MCU emulator and simulator tools (automatically updates all project information)

- · Debug using:

- source files (assembly or C)

- absolute listing file (mixed assembly and C)

- machine code

MPLAB IDE supports multiple debugging tools in a single development paradigm, from the cost effective simulators, through low cost in-circuit debuggers, to full-featured emulators. This eliminates the learning curve when upgrading to tools with increasing flexibility and power.

### 16.2 MPASM Assembler

The MPASM assembler is a full-featured, universal macro assembler for all PIC MCUs.

The MPASM assembler generates relocatable object files for the MPLINK object linker, Intel® standard HEX files, MAP files to detail memory usage and symbol reference, absolute LST files that contain source lines and generated machine code and COFF files for debugging.

The MPASM assembler features include:

- · Integration into MPLAB IDE projects

- User defined macros to streamline assembly code

- Conditional assembly for multi-purpose source files

- Directives that allow complete control over the assembly process

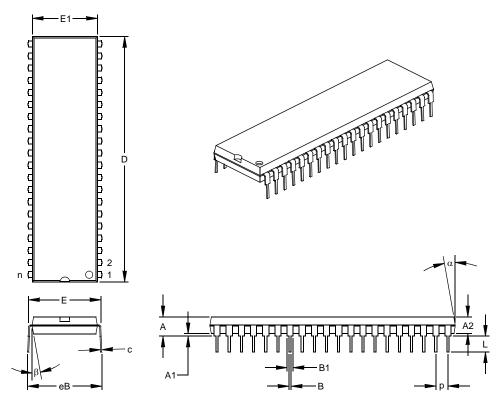

## 40-Lead Plastic Dual In-line (P) - 600 mil (PDIP)

Note: For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

|                            | Units    | INCHES* |       |       | MILLIMETERS |       |       |

|----------------------------|----------|---------|-------|-------|-------------|-------|-------|

| Dimension                  | n Limits | MIN     | MOM   | MAX   | MIN         | NOM   | MAX   |

| Number of Pins             | n        |         | 40    |       |             | 40    |       |

| Pitch                      | р        |         | .100  |       |             | 2.54  |       |

| Top to Seating Plane       | Α        | .160    | .175  | .190  | 4.06        | 4.45  | 4.83  |

| Molded Package Thickness   | A2       | .140    | .150  | .160  | 3.56        | 3.81  | 4.06  |

| Base to Seating Plane      | A1       | .015    |       |       | 0.38        |       |       |

| Shoulder to Shoulder Width | Е        | .595    | .600  | .625  | 15.11       | 15.24 | 15.88 |

| Molded Package Width       | E1       | .530    | .545  | .560  | 13.46       | 13.84 | 14.22 |

| Overall Length             | D        | 2.045   | 2.058 | 2.065 | 51.94       | 52.26 | 52.45 |

| Tip to Seating Plane       | L        | .120    | .130  | .135  | 3.05        | 3.30  | 3.43  |

| Lead Thickness             | С        | .008    | .012  | .015  | 0.20        | 0.29  | 0.38  |

| Upper Lead Width           | B1       | .030    | .050  | .070  | 0.76        | 1.27  | 1.78  |

| Lower Lead Width           | В        | .014    | .018  | .022  | 0.36        | 0.46  | 0.56  |

| Overall Row Spacing §      | eВ       | .620    | .650  | .680  | 15.75       | 16.51 | 17.27 |

| Mold Draft Angle Top       | α        | 5       | 10    | 15    | 5           | 10    | 15    |

| Mold Draft Angle Bottom    | β        | 5       | 10    | 15    | 5           | 10    | 15    |

Dimensions D and E1 do not include mold flash or protrusions. Mold flash or protrusions shall not exceed

.010" (0.254mm) per side.

JEDEC Equivalent: MO-011

Drawing No. C04-016

<sup>\*</sup> Controlling Parameter § Significant Characteristic

| Capture/Compare/PWM Requirements           |            | Data EEPROM Memory                                       |          |

|--------------------------------------------|------------|----------------------------------------------------------|----------|

| (CCP1 and CCP2)                            | 186        | Associated Registers                                     | 39       |

| CCP. See Capture/Compare/PWM.              |            | EEADR Register                                           | 33       |

| CCP1CON Register                           | 19         | EEADRH Register                                          | 33       |

| CCP2CON Register                           |            | EECON1 Register                                          |          |

| CCPR1H Register                            |            | EECON2 Register                                          |          |

| CCPR1L Register                            |            | Operation During Code-Protect                            |          |

| CCPR2H Register                            |            | Protection Against Spurious Writes                       |          |

| CCPR2L Register                            |            | Reading                                                  |          |

| CCPxM0 Bit                                 |            | Write Complete Flag Bit (EEIF)                           |          |

| CCPxM1 Bit                                 |            | Writing                                                  |          |

| CCPxM2 Bit                                 |            | · · · · · · · · · · · · · · · · · · ·                    |          |

| CCPxM3 Bit                                 |            | Data Memory                                              |          |

|                                            |            | Bank Select (RP1:RP0 Bits)                               |          |

| CCPxX Bit                                  |            | General Purpose Registers                                |          |

| CCPxY Bit                                  |            | Register File Map                                        |          |

| CLKO and I/O Timing Requirements           |            | Special Function Registers                               |          |

| CMCON Register                             | 20         | DC and AC Characteristics Graphs and Tables              |          |

| Code Examples                              |            | DC Characteristics1                                      | 75–179   |

| Call of a Subroutine in Page 1 from Page 0 |            | Demonstration Boards                                     |          |

| Indirect Addressing                        |            | PICDEM 1                                                 |          |

| Initializing PORTA                         |            | PICDEM 17                                                |          |

| Loading the SSPBUF (SSPSR) Register        |            | PICDEM 18R PIC18C601/801                                 |          |

| Reading Data EEPROM                        | 35         | PICDEM 2 Plus                                            | 170      |

| Reading Flash Program Memory               | 36         | PICDEM 3 PIC16C92X                                       | 170      |

| Saving Status, W and PCLATH Registers      |            | PICDEM 4                                                 | 170      |

| in RAM                                     | 154        | PICDEM LIN PIC16C43X                                     | 171      |

| Writing to Data EEPROM                     | 35         | PICDEM USB PIC16C7X5                                     | 171      |

| Writing to Flash Program Memory            |            | PICDEM.net Internet/Ethernet                             | 170      |

| Code Protection                            | . 143, 157 | Development Support                                      | 167      |

| Comparator Module                          | 135        | Device Differences                                       |          |

| Analog Input Connection                    |            | Device Overview                                          | 5        |

| Considerations                             | 139        | Direct Addressing                                        | 31       |

| Associated Registers                       |            | _                                                        |          |

| Configuration                              |            | E                                                        |          |

| Effects of a Reset                         |            | EEADR Register                                           | 21, 33   |

| Interrupts                                 |            | EEADRH Register                                          | 21. 33   |

| Operation                                  |            | EECON1 Register                                          |          |

| Operation During Sleep                     |            | EECON2 Register                                          |          |

| Outputs                                    |            | EEDATA Register                                          |          |

| Reference                                  |            | EEDATH Register                                          |          |

| Response Time                              |            | Electrical Characteristics                               |          |

| Comparator Specifications                  |            | Errata                                                   |          |

| Comparator Voltage Reference               |            | Evaluation and Programming Tools                         |          |

| Associated Registers                       |            | External Clock Timing Requirements                       |          |

| Computed GOTO                              |            | External Interrupt Input (RB0/INT). See Interrupt Source |          |

| •                                          |            | External Reference Signal                                |          |

| Configuration Bits                         |            | External Neterence Signal                                | 131      |

| Configuration Word                         |            | F                                                        |          |

| Conversion Considerations                  |            | Firmware Instructions                                    | 150      |

| CVRCON Register                            | 20         | Flash Program Memory                                     | 100      |

| D                                          |            | Associated Registers                                     | 30       |

|                                            |            | EECON1 Register                                          |          |

| Data EEPROM and Flash Program Memory       | 22         |                                                          |          |

| EEADR Register                             |            | EECON2 Register                                          |          |

| EEADRH Register                            |            | Reading                                                  |          |

| EECON1 Register                            |            | Writing                                                  |          |

| EECON2 Register                            |            | FSR Register19                                           | , ∠∪, 31 |

| EEDATA Register                            |            | G                                                        |          |

| EEDATH Register                            | 33         |                                                          |          |

|                                            |            | General Call Address Support                             | 94       |

| MPLAB ICE 4000 High-Performance Universal          |             | PICSTART Plus Development Programmer  | 169                                   |

|----------------------------------------------------|-------------|---------------------------------------|---------------------------------------|

| In-Circuit Emulator                                | 169         | PIE1 Register                         | 20, 25                                |

| MPLAB Integrated Development                       |             | PIE2 Register                         | 20, 27                                |

| Environment Software                               | 167         | Pinout Descriptions                   |                                       |

| MPLINK Object Linker/MPLIB Object Librarian        |             | PIC16F873A/PIC16F876A                 |                                       |

| MSSP                                               | 71          | PIR1 Register                         |                                       |

| I <sup>2</sup> C Mode. See I <sup>2</sup> C.       |             | PIR2 Register                         | 19, 28                                |

| SPI Mode                                           | 71          | POP                                   | 30                                    |

| SPI Mode. See SPI.                                 |             | POR. See Power-on Reset.              |                                       |

| MSSP Module                                        |             | PORTA                                 | 8, 10                                 |

| Clock Stretching                                   |             | Associated Registers                  |                                       |

| Clock Synchronization and the CKP Bit.             |             | Functions                             |                                       |

| Control Registers (General)                        |             | PORTA Register                        | · · · · · · · · · · · · · · · · · · · |

| Operation                                          | 84          | TRISA Register                        |                                       |

| Overview                                           |             | PORTB                                 |                                       |

| SPI Master Mode                                    |             | Associated Registers                  |                                       |

| SPI Slave Mode                                     |             | Functions                             |                                       |

| SSPBUF                                             |             | PORTB Register                        |                                       |

| SSPSR                                              |             | Pull-up Enable (RBPU Bit)             |                                       |

| Multi-Master Mode                                  | 105         | RB0/INT Edge Select (INTEDG Bit)      |                                       |

| 0                                                  |             | RB0/INT Pin, External                 |                                       |

|                                                    |             | RB7:RB4 Interrupt-on-Change           | 154                                   |

| Opcode Field Descriptions                          |             | RB7:RB4 Interrupt-on-Change Enable    |                                       |

| OPTION_REG Register                                |             | (RBIE Bit)                            | 24, 154                               |

| INTEDG Bit                                         |             | RB7:RB4 Interrupt-on-Change Flag      |                                       |

| PS2:PS0 Bits                                       |             | (RBIF Bit)                            |                                       |

| PSA Bit                                            |             | TRISB Register                        |                                       |

| RBPU Bit                                           |             | PORTB Register                        |                                       |

| TOCS Bit                                           |             | PORTC                                 | · · · · · · · · · · · · · · · · · · · |

| TOSE Bit                                           |             | Associated Registers                  |                                       |

| OSC1/CLKI Pin                                      |             | Functions                             |                                       |

| OSC2/CLKO Pin                                      | 8, 10       | PORTC Register                        |                                       |

| Oscillator Configuration                           | 4.45 4.40   | RC3/SCK/SCL Pin                       |                                       |

| HS                                                 |             | RC6/TX/CK Pin                         |                                       |

| LP                                                 |             | RC7/RX/DT Pin                         |                                       |

| RC                                                 |             | TRISC Register                        |                                       |

| XT                                                 |             | PORTD                                 |                                       |

| Oscillator Selection                               |             | Associated Registers                  |                                       |

| Oscillator Start-up Timer (OST)<br>Oscillator, WDT |             | Functions                             |                                       |

| Oscillators                                        | 133         | Parallel Slave Port (PSP) Function    |                                       |

| Capacitor Selection                                | 1.46        | PORTD Register                        |                                       |

| Ceramic Resonator Selection                        |             | TRISD Register                        |                                       |

| Crystal and Ceramic Resonators                     |             | PORTE                                 |                                       |

| RC                                                 |             | Analog Port Pins                      |                                       |

| NO                                                 | 140         | Associated RegistersFunctions         |                                       |

| P                                                  |             | Input Buffer Full Status (IBF Bit)    |                                       |

| Package Information                                |             | Input Buffer Overflow (IBOV Bit)      |                                       |

| Marking                                            | 209         | Output Buffer Full Status (OBF Bit)   |                                       |

| Packaging Information                              |             | PORTE Register                        |                                       |

| Paging, Program Memory                             |             | PSP Mode Select (PSPMODE Bit)         |                                       |

| Parallel Slave Port (PSP)                          |             | RE0/RD/AN5 Pin                        |                                       |

| Associated Registers                               |             | RE1/WR/AN6 Pin                        |                                       |

| RE0/RD/AN5 Pin                                     |             | RE2/CS/AN7 Pin                        |                                       |

| RE1/WR/AN6 Pin                                     | 49, 51      | TRISE Register                        |                                       |

| RE2/CS/AN7 Pin                                     | 49, 51      | Postscaler, WDT                       |                                       |

| Select (PSPMODE Bit)                               |             | Assignment (PSA Bit)                  | 23                                    |

| Parallel Slave Port Requirements                   | •           | Rate Select (PS2:PS0 Bits)            |                                       |

| (PIC16F874A/ 877A Only)                            | 187         | Power-down Mode. See Sleep.           |                                       |

| PCL Register                                       |             | Power-on Reset ( <u>POR)</u> 143, 147 | . 148. 149. 150                       |

| PCLATH Register                                    |             | POR Status (POR Bit)                  |                                       |

| PCON Register                                      | 20, 29, 149 | Power Control (PCON) Register         |                                       |

| BOR Bit                                            | 29          | Power-down (PD Bit)                   |                                       |

| POR Bit                                            |             | Power-up Timer (PWRT)                 |                                       |

| PIC16F87XA Product Identification System           | 231         | Time-out (TO Bit)                     |                                       |

| DICkit 1 Flach Starter Kit                         | 171         | * *                                   | ,                                     |