Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                                            |

|----------------------------|----------------------------------------------------------------------------|

| Product Status             | Active                                                                     |

| Core Processor             | PIC                                                                        |

| Core Size                  | 8-Bit                                                                      |

| Speed                      | 20MHz                                                                      |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                          |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                      |

| Number of I/O              | 22                                                                         |

| Program Memory Size        | 14KB (8K x 14)                                                             |

| Program Memory Type        | FLASH                                                                      |

| EEPROM Size                | 256 x 8                                                                    |

| RAM Size                   | 368 x 8                                                                    |

| Voltage - Supply (Vcc/Vdd) | 4V ~ 5.5V                                                                  |

| Data Converters            | A/D 5x10b                                                                  |

| Oscillator Type            | External                                                                   |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                          |

| Mounting Type              | Surface Mount                                                              |

| Package / Case             | 28-SOIC (0.295", 7.50mm Width)                                             |

| Supplier Device Package    | 28-SOIC                                                                    |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16f876at-i-so |

TABLE 1-2: PIC16F873A/876A PINOUT DESCRIPTION (CONTINUED)

| IABLE 1-2. PI         |                          | QFN  | I/O/P      | Buffer                | TION (CONTINUED)                                                                                                     |

|-----------------------|--------------------------|------|------------|-----------------------|----------------------------------------------------------------------------------------------------------------------|

| Pin Name              | PDIP, SOIC,<br>SSOP Pin# | Pin# | Type       | Туре                  | Description                                                                                                          |

|                       |                          |      |            |                       | PORTB is a bidirectional I/O port. PORTB can be software                                                             |

| DD0/INIT              | 0.4                      | 40   |            | TTI (OT(1)            | programmed for internal weak pull-ups on all inputs.                                                                 |

| RB0/INT<br>RB0        | 21                       | 18   | I/O        | TTL/ST <sup>(1)</sup> | Digital I/O.                                                                                                         |

| INT                   |                          |      | 1/0        |                       | External interrupt.                                                                                                  |

| RB1                   | 22                       | 19   | I/O        | TTL                   | Digital I/O.                                                                                                         |

| RB2                   | 23                       | 20   | I/O        | TTL                   | Digital I/O.                                                                                                         |

|                       |                          |      | 1/0        |                       | Digital I/O.                                                                                                         |

| RB3/PGM<br>RB3        | 24                       | 21   | I/O        | TTL                   | Digital I/O.                                                                                                         |

| PGM                   |                          |      | ı, ü       |                       | Low-voltage (single-supply) ICSP programming enable pin.                                                             |

| RB4                   | 25                       | 22   | I/O        | TTL                   | Digital I/O.                                                                                                         |

| RB5                   | 26                       | 23   | I/O        | TTL                   | Digital I/O.                                                                                                         |

| RB6/PGC               | 27                       | 24   | ","        | TTL/ST <sup>(2)</sup> | Digital I/O.                                                                                                         |

| RB6                   | 21                       | 24   | I/O        | 111/31                | Digital I/O.                                                                                                         |

| PGC                   |                          |      | ı, c       |                       | In-circuit debugger and ICSP programming clock.                                                                      |

| RB7/PGD               | 28                       | 25   |            | TTL/ST <sup>(2)</sup> |                                                                                                                      |

| RB7                   |                          |      | I/O        |                       | Digital I/O.                                                                                                         |

| PGD                   |                          |      | I/O        |                       | In-circuit debugger and ICSP programming data.                                                                       |

|                       |                          |      |            |                       | PORTC is a bidirectional I/O port.                                                                                   |

| RC0/T1OSO/T1CKI       | 11                       | 8    |            | ST                    |                                                                                                                      |

| RC0                   |                          |      | I/O        |                       | Digital I/O.                                                                                                         |

| T10S0                 |                          |      | 0          |                       | Timer1 oscillator output.                                                                                            |

| T1CKI                 | 40                       | 0    | I          | OT                    | Timer1 external clock input.                                                                                         |

| RC1/T1OSI/CCP2<br>RC1 | 12                       | 9    | I/O        | ST                    | Digital I/O.                                                                                                         |

| T1OSI                 |                          |      | 1/0        |                       | Timer1 oscillator input.                                                                                             |

| CCP2                  |                          |      | I/O        |                       | Capture2 input, Compare2 output, PWM2 output.                                                                        |

| RC2/CCP1              | 13                       | 10   |            | ST                    |                                                                                                                      |

| RC2                   |                          |      | I/O        |                       | Digital I/O.                                                                                                         |

| CCP1                  |                          |      | I/O        |                       | Capture1 input, Compare1 output, PWM1 output.                                                                        |

| RC3/SCK/SCL           | 14                       | 11   |            | ST                    |                                                                                                                      |

| RC3                   |                          |      | I/O        |                       | Digital I/O.                                                                                                         |

| SCK<br>SCL            |                          |      | I/O<br>I/O |                       | Synchronous serial clock input/output for SPI mode. Synchronous serial clock input/output for I <sup>2</sup> C mode. |

| RC4/SDI/SDA           | 15                       | 12   | 1/0        | ST                    | Synchronous serial clock input/output for 1 c mode.                                                                  |

| RC4/SDI/SDA<br>RC4    | 13                       | 12   | I/O        | ٥ı                    | Digital I/O.                                                                                                         |

| SDI                   |                          |      | ı, o       |                       | SPI data in.                                                                                                         |

| SDA                   |                          |      | I/O        |                       | I <sup>2</sup> C data I/O.                                                                                           |

| RC5/SDO               | 16                       | 13   |            | ST                    |                                                                                                                      |

| RC5                   |                          |      | I/O        |                       | Digital I/O.                                                                                                         |

| SDO                   |                          |      | 0          |                       | SPI data out.                                                                                                        |

| RC6/TX/CK             | 17                       | 14   |            | ST                    | Bis tel I/O                                                                                                          |

| RC6<br>TX             |                          |      | I/O<br>O   |                       | Digital I/O. USART asynchronous transmit.                                                                            |

| CK                    |                          |      | 1/0        |                       | USART asynchronous transmit. USART1 synchronous clock.                                                               |

| RC7/RX/DT             | 18                       | 15   |            | ST                    | · · · · · · · · · · · · · · · · · · ·                                                                                |

| RC7                   | 1.0                      |      | I/O        | <b>0</b> 1            | Digital I/O.                                                                                                         |

| RX                    |                          |      | I          |                       | USART asynchronous receive.                                                                                          |

| DT                    |                          |      | I/O        |                       | USART synchronous data.                                                                                              |

| Vss                   | 8, 19                    | 5, 6 | Р          |                       | Ground reference for logic and I/O pins.                                                                             |

| VDD                   | 20                       | 17   | Р          | _                     | Positive supply for logic and I/O pins.                                                                              |

**Legend:** I = input

ut O = output

I/O = input/output

P = power

— = Not used

TTL = TTL input

ST = Schmitt Trigger input

Note 1: This buffer is a Schmitt Trigger input when configured as the external interrupt.

- 2: This buffer is a Schmitt Trigger input when used in Serial Programming mode.

- 3: This buffer is a Schmitt Trigger input when configured in RC Oscillator mode and a CMOS input otherwise.

**TABLE 1-3:** PIC16F874A/877A PINOUT DESCRIPTION (CONTINUED)

| Pin Name                       | PDIP<br>Pin# | PLCC<br>Pin#     | TQFP<br>Pin#     | QFN<br>Pin#     | I/O/P<br>Type | Buffer<br>Type        | Description                                                                                        |

|--------------------------------|--------------|------------------|------------------|-----------------|---------------|-----------------------|----------------------------------------------------------------------------------------------------|

|                                |              |                  |                  |                 |               |                       | PORTD is a bidirectional I/O port or Parallel Slave Port when interfacing to a microprocessor bus. |

| RD0/PSP0<br>RD0<br>PSP0        | 19           | 21               | 38               | 38              | I/O<br>I/O    | ST/TTL <sup>(3)</sup> | Digital I/O.<br>Parallel Slave Port data.                                                          |

| RD1/PSP1<br>RD1<br>PSP1        | 20           | 22               | 39               | 39              | I/O<br>I/O    | ST/TTL <sup>(3)</sup> | Digital I/O.<br>Parallel Slave Port data.                                                          |

| RD2/PSP2<br>RD2<br>PSP2        | 21           | 23               | 40               | 40              | I/O<br>I/O    | ST/TTL <sup>(3)</sup> | Digital I/O. Parallel Slave Port data.                                                             |

| RD3/PSP3<br>RD3<br>PSP3        | 22           | 24               | 41               | 41              | I/O<br>I/O    | ST/TTL <sup>(3)</sup> | Digital I/O. Parallel Slave Port data.                                                             |

| RD4/PSP4<br>RD4<br>PSP4        | 27           | 30               | 2                | 2               | I/O<br>I/O    | ST/TTL <sup>(3)</sup> | Digital I/O. Parallel Slave Port data.                                                             |

| RD5/PSP5<br>RD5<br>PSP5        | 28           | 31               | 3                | 3               | I/O<br>I/O    | ST/TTL <sup>(3)</sup> | Digital I/O. Parallel Slave Port data.                                                             |

| RD6/PSP6<br>RD6<br>PSP6        | 29           | 32               | 4                | 4               | I/O<br>I/O    | ST/TTL <sup>(3)</sup> | Digital I/O.<br>Parallel Slave Port data.                                                          |

| RD7/PSP7<br>RD7<br>PSP7        | 30           | 33               | 5                | 5               | I/O<br>I/O    | ST/TTL <sup>(3)</sup> | Digital I/O.<br>Parallel Slave Port data.                                                          |

| RE0/RD/AN5                     |              |                  | 05               | 05              |               | ST/TTL <sup>(3)</sup> | PORTE is a bidirectional I/O port.                                                                 |

| RE0/RD/ANS<br>RE0<br>RD<br>AN5 | 8            | 9                | 25               | 25              | I/O<br>I<br>I | SI/TILE               | Digital I/O.<br>Read control for Parallel Slave Port.<br>Analog input 5.                           |

| RE1/WR/AN6<br>RE1<br>WR<br>AN6 | 9            | 10               | 26               | 26              | I/O<br>I<br>I | ST/TTL <sup>(3)</sup> | Digital I/O. Write control for Parallel Slave Port.                                                |

| RE2/CS/AN7 RE2 CS              | 10           | 11               | 27               | 27              | I/O<br>I      | ST/TTL <sup>(3)</sup> | Analog input 6.  Digital I/O.  Chip select control for Parallel Slave Port.                        |

| Vss                            | 12, 31       | 13, 34           | 6, 29            | 6, 30,          | l<br>P        | _                     | Analog input 7.  Ground reference for logic and I/O pins.                                          |

| VDD                            | 11, 32       | 12, 35           | 7, 28            | 7, 8,<br>28, 29 | Р             | _                     | Positive supply for logic and I/O pins.                                                            |

| NC                             | _            | 1, 17,<br>28, 40 | 12,13,<br>33, 34 | 13              | _             | _                     | These pins are not internally connected. These pins should be left unconnected.                    |

Legend: I = input O = output I/O = input/output

P = power

— = Not used TTL = TTL input ST = Schmitt Trigger input

Note 1: This buffer is a Schmitt Trigger input when configured as the external interrupt.

2: This buffer is a Schmitt Trigger input when used in Serial Programming mode.

3: This buffer is a Schmitt Trigger input when configured in RC Oscillator mode and a CMOS input otherwise.

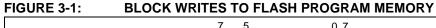

#### 3.6 Writing to Flash Program Memory

Flash program memory may only be written to if the destination address is in a segment of memory that is not write-protected, as defined in bits WRT1:WRT0 of the device configuration word (Register 14-1). Flash program memory must be written in four-word blocks. A block consists of four words with sequential addresses, with a lower boundary defined by an address, where EEADR<1:0> = 00. At the same time, all block writes to program memory are done as erase and write operations. The write operation is edge-aligned and cannot occur across boundaries.

To write program data, it must first be loaded into the buffer registers (see Figure 3-1). This is accomplished by first writing the destination address to EEADR and EEADRH and then writing the data to EEDATA and EEDATH. After the address and data have been set up, then the following sequence of events must be executed:

- 1. Set the EEPGD control bit (EECON1<7>).

- 2. Write 55h, then AAh, to EECON2 (Flash programming sequence).

- 3. Set the WR control bit (EECON1<1>).

All four buffer register locations **MUST** be written to with correct data. If only one, two or three words are being written to in the block of four words, then a read from the program memory location(s) not being written to must be performed. This takes the data from the program location(s) not being written and loads it into the EEDATA and EEDATH registers. Then the sequence of events to transfer data to the buffer registers must be executed.

To transfer data from the buffer registers to the program memory, the EEADR and EEADRH must point to the last location in the four-word block (EEADR<1:0> = 11). Then the following sequence of events must be executed:

- 1. Set the EEPGD control bit (EECON1<7>).

- 2. Write 55h, then AAh, to EECON2 (Flash programming sequence).

- Set control bit WR (EECON1<1>) to begin the write operation.

The user must follow the same specific sequence to initiate the write for each word in the program block, writing each program word in sequence (00,01,10,11). When the write is performed on the last word (EEADR<1:0> = 11), the block of four words are automatically erased and the contents of the buffer registers are written into the program memory.

After the "BSF EECON1, WR" instruction, the processor requires two cycles to set up the erase/write operation. The user must place two NOP instructions after the WR bit is set. Since data is being written to buffer registers, the writing of the first three words of the block appears to occur immediately. The processor will halt internal operations for the typical 4 ms, only during the cycle in which the erase takes place (i.e., the last word of the four-word block). This is not Sleep mode as the clocks and peripherals will continue to run. After the write cycle, the processor will resume operation with the third instruction after the EECON1 write instruction. If the sequence is performed to any other location, the action is ignored.

An example of the complete four-word write sequence is shown in Example 3-4. The initial address is loaded into the EEADRH:EEADR register pair; the four words of data are loaded using indirect addressing.

#### **EXAMPLE 3-4: WRITING TO FLASH PROGRAM MEMORY**

```

; This write routine assumes the following:

; 1. A valid starting address (the least significant bits = '00')is loaded in ADDRH:ADDRL

; 2. The 8 bytes of data are loaded, starting at the address in DATADDR

; 3. ADDRH, ADDRL and DATADDR are all located in shared data memory 0x70 - 0x7f

BSF

STATUS, RP1

; Bank 2

BCF

STATUS, RPO

; Load initial address

MOVF

ADDRH, W

MOVWF EEADRH

MOVF

ADDRL,W

MOVWF EEADR

MOVF DATAADDR,W

; Load initial data address

MOVWF FSR

; Load first data byte into lower

LOOP

MOVF INDF, W

MOVWF EEDATA

INCF FSR, F

; Next byte

INDF,W

MOVF

; Load second data byte into upper

MOVWF EEDATH

INCF

FSR, F

; Bank 3

STATUS, RPO

BSF

EECON1, EEPGD

BSF

; Point to program memory

; Enable writes

BSF

EECON1, WREN

BCF

INTCON, GIE

; Disable interrupts (if using)

MOVLW 55h

; Start of required write sequence:

MOVWF EECON2

; Write 55h

MOVLW AAh

; Write AAh

MOVWF EECON2

BSF

EECON1,WR

; Set WR bit to begin write

NOP

; Any instructions here are ignored as processor

; halts to begin write sequence

NOP

; processor will stop here and wait for write complete

; after write processor continues with 3rd instruction

EECON1, WREN

; Disable writes

INTCON, GIE

; Enable interrupts (if using)

BSF

BCF

STATUS, RPO

; Bank 2

INCF

EEADR.F

; Increment address

; Check if lower two bits of address are '00'

MOVF

EEADR,W

ANDLW

; Indicates when four words have been programmed

0 \times 03

XORLW

0x03

BTFSC STATUS, Z

; Exit if more than four words,

GOTO

; Continue if less than four words

LOOP

```

## 8.0 CAPTURE/COMPARE/PWM MODULES

Each Capture/Compare/PWM (CCP) module contains a 16-bit register which can operate as a:

- 16-bit Capture register

- 16-bit Compare register

- · PWM Master/Slave Duty Cycle register

Both the CCP1 and CCP2 modules are identical in operation, with the exception being the operation of the special event trigger. Table 8-1 and Table 8-2 show the resources and interactions of the CCP module(s). In the following sections, the operation of a CCP module is described with respect to CCP1. CCP2 operates the same as CCP1 except where noted.

#### **CCP1 Module:**

Capture/Compare/PWM Register 1 (CCPR1) is comprised of two 8-bit registers: CCPR1L (low byte) and CCPR1H (high byte). The CCP1CON register controls the operation of CCP1. The special event trigger is generated by a compare match and will reset Timer1.

#### CCP2 Module:

Capture/Compare/PWM Register 2 (CCPR2) is comprised of two 8-bit registers: CCPR2L (low byte) and CCPR2H (high byte). The CCP2CON register controls the operation of CCP2. The special event trigger is generated by a compare match and will reset Timer1 and start an A/D conversion (if the A/D module is enabled).

Additional information on CCP modules is available in the PIC<sup>®</sup> Mid-Range MCU Family Reference Manual (DS33023) and in application note *AN594*, "Using the CCP Module(s)" (DS00594).

TABLE 8-1: CCP MODE – TIMER RESOURCES REQUIRED

| CCP Mode | Timer Resource |

|----------|----------------|

| Capture  | Timer1         |

| Compare  | Timer1         |

| PWM      | Timer2         |

TABLE 8-2: INTERACTION OF TWO CCP MODULES

| CCPx Mode | CCPy Mode | Interaction                                                                         |

|-----------|-----------|-------------------------------------------------------------------------------------|

| Capture   | Capture   | Same TMR1 time base                                                                 |

| Capture   | Compare   | The compare should be configured for the special event trigger which clears TMR1    |

| Compare   | Compare   | The compare(s) should be configured for the special event trigger which clears TMR1 |

| PWM       | PWM       | The PWMs will have the same frequency and update rate (TMR2 interrupt)              |

| PWM       | Capture   | None                                                                                |

| PWM       | Compare   | None                                                                                |

#### 9.0 MASTER SYNCHRONOUS SERIAL PORT (MSSP) MODULE

#### 9.1 Master SSP (MSSP) Module Overview

The Master Synchronous Serial Port (MSSP) module is a serial interface, useful for communicating with other peripheral or microcontroller devices. These peripheral devices may be serial EEPROMs, shift registers, display drivers, A/D converters, etc. The MSSP module can operate in one of two modes:

- Serial Peripheral Interface (SPI)

- Inter-Integrated Circuit (I<sup>2</sup>C)

- Full Master mode

- Slave mode (with general address call)

The I<sup>2</sup>C interface supports the following modes in hardware:

- · Master mode

- · Multi-Master mode

- Slave mode

#### 9.2 Control Registers

The MSSP module has three associated registers. These include a status register (SSPSTAT) and two control registers (SSPCON and SSPCON2). The use of these registers and their individual configuration bits differ significantly, depending on whether the MSSP module is operated in SPI or I<sup>2</sup>C mode.

Additional details are provided under the individual sections.

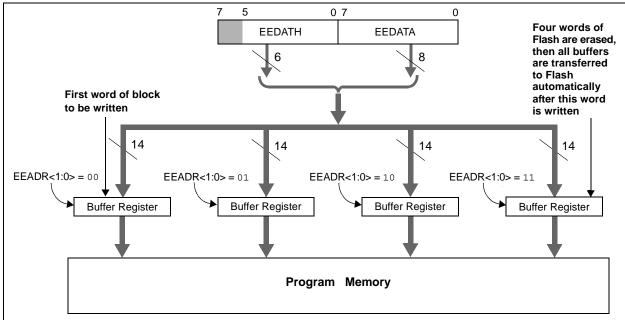

#### 9.3 SPI Mode

The SPI mode allows 8 bits of data to be synchronously transmitted and received simultaneously. All four modes of SPI are supported. To accomplish communication, typically three pins are used:

- Serial Data Out (SDO) RC5/SDO

- Serial Data In (SDI) RC4/SDI/SDA

- Serial Clock (SCK) RC3/SCK/SCL

Additionally, a fourth pin may be used when in a Slave mode of operation:

• Slave Select (SS) - RA5/AN4/SS/C2OUT

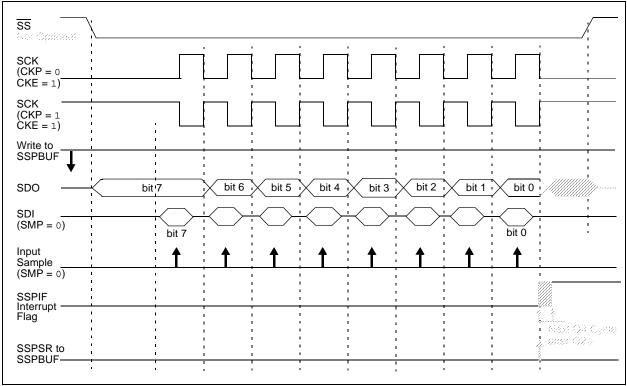

Figure 9-1 shows the block diagram of the MSSP module when operating in SPI mode.

FIGURE 9-1: MSSP BLOCK DIAGRAM (SPI MODE)

Note: When the SPI is in Slave mode with \$\overline{SS}\$ pin control enabled (SSPCON<3:0> = 0100), the state of the \$\overline{SS}\$ pin can affect the state read back from the TRISC<5> bit. The Peripheral OE signal from the SSP module in PORTC controls the state that is read back from the TRISC<5> bit (see Section 4.3 "PORTC and the TRISC Register" for information on PORTC). If Read-Modify-Write instructions, such as BSF, are performed on the TRISC register while the \$\overline{SS}\$ pin is high, this will cause the TRISC<5> bit to be set, thus disabling the SDO output.

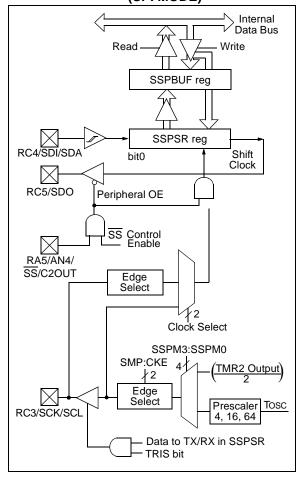

#### 9.3.2 OPERATION

When initializing the SPI, several options need to be specified. This is done by programming the appropriate control bits (SSPCON<5:0> and SSPSTAT<7:6>). These control bits allow the following to be specified:

- Master mode (SCK is the clock output)

- Slave mode (SCK is the clock input)

- Clock Polarity (Idle state of SCK)

- Data Input Sample Phase (middle or end of data output time)

- Clock Edge (output data on rising/falling edge of SCK)

- Clock Rate (Master mode only)

- Slave Select mode (Slave mode only)

The MSSP consists of a transmit/receive shift register (SSPSR) and a buffer register (SSPBUF). The SSPSR shifts the data in and out of the device, MSb first. The SSPBUF holds the data that was written to the SSPSR until the received data is ready. Once the eight bits of data have been received, that byte is moved to the SSPBUF register. Then, the Buffer Full detect bit, BF (SSPSTAT<0>), and the interrupt flag bit, SSPIF, are set. This double-buffering of the received data (SSPBUF) allows the next byte to start reception before reading the data that was just received. Any write to the

SSPBUF register during transmission/reception of data will be ignored and the write collision detect bit, WCOL (SSPCON<7>), will be set. User software must clear the WCOL bit so that it can be determined if the following write(s) to the SSPBUF register completed successfully.

When the application software is expecting to receive valid data, the SSPBUF should be read before the next byte of data to transfer is written to the SSPBUF. Buffer Full bit, BF (SSPSTAT<0>), indicates when SSPBUF has been loaded with the received data (transmission is complete). When the SSPBUF is read, the BF bit is cleared. This data may be irrelevant if the SPI is only a transmitter. Generally, the MSSP interrupt is used to determine when the transmission/reception has completed. The SSPBUF must be read and/or written. If the interrupt method is not going to be used, then software polling can be done to ensure that a write collision does not occur. Example 9-1 shows the loading of the SSPBUF (SSPSR) for data transmission.

The SSPSR is not directly readable or writable and can only be accessed by addressing the SSPBUF register. Additionally, the MSSP Status register (SSPSTAT) indicates the various status conditions.

#### **EXAMPLE 9-1: LOADING THE SSPBUF (SSPSR) REGISTER**

| LOOP | BTFSS<br>BRA  | SSPSTAT, BF<br>LOOP | ;Has data been received(transmit complete)?   |

|------|---------------|---------------------|-----------------------------------------------|

|      |               |                     |                                               |

|      | MOVF          | SSPBUF, W           | ;WREG reg = contents of SSPBUF                |

|      | MOVWF         | RXDATA              | ;Save in user RAM, if data is meaningful      |

|      | MOVF<br>MOVWF | TXDATA, W<br>SSPBUF | ;W reg = contents of TXDATA ;New data to xmit |

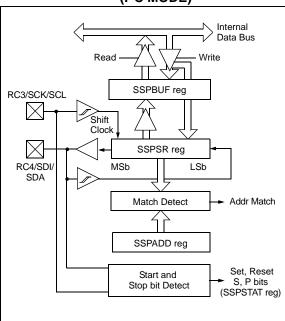

#### 9.4 I<sup>2</sup>C Mode

The MSSP module in I<sup>2</sup>C mode fully implements all master and slave functions (including general call support) and provides interrupts on Start and Stop bits in hardware to determine a free bus (multi-master function). The MSSP module implements the standard mode specifications, as well as 7-bit and 10-bit addressing.

Two pins are used for data transfer:

- Serial clock (SCL) RC3/SCK/SCL

- Serial data (SDA) RC4/SDI/SDA

The user must configure these pins as inputs or outputs through the TRISC<4:3> bits.

FIGURE 9-7: MSSP BLOCK DIAGRAM (I<sup>2</sup>C MODE)

#### 9.4.1 REGISTERS

The MSSP module has six registers for I<sup>2</sup>C operation. These are:

- MSSP Control Register (SSPCON)

- MSSP Control Register 2 (SSPCON2)

- MSSP Status Register (SSPSTAT)

- Serial Receive/Transmit Buffer Register (SSPBUF)

- MSSP Shift Register (SSPSR) Not directly accessible

- MSSP Address Register (SSPADD)

SSPCON, SSPCON2 and SSPSTAT are the control and status registers in  $I^2C$  mode operation. The SSPCON and SSPCON2 registers are readable and writable. The lower six bits of the SSPSTAT are read-only. The upper two bits of the SSPSTAT are read/write.

SSPSR is the shift register used for shifting data in or out. SSPBUF is the buffer register to which data bytes are written to or read from.

SSPADD register holds the slave device address when the SSP is configured in I<sup>2</sup>C Slave mode. When the SSP is configured in Master mode, the lower seven bits of SSPADD act as the baud rate generator reload value.

In receive operations, SSPSR and SSPBUF together create a double-buffered receiver. When SSPSR receives a complete byte, it is transferred to SSPBUF and the SSPIF interrupt is set.

During transmission, the SSPBUF is not double-buffered. A write to SSPBUF will write to both SSPBUF and SSPSR.

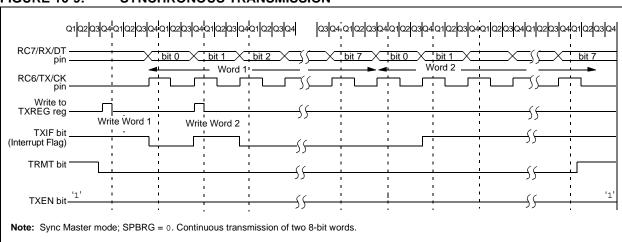

TABLE 10-8: REGISTERS ASSOCIATED WITH SYNCHRONOUS MASTER TRANSMISSION

| Address                | Name   | Bit 7                | Bit 6                        | Bit 5  | Bit 4 | Bit 3 | Bit 2  | Bit 1  | Bit 0  | Value on:<br>POR, BOR | Value on<br>all other<br>Resets |

|------------------------|--------|----------------------|------------------------------|--------|-------|-------|--------|--------|--------|-----------------------|---------------------------------|

| 0Bh, 8Bh,<br>10Bh,18Bh | INTCON | GIE                  | PEIE                         | TMR0IE | INTE  | RBIE  | TMR0IF | INTF   | R0IF   | 0000 000x             | 0000 000u                       |

| 0Ch                    | PIR1   | PSPIF <sup>(1)</sup> | ADIF                         | RCIF   | TXIF  | SSPIF | CCP1IF | TMR2IF | TMR1IF | 0000 0000             | 0000 0000                       |

| 18h                    | RCSTA  | SPEN                 | RX9                          | SREN   | CREN  | _     | FERR   | OERR   | RX9D   | 0000 -00x             | 0000 -00x                       |

| 19h                    | TXREG  | USART Tra            | USART Transmit Register      |        |       |       |        |        |        | 0000 0000             | 0000 0000                       |

| 8Ch                    | PIE1   | PSPIE <sup>(1)</sup> | ADIE                         | RCIE   | TXIE  | SSPIE | CCP1IE | TMR2IE | TMR1IE | 0000 0000             | 0000 0000                       |

| 98h                    | TXSTA  | CSRC                 | TX9                          | TXEN   | SYNC  | _     | BRGH   | TRMT   | TX9D   | 0000 -010             | 0000 -010                       |

| 99h                    | SPBRG  | Baud Rate            | Baud Rate Generator Register |        |       |       |        |        |        | 0000 0000             | 0000 0000                       |

**Legend:** x = unknown, - = unimplemented, read as '0'. Shaded cells are not used for synchronous master transmission.

Note 1: Bits PSPIE and PSPIF are reserved on 28-pin devices; always maintain these bits clear.

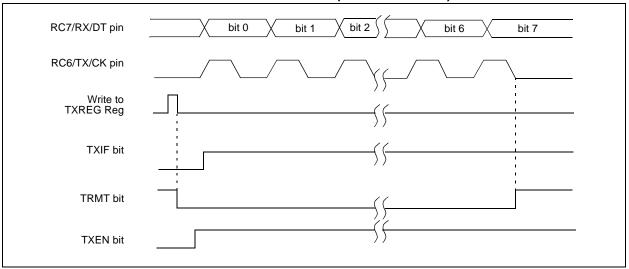

FIGURE 10-9: SYNCHRONOUS TRANSMISSION

FIGURE 10-10: SYNCHRONOUS TRANSMISSION (THROUGH TXEN)

TABLE 14-6: INITIALIZATION CONDITIONS FOR ALL REGISTERS (CONTINUED)

| Register | Devices |     |     |     | Power-on Reset,<br>Brown-out Reset | MCLR Resets,<br>WDT Reset | Wake-up via WDT or<br>Interrupt |

|----------|---------|-----|-----|-----|------------------------------------|---------------------------|---------------------------------|

| TRISD    | 73A     | 74A | 76A | 77A | 1111 1111                          | 1111 1111                 | uuuu uuuu                       |

| TRISE    | 73A     | 74A | 76A | 77A | 0000 -111                          | 0000 -111                 | uuuu -uuu                       |

| PIE1     | 73A     | 74A | 76A | 77A | r000 0000                          | r000 0000                 | ruuu uuuu                       |

| FIET     | 73A     | 74A | 76A | 77A | 0000 0000                          | 0000 0000                 | uuuu uuuu                       |

| PIE2     | 73A     | 74A | 76A | 77A | -0-0 00                            | -0-0 00                   | -u-u uu                         |

| PCON     | 73A     | 74A | 76A | 77A | qq                                 | uu                        | uu                              |

| SSPCON2  | 73A     | 74A | 76A | 77A | 0000 0000                          | 0000 0000                 | uuuu uuuu                       |

| PR2      | 73A     | 74A | 76A | 77A | 1111 1111                          | 1111 1111                 | 1111 1111                       |

| SSPADD   | 73A     | 74A | 76A | 77A | 0000 0000                          | 0000 0000                 | uuuu uuuu                       |

| SSPSTAT  | 73A     | 74A | 76A | 77A | 00 0000                            | 00 0000                   | uu uuuu                         |

| TXSTA    | 73A     | 74A | 76A | 77A | 0000 -010                          | 0000 -010                 | uuuu -uuu                       |

| SPBRG    | 73A     | 74A | 76A | 77A | 0000 0000                          | 0000 0000                 | uuuu uuuu                       |

| CMCON    | 73A     | 974 | 76A | 77A | 0000 0111                          | 0000 0111                 | uuuu uuuu                       |

| CVRCON   | 73A     | 74A | 76A | 77A | 000- 0000                          | 000- 0000                 | uuu- uuuu                       |

| ADRESL   | 73A     | 74A | 76A | 77A | xxxx xxxx                          | uuuu uuuu                 | uuuu uuuu                       |

| ADCON1   | 73A     | 74A | 76A | 77A | 00 0000                            | 00 0000                   | uu uuuu                         |

| EEDATA   | 73A     | 74A | 76A | 77A | xxxx xxxx                          | uuuu uuuu                 | uuuu uuuu                       |

| EEADR    | 73A     | 74A | 76A | 77A | xxxx xxxx                          | uuuu uuuu                 | uuuu uuuu                       |

| EEDATH   | 73A     | 74A | 76A | 77A | xxxx xxxx                          | uuuu uuuu                 | uuuu uuuu                       |

| EEADRH   | 73A     | 74A | 76A | 77A | xxxx xxxx                          | uuuu uuuu                 | uuuu uuuu                       |

| EECON1   | 73A     | 74A | 76A | 77A | x x000                             | u u000                    | u uuuu                          |

| EECON2   | 73A     | 74A | 76A | 77A |                                    |                           |                                 |

**Legend:** u = unchanged, x = unknown, - = unimplemented bit, read as '0', <math>q = value depends on condition, r = reserved, maintain clear. Shaded cells indicate conditions do not apply for the designated device.

- Note 1: One or more bits in INTCON, PIR1 and/or PIR2 will be affected (to cause wake-up).

- 2: When the wake-up is due to an interrupt and the GIE bit is set, the PC is loaded with the interrupt vector (0004h).

- 3: See Table 14-5 for Reset value for specific condition.

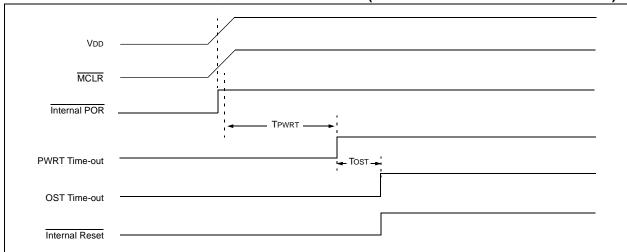

FIGURE 14-6: TIME-OUT SEQUENCE ON POWER-UP (MCLR TIED TO VDD VIA RC NETWORK)

| DECFSZ           | Decrement f, Skip if 0                                                                                                                                                                                                                                                                                       |

|------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [label] DECFSZ f,d                                                                                                                                                                                                                                                                                           |

| Operands:        | $0 \le f \le 127$<br>$d \in [0,1]$                                                                                                                                                                                                                                                                           |

| Operation:       | (f) - 1 $\rightarrow$ (destination);<br>skip if result = 0                                                                                                                                                                                                                                                   |

| Status Affected: | None                                                                                                                                                                                                                                                                                                         |

| Description:     | The contents of register 'f' are decremented. If 'd' is '0', the result is placed in the W register. If 'd' is '1', the result is placed back in register 'f'.  If the result is '1', the next instruction is executed. If the result is '0', then a NOP is executed instead, making it a 2 Tcy instruction. |

| INCFSZ           | Increment f, Skip if 0                                                                                                                                                                                                                                                                                  |

|------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [ label ] INCFSZ f,d                                                                                                                                                                                                                                                                                    |

| Operands:        | $0 \le f \le 127$<br>$d \in [0,1]$                                                                                                                                                                                                                                                                      |

| Operation:       | (f) + 1 $\rightarrow$ (destination),<br>skip if result = 0                                                                                                                                                                                                                                              |

| Status Affected: | None                                                                                                                                                                                                                                                                                                    |

| Description:     | The contents of register 'f' are incremented. If 'd' is '0', the result is placed in the W register. If 'd' is '1', the result is placed back in register 'f'.  If the result is '1', the next instruction is executed. If the result is '0', a NOP is executed instead, making it a 2 Tcy instruction. |

| GOTO             | Unconditional Branch                                                                                                                                                              |

|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [ label ] GOTO k                                                                                                                                                                  |

| Operands:        | $0 \leq k \leq 2047$                                                                                                                                                              |

| Operation:       | $k \rightarrow PC<10:0>$<br>PCLATH<4:3> $\rightarrow$ PC<12:11>                                                                                                                   |

| Status Affected: | None                                                                                                                                                                              |

| Description:     | GOTO is an unconditional branch. The eleven-bit immediate value is loaded into PC bits <10:0>. The upper bits of PC are loaded from PCLATH<4:3>. GOTO is a two-cycle instruction. |

| IORLW            | Inclusive OR Literal with W                                                                                      |

|------------------|------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [ label ] IORLW k                                                                                                |

| Operands:        | $0 \leq k \leq 255$                                                                                              |

| Operation:       | (W) .OR. $k \rightarrow (W)$                                                                                     |

| Status Affected: | Z                                                                                                                |

| Description:     | The contents of the W register are OR'ed with the eight-bit literal 'k'. The result is placed in the W register. |

| INCF             | Increment f                                                                                                                                                    |

|------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [ label ] INCF f,d                                                                                                                                             |

| Operands:        | $0 \le f \le 127$<br>$d \in [0,1]$                                                                                                                             |

| Operation:       | (f) + 1 $\rightarrow$ (destination)                                                                                                                            |

| Status Affected: | Z                                                                                                                                                              |

| Description:     | The contents of register 'f' are incremented. If 'd' is '0', the result is placed in the W register. If 'd' is '1', the result is placed back in register 'f'. |

| IORWF            | Inclusive OR W with f                                                                                                                                           |  |  |  |  |  |  |

|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

| Syntax:          | [ label ] IORWF f,d                                                                                                                                             |  |  |  |  |  |  |

| Operands:        | $0 \le f \le 127$<br>$d \in [0,1]$                                                                                                                              |  |  |  |  |  |  |

| Operation:       | (W) .OR. (f) $\rightarrow$ (destination)                                                                                                                        |  |  |  |  |  |  |

| Status Affected: | Z                                                                                                                                                               |  |  |  |  |  |  |

| Description:     | Inclusive OR the W register with register 'f'. If 'd' is '0', the result is placed in the W register. If 'd' is '1', the result is placed back in register 'f'. |  |  |  |  |  |  |

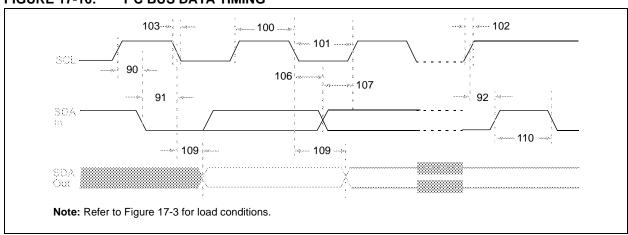

TABLE 17-10: I<sup>2</sup>C BUS START/STOP BITS REQUIREMENTS

| Param<br>No. | Symbol  | Charact         | Min          | Тур  | Max | Units | Conditions |                                          |

|--------------|---------|-----------------|--------------|------|-----|-------|------------|------------------------------------------|

| 90           | Tsu:sta | Start condition | 100 kHz mode | 4700 | _   | _     | ns         | Only relevant for Repeated Start         |

|              |         | Setup time      | 400 kHz mode | 600  | _   | _     |            | condition                                |

| 91           | THD:STA | Start condition | 100 kHz mode | 4000 | _   | _     | ns         | After this period, the first clock pulse |

|              |         | Hold time       | 400 kHz mode | 600  | _   | _     |            | is generated                             |

| 92           | Tsu:sto | Stop condition  | 100 kHz mode | 4700 | _   | _     | ns         |                                          |

|              |         | Setup time      | 400 kHz mode | 600  | _   | _     |            |                                          |

| 93           | THD:STO | Stop condition  | 100 kHz mode | 4000 | _   | _     | ns         |                                          |

|              |         | Hold time       | 400 kHz mode | 600  | _   | _     |            |                                          |

### FIGURE 17-16: I<sup>2</sup>C BUS DATA TIMING

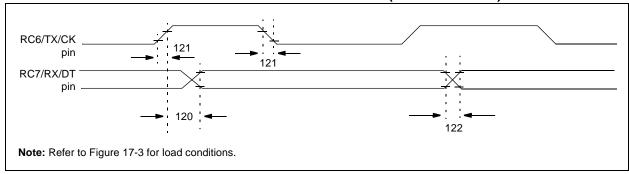

#### FIGURE 17-17: USART SYNCHRONOUS TRANSMISSION (MASTER/SLAVE) TIMING

TABLE 17-12: USART SYNCHRONOUS TRANSMISSION REQUIREMENTS

| Param<br>No.  | Symbol                | Characteristic                                          |                       | Min | Тур† | Max | Units | Conditions |

|---------------|-----------------------|---------------------------------------------------------|-----------------------|-----|------|-----|-------|------------|

| 120           | TCKH2DTV              | SYNC XMIT (MASTER & SLAVE) Clock High to Data Out Valid | Standard( <b>F</b> )  | _   | _    | 80  | ns    |            |

|               |                       |                                                         | Extended( <b>LF</b> ) | _   | _    | 100 | ns    |            |

| 121           | TCKRF                 | Clock Out Rise Time and Fall Time                       | Standard(F)           | _   | _    | 45  | ns    |            |

| (Master mode) | Extended( <b>LF</b> ) | _                                                       | _                     | 50  | ns   |     |       |            |

| 122           | TDTRF                 | Data Out Rise Time and Fall Time                        | Standard(F)           | _   | _    | 45  | ns    |            |

|               |                       |                                                         | Extended( <b>LF</b> ) | _   | _    | 50  | ns    |            |

<sup>†</sup> Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

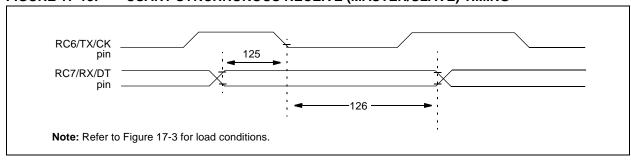

FIGURE 17-18: USART SYNCHRONOUS RECEIVE (MASTER/SLAVE) TIMING

TABLE 17-13: USART SYNCHRONOUS RECEIVE REQUIREMENTS

| Param<br>No. | Symbol   | Characteristic                                                    | Min | Тур† | Max | Units | Conditions |

|--------------|----------|-------------------------------------------------------------------|-----|------|-----|-------|------------|

| 125          | TDTV2CKL | SYNC RCV (MASTER & SLAVE)  Data Setup before CK ↓ (DT setup time) | 15  | _    | _   | ns    |            |

| 126          | TCKL2DTL | Data Hold after CK ↓ (DT hold time)                               | 15  | _    | _   | ns    |            |

<sup>†</sup> Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

TABLE 17-14: A/D CONVERTER CHARACTERISTICS:PIC16F873A/874A/876A/877A (INDUSTRIAL)

PIC16LF873A/874A/876A/877A (INDUSTRIAL)

| Param<br>No. | Sym   | Characte                              | ristic      | Min         | Тур†                      | Max          | Units | Conditions                                                                                                                        |

|--------------|-------|---------------------------------------|-------------|-------------|---------------------------|--------------|-------|-----------------------------------------------------------------------------------------------------------------------------------|

| A01          | NR    | Resolution                            |             | _           | _                         | 10-bits      | bit   | VREF = VDD = 5.12V,<br>VSS ≤ VAIN ≤ VREF                                                                                          |

| A03          | EIL   | Integral Linearity Er                 | ror         | _           | _                         | < ± 1        | LSb   | VREF = VDD = 5.12V,<br>VSS ≤ VAIN ≤ VREF                                                                                          |

| A04          | EDL   | Differential Linearity                | Error       | _           | _                         | < ± 1        | LSb   | VREF = VDD = 5.12V,<br>$VSS \le VAIN \le VREF$                                                                                    |

| A06          | EOFF  | Offset Error                          |             | _           | _                         | < ± 2        | LSb   | $VREF = VDD = 5.12V$ , $VSS \le VAIN \le VREF$                                                                                    |

| A07          | EGN   | Gain Error                            |             | _           | _                         | < ± 1        | LSb   | $VREF = VDD = 5.12V$ , $VSS \le VAIN \le VREF$                                                                                    |

| A10          | _     | Monotonicity                          |             | _           | guaranteed <sup>(3)</sup> |              | _     | VSS ≤ VAIN ≤ VREF                                                                                                                 |

| A20          | VREF  | Reference Voltage (VREF+ - VREF-)     |             | 2.0         | _                         | VDD + 0.3    | V     |                                                                                                                                   |

| A21          | VREF+ | Reference Voltage High                |             | AVDD - 2.5V |                           | AVDD + 0.3V  | V     |                                                                                                                                   |

| A22          | VREF- | Reference Voltage I                   | _ow         | AVss - 0.3V |                           | VREF+ - 2.0V | V     |                                                                                                                                   |

| A25          | Vain  | Analog Input Voltag                   | е           | Vss - 0.3V  | _                         | VREF + 0.3V  | V     |                                                                                                                                   |

| A30          | ZAIN  | Recommended Imp<br>Analog Voltage Sou |             | _           | _                         | 2.5          | kΩ    | (Note 4)                                                                                                                          |

| A40          | IAD   | A/D Conversion                        | PIC16F87XA  | _           | 220                       | _            | μΑ    | Average current                                                                                                                   |

|              |       | Current (VDD)                         | PIC16LF87XA | _           | 90                        | _            | μА    | consumption when A/D is on (Note 1)                                                                                               |

| A50          | IREF  | VREF Input Current                    | (Note 2)    |             |                           | 5            | μΑ    | During VAIN acquisition. Based on differential of VHOLD to VAIN to charge CHOLD, see Section 11.1 "A/D Acquisition Requirements". |

|              |       |                                       |             | _           | _                         | 150          | μА    | During A/D conversion cycle                                                                                                       |

<sup>\*</sup> These parameters are characterized but not tested.

Note 1: When A/D is off, it will not consume any current other than minor leakage current. The power-down current spec includes any such leakage from the A/D module.

- 2: VREF current is from RA3 pin or VDD pin, whichever is selected as reference input.

- 3: The A/D conversion result never decreases with an increase in the input voltage and has no missing codes.

- 4: Maximum allowed impedance for analog voltage source is 10 k $\Omega$ . This requires higher acquisition time.

<sup>†</sup> Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

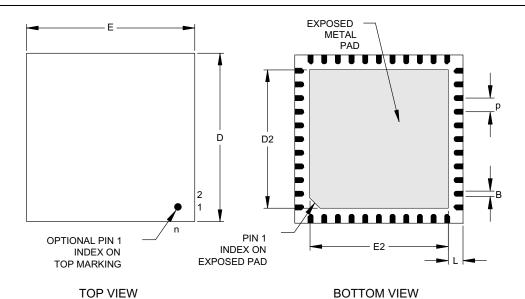

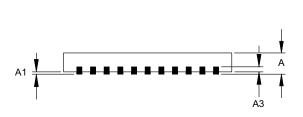

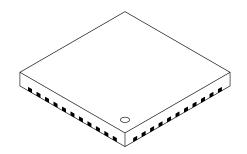

#### 44-Lead Plastic Quad Flat No Lead Package (ML) 8x8 mm Body (QFN)

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

|                    | Units    |      | INCHES   |      | М        | ILLIMETERS* |      |

|--------------------|----------|------|----------|------|----------|-------------|------|

| Dimensio           | n Limits | MIN  | NOM      | MAX  | MIN      | NOM         | MAX  |

| Number of Pins     | n        |      | 44       |      |          | 44          |      |

| Pitch              | р        |      | .026 BSC |      |          | 0.65 BSC    |      |

| Overall Height     | Α        | .031 | .035     | .039 | 0.80     | 0.90        | 1.00 |

| Standoff           | A1       | .000 | .001     | .002 | 0        | 0.02        | 0.05 |

| Base Thickness     | A3       |      | .010 REF |      | 0.25 REF |             |      |

| Overall Width      | E        |      | .315 BSC |      | 8.00 BSC |             |      |

| Exposed Pad Width  | E2       | .262 | .268     | .274 | 6.65     | 6.80        | 6.95 |

| Overall Length     | D        |      | .315 BSC |      |          | 8.00 BSC    |      |

| Exposed Pad Length | D2       | .262 | .268     | .274 | 6.65     | 6.80        | 6.95 |

| Lead Width         | В        | .012 | .013     | .013 | 0.30     | 0.33        | 0.35 |

| Lead Length        | L        | .014 | .016     | .018 | 0.35     | 0.40        | 0.45 |

<sup>\*</sup>Controlling Parameter

Notes

Dimensions D and E1 do not include mold flash or protrusions. Mold flash or protrusions shall not exceed .010" (0.254mm) per side.

JEDEC equivalent: M0-220

Drawing No. C04-103

### **INDEX**

| A                                              | Interrupt Logic                                 |        |

|------------------------------------------------|-------------------------------------------------|--------|

| A/D127                                         | MSSP (I <sup>2</sup> C Mode)                    |        |

| Acquisition Requirements                       | MSSP (SPI Mode)                                 | 71     |

| ADCON0 Register                                | On-Chip Reset Circuit                           | 147    |

| ADCON1 Register127                             | PIC16F873A/PIC16F876A Architecture              | 6      |

| ADIF Bit                                       | PIC16F874A/PIC16F877A Architecture              | 7      |

| ADRESH Register                                | PORTC                                           |        |

| ADRESL Register                                | Peripheral Output Override                      |        |

|                                                | (RC2:0, RC7:5) Pins                             | 46     |

| Analog Port Pins                               | Peripheral Output Override (RC4:3) Pins         |        |

| Associated Registers and Bits                  | PORTD (in I/O Port Mode)                        |        |

| Calculating Acquisition Time                   | PORTD and PORTE (Parallel Slave Port)           |        |

| Configuring Analog Port Pins                   | PORTE (In I/O Port Mode)                        |        |

| Configuring the Interrupt                      | RA3:RA0 Pins                                    |        |

| Configuring the Module129                      | RA4/T0CKI Pin                                   |        |

| Conversion Clock131                            | RA5 Pin                                         |        |

| Conversions132                                 | RB3:RB0 Pins                                    |        |

| Converter Characteristics194                   | RB7:RB4 Pins                                    |        |

| Effects of a Reset133                          | RC Oscillator Mode                              |        |

| GO/DONE Bit129                                 | Recommended MCLR Circuit                        |        |

| Internal Sampling Switch (Rss) Impedance130    |                                                 |        |

| Operation During Sleep133                      | Simplified PWM Mode                             |        |

| Result Registers132                            | Timer0/WDT Prescaler                            |        |

| Source Impedance130                            | Timer1                                          |        |

| A/D Conversion Requirements                    | Timer2                                          |        |

| Absolute Maximum Ratings173                    | USART Receive11                                 | ,      |

| ACKSTAT 101                                    | USART Transmit                                  |        |

| ADCON0 Register                                | Watchdog Timer                                  | 155    |

| ADCON1 Register20                              | BOR. See Brown-out Reset.                       |        |

| Addressable Universal Synchronous Asynchronous | BRG. See Baud Rate Generator.                   |        |

| Receiver Transmitter. See USART.               | BRGH Bit                                        | 113    |

| ADRESH Register                                | Brown-out Reset (BOR)143, 147, 148, 14          | 9, 150 |

| ADRESL Register                                | BOR Status (BOR Bit)                            | 29     |

| Analog-to-Digital Converter. See A/D.          | Bus Collision During a Repeated Start Condition | 108    |

| •                                              | Bus Collision During a Start Condition          |        |

| Application Notes                              | Bus Collision During a Stop Condition           | 109    |

| AN552 (Implementing Wake-up                    | Bus Collision Interrupt Flag bit, BCLIF         |        |

| on Key Stroke)                                 |                                                 |        |

| AN556 (Implementing a Table Read)30            | C                                               |        |

| Assembler                                      | C Compilers                                     |        |

| MPASM Assembler                                | MPLAB C17                                       | 168    |

| Asynchronous Reception                         | MPLAB C18                                       | 168    |

| Associated Registers118, 120                   | MPLAB C30                                       |        |

| Asynchronous Transmission                      | Capture/Compare/PWM (CCP)                       |        |

| Associated Registers116                        | Associated Registers                            |        |

| В                                              | Capture, Compare and Timer1                     | 68     |

|                                                | PWM and Timer2                                  |        |

| Banking, Data Memory                           | Capture Mode                                    |        |

| Baud Rate Generator97                          | CCP1IF                                          |        |

| Associated Registers113                        | Prescaler                                       |        |

| BCLIF28                                        | CCP Timer Resources                             |        |

| BF101                                          |                                                 | 03     |

| Block Diagrams                                 | Compare                                         | 00     |

| A/D129                                         | Special Event Trigger Output of CCP1            |        |

| Analog Input Model 130, 139                    | Special Event Trigger Output of CCP2            |        |

| Baud Rate Generator97                          | Compare Mode                                    |        |

| Capture Mode Operation65                       | Software Interrupt Mode                         |        |

| Comparator I/O Operating Modes136              | Special Event Trigger                           |        |

| Comparator Output138                           | Interaction of Two CCP Modules (table)          |        |

| Comparator Voltage Reference142                | PWM Mode                                        |        |

| Compare Mode Operation66                       | Duty Cycle                                      |        |

| Crystal/Ceramic Resonator Operation            | Example Frequencies/Resolutions (table)         |        |

| (HS, XT or LP Osc Configuration)               | PWM Period                                      |        |

| External Clock Input Operation                 | Special Event Trigger and A/D Conversions       | 66     |

| (HS. XT or LP Osc Configuration)               |                                                 |        |

| Power-up Timer (PWRT)148                         | RE0/RD/AN5 Pin                                    |     |

|--------------------------------------------------|---------------------------------------------------|-----|

| PR2 Register 20, 61                              | RE1/WR/AN6 Pin                                    | 13  |

| Prescaler, Timer0                                | RE2/CS/AN7 Pin                                    | 13  |

| Assignment (PSA Bit)23                           | Read-Modify-Write Operations 1                    | 59  |

| Rate Select (PS2:PS0 Bits)23                     | Register File                                     | 16  |

| PRO MATE II Universal Device Programmer169       | Register File Map (PIC16F873A/874A)               |     |

| Program Counter                                  | Register File Map (PIC16F876A/877A)               |     |

| Reset Conditions149                              | Registers                                         |     |

| Program Memory15                                 | ADCON0 (A/D Control 0) 1                          | 27  |

| Interrupt Vector                                 | ADCON1 (A/D Control 1) 1                          |     |

| Paging                                           | CCP1CON/CCP2CON (CCP Control 1                    |     |

| Program Memory Map and Stack                     | and CCP Control 2)                                | 64  |

| (PIC16F873A/874A)15                              | CMCON (Comparator Control)                        |     |

| Program Memory Map and Stack                     | CVRCON (Comparator Voltage                        | 00  |

| (PIC16F876A/877A)15                              | Reference Control)1                               | 11  |

| Reset Vector                                     | EECON1 (EEPROM Control 1)                         |     |

| Program Verification                             | FSR                                               |     |

|                                                  | INTCON                                            |     |

| Programming Pin (VPP)                            |                                                   |     |

|                                                  | OPTION_REG23,                                     |     |

| PSP. See Parallel Slave Port.                    | PCON (Power Control)                              |     |

| Pulse Width Modulation. See Capture/Compare/PWM, | PIE1 (Peripheral Interrupt Enable 1)              |     |

| PWM Mode.                                        | PIE2 (Peripheral Interrupt Enable 2)              |     |

| PUSH30                                           | PIR1 (Peripheral Interrupt Request 1)             |     |

| R                                                | PIR2 (Peripheral Interrupt Request 2)             |     |

|                                                  | RCSTA (Receive Status and Control)                |     |

| RAO/ANO Pin                                      | Special Function, Summary                         |     |

| RA1/AN1 Pin                                      | SSPCON (MSSP Control 1, I <sup>2</sup> C Mode)    |     |

| RA2/AN2/VREF-/CVREF Pin                          | SSPCON (MSSP Control 1, SPI Mode)                 |     |

| RA3/AN3/VREF+ Pin                                | SSPCON2 (MSSP Control 2, I <sup>2</sup> C Mode)   |     |

| RA4/T0CKI/C1OUT Pin                              | SSPSTAT (MSSP Status, I <sup>2</sup> C Mode)      |     |

| RA5/AN4/SS/C2OUT Pin                             | SSPSTAT (MSSP Status, SPI Mode)                   |     |

| RAM. See Data Memory.                            | Status                                            |     |

| RB0/INT Pin                                      | T1CON (Timer1 Control)                            |     |

| RB1 Pin                                          | T2CON (Timer2 Control)                            |     |

| RB2 Pin                                          | TRISE Register                                    |     |

| RB3/PGM Pin                                      | TXSTA (Transmit Status and Control) 1             |     |

| RB4 Pin                                          | Reset143, 1                                       |     |

| RB5 Pin                                          | Brown-out Reset (BOR). See Brown-out Reset (BOR)  | ).  |

| RB6/PGC Pin                                      | MCLR Reset. See MCLR.                             |     |

| RB7/PGD Pin                                      | Power-on Reset (POR). See Power-on Reset (POR).   |     |

| RC0/T10S0/T1CKI Pin                              | Reset Conditions for PCON Register 1              |     |

| RC1/T1OSI/CCP2 Pin                               | Reset Conditions for Program Counter 1            | 49  |

| RC2/CCP1 Pin                                     | Reset Conditions for Status Register 1            | 49  |

| RC3/SCK/SCL Pin                                  | WDT Reset. See Watchdog Timer (WDT).              |     |

| RC4/SDI/SDA Pin                                  | Reset, Watchdog Timer, Oscillator Start-up Timer, |     |

| RC5/SDO Pin                                      | Power-up Timer and Brown-out Reset                |     |

| RC6/TX/CK Pin                                    | Requirements1                                     | 84  |

| RC7/RX/DT Pin                                    | Revision History 2                                | 219 |

| RCREG Register19                                 | •                                                 |     |

| RCSTA Register19                                 | S                                                 |     |

| ADDEN Bit112                                     | SCI. See USART.                                   |     |

| CREN Bit112                                      | SCK                                               | 71  |

| FERR Bit112                                      | SDI                                               | 71  |

| OERR Bit112                                      | SDO                                               | 71  |

| RX9 Bit112                                       | Serial Clock, SCK                                 | 71  |

| RX9D Bit112                                      | Serial Communication Interface. See USART.        |     |

| SPEN Bit111, 112                                 | Serial Data In, SDI                               | 71  |

| SREN Bit112                                      | Serial Data Out, SDO                              |     |

| RD0/PSP0 Pin13                                   | Serial Peripheral Interface. See SPI.             |     |

| RD1/PSP1 Pin                                     | Slave Select Synchronization                      | 77  |

| RD2/PSP2 Pin                                     | Slave Select, SS                                  |     |

| RD3/PSP3 Pin                                     | Sleep143, 147, 1                                  |     |

| RD4/PSP4 Pin                                     | Software Simulator (MPLAB SIM)                    |     |

| RD5/PSP5 Pin                                     | Software Simulator (MPLAB SIM30)1                 | 68  |

| RD6/PSP6 Pin                                     | SPBRG Register                                    |     |

| RD7/PSP7 Pin13                                   | Special Features of the CPU1                      |     |

|                                                  |                                                   |     |

| Special Function Registers        | 19      | Timer0                                                   | 53       |

|-----------------------------------|---------|----------------------------------------------------------|----------|

| Special Function Registers (SFRs) | 19      | Associated Registers                                     |          |

| Speed, Operating                  | 1       | Clock Source Edge Select (T0SE Bit)                      |          |

| SPI Mode                          | 71, 77  | Clock Source Select (T0CS Bit)                           | 23       |

| Associated Registers              | 79      | External Clock                                           |          |

| Bus Mode Compatibility            |         | Interrupt                                                |          |

| Effects of a Reset                |         | Overflow Enable (TMR0IE Bit)                             |          |

| Enabling SPI I/O                  |         | Overflow Flag (TMR0IF Bit)                               | .24, 154 |

| Master Mode                       |         | Overflow Interrupt                                       |          |

| Master/Slave Connection           |         | Prescaler                                                |          |