Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                            |

|----------------------------|----------------------------------------------------------------------------|

| Product Status             | Active                                                                     |

| Core Processor             | PIC                                                                        |

| Core Size                  | 8-Bit                                                                      |

| Speed                      | 20MHz                                                                      |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                          |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                      |

| Number of I/O              | 22                                                                         |

| Program Memory Size        | 14KB (8K x 14)                                                             |

| Program Memory Type        | FLASH                                                                      |

| EEPROM Size                | 256 x 8                                                                    |

| RAM Size                   | 368 x 8                                                                    |

| Voltage - Supply (Vcc/Vdd) | 4V ~ 5.5V                                                                  |

| Data Converters            | A/D 5x10b                                                                  |

| Oscillator Type            | External                                                                   |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                          |

| Mounting Type              | Surface Mount                                                              |

| Package / Case             | 28-SSOP (0.209", 5.30mm Width)                                             |

| Supplier Device Package    | 28-SSOP                                                                    |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16f876at-i-ss |

|                            |                                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# **Table of Contents**

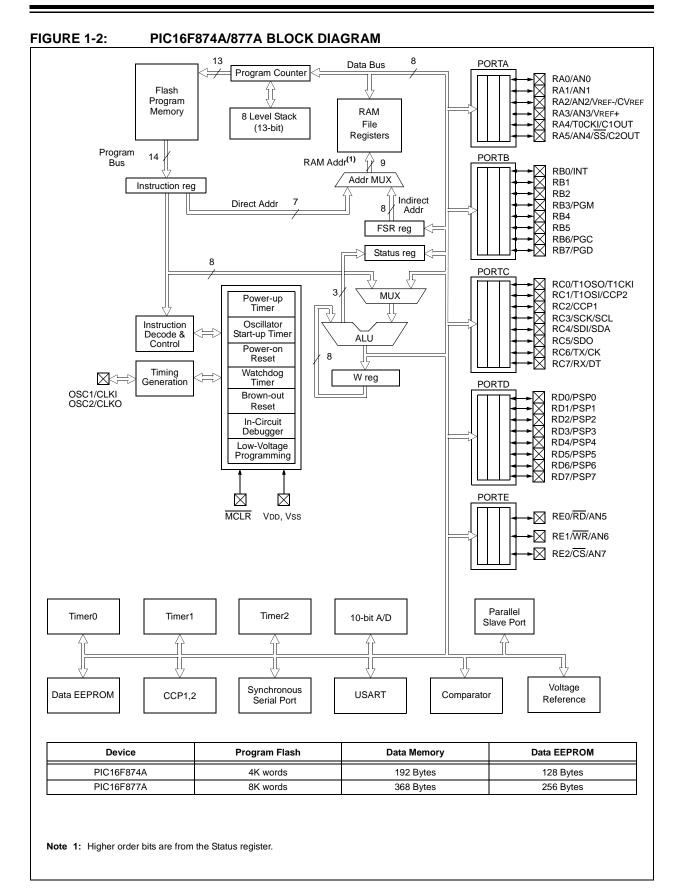

| 1.0   | Device Overview                                                             | 5    |

|-------|-----------------------------------------------------------------------------|------|

| 2.0   | Memory Organization                                                         | . 15 |

| 3.0   | Data EEPROM and Flash Program Memory                                        | . 33 |

| 4.0   | I/O Ports                                                                   | . 41 |

| 5.0   | Timer0 Module                                                               | . 53 |

| 6.0   | Timer1 Module                                                               | . 57 |

| 7.0   | Timer2 Module                                                               | . 61 |

| 8.0   | Capture/Compare/PWM Modules                                                 | . 63 |

| 9.0   | Master Synchronous Serial Port (MSSP) Module                                |      |

| 10.0  | Addressable Universal Synchronous Asynchronous Receiver Transmitter (USART) |      |

| 11.0  | Analog-to-Digital Converter (A/D) Module                                    | 127  |

| 12.0  | Comparator Module                                                           | 135  |

| 13.0  | Comparator Voltage Reference Module                                         | 141  |

| 14.0  | Special Features of the CPU                                                 | 143  |

| 15.0  | Instruction Set Summary                                                     | 159  |

| 16.0  | Development Support                                                         | 167  |

| 17.0  | Electrical Characteristics                                                  |      |

| 18.0  | DC and AC Characteristics Graphs and Tables                                 | 197  |

| 19.0  | Packaging Information                                                       | 209  |

| Apper | ndix A: Revision History                                                    | 219  |

| Apper | ndix B: Device Differences                                                  | 219  |

| Apper | ndix C: Conversion Considerations                                           | 220  |

| Index |                                                                             | 221  |

| On-Li | ne Support                                                                  | 229  |

| Syste | ms Information and Upgrade Hot Line                                         | 229  |

| Read  | er Response                                                                 | 230  |

| PIC16 | SF87XA Product Identification System                                        | 231  |

# TO OUR VALUED CUSTOMERS

It is our intention to provide our valued customers with the best documentation possible to ensure successful use of your Microchip products. To this end, we will continue to improve our publications to better suit your needs. Our publications will be refined and enhanced as new volumes and updates are introduced.

If you have any questions or comments regarding this publication, please contact the Marketing Communications Department via E-mail at **docerrors@mail.microchip.com** or fax the **Reader Response Form** in the back of this data sheet to (480) 792-4150. We welcome your feedback.

# Most Current Data Sheet

To obtain the most up-to-date version of this data sheet, please register at our Worldwide Web site at:

http://www.microchip.com

You can determine the version of a data sheet by examining its literature number found on the bottom outside corner of any page. The last character of the literature number is the version number, (e.g., DS30000A is version A of document DS30000).

#### Errata

An errata sheet, describing minor operational differences from the data sheet and recommended workarounds, may exist for current devices. As device/documentation issues become known to us, we will publish an errata sheet. The errata will specify the revision of silicon and revision of document to which it applies.

To determine if an errata sheet exists for a particular device, please check with one of the following:

- Microchip's Worldwide Web site; http://www.microchip.com

- Your local Microchip sales office (see last page)

- The Microchip Corporate Literature Center; U.S. FAX: (480) 792-7277

When contacting a sales office or the literature center, please specify which device, revision of silicon and data sheet (include literature number) you are using.

# **Customer Notification System**

Register on our Web site at www.microchip.com/cn to receive the most current information on all of our products.

# 2.2 Data Memory Organization

The data memory is partitioned into multiple banks which contain the General Purpose Registers and the Special Function Registers. Bits RP1 (Status<6>) and RP0 (Status<5>) are the bank select bits.

| RP1:RP0 | Bank |

|---------|------|

| 00      | 0    |

| 01      | 1    |

| 10      | 2    |

| 11      | 3    |

Each bank extends up to 7Fh (128 bytes). The lower locations of each bank are reserved for the Special Function Registers. Above the Special Function Registers are General Purpose Registers, implemented as static RAM. All implemented banks contain Special Function Registers. Some frequently used Special Function Registers from one bank may be mirrored in another bank for code reduction and quicker access.

| Note: | The EEPROM data memory description can |

|-------|----------------------------------------|

|       | be found in Section 3.0 "Data EEPROM   |

|       | and Flash Program Memory" of this data |

|       | sheet.                                 |

#### 2.2.1 GENERAL PURPOSE REGISTER FILE

The register file can be accessed either directly, or indirectly, through the File Select Register (FSR).

#### 2.2.2.2 OPTION\_REG Register

The OPTION\_REG Register is a readable and writable register, which contains various control bits to configure the TMR0 prescaler/WDT postscaler (single assignable register known also as the prescaler), the external INT interrupt, TMR0 and the weak pull-ups on PORTB.

**Note:** To achieve a 1:1 prescaler assignment for the TMR0 register, assign the prescaler to the Watchdog Timer.

|         | ••••••                                                                                                                                                                      |                                |                  |               | ,,                |             |              |          |

|---------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------|------------------|---------------|-------------------|-------------|--------------|----------|

|         | R/W-1                                                                                                                                                                       | R/W-1                          | R/W-1            | R/W-1         | R/W-1             | R/W-1       | R/W-1        | R/W-1    |

|         | RBPU                                                                                                                                                                        | INTEDG                         | TOCS             | TOSE          | PSA               | PS2         | PS1          | PS0      |

|         | bit 7                                                                                                                                                                       |                                |                  |               |                   |             |              | bit 0    |

|         |                                                                                                                                                                             |                                |                  |               |                   |             |              |          |

| bit 7   |                                                                                                                                                                             | DRTB Pull-up                   |                  |               |                   |             |              |          |

|         |                                                                                                                                                                             | B pull-ups ar                  |                  | ov individual | port latch value  | 26          |              |          |

| bit 6   |                                                                                                                                                                             | nterrupt Edg                   |                  | •             | port lateri value |             |              |          |

| DIL U   |                                                                                                                                                                             | pt on rising e                 |                  |               |                   |             |              |          |

|         |                                                                                                                                                                             | pt on falling                  |                  |               |                   |             |              |          |

| bit 5   | TOCS: TM                                                                                                                                                                    | R0 Clock So                    | urce Select      | t bit         |                   |             |              |          |

|         |                                                                                                                                                                             | tion on RA4/                   |                  |               |                   |             |              |          |

|         | 0 = Interna                                                                                                                                                                 | al instruction                 | cycle clock      | (CLKO)        |                   |             |              |          |

| bit 4   |                                                                                                                                                                             | R0 Source E                    | •                |               |                   |             |              |          |

|         |                                                                                                                                                                             | nent on high-                  |                  |               |                   |             |              |          |

| hit 0   |                                                                                                                                                                             | nent on low-t                  |                  | Sition on RA  | 4/TUCKI pin       |             |              |          |

| bit 3   |                                                                                                                                                                             | caler Assign<br>aler is assign |                  |               |                   |             |              |          |

|         |                                                                                                                                                                             | aler is assign                 |                  |               | le                |             |              |          |

| bit 2-0 | <b>PS2:PS0</b> : Prescaler Rate Select bits                                                                                                                                 |                                |                  |               |                   |             |              |          |

|         | Bit Value                                                                                                                                                                   | TMR0 Rate                      | WDT Rate         | e             |                   |             |              |          |

|         | 000                                                                                                                                                                         | 1:2                            | 1:1              |               |                   |             |              |          |

|         | 001<br>010                                                                                                                                                                  | 1:4                            | 1:2<br>1:4       |               |                   |             |              |          |

|         | 010                                                                                                                                                                         | 1:8<br>1:16                    | 1:8              |               |                   |             |              |          |

|         | 100<br>101                                                                                                                                                                  | 1:32                           | 1 : 16<br>1 : 32 |               |                   |             |              |          |

|         | 110                                                                                                                                                                         | 1:64<br>1:128                  | 1:64             |               |                   |             |              |          |

|         | 111                                                                                                                                                                         | 1 : 256                        | 1 : 128          |               |                   |             |              |          |

|         | 1                                                                                                                                                                           |                                |                  |               |                   |             |              | 1        |

|         | Legend:                                                                                                                                                                     |                                | 10/ 1/           |               |                   |             | :            | 21       |

|         | R = Readable bit $W$ = Writable bit $U$ = Unimplemented bit, read as '0'<br>n = Volue at POP (1' = Pit is set (0' = Pit is cleared v = Pit is upknown)                      |                                |                  |               |                   |             |              |          |

|         | - n = Value at POR $(1)^2$ = Bit is set $(0)^2$ = Bit is cleared x = Bit is unknown                                                                                         |                                |                  |               |                   |             | IKNOWN       |          |

|         | Note:                                                                                                                                                                       | When using                     | I ow-Volta       | ne ICSP Pro   | gramming (LVP     | ) and the n | ull-ups on F | ORTR are |

|         | <b>Note:</b> When using Low-Voltage ICSP Programming (LVP) and the pull-ups on PORTB are enabled, bit 3 in the TRISB register must be cleared to disable the pull-up on RB3 |                                |                  |               |                   |             |              |          |

|         |                                                                                                                                                                             | and ensure                     | the proper       | operation of  | the device        |             |              |          |

#### **REGISTER 2-2: OPTION\_REG REGISTER (ADDRESS 81h, 181h)**

# PIC16F87XA

NOTES:

# PIC16F87XA

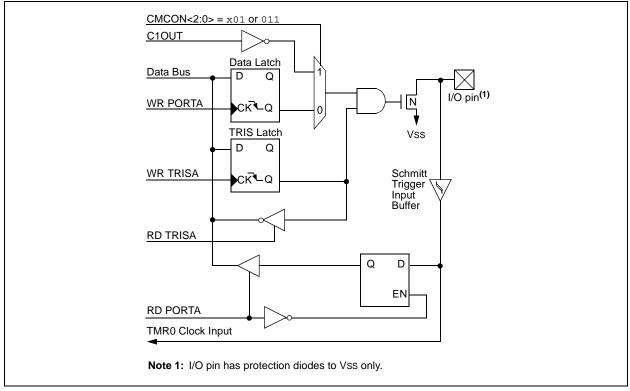

#### FIGURE 4-2: BLOCK DIAGRAM OF RA4/T0CKI PIN

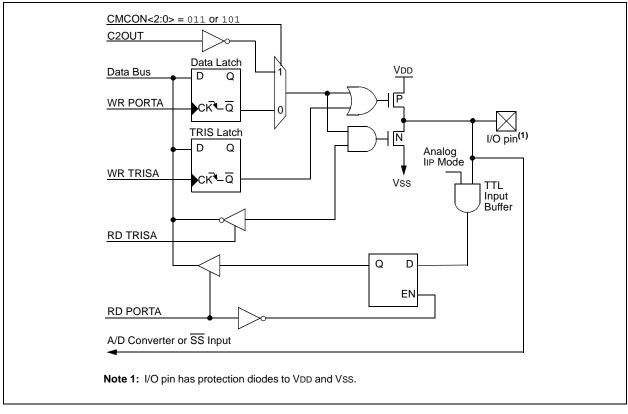

#### FIGURE 4-3: BLOCK DIAGRAM OF RA5 PIN

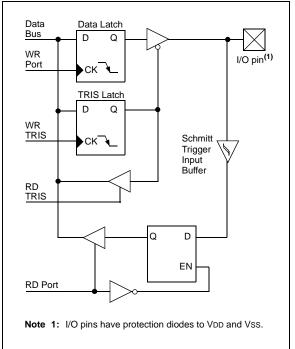

#### 4.5 PORTE and TRISE Register

| Note: | PORTE and TRISE are not implemented |

|-------|-------------------------------------|

|       | on the 28-pin devices.              |

PORTE has three pins (RE0/RD/AN5, RE1/WR/AN6 and RE2/CS/AN7) which are individually configurable as inputs or outputs. These pins have Schmitt Trigger input buffers.

The PORTE pins become the I/O control inputs for the microprocessor port when bit PSPMODE (TRISE<4>) is set. In this mode, the user must make certain that the TRISE<2:0> bits are set and that the pins are configured as digital inputs. Also, ensure that ADCON1 is configured for digital I/O. In this mode, the input buffers are TTL.

Register 4-1 shows the TRISE register which also controls the Parallel Slave Port operation.

PORTE pins are multiplexed with analog inputs. When selected for analog input, these pins will read as '0's.

TRISE controls the direction of the RE pins, even when they are being used as analog inputs. The user must make sure to keep the pins configured as inputs when using them as analog inputs.

Note: On a Power-on Reset, these pins are configured as analog inputs and read as '0'.

#### TABLE 4-9: PORTE FUNCTIONS

#### FIGURE 4-9:

#### PORTE BLOCK DIAGRAM (IN I/O PORT MODE)

| Name       | Bit#  | Buffer Type                                                                                                                                                                                                                     | Function                                                                                                                                                                                                                                   |  |

|------------|-------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| RE0/RD/AN5 | bit 0 | ST/TTL <sup>(1)</sup>                                                                                                                                                                                                           | <ul> <li>I/O port pin or read control input in Parallel Slave Port mode or analog input:</li> <li>RD</li> <li>1 = Idle</li> <li>0 = Read operation. Contents of PORTD register are output to PORTD I/O pins (if chip selected).</li> </ul> |  |

| RE1/WR/AN6 | bit 1 | ST/TTL <sup>(1)</sup> I/O port pin or write control input in Parallel Slave Port mode or analog input WR         1 = Idle       0 = Write operation. Value of PORTD I/O pins is latched into PORTD register (if chip selected). |                                                                                                                                                                                                                                            |  |

| RE2/CS/AN7 | bit 2 | ST/TTL <sup>(1)</sup>                                                                                                                                                                                                           | <ul> <li>I/O port pin or chip select control input in Parallel Slave Port mode or analog input:</li> <li>CS</li> <li>1 = Device is not selected</li> <li>0 = Device is selected</li> </ul>                                                 |  |

Legend: ST = Schmitt Trigger input, TTL = TTL input

Note 1: Input buffers are Schmitt Triggers when in I/O mode and TTL buffers when in Parallel Slave Port mode.

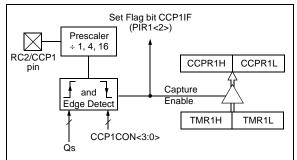

# 8.1 Capture Mode

In Capture mode, CCPR1H:CCPR1L captures the 16-bit value of the TMR1 register when an event occurs on pin RC2/CCP1. An event is defined as one of the following:

- Every falling edge

- Every rising edge

- Every 4th rising edge

- · Every 16th rising edge

The type of event is configured by control bits, CCP1M3:CCP1M0 (CCPxCON<3:0>). When a capture is made, the interrupt request flag bit, CCP1IF (PIR1<2>), is set. The interrupt flag must be cleared in software. If another capture occurs before the value in register CCPR1 is read, the old captured value is overwritten by the new value.

#### 8.1.1 CCP PIN CONFIGURATION

In Capture mode, the RC2/CCP1 pin should be configured as an input by setting the TRISC<2> bit.

| Note: If | the RC2/CCP1 pin is configured as an                     |

|----------|----------------------------------------------------------|

|          | utput, a write to the port can cause a apture condition. |

#### FIGURE 8-1: CAPTURE MODE OPERATION BLOCK DIAGRAM

#### 8.1.2 TIMER1 MODE SELECTION

Timer1 must be running in Timer mode, or Synchronized Counter mode, for the CCP module to use the capture feature. In Asynchronous Counter mode, the capture operation may not work.

#### 8.1.3 SOFTWARE INTERRUPT

When the Capture mode is changed, a false capture interrupt may be generated. The user should keep bit CCP1IE (PIE1<2>) clear to avoid false interrupts and should clear the flag bit, CCP1IF, following any such change in operating mode.

#### 8.1.4 CCP PRESCALER

There are four prescaler settings, specified by bits CCP1M3:CCP1M0. Whenever the CCP module is turned off, or the CCP module is not in Capture mode, the prescaler counter is cleared. Any Reset will clear the prescaler counter.

Switching from one capture prescaler to another may generate an interrupt. Also, the prescaler counter will not be cleared, therefore, the first capture may be from a non-zero prescaler. Example 8-1 shows the recommended method for switching between capture prescalers. This example also clears the prescaler counter and will not generate the "false" interrupt.

#### EXAMPLE 8-1: CHANGING BETWEEN CAPTURE PRESCALERS

| CLRF  | CCP1CON     | ;   | Turn CCP module off                                                |

|-------|-------------|-----|--------------------------------------------------------------------|

| MOVLW | NEW_CAPT_PS | ;   | Load the W reg with                                                |

|       |             | ;   | the new prescaler                                                  |

|       |             | ;   | move value and CCP ON                                              |

| MOVWF | CCP1CON     | ;   | Load CCP1CON with this                                             |

|       |             | ;   | value                                                              |

|       |             | ;;; | the new prescaler<br>move value and CCP O<br>Load CCPICON with the |

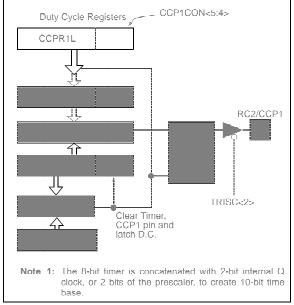

# 8.3 PWM Mode (PWM)

In Pulse Width Modulation mode, the CCPx pin produces up to a 10-bit resolution PWM output. Since the CCP1 pin is multiplexed with the PORTC data latch, the TRISC<2> bit must be cleared to make the CCP1 pin an output.

| Note: | Clearing the CCP1CON register will force  |

|-------|-------------------------------------------|

|       | the CCP1 PWM output latch to the default  |

|       | low level. This is not the PORTC I/O data |

|       | latch.                                    |

Figure 8-3 shows a simplified block diagram of the CCP module in PWM mode.

For a step-by-step procedure on how to set up the CCP module for PWM operation, see **Section 8.3.3 "Setup for PWM Operation**".

| FIGURE 8-3: | SIMPLIFIED PWM BLOCK |

|-------------|----------------------|

|             | DIAGRAM              |

|             |                      |

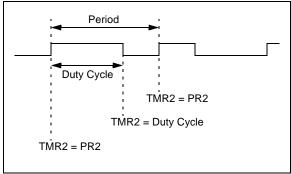

A PWM output (Figure 8-4) has a time base (period) and a time that the output stays high (duty cycle). The frequency of the PWM is the inverse of the period (1/period).

#### 8.3.1 PWM PERIOD

The PWM period is specified by writing to the PR2 register. The PWM period can be calculated using the following formula:

$PWM Period = [(PR2) + 1] \bullet 4 \bullet TOSC \bullet$ (TMR2 Prescale Value)

PWM frequency is defined as 1/[PWM period].

When TMR2 is equal to PR2, the following three events occur on the next increment cycle:

- TMR2 is cleared

- The CCP1 pin is set (exception: if PWM duty cycle = 0%, the CCP1 pin will not be set)

- The PWM duty cycle is latched from CCPR1L into CCPR1H

| Note: | The Timer2 postscaler (see Section 7.1     |

|-------|--------------------------------------------|

|       | "Timer2 Prescaler and Postscaler") is      |

|       | not used in the determination of the PWM   |

|       | frequency. The postscaler could be used    |

|       | to have a servo update rate at a different |

|       | frequency than the PWM output.             |

#### 8.3.2 PWM DUTY CYCLE

The PWM duty cycle is specified by writing to the CCPR1L register and to the CCP1CON<5:4> bits. Up to 10-bit resolution is available. The CCPR1L contains the eight MSbs and the CCP1CON<5:4> contains the two LSbs. This 10-bit value is represented by CCPR1L:CCP1CON<5:4>. The following equation is used to calculate the PWM duty cycle in time:

```

PWM Duty Cycle =(CCPR1L:CCP1CON<5:4>)•

Tosc • (TMR2 Prescale Value)

```

CCPR1L and CCP1CON<5:4> can be written to at any time, but the duty cycle value is not latched into CCPR1H until after a match between PR2 and TMR2 occurs (i.e., the period is complete). In PWM mode, CCPR1H is a read-only register.

The CCPR1H register and a 2-bit internal latch are used to double-buffer the PWM duty cycle. This double-buffering is essential for glitch-free PWM operation.

When the CCPR1H and 2-bit latch match TMR2, concatenated with an internal 2-bit Q clock or 2 bits of the TMR2 prescaler, the CCP1 pin is cleared.

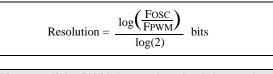

The maximum PWM resolution (bits) for a given PWM frequency is given by the following formula.

#### **EQUATION 8-1:**

**Note:** If the PWM duty cycle value is longer than the PWM period, the CCP1 pin will not be cleared.

#### 9.3.1 REGISTERS

The MSSP module has four registers for SPI mode operation. These are:

- MSSP Control Register (SSPCON)

- MSSP Status Register (SSPSTAT)

- Serial Receive/Transmit Buffer Register (SSPBUF)

- MSSP Shift Register (SSPSR) Not directly accessible

SSPCON and SSPSTAT are the control and status registers in SPI mode operation. The SSPCON register is readable and writable. The lower six bits of the SSPSTAT are read-only. The upper two bits of the SSPSTAT are read/write. SSPSR is the shift register used for shifting data in or out. SSPBUF is the buffer register to which data bytes are written to or read from.

In receive operations, SSPSR and SSPBUF together create a double-buffered receiver. When SSPSR receives a complete byte, it is transferred to SSPBUF and the SSPIF interrupt is set.

During transmission, the SSPBUF is not doublebuffered. A write to SSPBUF will write to both SSPBUF and SSPSR.

#### REGISTER 9-1: SSPSTAT: MSSP STATUS REGISTER (SPI MODE) (ADDRESS 94h)

|       | R/W-0                                | R/W-0         | R-0             | R-0          | R-0           | R-0           | R-0          | R-0           |  |

|-------|--------------------------------------|---------------|-----------------|--------------|---------------|---------------|--------------|---------------|--|

|       | SMP                                  | CKE           | D/A             | Р            | S             | R/W           | UA           | BF            |  |

|       | bit 7                                |               |                 |              |               |               |              | bit 0         |  |

| bit 7 | SMP: Sam                             | ple bit       |                 |              |               |               |              |               |  |

|       | SPI Master                           |               |                 |              |               |               |              |               |  |

|       |                                      | ata sampled   |                 |              |               |               |              |               |  |

|       |                                      | ata sampled   | at middle o     | r data outpu | tume          |               |              |               |  |

|       | SMP must                             | be cleared v  | when SPI is     | used in Slav | ve mode       |               |              |               |  |

| bit 6 |                                      | Clock Select  |                 |              | o modo.       |               |              |               |  |

|       | 1 = Transm                           | nit occurs on | transition fr   | om active to | ldle clock s  | state         |              |               |  |

|       | 0 = Transm                           | nit occurs on | transition fr   | om Idle to a | ctive clock s | state         |              |               |  |

|       | Note:                                | Polarity of o | clock state is  | s set by the | CKP bit (SS   | PCON1<4>      | ).           |               |  |

| bit 5 | D/A: Data/                           | Address bit   |                 |              |               |               |              |               |  |

|       | Used in I <sup>2</sup> C             | c mode only.  |                 |              |               |               |              |               |  |

| bit 4 | P: Stop bit                          |               |                 |              |               |               |              |               |  |

|       | Used in I <sup>2</sup> C             | mode only.    | This bit is cle | ared when t  | he MSSP me    | odule is disa | bled, SSPEI  | N is cleared. |  |

| bit 3 | S: Start bit                         |               |                 |              |               |               |              |               |  |

|       | Used in I <sup>2</sup> C             | c mode only.  |                 |              |               |               |              |               |  |

| bit 2 | R/W: Read/Write bit information      |               |                 |              |               |               |              |               |  |

|       | Used in I <sup>2</sup> C             | c mode only.  |                 |              |               |               |              |               |  |

| bit 1 | UA: Update                           | e Address b   | it              |              |               |               |              |               |  |

|       | Used in I <sup>2</sup> C             | c mode only.  |                 |              |               |               |              |               |  |

| bit 0 | BF: Buffer                           | Full Status b | oit (Receive    | mode only)   |               |               |              |               |  |

|       | 1 = Receive complete, SSPBUF is full |               |                 |              |               |               |              |               |  |

|       | 0 = Receiv                           | e not comple  | ete, SSPBU      | F is empty   |               |               |              |               |  |

|       | Legend:                              |               |                 |              |               |               |              |               |  |

|       | R = Reada                            | ble bit       | W = W           | ritable bit  | U = Unim      | plemented     | bit, read as | '0'           |  |

|       | - n = Value                          | at POR        | '1' = B         | it is set    | '0' = Bit i   | s cleared     | x = Bit is ι | Inknown       |  |

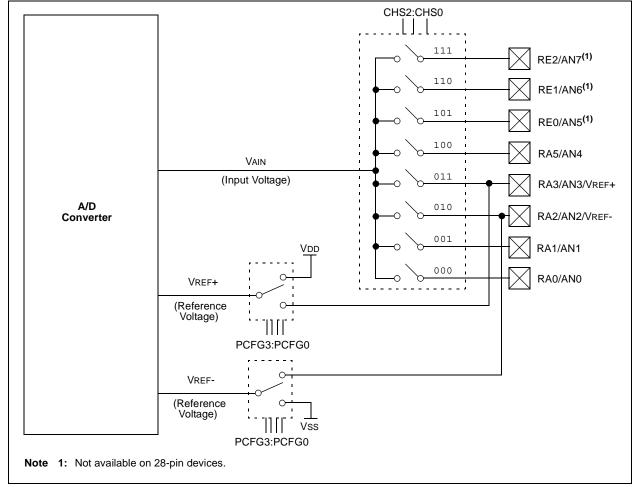

The ADRESH:ADRESL registers contain the 10-bit result of the A/D conversion. When the A/D conversion is complete, the result is loaded into this A/D Result register pair, the GO/DONE bit (ADCON0<2>) is cleared and the A/D interrupt flag bit ADIF is set. The block diagram of the A/D module is shown in Figure 11-1.

After the A/D module has been configured as desired, the selected channel must be acquired before the conversion is started. The analog input channels must have their corresponding TRIS bits selected as inputs.

To determine sample time, see **Section 11.1 "A/D Acquisition Requirements"**. After this acquisition time has elapsed, the A/D conversion can be started.

To do an A/D Conversion, follow these steps:

- 1. Configure the A/D module:

- Configure analog pins/voltage reference and digital I/O (ADCON1)

- Select A/D input channel (ADCON0)

- Select A/D conversion clock (ADCON0)

- Turn on A/D module (ADCON0)

- 2. Configure A/D interrupt (if desired):

- Clear ADIF bit

- Set ADIE bit

- Set PEIE bit

- Set GIE bit

- 3. Wait the required acquisition time.

- 4. Start conversion:

- Set GO/DONE bit (ADCON0)

- 5. Wait for A/D conversion to complete by either:

- Polling for the GO/DONE bit to be cleared (interrupts disabled); OR

- Waiting for the A/D interrupt

- 6. Read A/D Result register pair (ADRESH:ADRESL), clear bit ADIF if required.

- 7. For the next conversion, go to step 1 or step 2 as required. The A/D conversion time per bit is defined as TAD.

# FIGURE 11-1: A/D BLOCK DIAGRAM

### 11.1 A/D Acquisition Requirements

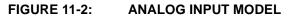

For the A/D converter to meet its specified accuracy, the charge holding capacitor (CHOLD) must be allowed to fully charge to the input channel voltage level. The analog input model is shown in Figure 11-2. The source impedance (Rs) and the internal sampling switch impedance (Rss) directly affect the time required to charge the capacitor CHOLD. The sampling switch (Rss) impedance varies over the device voltage (VDD); see Figure 11-2. The maximum recommended impedance for analog sources is 2.5 k $\Omega$ . As the impedance is decreased, the acquisition time may be

#### EQUATION 11-1: ACQUISITION TIME

decreased. After the analog input channel is selected (changed), this acquisition must be done before the conversion can be started.

To calculate the minimum acquisition time, Equation 11-1 may be used. This equation assumes that 1/2 LSb error is used (1024 steps for the A/D). The 1/2 LSb error is the maximum error allowed for the A/D to meet its specified resolution.

To calculate the minimum acquisition time, TACQ, see the PIC<sup>®</sup> Mid-Range MCU Family Reference Manual (DS33023).

| TACQ | = Amplifier Settling Time + Hold Capacitor Charging Time + Temperature Coefficient                                                                                                                                                                                |

|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Тс   | = TAMP + TC + TCOFF<br>= $2 \mu s + TC + [(Temperature - 25^{\circ}C)(0.05 \mu s/^{\circ}C)]$<br>= CHOLD (RIC + RSs + RS) In(1/2047)<br>= $-120 \text{ pF} (1 \text{ k}\Omega + 7 \text{ k}\Omega + 10 \text{ k}\Omega) \text{ In}(0.0004885)$<br>= $16.47 \mu s$ |

| TACQ | = $2 \ \mu s + 16.47 \ \mu s + [(50^{\circ}C - 25^{\circ}C)(0.05 \ \mu s/^{\circ}C)]$<br>= $19.72 \ \mu s$                                                                                                                                                        |

Note 1: The reference voltage (VREF) has no effect on the equation since it cancels itself out.

- 2: The charge holding capacitor (CHOLD) is not discharged after each conversion.

- **3:** The maximum recommended impedance for analog sources is 2.5 k $\Omega$ . This is required to meet the pin leakage specification.

# TABLE 14-2:CAPACITOR SELECTION FOR<br/>CRYSTAL OSCILLATOR

| Osc Type | Crystal<br>Freq. | Cap. Range<br>C1 | Cap. Range<br>C2 |

|----------|------------------|------------------|------------------|

| LP       | 32 kHz           | 33 pF            | 33 pF            |

|          | 200 kHz          | 15 pF            | 15 pF            |

| XT       | 200 kHz          | 47-68 pF         | 47-68 pF         |

|          | 1 MHz            | 15 pF            | 15 pF            |

|          | 4 MHz            | 15 pF            | 15 pF            |

| HS       | 4 MHz            | 15 pF            | 15 pF            |

|          | 8 MHz            | 15-33 pF         | 15-33 pF         |

|          | 20 MHz           | 15-33 pF         | 15-33 pF         |

**These values are for design guidance only.** See notes following this table.

| Crystals Used |                        |          |  |  |  |  |  |

|---------------|------------------------|----------|--|--|--|--|--|

| 32 kHz        | Epson C-001R32.768K-A  | ± 20 PPM |  |  |  |  |  |

| 200 kHz       | STD XTL 200.000KHz     | ± 20 PPM |  |  |  |  |  |

| 1 MHz         | ECS ECS-10-13-1        | ± 50 PPM |  |  |  |  |  |

| 4 MHz         | ECS ECS-40-20-1        | ± 50 PPM |  |  |  |  |  |

| 8 MHz         | EPSON CA-301 8.000M-C  | ± 30 PPM |  |  |  |  |  |

| 20 MHz        | EPSON CA-301 20.000M-C | ± 30 PPM |  |  |  |  |  |

- Note 1: Higher capacitance increases the stability of oscillator but also increases the start-up time.

- 2: Since each resonator/crystal has its own characteristics, the user should consult the resonator/crystal manufacturer for appropriate values of external components.

- **3:** *R*<sub>s</sub> may be required in HS mode, as well as XT mode, to avoid overdriving crystals with low drive level specification.

- When migrating from other PIC<sup>®</sup> devices, oscillator performance should be verified.

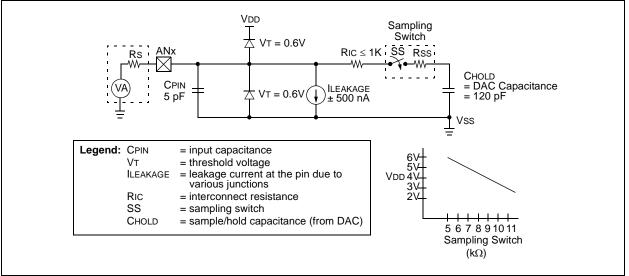

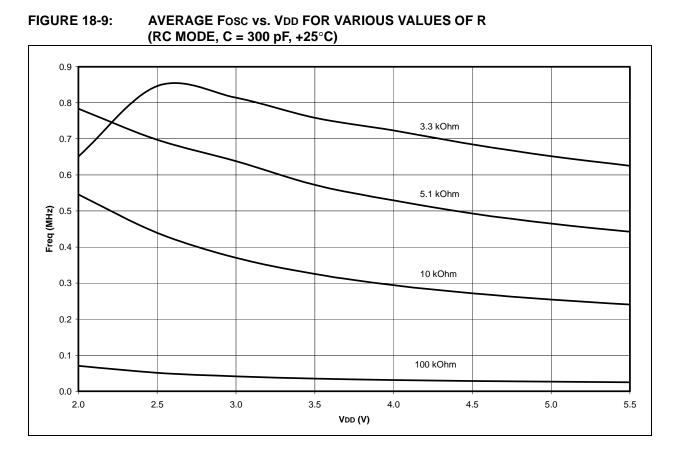

# 14.2.3 RC OSCILLATOR

For timing insensitive applications, the "RC" device option offers additional cost savings. The RC oscillator frequency is a function of the supply voltage, the resistor (REXT) and capacitor (CEXT) values and the operating temperature. In addition to this, the oscillator frequency will vary from unit to unit due to normal process parameter variation. Furthermore, the difference in lead frame capacitance between package types will also affect the oscillation frequency, especially for low CEXT values. The user also needs to take into account variation due to tolerance of external R and C components used. Figure 14-3 shows how the R/C combination is connected to the PIC16F87XA.

| TABLE 15-2: PIC16 | F87XA INSTRUCTION SET |

|-------------------|-----------------------|

|-------------------|-----------------------|

| Mnem     | ionic, | Description                                    | Cycles        |       | 14-Bit | Status | Notes |          |       |  |

|----------|--------|------------------------------------------------|---------------|-------|--------|--------|-------|----------|-------|--|

| Operands |        | Description                                    | Cycles        | MSb   |        |        | LSb   | Affected | Notes |  |

|          |        | BYTE-ORIENTED FILE                             | EREGISTER OPE | RATIC | NS     |        |       |          |       |  |

| ADDWF    | f, d   | Add W and f                                    | 1             | 00    | 0111   | dfff   | ffff  | C,DC,Z   | 1,2   |  |

| ANDWF    | f, d   | AND W with f                                   | 1             | 00    | 0101   | dfff   | ffff  | Z        | 1,2   |  |

| CLRF     | f      | Clear f                                        | 1             | 00    | 0001   | lfff   | ffff  | Z        | 2     |  |

| CLRW     | -      | Clear W                                        | 1             | 00    | 0001   | 0xxx   | xxxx  | Z        |       |  |

| COMF     | f, d   | Complement f                                   | 1             | 00    | 1001   | dfff   | ffff  | Z        | 1,2   |  |

| DECF     | f, d   | Decrement f                                    | 1             | 00    | 0011   | dfff   | ffff  | Z        | 1,2   |  |

| DECFSZ   | f, d   | Decrement f, Skip if 0                         | 1(2)          | 00    | 1011   | dfff   | ffff  |          | 1,2,3 |  |

| INCF     | f, d   | Increment f                                    | 1             | 00    | 1010   | dfff   | ffff  | Z        | 1,2   |  |

| INCFSZ   | f, d   | Increment f, Skip if 0                         | 1(2)          | 00    | 1111   | dfff   | ffff  |          | 1,2,3 |  |

| IORWF    | f, d   | Inclusive OR W with f                          | 1             | 00    | 0100   | dfff   | ffff  | Z        | 1,2   |  |

| MOVF     | f, d   | Move f                                         | 1             | 00    | 1000   | dfff   | ffff  | Z        | 1,2   |  |

| MOVWF    | f      | Move W to f                                    | 1             | 00    | 0000   | lfff   | ffff  |          |       |  |

| NOP      | -      | No Operation                                   | 1             | 00    | 0000   | 0xx0   | 0000  |          |       |  |

| RLF      | f, d   | Rotate Left f through Carry                    | 1             | 00    | 1101   | dfff   | ffff  | С        | 1,2   |  |

| RRF      | f, d   | Rotate Right f through Carry                   | 1             | 00    | 1100   | dfff   | ffff  | С        | 1,2   |  |

| SUBWF    | f, d   | Subtract W from f                              | 1             | 00    | 0010   | dfff   | ffff  | C,DC,Z   | 1,2   |  |

| SWAPF    | f, d   | Swap nibbles in f                              | 1             | 00    | 1110   | dfff   | ffff  |          | 1,2   |  |

| XORWF    | f, d   | Exclusive OR W with f                          | 1             | 00    | 0110   | dfff   | ffff  | Z        | 1,2   |  |

|          |        | BIT-ORIENTED FILE                              |               | ATIO  | NS     |        |       |          |       |  |

| BCF      | f, b   | Bit Clear f                                    | 1             | 01    | 00bb   | bfff   | ffff  |          | 1,2   |  |

| BSF      | f, b   | Bit Set f                                      | 1             | 01    |        | bfff   |       |          | 1,2   |  |

| BTFSC    | f, b   | Bit Test f, Skip if Clear                      | 1 (2)         | 01    | 10bb   | bfff   |       |          | 3     |  |

| BTFSS    | f, b   | Bit Test f, Skip if Set                        | 1 (2)         | 01    | 11bb   | bfff   | ffff  |          | 3     |  |

|          | ,      | LITERAL AND CO                                 | ( )           | IONS  |        |        |       |          |       |  |

| ADDLW    | k      | Add Literal and W                              | 1             | 11    | 111x   | kkkk   | kkkk  | C,DC,Z   |       |  |

| ANDLW    | k      | AND Literal with W                             | 1             | 11    | 1001   | kkkk   | kkkk  | Z        |       |  |

| CALL     | k      | Call Subroutine                                | 2             | 10    | 0kkk   | kkkk   | kkkk  |          |       |  |

| CLRWDT   | -      | Clear Watchdog Timer                           | 1             | 00    | 0000   | 0110   | 0100  | TO,PD    |       |  |

| GOTO     | k      | Go to Address                                  | 2             | 10    | 1kkk   | kkkk   | kkkk  | -        |       |  |

| IORLW    | k      | Inclusive OR Literal with W                    | 1             | 11    | 1000   | kkkk   | kkkk  | Z        |       |  |

| MOVLW    | k      | Move Literal to W                              | 1             | 11    | 00xx   | kkkk   | kkkk  |          |       |  |

| RETFIE   | -      | Return from Interrupt                          | 2             | 00    | 0000   | 0000   | 1001  |          |       |  |

| RETLW    | k      | Return with Literal in W                       | 2             | 11    | 01xx   | kkkk   |       |          |       |  |

| RETURN   | -      | Return from Subroutine                         | 2             | 00    | 0000   | 0000   | 1000  |          |       |  |

| SLEEP    | -      | Go into Standby mode                           | 1             | 00    | 0000   | 0110   | 0011  | TO,PD    |       |  |

| SUBLW    | k      | Subtract W from Literal                        | 1             | 11    |        | kkkk   |       | C,DC,Z   |       |  |

| XORLW    | k      | Exclusive OR Literal with W                    | 1             | 11    | 1010   | kkkk   |       | Z        |       |  |

| Note 1:  |        | I/O register is modified as a function of itse |               |       |        |        |       |          |       |  |

Note 1: When an I/O register is modified as a function of itself (e.g., MOVF PORTE, 1), the value used will be that value present on the pins themselves. For example, if the data latch is '1' for a pin configured as input and is driven low by an external device, the data will be written back with a '0'.

2: If this instruction is executed on the TMR0 register (and where applicable, d = 1), the prescaler will be cleared if assigned to the Timer0 module.

3: If Program Counter (PC) is modified, or a conditional test is true, the instruction requires two cycles. The second cycle is executed as a NOP.

**Note:** Additional information on the mid-range instruction set is available in the PIC<sup>®</sup> Mid-Range MCU Family Reference Manual (DS33023).

### 17.1 DC Characteristics: PIC16F873A/874A/876A/877A (Industrial, Extended) PIC16LF873A/874A/876A/877A (Industrial) (Continued)

| PIC16LF873A/874A/876A/877A<br>(Industrial)<br>PIC16F873A/874A/876A/877A<br>(Industrial, Extended) |               |                                           | Standard Operating Conditions (unless otherwise stated)Operating temperature $-40^{\circ}C \le TA \le +85^{\circ}C$ for industrial                                                      |                               |     |    |                                                                     |  |  |

|---------------------------------------------------------------------------------------------------|---------------|-------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------|-----|----|---------------------------------------------------------------------|--|--|

|                                                                                                   |               |                                           | Standard Operating Conditions (unless otherwise stated)Operating temperature $-40^{\circ}C \le TA \le +85^{\circ}C$ for industrial $-40^{\circ}C \le TA \le +125^{\circ}C$ for extended |                               |     |    |                                                                     |  |  |

| Param<br>No.                                                                                      | Symbol        | Characteristic/<br>Device                 | Min                                                                                                                                                                                     | Min Typ† Max Units Conditions |     |    |                                                                     |  |  |

|                                                                                                   | Idd           | Supply Current <sup>(2,5)</sup>           |                                                                                                                                                                                         |                               |     |    |                                                                     |  |  |

| D010                                                                                              |               | 16LF87XA                                  | _                                                                                                                                                                                       | 0.6                           | 2.0 | mA | XT, RC osc configurations,<br>Fosc = 4 MHz, VDD = 3.0V              |  |  |

| D010                                                                                              |               | 16F87XA                                   | —                                                                                                                                                                                       | 1.6                           | 4   | mA | XT, RC osc configurations,<br>Fosc = 4 MHz, VDD = 5.5V              |  |  |

| D010A                                                                                             |               | 16LF87XA                                  | —                                                                                                                                                                                       | 20                            | 35  | μΑ | LP osc configuration,<br>Fosc = 32 kHz, VDD = 3.0V,<br>WDT disabled |  |  |

| D013                                                                                              |               | 16F87XA                                   | —                                                                                                                                                                                       | 7                             | 15  | mA | HS osc configuration,<br>Fosc = 20 MHz, VDD = 5.5V                  |  |  |

| D015                                                                                              | $\Delta$ IBOR | Brown-out<br>Reset Current <sup>(6)</sup> | _                                                                                                                                                                                       | 85                            | 200 | μΑ | BOR enabled, VDD = 5.0V                                             |  |  |

Legend: Rows with standard voltage device data only are shaded for improved readability.

† Data in "Typ" column is at 5V, 25°C, unless otherwise stated. These parameters are for design guidance only and are not tested.

- **Note 1:** This is the limit to which VDD can be lowered without losing RAM data.

- **2:** The supply current is mainly a function of the operating voltage and frequency. Other factors, such as I/O pin loading, switching rate, oscillator type, internal code execution pattern and temperature, also have an impact on the current consumption.

- The test conditions for all IDD measurements in active operation mode are:

- <u>OSC1</u> = external square wave, from rail-to-rail; all I/O pins tri-stated, pulled to VDD;

- $\overline{MCLR} = VDD$ ; WDT enabled/disabled as specified.

- **3:** The power-down current in Sleep mode does not depend on the oscillator type. Power-down current is measured with the part in Sleep mode, with all I/O pins in high-impedance state and tied to VDD and Vss.

- 4: For RC osc configuration, current through REXT is not included. The current through the resistor can be estimated by the formula Ir = VDD/2REXT (mA) with REXT in kΩ.

- **5:** Timer1 oscillator (when enabled) adds approximately 20 μA to the specification. This value is from characterization and is for design guidance only. This is not tested.

- 6: The ∆ current is the additional current consumed when this peripheral is enabled. This current should be added to the base IDD or IPD measurement.

- 7: When BOR is enabled, the device will operate correctly until the VBOR voltage trip point is reached.

### 17.1 DC Characteristics: PIC16F873A/874A/876A/877A (Industrial, Extended) PIC16LF873A/874A/876A/877A (Industrial) (Continued)

| PIC16LF873A/874A/876A/877A<br>(Industrial)<br>PIC16F873A/874A/876A/877A<br>(Industrial, Extended) |               |                                           | Standard Operating Conditions (unless otherwise stated)Operating temperature $-40^{\circ}C \le TA \le +85^{\circ}C$ for industrialStandard Operating Conditions (unless otherwise stated)Operating temperature $-40^{\circ}C \le TA \le +85^{\circ}C$ for industrial $-40^{\circ}C \le TA \le +85^{\circ}C$ for industrial $-40^{\circ}C \le TA \le +125^{\circ}C$ for extended |      |          |          |                                                                                                        |  |

|---------------------------------------------------------------------------------------------------|---------------|-------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|----------|----------|--------------------------------------------------------------------------------------------------------|--|

|                                                                                                   |               |                                           |                                                                                                                                                                                                                                                                                                                                                                                 |      |          |          |                                                                                                        |  |

|                                                                                                   | IPD           | Power-down Current <sup>(3,5)</sup>       |                                                                                                                                                                                                                                                                                                                                                                                 |      |          |          |                                                                                                        |  |

| D020                                                                                              |               | 16LF87XA                                  | _                                                                                                                                                                                                                                                                                                                                                                               | 7.5  | 30       | μΑ       | VDD = 3.0V, WDT enabled,<br>-40°C to +85°C                                                             |  |

| D020                                                                                              |               | 16F87XA                                   | _                                                                                                                                                                                                                                                                                                                                                                               | 10.5 | 42<br>60 | μΑ<br>μΑ | VDD = 4.0V, WDT enabled,<br>-40°C to +85°C<br>VDD = 4.0V, WDT enabled,<br>-40°C to +125°C (extended)   |  |

| D021                                                                                              |               | 16LF87XA                                  |                                                                                                                                                                                                                                                                                                                                                                                 | 0.9  | 5        | μA       | VDD = 3.0V, WDT disabled,<br>0°C to +70°C                                                              |  |

| D021                                                                                              |               | 16F87XA                                   | _                                                                                                                                                                                                                                                                                                                                                                               | 1.5  | 16<br>20 | μΑ<br>μΑ | VDD = 4.0V, WDT disabled,<br>-40°C to +85°C<br>VDD = 4.0V, WDT disabled,<br>-40°C to +125°C (extended) |  |

| D021A                                                                                             |               | 16LF87XA                                  |                                                                                                                                                                                                                                                                                                                                                                                 | 0.9  | 5        | μA       | VDD = 3.0V, WDT disabled,<br>-40°C to +85°C                                                            |  |

| D021A                                                                                             |               | 16F87XA                                   |                                                                                                                                                                                                                                                                                                                                                                                 | 1.5  | 19       | μΑ       | VDD = 4.0V, WDT disabled,<br>-40°C to +85°C                                                            |  |

| D023                                                                                              | $\Delta$ IBOR | Brown-out<br>Reset Current <sup>(6)</sup> |                                                                                                                                                                                                                                                                                                                                                                                 | 85   | 200      | μΑ       | BOR enabled, VDD = 5.0V                                                                                |  |

Legend: Rows with standard voltage device data only are shaded for improved readability.

- † Data in "Typ" column is at 5V, 25°C, unless otherwise stated. These parameters are for design guidance only and are not tested.

- Note 1: This is the limit to which VDD can be lowered without losing RAM data.

- **2:** The supply current is mainly a function of the operating voltage and frequency. Other factors, such as I/O pin loading, switching rate, oscillator type, internal code execution pattern and temperature, also have an impact on the current consumption.

- The test conditions for all IDD measurements in active operation mode are:

- OSC1 = external square wave, from rail-to-rail; all I/O pins tri-stated, pulled to VDD; MCLR = VDD; WDT enabled/disabled as specified.

- **3:** The power-down current in Sleep mode does not depend on the oscillator type. Power-down current is measured with the part in Sleep mode, with all I/O pins in high-impedance state and tied to VDD and Vss.

- **4:** For RC osc configuration, current through REXT is not included. The current through the resistor can be estimated by the formula Ir = VDD/2REXT (mA) with REXT in kΩ.

- **5:** Timer1 oscillator (when enabled) adds approximately 20 μA to the specification. This value is from characterization and is for design guidance only. This is not tested.

- 6: The ∆ current is the additional current consumed when this peripheral is enabled. This current should be added to the base IDD or IPD measurement.

- 7: When BOR is enabled, the device will operate correctly until the VBOR voltage trip point is reached.

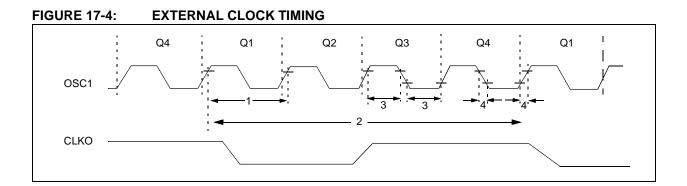

| TABLE 17-3: | EXTERNAL | CLOCK TIMING REQUIREMENTS |

|-------------|----------|---------------------------|

|-------------|----------|---------------------------|

| Param<br>No. | Symbol | Characteristic                   | Min    | Тур† | Max       | Units      | Conditions                 |

|--------------|--------|----------------------------------|--------|------|-----------|------------|----------------------------|

|              | Fosc   | External CLKI Frequency          | DC     | _    | 1         | MHz        | XT and RC Osc mode         |

|              |        | (Note 1)                         | DC     | _    | 20        | MHz        | HS Osc mode                |

|              |        |                                  | DC     | _    | 32        | kHz        | LP Osc mode                |

|              |        | Oscillator Frequency             | DC     | _    | 4         | MHz        | RC Osc mode                |

|              |        | (Note 1)                         | 0.1    | —    | 4         | MHz        | XT Osc mode                |

|              |        |                                  | 4<br>5 | _    | 20<br>200 | MHz<br>kHz | HS Osc mode<br>LP Osc mode |

| 1            | Tosc   | External CLKI Period             | 1000   | _    |           | ns         | XT and RC Osc mode         |

|              |        | (Note 1)                         | 50     | _    | _         | ns         | HS Osc mode                |

|              |        |                                  | 5      | —    | —         | μS         | LP Osc mode                |

|              |        | Oscillator Period                | 250    | —    | —         | ns         | RC Osc mode                |

|              |        | (Note 1)                         | 250    | —    | 1         | μS         | XT Osc mode                |

|              |        |                                  | 100    | —    | 250       | ns         | HS Osc mode                |

|              |        |                                  | 50     | —    | 250       | ns         | HS Osc mode                |

|              |        |                                  | 31.25  |      | —         | μS         | LP Osc mode                |

| 2            | Тсү    | Instruction Cycle Time (Note 1)  | 200    | Тсү  | DC        | ns         | Tcy = 4/Fosc               |

| 3            | TosL,  | External Clock in (OSC1) High or | 100    | —    | —         | ns         | XT oscillator              |

|              | TosH   | Low Time                         | 2.5    | —    | —         | μS         | LP oscillator              |

|              |        |                                  | 15     |      | —         | ns         | HS oscillator              |

| 4            | TosR,  | External Clock in (OSC1) Rise or | _      |      | 25        | ns         | XT oscillator              |

|              | TosF   | Fall Time                        | —      | —    | 50        | ns         | LP oscillator              |

|              |        |                                  | —      | _    | 15        | ns         | HS oscillator              |

† Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

**Note 1:** Instruction cycle period (TCY) equals four times the input oscillator time base period. All specified values are based on characterization data for that particular oscillator type, under standard operating conditions, with the device executing code. Exceeding these specified limits may result in an unstable oscillator operation and/or higher than expected current consumption. All devices are tested to operate at "min." values with an external clock applied to the OSC1/CLKI pin. When an external clock input is used, the "max." cycle time limit is "DC" (no clock) for all devices.

100 Max (125°C) 10 Max (85°C) 1 IPD (NA) 0.1 0.01 Тур (25°С) Typical: statistical mean @ 25°C **Maximum:** mean +  $3\sigma$  (-40°C to +125°C) **Minimum:** mean -  $3\sigma$  (-40°C to +125°C) 0.001 2.0 2.5 3.0 3.5 4.0 4.5 5.0 5.5 VDD (V)

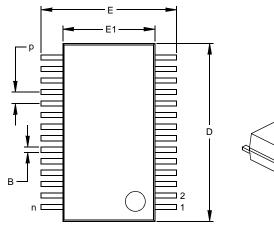

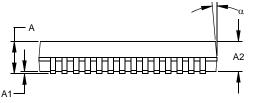

# 28-Lead Plastic Shrink Small Outline (SS) - 209 mil, 5.30 mm (SSOP)

Note: For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

|                          |          | INCHES |      | MILLIMETERS* |       |        |        |

|--------------------------|----------|--------|------|--------------|-------|--------|--------|

| Dimension                | n Limits | MIN    | NOM  | MAX          | MIN   | NOM    | MAX    |

| Number of Pins           | n        |        | 28   |              |       | 28     |        |

| Pitch                    | р        |        | .026 |              |       | 0.65   |        |

| Overall Height           | Α        | .068   | .073 | .078         | 1.73  | 1.85   | 1.98   |

| Molded Package Thickness | A2       | .064   | .068 | .072         | 1.63  | 1.73   | 1.83   |

| Standoff §               | A1       | .002   | .006 | .010         | 0.05  | 0.15   | 0.25   |

| Overall Width            | E        | .299   | .309 | .319         | 7.59  | 7.85   | 8.10   |

| Molded Package Width     | E1       | .201   | .207 | .212         | 5.11  | 5.25   | 5.38   |

| Overall Length           | D        | .396   | .402 | .407         | 10.06 | 10.20  | 10.34  |

| Foot Length              | L        | .022   | .030 | .037         | 0.56  | 0.75   | 0.94   |

| Lead Thickness           | С        | .004   | .007 | .010         | 0.10  | 0.18   | 0.25   |

| Foot Angle               | φ        | 0      | 4    | 8            | 0.00  | 101.60 | 203.20 |

| Lead Width               | В        | .010   | .013 | .015         | 0.25  | 0.32   | 0.38   |

| Mold Draft Angle Top     | α        | 0      | 5    | 10           | 0     | 5      | 10     |

| Mold Draft Angle Bottom  | β        | 0      | 5    | 10           | 0     | 5      | 10     |

\* Controlling Parameter § Significant Characteristic

Notes:

Dimensions D and E1 do not include mold flash or protrusions. Mold flash or protrusions shall not exceed .010" (0.254mm) per side. JEDEC Equivalent: MS-150

Drawing No. C04-073

# PIC16F87XA

| MPLAB ICE 4000 High-Performance Universal    |

|----------------------------------------------|

| In-Circuit Emulator169                       |

| MPLAB Integrated Development                 |

| Environment Software167                      |

| MPLINK Object Linker/MPLIB Object Librarian  |

| MSSP71                                       |

| I <sup>2</sup> C Mode. See I <sup>2</sup> C. |

| SPI Mode71                                   |

| SPI Mode. See SPI.                           |

| MSSP Module                                  |

| Clock Stretching90                           |

| Clock Synchronization and the CKP Bit91      |

| Control Registers (General)71                |

| Operation84                                  |

| Overview71                                   |

| SPI Master Mode76                            |

| SPI Slave Mode77                             |

| SSPBUF                                       |

| SSPSR76                                      |

| Multi-Master Mode105                         |

# 0

| Opcode Field Descriptions       |               |

|---------------------------------|---------------|

| OPTION_REG Register             |               |

| INTEDG Bit                      |               |

| PS2:PS0 Bits                    |               |

| PSA Bit                         |               |

| RBPU Bit                        |               |

| T0CS Bit                        |               |

| T0SE Bit                        |               |

| OSC1/CLKI Pin                   |               |

| OSC2/CLKO Pin                   |               |

| Oscillator Configuration        |               |

| HS                              |               |

| LP                              |               |

| RC                              | 145, 146, 149 |

| XT                              |               |

| Oscillator Selection            |               |

| Oscillator Start-up Timer (OST) |               |

| Oscillator, WDT                 |               |

| Oscillators                     |               |

| Capacitor Selection             |               |

| Ceramic Resonator Selection     |               |

| Crystal and Ceramic Resonators  |               |

| RC                              |               |

|                                 |               |

# Ρ

| Package Information                      |                 |

|------------------------------------------|-----------------|

| Marking                                  |                 |

| Packaging Information                    |                 |

| Paging, Program Memory                   |                 |

| Parallel Slave Port (PSP)                | 13, 48, 51      |

| Associated Registers                     |                 |

| RE0/RD/AN5 Pin                           |                 |

| RE1/WR/AN6 Pin                           | 49, 51          |

| RE2/CS/AN7 Pin                           | 49, 51          |

| Select (PSPMODE Bit)                     | .48, 49, 50, 51 |

| Parallel Slave Port Requirements         |                 |

| (PIC16F874A/ 877A Only)                  |                 |

| PCL Register                             | 19, 20, 30      |

| PCLATH Register                          | 19, 20, 30      |

| PCON Register                            | 20, 29, 149     |

| BOR Bit                                  |                 |

| POR Bit                                  |                 |

| PIC16F87XA Product Identification System |                 |

| PICkit 1 Flash Starter Kit               | 171             |

| PICSTART Plus Development Programmer                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                               |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------|