Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

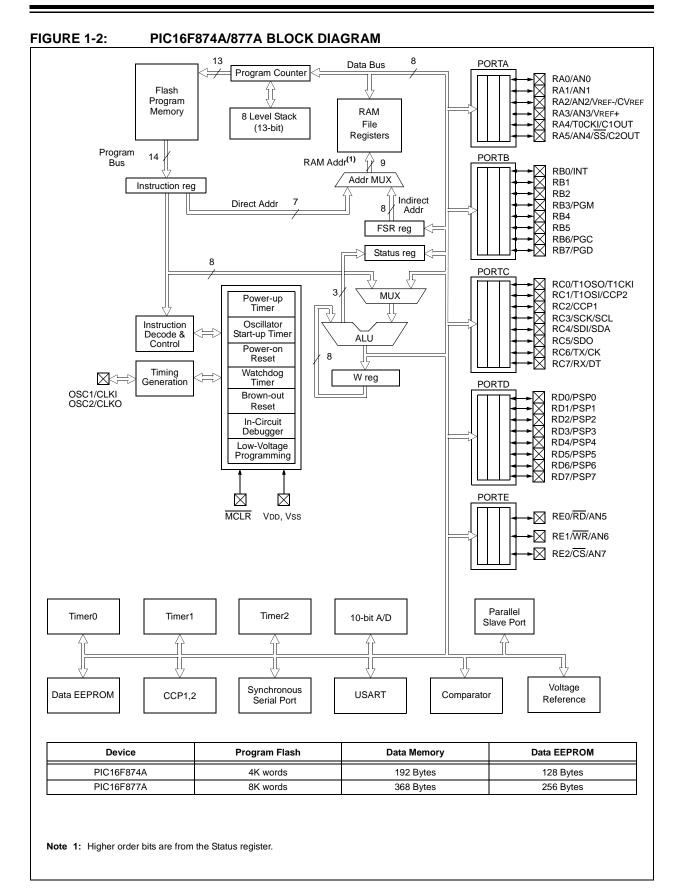

| Product Status             | Active                                                                    |

|----------------------------|---------------------------------------------------------------------------|

| Core Processor             | PIC                                                                       |

| Core Size                  | 8-Bit                                                                     |

| Speed                      | 20MHz                                                                     |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                         |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                     |

| Number of I/O              | 33                                                                        |

| Program Memory Size        | 14KB (8K x 14)                                                            |

| Program Memory Type        | FLASH                                                                     |

| EEPROM Size                | 256 x 8                                                                   |

| RAM Size                   | 368 x 8                                                                   |

| Voltage - Supply (Vcc/Vdd) | 4V ~ 5.5V                                                                 |

| Data Converters            | A/D 8x10b                                                                 |

| Oscillator Type            | External                                                                  |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                        |

| Mounting Type              | Surface Mount                                                             |

| Package / Case             | 44-VQFN Exposed Pad                                                       |

| Supplier Device Package    | 44-QFN (8x8)                                                              |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16f877a-e-ml |

|                            |                                                                           |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

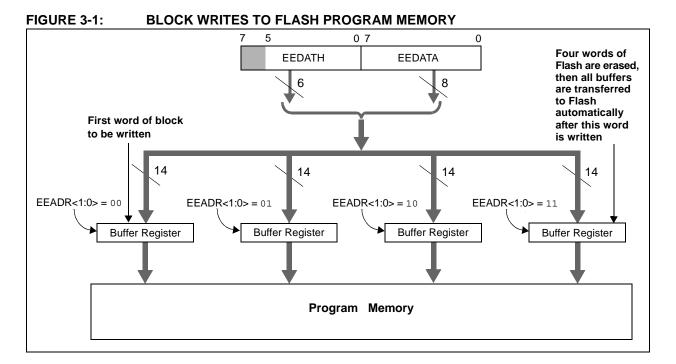

### 3.6 Writing to Flash Program Memory

Flash program memory may only be written to if the destination address is in a segment of memory that is not write-protected, as defined in bits WRT1:WRT0 of the device configuration word (Register 14-1). Flash program memory must be written in four-word blocks. A block consists of four words with sequential addresses, with a lower boundary defined by an address, where EEADR<1:0> = 00. At the same time, all block writes to program memory are done as erase and write operations. The write operation is edge-aligned and cannot occur across boundaries.

To write program data, it must first be loaded into the buffer registers (see Figure 3-1). This is accomplished by first writing the destination address to EEADR and EEADRH and then writing the data to EEDATA and EEDATH. After the address and data have been set up, then the following sequence of events must be executed:

- 1. Set the EEPGD control bit (EECON1<7>).

- 2. Write 55h, then AAh, to EECON2 (Flash programming sequence).

- 3. Set the WR control bit (EECON1<1>).

All four buffer register locations **MUST** be written to with correct data. If only one, two or three words are being written to in the block of four words, then a read from the program memory location(s) not being written to must be performed. This takes the data from the program location(s) not being written and loads it into the EEDATA and EEDATH registers. Then the sequence of events to transfer data to the buffer registers must be executed. To transfer data from the buffer registers to the program memory, the EEADR and EEADRH must point to the last location in the four-word block (EEADR<1:0> = 11). Then the following sequence of events must be executed:

- 1. Set the EEPGD control bit (EECON1<7>).

- 2. Write 55h, then AAh, to EECON2 (Flash programming sequence).

- Set control bit WR (EECON1<1>) to begin the write operation.

The user must follow the same specific sequence to initiate the write for each word in the program block, writing each program word in sequence (00, 01, 10, 11). When the write is performed on the last word (EEADR<1:0> = 11), the block of four words are automatically erased and the contents of the buffer registers are written into the program memory.

After the "BSF EECON1, WR" instruction, the processor requires two cycles to set up the erase/write operation. The user must place two NOP instructions after the WR bit is set. Since data is being written to buffer registers, the writing of the first three words of the block appears to occur immediately. The processor will halt internal operations for the typical 4 ms, only during the cycle in which the erase takes place (i.e., the last word of the four-word block). This is not Sleep mode as the clocks and peripherals will continue to run. After the write cycle, the processor will resume operation with the third instruction after the EECON1 write instruction. If the sequence is performed to any other location, the action is ignored.

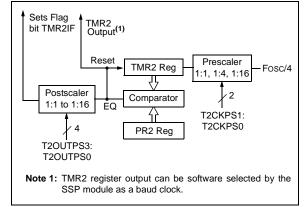

## 7.0 TIMER2 MODULE

Timer2 is an 8-bit timer with a prescaler and a postscaler. It can be used as the PWM time base for the PWM mode of the CCP module(s). The TMR2 register is readable and writable and is cleared on any device Reset.

The input clock (Fosc/4) has a prescale option of 1:1, 1:4 or 1:16, selected by control bits T2CKPS1:T2CKPS0 (T2CON<1:0>).

The Timer2 module has an 8-bit period register, PR2. Timer2 increments from 00h until it matches PR2 and then resets to 00h on the next increment cycle. PR2 is a readable and writable register. The PR2 register is initialized to FFh upon Reset.

The match output of TMR2 goes through a 4-bit postscaler (which gives a 1:1 to 1:16 scaling inclusive) to generate a TMR2 interrupt (latched in flag bit, TMR2IF (PIR1<1>)).

Timer2 can be shut-off by clearing control bit, TMR2ON (T2CON<2>), to minimize power consumption.

Register 7-1 shows the Timer2 Control register.

Additional information on timer modules is available in the PIC<sup>®</sup> Mid-Range MCU Family Reference Manual (DS33023).

### FIGURE 7-1: TIMER2 BLOCK DIAGRAM

### REGISTER 7-1: T2CON: TIMER2 CONTROL REGISTER (ADDRESS 12h)

| ER 7-1: | T2CON: T                               | IMER2 CC                                  | NTROL R         | EGISTER      | (ADDRESS      | 5 12h)    |              |         |

|---------|----------------------------------------|-------------------------------------------|-----------------|--------------|---------------|-----------|--------------|---------|

|         | U-0                                    | R/W-0                                     | R/W-0           | R/W-0        | R/W-0         | R/W-0     | R/W-0        | R/W-0   |

|         |                                        | TOUTPS3                                   | TOUTPS2         | TOUTPS1      | TOUTPS0       | TMR2ON    | T2CKPS1      | T2CKPS0 |

|         | bit 7                                  |                                           |                 |              |               |           |              | bit 0   |

| bit 7   | Unimplem                               | nented: Rea                               | <b>d as</b> '0' |              |               |           |              |         |

| bit 6-3 | TOUTPS3                                | :TOUTPS0:                                 | Timer2 Out      | put Postsca  | e Select bits |           |              |         |

|         | 0001 = 1:2                             | 1 postscale<br>2 postscale<br>3 postscale |                 |              |               |           |              |         |

|         | 1111 <b>= 1</b> :1                     | 16 postscale                              |                 |              |               |           |              |         |

| bit 2   | TMR2ON:                                | Timer2 On I                               | oit             |              |               |           |              |         |

|         | 1 = Timer2<br>0 = Timer2               |                                           |                 |              |               |           |              |         |

| bit 1-0 | T2CKPS1                                | :T2CKPS0:                                 | Timer2 Cloc     | k Prescale   | Select bits   |           |              |         |

|         | 00 = Prese<br>01 = Prese<br>1x = Prese | caler is 4                                |                 |              |               |           |              |         |

|         | Logondi                                |                                           |                 |              |               |           |              |         |

|         | Legend:                                |                                           | 147 14          |              |               |           |              | (O)     |

|         | R = Reada                              |                                           |                 | Vritable bit |               | -         | bit, read as |         |

|         | - n = Value                            | e at POR                                  | `1 <i>`</i> = E | Bit is set   | 0' = Bit is   | s cleared | x = Bit is u | nknown  |

### 7.1 Timer2 Prescaler and Postscaler

The prescaler and postscaler counters are cleared when any of the following occurs:

- a write to the TMR2 register

- a write to the T2CON register

- any device Reset (POR, MCLR Reset, WDT Reset or BOR)

TMR2 is not cleared when T2CON is written.

### 7.2 Output of TMR2

The output of TMR2 (before the postscaler) is fed to the SSP module, which optionally uses it to generate the shift clock.

| TABLE 7-1:       | REGISTERS ASSOCIATED WITH TIMER2 AS A TIMER/COUNTER |

|------------------|-----------------------------------------------------|

| $IADEE I^{-1}$ . |                                                     |

| Address                 | Name   | Bit 7                | Bit 6                         | Bit 5   | Bit 4   | Bit 3   | Bit 2  | Bit 1   | Bit 0   | Value<br>POR, |      |      | e on<br>other<br>sets |

|-------------------------|--------|----------------------|-------------------------------|---------|---------|---------|--------|---------|---------|---------------|------|------|-----------------------|

| 0Bh, 8Bh,<br>10Bh, 18Bh | INTCON | GIE                  | PEIE                          | TMR0IE  | INTE    | RBIE    | TMR0IF | INTF    | RBIF    | 0000          | 000x | 0000 | 000u                  |

| 0Ch                     | PIR1   | PSPIF <sup>(1)</sup> | ADIF                          | RCIF    | TXIF    | SSPIF   | CCP1IF | TMR2IF  | TMR1IF  | 0000          | 0000 | 0000 | 0000                  |

| 8Ch                     | PIE1   | PSPIE <sup>(1)</sup> | ADIE                          | RCIE    | TXIE    | SSPIE   | CCP1IE | TMR2IE  | TMR1IE  | 0000          | 0000 | 0000 | 0000                  |

| 11h                     | TMR2   | Timer2 M             | Timer2 Module's Register 0000 |         |         |         |        | 0000    | 0000    | 0000          |      |      |                       |

| 12h                     | T2CON  | —                    | TOUTPS3                       | TOUTPS2 | TOUTPS1 | TOUTPS0 | TMR2ON | T2CKPS1 | T2CKPS0 | -000          | 0000 | -000 | 0000                  |

| 92h                     | PR2    | Timer2 P             | imer2 Period Register         |         |         |         |        |         |         | 1111          | 1111 | 1111 | 1111                  |

Legend: x = unknown, u = unchanged, - = unimplemented, read as '0'. Shaded cells are not used by the Timer2 module.

Note 1: Bits PSPIE and PSPIF are reserved on 28-pin devices; always maintain these bits clear.

### 9.3.3 ENABLING SPI I/O

To enable the serial port, SSP Enable bit, SSPEN (SSPCON<5>), must be set. To reset or reconfigure SPI mode, clear the SSPEN bit, re-initialize the SSPCON registers and then set the SSPEN bit. This configures the SDI, SDO, SCK and SS pins as serial port pins. For the pins to behave as the serial port function, some must have their data direction bits (in the TRIS register) appropriately programmed. That is:

- SDI is automatically controlled by the SPI module

- SDO must have TRISC<5> bit cleared

- SCK (Master mode) must have TRISC<3> bit cleared

- SCK (Slave mode) must have TRISC<3> bit set

- SS must have TRISC<4> bit set

Any serial port function that is not desired may be overridden by programming the corresponding data direction (TRIS) register to the opposite value.

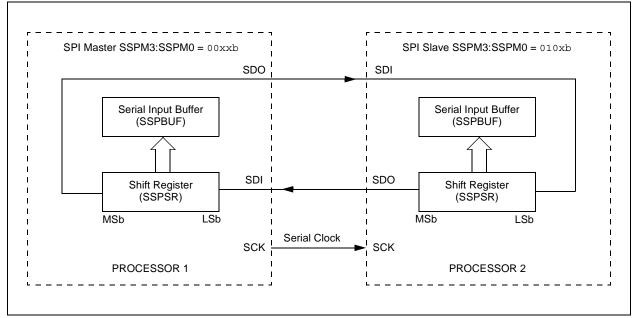

### 9.3.4 TYPICAL CONNECTION

Figure 9-2 shows a typical connection between two microcontrollers. The master controller (Processor 1) initiates the data transfer by sending the SCK signal. Data is shifted out of both shift registers on their programmed clock edge and latched on the opposite edge of the clock. Both processors should be programmed to the same Clock Polarity (CKP), then both controllers would send and receive data at the same time. Whether the data is meaningful (or dummy data) depends on the application software. This leads to three scenarios for data transmission:

- Master sends data Slave sends dummy data

- Master sends data Slave sends data

- Master sends dummy data Slave sends data

### FIGURE 9-2: SPI MASTER/SLAVE CONNECTION

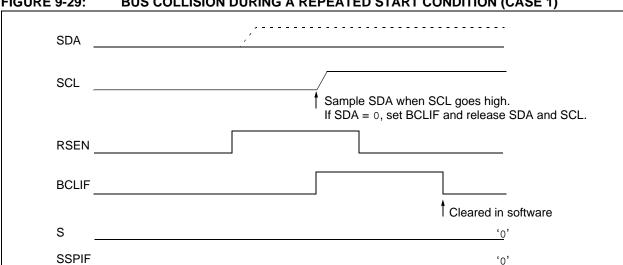

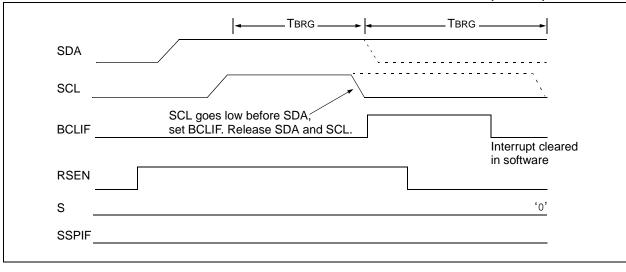

#### Bus Collision During a Repeated 9.4.17.2 Start Condition

During a Repeated Start condition, a bus collision occurs if:

- a) A low level is sampled on SDA when SCL goes from low level to high level.

- b) SCL goes low before SDA is asserted low, indicating that another master is attempting to transmit a data '1'.

When the user deasserts SDA and the pin is allowed to float high, the BRG is loaded with SSPADD<6:0> and counts down to 0. The SCL pin is then deasserted and when sampled high, the SDA pin is sampled.

If SDA is low, a bus collision has occurred (i.e., another master is attempting to transmit a data '0', see Figure 9-29). If SDA is sampled high, the BRG is

reloaded and begins counting. If SDA goes from high to low before the BRG times out, no bus collision occurs because no two masters can assert SDA at exactly the same time.

If SCL goes from high to low before the BRG times out and SDA has not already been asserted, a bus collision occurs. In this case, another master is attempting to transmit a data '1' during the Repeated Start condition (Figure 9-30).

If at the end of the BRG time-out, both SCL and SDA are still high, the SDA pin is driven low and the BRG is reloaded and begins counting. At the end of the count, regardless of the status of the SCL pin, the SCL pin is driven low and the Repeated Start condition is complete.

#### FIGURE 9-29: **BUS COLLISION DURING A REPEATED START CONDITION (CASE 1)**

NOTES:

### 14.10 Power Control/Status Register (PCON)

The Power Control/Status Register, PCON, has up to two bits depending upon the device.

Bit 0 is the Brown-out Reset Status bit, BOR. The BOR bit is unknown on a Power-on Reset. It must then be set by the user and checked on subsequent Resets to see if it has been cleared, indicating that a BOR has occurred.

When the Brown-out Reset is disabled, the state of the  $\overline{\text{BOR}}$  bit is unpredictable and is, therefore, not valid at any time.

Bit 1 is the Power-on Reset Status bit,  $\overline{\text{POR}}$ . It is cleared on a Power-on Reset and unaffected otherwise. The user must set this bit following a Power-on Reset.

| TABLE 14-3: | TIME-OUT IN VARIOUS SITUATIONS |

|-------------|--------------------------------|

|-------------|--------------------------------|

| Oscillator Configuration | Power             | -up              | Brown-out         | Wake-up from |  |

|--------------------------|-------------------|------------------|-------------------|--------------|--|

| Oscillator Configuration | <b>PWRTE =</b> 0  | <b>PWRTE</b> = 1 | Brown-out         | Sleep        |  |

| XT, HS, LP               | 72 ms + 1024 Tosc | 1024 Tosc        | 72 ms + 1024 Tosc | 1024 Tosc    |  |

| RC                       | 72 ms             |                  | 72 ms             | _            |  |

### TABLE 14-4: STATUS BITS AND THEIR SIGNIFICANCE

| POR | BOR | то | PD | Condition                                               |

|-----|-----|----|----|---------------------------------------------------------|

| 0   | x   | 1  | 1  | Power-on Reset                                          |

| 0   | x   | 0  | x  | Illegal, TO is set on POR                               |

| 0   | x   | х  | 0  | Illegal, PD is set on POR                               |

| 1   | 0   | 1  | 1  | Brown-out Reset                                         |

| 1   | 1   | 0  | 1  | WDT Reset                                               |

| 1   | 1   | 0  | 0  | WDT Wake-up                                             |

| 1   | 1   | u  | u  | MCLR Reset during normal operation                      |

| 1   | 1   | 1  | 0  | MCLR Reset during Sleep or Interrupt Wake-up from Sleep |

**Legend:** x = don't care, u = unchanged

### TABLE 14-5: RESET CONDITIONS FOR SPECIAL REGISTERS

| Condition                          | Program<br>Counter    | Status<br>Register | PCON<br>Register |

|------------------------------------|-----------------------|--------------------|------------------|

| Power-on Reset                     | 000h                  | 0001 1xxx          | 0x               |

| MCLR Reset during normal operation | 000h                  | 000u uuuu          | uu               |

| MCLR Reset during Sleep            | 000h                  | 0001 0uuu          | uu               |

| WDT Reset                          | 000h                  | 0000 luuu          | uu               |

| WDT Wake-up                        | PC + 1                | uuu0 0uuu          | uu               |

| Brown-out Reset                    | 000h                  | 0001 luuu          | u0               |

| Interrupt Wake-up from Sleep       | PC + 1 <sup>(1)</sup> | uuul Ouuu          | uu               |

Legend: u = unchanged, x = unknown, - = unimplemented bit, read as '0'

**Note 1:** When the wake-up is due to an interrupt and the GIE bit is set, the PC is loaded with the interrupt vector (0004h).

### 14.11.1 INT INTERRUPT

External interrupt on the RB0/INT pin is edge triggered, either rising if bit INTEDG (OPTION\_REG<6>) is set or falling if the INTEDG bit is clear. When a valid edge appears on the RB0/INT pin, flag bit, INTF (INTCON<1>), is set. This interrupt can be disabled by clearing enable bit, INTE (INTCON<4>). Flag bit INTF must be cleared in software in the Interrupt Service Routine before re-enabling this interrupt. The INT interrupt can wake-up the processor from Sleep if bit INTE was set prior to going into Sleep. The status of global interrupt enable bit, GIE, decides whether or not the processor branches to the interrupt vector following wake-up. See **Section 14.14** "**Power-down Mode** (**Sleep**)" for details on Sleep mode.

### 14.11.2 TMR0 INTERRUPT

An overflow (FFh  $\rightarrow$  00h) in the TMR0 register will set flag bit, TMR0IF (INTCON<2>). The interrupt can be enabled/disabled by setting/clearing enable bit, TMR0IE (INTCON<5>). See **Section 5.0 "Timer0 Module"**.

### 14.11.3 PORTB INTCON CHANGE

An input change on PORTB<7:4> sets flag bit, RBIF (INTCON<0>). The interrupt can be enabled/disabled by setting/clearing enable bit, RBIE (INTCON<4>). See Section 4.2 "PORTB and the TRISB Register".

### 14.12 Context Saving During Interrupts

During an interrupt, only the return PC value is saved on the stack. Typically, users may wish to save key registers during an interrupt (i.e., W register and Status register). This will have to be implemented in software.

For the PIC16F873A/874A devices, the register W\_TEMP must be defined in both Banks 0 and 1 and must be defined at the same offset from the bank base address (i.e., If W\_TEMP is defined at 0x20 in Bank 0, it must also be defined at 0xA0 in Bank 1). The registers, PCLATH\_TEMP and STATUS\_TEMP, are only defined in Bank 0.

Since the upper 16 bytes of each bank are common in the PIC16F876A/877A devices, temporary holding registers, W\_TEMP, STATUS\_TEMP and PCLATH\_TEMP, should be placed in here. These 16 locations don't require banking and therefore, make it easier for context save and restore. The same code shown in Example 14-1 can be used.

| EXAMPLE 14-1: | SAVING STATUS, W AND PCLATH REGISTERS IN RAM |

|---------------|----------------------------------------------|

|---------------|----------------------------------------------|

| MOVWF  | W_TEMP         | ;Copy W to TEMP register                                |

|--------|----------------|---------------------------------------------------------|

| SWAPF  | STATUS,W       | ;Swap status to be saved into W                         |

| CLRF   | STATUS         | ;bank 0, regardless of current bank, Clears IRP,RP1,RP0 |

| MOVWF  | STATUS_TEMP    | ;Save status to bank zero STATUS_TEMP register          |

| MOVF   | PCLATH, W      | ;Only required if using pages 1, 2 and/or 3             |

| MOVWF  | PCLATH_TEMP    | ;Save PCLATH into W                                     |

| CLRF   | PCLATH         | ;Page zero, regardless of current page                  |

| :      |                |                                                         |

| :(ISR) |                | ;(Insert user code here)                                |

| :      |                |                                                         |

| MOVF   | PCLATH_TEMP, W | ;Restore PCLATH                                         |

| MOVWF  | PCLATH         | ;Move W into PCLATH                                     |

| SWAPF  | STATUS_TEMP,W  | ;Swap STATUS_TEMP register into W                       |

|        |                | ;(sets bank to original state)                          |

| MOVWF  | STATUS         | ;Move W into STATUS register                            |

| SWAPF  | W_TEMP,F       | ;Swap W_TEMP                                            |

| SWAPF  | W_TEMP,W       | ;Swap W_TEMP into W                                     |

|        |                |                                                         |

### 14.14 Power-down Mode (Sleep)

Power-down mode is entered by executing a  $\ensuremath{\mathtt{SLEEP}}$  instruction.

If enabled, the Watchdog Timer will be cleared but keeps running, the PD bit (Status<3>) is cleared, the TO (Status<4>) bit is set and the oscillator driver is turned off. The I/O ports maintain the status they had before the SLEEP instruction was executed (driving high, low or high-impedance).

For lowest current consumption in this mode, place all I/O pins at either VDD or VSS, ensure no external circuitry is drawing current from the I/O pin, powerdown the A/D and disable external clocks. Pull all I/O pins that are high-impedance inputs, high or low externally, to avoid switching currents caused by floating inputs. The TOCKI input should also be at VDD or VSS for lowest current consumption. The contribution from on-chip pull-ups on PORTB should also be considered.

The MCLR pin must be at a logic high level (VIHMC).

### 14.14.1 WAKE-UP FROM SLEEP

The device can wake-up from Sleep through one of the following events:

- 1. External Reset input on  $\overline{\text{MCLR}}$  pin.

- 2. Watchdog Timer wake-up (if WDT was enabled).

- 3. Interrupt from INT pin, RB port change or peripheral interrupt.

External MCLR Reset will cause a device Reset. All other events are considered a continuation of program execution and cause a "wake-up". The TO and PD bits in the Status register can be used to determine the cause of device Reset. The PD bit, which is set on power-up, is cleared when Sleep is invoked. The TO bit is cleared if a WDT time-out occurred and caused wake-up.

The following peripheral interrupts can wake the device from Sleep:

- 1. PSP read or write (PIC16F874/877 only).

- 2. TMR1 interrupt. Timer1 must be operating as an asynchronous counter.

- 3. CCP Capture mode interrupt.

- 4. Special event trigger (Timer1 in Asynchronous mode using an external clock).

- 5. SSP (Start/Stop) bit detect interrupt.

- 6. SSP transmit or receive in Slave mode (SPI/I<sup>2</sup>C).

- 7. USART RX or TX (Synchronous Slave mode).

- 8. A/D conversion (when A/D clock source is RC).

- 9. EEPROM write operation completion.

- 10. Comparator output changes state.

Other peripherals cannot generate interrupts since during Sleep, no on-chip clocks are present.

When the SLEEP instruction is being executed, the next instruction (PC + 1) is prefetched. For the device to wake-up through an interrupt event, the corresponding interrupt enable bit must be set (enabled). Wake-up is regardless of the state of the GIE bit. If the GIE bit is clear (disabled), the device continues execution at the instruction after the SLEEP instruction. If the GIE bit is set (enabled), the device executes the instruction after the SLEEP instruction and then branches to the interrupt address (0004h). In cases where the execution of the instruction following SLEEP is not desirable, the user should have a NOP after the SLEEP instruction.

### 14.14.2 WAKE-UP USING INTERRUPTS

When global interrupts are disabled (GIE cleared) and any interrupt source has both its interrupt enable bit and interrupt flag bit set, one of the following will occur:

- If the interrupt occurs **before** the execution of a SLEEP instruction, the SLEEP instruction will complete as a NOP. Therefore, the WDT and WDT postscaler will not be cleared, the TO bit will not be set and PD bits will not be cleared.

- If the interrupt occurs during or after the execution of a SLEEP instruction, the device will immediately wake-up from Sleep. The SLEEP instruction will be completely executed before the wake-up. Therefore, the WDT and WDT postscaler will be cleared, the TO bit will be set and the PD bit will be cleared.

Even if the flag bits were checked before executing a SLEEP instruction, it may be possible for flag bits to become set before the SLEEP instruction completes. To determine whether a SLEEP instruction executed, test the PD bit. If the PD bit is set, the SLEEP instruction was executed as a NOP.

To ensure that the WDT is cleared, a CLRWDT instruction should be executed before a SLEEP instruction.

| 15.2 | Instruction | Descriptions |

|------|-------------|--------------|

|------|-------------|--------------|

| ADDLW            | Add Literal and W                                                                                                          |

|------------------|----------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [ <i>label</i> ] ADDLW k                                                                                                   |

| Operands:        | $0 \leq k \leq 255$                                                                                                        |

| Operation:       | $(W) + k \to (W)$                                                                                                          |

| Status Affected: | C, DC, Z                                                                                                                   |

| Description:     | The contents of the W register<br>are added to the eight-bit literal 'k'<br>and the result is placed in the W<br>register. |

|                  | register.                                                                                                                                                      |  |  |  |

|------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| ADDWF            | Add W and f                                                                                                                                                    |  |  |  |

| Syntax:          | [label] ADDWF f,d                                                                                                                                              |  |  |  |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ d \in [0,1] \end{array}$                                                                                                |  |  |  |

| Operation:       | (W) + (f) $\rightarrow$ (destination)                                                                                                                          |  |  |  |

| Status Affected: | C, DC, Z                                                                                                                                                       |  |  |  |

| Description:     | Add the contents of the W register<br>with register 'f'. If 'd' is '0', the<br>result is stored in the W register. If<br>'d' is '1', the result is stored back |  |  |  |

| BCF              | Bit Clear f                                                         |

|------------------|---------------------------------------------------------------------|

| Syntax:          | [label]BCF f,b                                                      |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ 0 \leq b \leq 7 \end{array}$ |

| Operation:       | $0 \rightarrow (f < b >)$                                           |

| Status Affected: | None                                                                |

| Description:     | Bit 'b' in register 'f' is cleared.                                 |

| BSF              | Bit Set f                                                           |

|------------------|---------------------------------------------------------------------|

| Syntax:          | [ <i>label</i> ] BSF f,b                                            |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ 0 \leq b \leq 7 \end{array}$ |

| Operation:       | $1 \rightarrow (f < b >)$                                           |

| Status Affected: | None                                                                |

| Description:     | Bit 'b' in register 'f' is set.                                     |

| ANDLW            | AND Literal with W                                                                                                     |

|------------------|------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [ <i>label</i> ] ANDLW k                                                                                               |

| Operands:        | $0 \leq k \leq 255$                                                                                                    |

| Operation:       | (W) .AND. (k) $\rightarrow$ (W)                                                                                        |

| Status Affected: | Z                                                                                                                      |

| Description:     | The contents of W register are<br>AND'ed with the eight-bit literal<br>'k'. The result is placed in the W<br>register. |

in register 'f'.

| BTFSS            | Bit Test f, Skip if Set                                                                                                                                                                           |

|------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [ label ] BTFSS f,b                                                                                                                                                                               |

| Operands:        | $0 \le f \le 127$<br>$0 \le b < 7$                                                                                                                                                                |

| Operation:       | skip if (f <b>) = 1</b>                                                                                                                                                                           |

| Status Affected: | None                                                                                                                                                                                              |

| Description:     | If bit 'b' in register 'f' is '0', the next instruction is executed.<br>If bit 'b' is '1', then the next instruction is discarded and a NOP is executed instead, making this a 2 TCY instruction. |

| ANDWF            | AND W with f                                                                                                                                           |  |  |  |  |

|------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| Syntax:          | [label] ANDWF f,d                                                                                                                                      |  |  |  |  |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ d \in [0,1] \end{array}$                                                                                        |  |  |  |  |

| Operation:       | (W) .AND. (f) $\rightarrow$ (destination)                                                                                                              |  |  |  |  |

| Status Affected: | Z                                                                                                                                                      |  |  |  |  |

| Description:     | AND the W register with register 'f'. If 'd' is '0', the result is stored in the W register. If 'd' is '1', the result is stored back in register 'f'. |  |  |  |  |

| BTFSC            | Bit Test, Skip if Clear                                                                                                                                                                                      |

|------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [ label ] BTFSC f,b                                                                                                                                                                                          |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ 0 \leq b \leq 7 \end{array}$                                                                                                                                          |

| Operation:       | skip if (f <b>) = <math>0</math></b>                                                                                                                                                                         |

| Status Affected: | None                                                                                                                                                                                                         |

| Description:     | If bit 'b' in register 'f' is '1', the next instruction is executed.<br>If bit 'b' in register 'f' is '0', the next instruction is discarded and a NOP is executed instead, making this a 2 TCY instruction. |

NOTES:

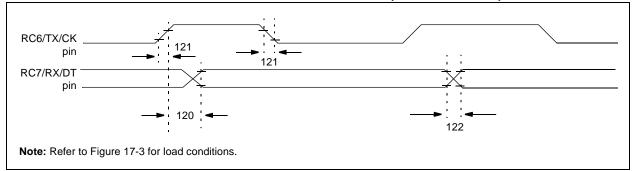

### FIGURE 17-17: USART SYNCHRONOUS TRANSMISSION (MASTER/SLAVE) TIMING

### TABLE 17-12: USART SYNCHRONOUS TRANSMISSION REQUIREMENTS

| Param<br>No. | Symbol        | Characteristic                                                        |                      | Min | Тур† | Max | Units | Conditions |

|--------------|---------------|-----------------------------------------------------------------------|----------------------|-----|------|-----|-------|------------|

| 120          | TCKH2DTV      | <u>SYNC XMIT (MASTER &amp; SLAVE)</u><br>Clock High to Data Out Valid | Standard( <b>F</b> ) | _   | _    | 80  | ns    |            |

|              |               |                                                                       | Extended(LF)         | —   |      | 100 | ns    |            |

| 121          | TCKRF         | Clock Out Rise Time and Fall Time                                     | Standard(F)          | —   | —    | 45  | ns    |            |

|              | (Master mode) | Extended(LF)                                                          | —                    | —   | 50   | ns  |       |            |

| 122          | Tdtrf         | Data Out Rise Time and Fall Time                                      | Standard(F)          | —   | —    | 45  | ns    |            |

|              |               |                                                                       | Extended(LF)         | _   | —    | 50  | ns    |            |

† Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

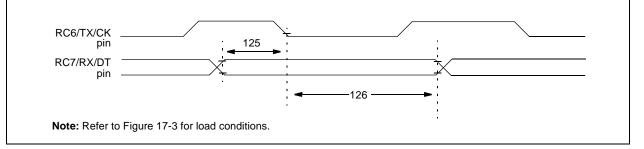

### FIGURE 17-18: USART SYNCHRONOUS RECEIVE (MASTER/SLAVE) TIMING

### TABLE 17-13: USART SYNCHRONOUS RECEIVE REQUIREMENTS

| Param<br>No. | Symbol   | Characteristic                                                                 | Min | Тур† | Max | Units | Conditions |

|--------------|----------|--------------------------------------------------------------------------------|-----|------|-----|-------|------------|

| 125          | TDTV2CKL | SYNC RCV (MASTER & SLAVE)<br>Data Setup before $CK \downarrow$ (DT setup time) | 15  |      |     | ns    |            |

| 126          | TCKL2DTL | Data Hold after CK $\downarrow$ (DT hold time)                                 | 15  | _    |     | ns    |            |

† Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

NOTES:

### APPENDIX A: REVISION HISTORY

### **Revision A (November 2001)**

Original data sheet for PIC16F87XA devices. The devices presented are enhanced versions of the PIC16F87X microcontrollers discussed in the *"PIC16F87X Data Sheet"* (DS30292).

### **Revision B (October 2003)**

This revision includes the DC and AC Characteristics Graphs and Tables. The Electrical Specifications in **Section 17.0 "Electrical Characteristics"** have been updated and there have been minor corrections to the data sheet text.

### Revision C (January 2013)

Added a note to each package outline drawing.

### APPENDIX B: DEVICE DIFFERENCES

The differences between the devices in this data sheet are listed in Table B-1.

|                                        | PIC16F873A                                              | PIC16F874A                                              | PIC16F876A                                              | PIC16F877A                                              |

|----------------------------------------|---------------------------------------------------------|---------------------------------------------------------|---------------------------------------------------------|---------------------------------------------------------|

| Flash Program Memory<br>(14-bit words) | 4K                                                      | 4K                                                      | 8K                                                      | 8K                                                      |

| Data Memory (bytes)                    | 192                                                     | 192                                                     | 368                                                     | 368                                                     |

| EEPROM Data Memory (bytes)             | 128                                                     | 128                                                     | 256                                                     | 256                                                     |

| Interrupts                             | 14                                                      | 15                                                      | 14                                                      | 15                                                      |

| I/O Ports                              | Ports A, B, C                                           | Ports A, B, C, D, E                                     | Ports A, B, C                                           | Ports A, B, C, D, E                                     |

| Serial Communications                  | MSSP, USART                                             | MSSP, USART                                             | MSSP, USART                                             | MSSP, USART                                             |

| Parallel Slave Port                    | No                                                      | Yes                                                     | No                                                      | Yes                                                     |

| 10-bit Analog-to-Digital Module        | 5 input channels                                        | 8 input channels                                        | 5 input channels                                        | 8 input channels                                        |

| Packages                               | 28-pin PDIP<br>28-pin SOIC<br>28-pin SSOP<br>28-pin QFN | 40-pin PDIP<br>44-pin PLCC<br>44-pin TQFP<br>44-pin QFN | 28-pin PDIP<br>28-pin SOIC<br>28-pin SSOP<br>28-pin QFN | 40-pin PDIP<br>44-pin PLCC<br>44-pin TQFP<br>44-pin QFN |

## INDEX

Α

| A/D                                            | 127      |

|------------------------------------------------|----------|

| Acquisition Requirements                       |          |

| ADCON0 Register                                |          |

| ADCON1 Register                                |          |

| ADIF Bit                                       |          |

| ADRESH Register                                |          |

| ADRESL Register                                |          |

| Analog Port Pins                               |          |

| Associated Registers and Bits                  |          |

| Calculating Acquisition Time                   |          |

| Configuring Analog Port Pins                   |          |

| Configuring the Interrupt                      |          |

| Configuring the Module                         |          |

| Conversion Clock                               |          |

| Conversions                                    |          |

| Converter Characteristics                      | 194      |

| Effects of a Reset                             |          |

| GO/DONE Bit                                    |          |

| Internal Sampling Switch (Rss) Impedance       |          |

| Operation During Sleep                         |          |

| Result Registers                               |          |

| Source Impedance                               |          |

| A/D Conversion Requirements                    |          |

| Absolute Maximum Ratings                       |          |

| ACKSTAT                                        |          |

| ADCON0 Register                                |          |

| ADCON1 Register                                |          |

| Addressable Universal Synchronous Asynchronous |          |

| Receiver Transmitter. See USART.               |          |

| ADRESH Register                                |          |

| ADRESL Register                                |          |

| Analog-to-Digital Converter. See A/D.          |          |

| Application Notes                              |          |

| AN552 (Implementing Wake-up                    |          |

| on Key Stroke)                                 |          |

| AN556 (Implementing a Table Read)              |          |

| Assembler                                      |          |

| MPASM Assembler                                | 167      |

| Asynchronous Reception                         |          |

| Associated Registers                           | 118, 120 |

| Asynchronous Transmission                      |          |

| Associated Registers                           | 116      |

| В                                              |          |

| -                                              | 40.00    |

| Banking, Data Memory                           |          |

| Baud Rate Generator                            |          |

| Associated Registers                           |          |

| BCLIF                                          |          |

| MSSP (SPI Mode)                                   |     |

|---------------------------------------------------|-----|

| On-Chip Reset Circuit 1                           | 47  |

| PIC16F873A/PIC16F876A Architecture                | . 6 |

| PIC16F874A/PIC16F877A Architecture                | . 7 |

| PORTC                                             |     |

| Peripheral Output Override                        |     |

| (RC2:0, RC7:5) Pins                               | 46  |

| Peripheral Output Override (RC4:3) Pins           | 46  |

| PORTD (in I/O Port Mode)                          |     |

| PORTD and PORTE (Parallel Slave Port)             |     |

| PORTE (In I/O Port Mode)                          |     |

| RA3:RA0 Pins                                      |     |

| RA4/T0CKI Pin                                     |     |

| RA5 Pin                                           |     |

| RB3:RB0 Pins                                      |     |

| RB7:RB4 Pins                                      |     |

| RC Oscillator Mode                                |     |

| Recommended MCLR Circuit                          | 10  |

| Simplified PWM Mode                               |     |

| Timer0/WDT Prescaler                              |     |

| Timero/WDT Prescaler                              |     |

|                                                   |     |

| Timer2                                            |     |

| USART Receive                                     |     |

| USART Transmit                                    |     |

| Watchdog Timer                                    | 55  |

| BOR. See Brown-out Reset.                         |     |

| BRG. See Baud Rate Generator.                     |     |

| BRGH Bit 1                                        |     |

| Brown-out Reset (BOR) 143, 147, 148, 149, 1       |     |

| BOR Status (BOR Bit)                              |     |

| Bus Collision During a Repeated Start Condition 1 |     |

| Bus Collision During a Start Condition 1          |     |

| Bus Collision During a Stop Condition 1           |     |

| Bus Collision Interrupt Flag bit, BCLIF           | 28  |

| С                                                 |     |

| -                                                 |     |

| C Compilers                                       |     |

| MPLAB C17 1                                       |     |

| MPLAB C18 1                                       |     |

| MPLAB C30 1                                       |     |

| Capture/Compare/PWM (CCP)                         | 63  |

| Associated Registers                              |     |

| Capture, Compare and Timer1                       |     |

| PWM and Timer2                                    | 69  |

| Capture Mode                                      | 65  |

| CCP1IF                                            | 65  |

| Prescaler                                         | 65  |

| CCP Timer Resources                               | 63  |

| Compare                                           |     |

| Special Event Trigger Output of CCP1              | 66  |

| Special Event Trigger Output of CCP2              |     |

| Compare Mode                                      |     |

| Software Interrupt Mode                           |     |

| Special Event Trigger                             |     |

|                                                   |     |

| Comparator I/O Operating Modes      |  |

|-------------------------------------|--|

| Comparator Output                   |  |

| Comparator Voltage Reference        |  |

| Compare Mode Operation              |  |

| Crystal/Ceramic Resonator Operation |  |

| (HS, XT or LP Osc Configuration) .  |  |

| External Clock Input Operation      |  |

| (HS, XT or LP Osc Configuration).   |  |

BF ......101

A/D129Analog Input Model130, 139Baud Rate Generator97Capture Mode Operation65

Block Diagrams

### I

| I/O Ports                                                                                                                                                                                                   |                                                                                                                                                                                              |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| I2C Bus Data Requirements                                                                                                                                                                                   |                                                                                                                                                                                              |

| I <sup>2</sup> C Bus Start/Stop Bits Requirements                                                                                                                                                           |                                                                                                                                                                                              |

|                                                                                                                                                                                                             |                                                                                                                                                                                              |

| I <sup>2</sup> C Mode                                                                                                                                                                                       |                                                                                                                                                                                              |

| Registers                                                                                                                                                                                                   | 80                                                                                                                                                                                           |

| I <sup>2</sup> C Mode                                                                                                                                                                                       | 80                                                                                                                                                                                           |

| ACK Pulse                                                                                                                                                                                                   |                                                                                                                                                                                              |

|                                                                                                                                                                                                             |                                                                                                                                                                                              |

| Acknowledge Sequence Timing                                                                                                                                                                                 |                                                                                                                                                                                              |

| Baud Rate Generator                                                                                                                                                                                         |                                                                                                                                                                                              |

| Bus Collision                                                                                                                                                                                               |                                                                                                                                                                                              |

| Repeated Start Condition                                                                                                                                                                                    |                                                                                                                                                                                              |

| Start Condition                                                                                                                                                                                             |                                                                                                                                                                                              |

|                                                                                                                                                                                                             |                                                                                                                                                                                              |

| Stop Condition                                                                                                                                                                                              |                                                                                                                                                                                              |

| Clock Arbitration                                                                                                                                                                                           |                                                                                                                                                                                              |

| Effect of a Reset                                                                                                                                                                                           | 105                                                                                                                                                                                          |

| General Call Address Support                                                                                                                                                                                | 94                                                                                                                                                                                           |

| Master Mode                                                                                                                                                                                                 |                                                                                                                                                                                              |

|                                                                                                                                                                                                             |                                                                                                                                                                                              |

| Operation                                                                                                                                                                                                   |                                                                                                                                                                                              |

| Repeated Start Timing                                                                                                                                                                                       | 100                                                                                                                                                                                          |

| Master Mode Reception                                                                                                                                                                                       |                                                                                                                                                                                              |

| Master Mode Start Condition                                                                                                                                                                                 |                                                                                                                                                                                              |

|                                                                                                                                                                                                             |                                                                                                                                                                                              |

| Master Mode Transmission                                                                                                                                                                                    |                                                                                                                                                                                              |

| Multi-Master Communication, Bus Collision                                                                                                                                                                   |                                                                                                                                                                                              |

| and Arbitration                                                                                                                                                                                             | 105                                                                                                                                                                                          |

| Multi-Master Mode                                                                                                                                                                                           | 105                                                                                                                                                                                          |

| Read/Write Bit Information (R/W Bit)                                                                                                                                                                        |                                                                                                                                                                                              |

|                                                                                                                                                                                                             |                                                                                                                                                                                              |

| Serial Clock (RC3/SCK/SCL)                                                                                                                                                                                  |                                                                                                                                                                                              |

| Slave Mode                                                                                                                                                                                                  |                                                                                                                                                                                              |

| Addressing                                                                                                                                                                                                  | 84                                                                                                                                                                                           |

| Reception                                                                                                                                                                                                   |                                                                                                                                                                                              |

| Transmission                                                                                                                                                                                                |                                                                                                                                                                                              |

| Sleep Operation                                                                                                                                                                                             |                                                                                                                                                                                              |

|                                                                                                                                                                                                             |                                                                                                                                                                                              |

|                                                                                                                                                                                                             |                                                                                                                                                                                              |

| Stop Condition Timing                                                                                                                                                                                       | 104                                                                                                                                                                                          |

| Stop Condition Timing<br>ID Locations                                                                                                                                                                       | 104                                                                                                                                                                                          |

|                                                                                                                                                                                                             | 104<br>143, 157                                                                                                                                                                              |

| ID Locations<br>In-Circuit Debugger                                                                                                                                                                         | 143, 157<br>143, 157<br>143, 157                                                                                                                                                             |

| ID Locations<br>In-Circuit Debugger<br>Resources                                                                                                                                                            | 104<br>143, 157<br>143, 157<br>157                                                                                                                                                           |

| ID Locations<br>In-Circuit Debugger<br>Resources<br>In-Circuit Serial Programming (ICSP)                                                                                                                    | 143, 157<br>143, 157<br>143, 157<br>143, 157<br>143, 158                                                                                                                                     |

| ID Locations<br>In-Circuit Debugger<br>Resources<br>In-Circuit Serial Programming (ICSP)<br>INDF Register                                                                                                   | 143, 157<br>143, 157<br>143, 157<br>157<br>157<br>143, 158<br>19, 20, 31                                                                                                                     |

| ID Locations<br>In-Circuit Debugger<br>Resources<br>In-Circuit Serial Programming (ICSP)<br>INDF Register<br>Indirect Addressing                                                                            |                                                                                                                                                                                              |

| ID Locations<br>In-Circuit Debugger<br>Resources<br>In-Circuit Serial Programming (ICSP)<br>INDF Register<br>Indirect Addressing<br>FSR Register                                                            |                                                                                                                                                                                              |

| ID Locations<br>In-Circuit Debugger<br>Resources<br>In-Circuit Serial Programming (ICSP)<br>INDF Register<br>Indirect Addressing                                                                            |                                                                                                                                                                                              |

| ID Locations<br>In-Circuit Debugger<br>Resources<br>In-Circuit Serial Programming (ICSP)<br>INDF Register<br>Indirect Addressing<br>FSR Register                                                            |                                                                                                                                                                                              |

| ID Locations<br>In-Circuit Debugger<br>Resources<br>In-Circuit Serial Programming (ICSP)<br>INDF Register<br>Indirect Addressing<br>FSR Register<br>Instruction Format<br>Instruction Set                   |                                                                                                                                                                                              |

| ID Locations<br>In-Circuit Debugger<br>Resources<br>In-Circuit Serial Programming (ICSP)<br>INDF Register<br>Indirect Addressing<br>FSR Register<br>Instruction Format<br>Instruction Set<br>ADDLW          |                                                                                                                                                                                              |

| ID Locations<br>In-Circuit Debugger<br>Resources<br>In-Circuit Serial Programming (ICSP)<br>INDF Register<br>Indirect Addressing<br>FSR Register<br>Instruction Format<br>Instruction Set<br>ADDLW<br>ADDWF |                                                                                                                                                                                              |

| ID Locations<br>In-Circuit Debugger                                                                                                                                                                         |                                                                                                                                                                                              |

| ID Locations<br>In-Circuit Debugger<br>Resources<br>In-Circuit Serial Programming (ICSP)<br>INDF Register<br>Indirect Addressing<br>FSR Register<br>Instruction Format<br>Instruction Set<br>ADDLW<br>ADDWF |                                                                                                                                                                                              |

| ID Locations<br>In-Circuit Debugger                                                                                                                                                                         | 104<br>143, 157<br>143, 157<br>143, 157<br>143, 158<br>19, 20, 31<br>31<br>                                                                                                                  |

| ID Locations<br>In-Circuit Debugger                                                                                                                                                                         | 104<br>143, 157<br>143, 157<br>143, 157<br>143, 158<br>19, 20, 31<br>31<br>                                                                                                                  |

| ID Locations<br>In-Circuit Debugger                                                                                                                                                                         | 104<br>143, 157<br>143, 157<br>143, 157<br>143, 158<br>19, 20, 31<br>31<br>                                                                                                                  |

| ID Locations<br>In-Circuit Debugger                                                                                                                                                                         | 104<br>104<br>143, 157<br>143, 157<br>143, 158<br>19, 20, 31<br>31<br>16<br>169<br>161<br>161<br>161<br>161<br>161<br>161<br>161<br>161<br>161<br>                                           |

| ID Locations<br>In-Circuit Debugger                                                                                                                                                                         | 104<br>104<br>143, 157<br>143, 157<br>143, 158<br>19, 20, 31<br>31<br>16<br>169<br>169<br>161<br>161<br>161<br>161<br>161<br>161<br>161<br>162<br>162<br>                                    |

| ID Locations<br>In-Circuit Debugger                                                                                                                                                                         | 104<br>104<br>143, 157<br>143, 157<br>143, 158<br>19, 20, 31<br>31<br>16<br>169<br>169<br>161<br>161<br>161<br>161<br>161<br>161<br>161<br>162<br>162<br>162<br>                             |

| ID Locations<br>In-Circuit Debugger                                                                                                                                                                         | 104<br>104<br>143, 157<br>143, 157<br>143, 158<br>19, 20, 31<br>31<br>16<br>169<br>161<br>161<br>161<br>161<br>161<br>161<br>161<br>162<br>162<br>162<br>162<br>                             |

| ID Locations<br>In-Circuit Debugger                                                                                                                                                                         | 104<br>104<br>143, 157<br>143, 157<br>143, 158<br>19, 20, 31<br>31<br>16<br>169<br>169<br>161<br>161<br>161<br>161<br>161<br>161<br>162<br>162<br>162<br>162<br>162<br>162<br>               |

| ID Locations<br>In-Circuit Debugger                                                                                                                                                                         | 104<br>104<br>143, 157<br>143, 157<br>143, 158<br>19, 20, 31<br>31<br>16<br>169<br>169<br>161<br>161<br>161<br>161<br>161<br>161<br>162<br>162<br>162<br>162<br>162<br>162<br>               |

| ID Locations<br>In-Circuit Debugger                                                                                                                                                                         | 104<br>104<br>143, 157<br>143, 157<br>143, 158<br>19, 20, 31<br>31<br>16<br>169<br>169<br>161<br>161<br>161<br>161<br>161<br>161<br>162<br>162<br>162<br>162<br>162<br>162<br>162<br>        |

| ID Locations<br>In-Circuit Debugger                                                                                                                                                                         | 104<br>104<br>143, 157<br>143, 157<br>143, 158<br>19, 20, 31<br>31<br>16<br>169<br>161<br>161<br>161<br>161<br>161<br>161<br>161<br>162<br>162<br>162<br>162<br>162<br>162<br>162<br>162<br> |