Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                    |

|----------------------------|---------------------------------------------------------------------------|

| Core Processor             | PIC                                                                       |

| Core Size                  | 8-Bit                                                                     |

| Speed                      | 20MHz                                                                     |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                         |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                     |

| Number of I/O              | 33                                                                        |

| Program Memory Size        | 14KB (8K x 14)                                                            |

| Program Memory Type        | FLASH                                                                     |

| EEPROM Size                | 256 x 8                                                                   |

| RAM Size                   | 368 x 8                                                                   |

| Voltage - Supply (Vcc/Vdd) | 4V ~ 5.5V                                                                 |

| Data Converters            | A/D 8x10b                                                                 |

| Oscillator Type            | External                                                                  |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                         |

| Mounting Type              | Surface Mount                                                             |

| Package / Case             | 44-VQFN Exposed Pad                                                       |

| Supplier Device Package    | 44-QFN (8x8)                                                              |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16f877a-i-ml |

|                            |                                                                           |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# 1.0 DEVICE OVERVIEW

This document contains device specific information about the following devices:

- PIC16F873A

- PIC16F874A

- PIC16F876A

- PIC16F877A

PIC16F873A/876A devices are available only in 28-pin packages, while PIC16F874A/877A devices are available in 40-pin and 44-pin packages. All devices in the PIC16F87XA family share common architecture with the following differences:

- The PIC16F873A and PIC16F874A have one-half of the total on-chip memory of the PIC16F876A and PIC16F877A

- The 28-pin devices have three I/O ports, while the 40/44-pin devices have five

- The 28-pin devices have fourteen interrupts, while the 40/44-pin devices have fifteen

- The 28-pin devices have five A/D input channels, while the 40/44-pin devices have eight

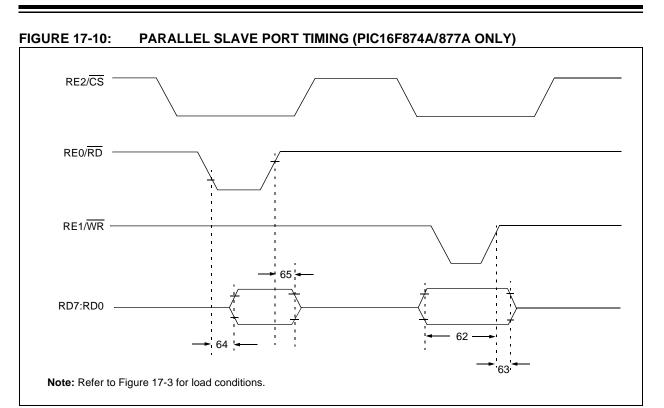

- The Parallel Slave Port is implemented only on the 40/44-pin devices

The available features are summarized in Table 1-1. Block diagrams of the PIC16F873A/876A and PIC16F874A/877A devices are provided in Figure 1-1 and Figure 1-2, respectively. The pinouts for these device families are listed in Table 1-2 and Table 1-3.

Additional information may be found in the PIC<sup>®</sup> Mid-Range Reference Manual (DS33023), which may be obtained from your local Microchip Sales Representative or downloaded from the Microchip web site. The Reference Manual should be considered a complementary document to this data sheet and is highly recommended reading for a better understanding of the device architecture and operation of the peripheral modules.

| Key Features                           | PIC16F873A                                              | PIC16F874A                                              | PIC16F876A                                              | PIC16F877A                                              |

|----------------------------------------|---------------------------------------------------------|---------------------------------------------------------|---------------------------------------------------------|---------------------------------------------------------|

| Operating Frequency                    | DC – 20 MHz                                             |

| Resets (and Delays)                    | POR, BOR<br>(PWRT, OST)                                 | POR, BOR<br>(PWRT, OST)                                 | POR, BOR<br>(PWRT, OST)                                 | POR, BOR<br>(PWRT, OST)                                 |

| Flash Program Memory<br>(14-bit words) | 4K                                                      | 4K                                                      | 8K                                                      | 8K                                                      |

| Data Memory (bytes)                    | 192                                                     | 192                                                     | 368                                                     | 368                                                     |

| EEPROM Data Memory (bytes)             | 128                                                     | 128                                                     | 256                                                     | 256                                                     |

| Interrupts                             | 14                                                      | 15                                                      | 14                                                      | 15                                                      |

| I/O Ports                              | Ports A, B, C                                           | Ports A, B, C, D, E                                     | Ports A, B, C                                           | Ports A, B, C, D, E                                     |

| Timers                                 | 3                                                       | 3                                                       | 3                                                       | 3                                                       |

| Capture/Compare/PWM modules            | 2                                                       | 2                                                       | 2                                                       | 2                                                       |

| Serial Communications                  | MSSP, USART                                             | MSSP, USART                                             | MSSP, USART                                             | MSSP, USART                                             |

| Parallel Communications                | —                                                       | PSP                                                     | _                                                       | PSP                                                     |

| 10-bit Analog-to-Digital Module        | 5 input channels                                        | 8 input channels                                        | 5 input channels                                        | 8 input channels                                        |

| Analog Comparators                     | 2                                                       | 2                                                       | 2                                                       | 2                                                       |

| Instruction Set                        | 35 Instructions                                         | 35 Instructions                                         | 35 Instructions                                         | 35 Instructions                                         |

| Packages                               | 28-pin PDIP<br>28-pin SOIC<br>28-pin SSOP<br>28-pin QFN | 40-pin PDIP<br>44-pin PLCC<br>44-pin TQFP<br>44-pin QFN | 28-pin PDIP<br>28-pin SOIC<br>28-pin SSOP<br>28-pin QFN | 40-pin PDIP<br>44-pin PLCC<br>44-pin TQFP<br>44-pin QFN |

### TABLE 1-1:PIC16F87XA DEVICE FEATURES

### 2.2.2 SPECIAL FUNCTION REGISTERS

The Special Function Registers are registers used by the CPU and peripheral modules for controlling the desired operation of the device. These registers are implemented as static RAM. A list of these registers is given in Table 2-1. The Special Function Registers can be classified into two sets: core (CPU) and peripheral. Those registers associated with the core functions are described in detail in this section. Those related to the operation of the peripheral features are described in detail in the peripheral features section.

TABLE 2-1:SPECIAL FUNCTION REGISTER SUMMARY

| Address              | Name    | Bit 7                | Bit 6                                | Bit 5        | Bit 4           | Bit 3          | Bit 2            | Bit 1        | Bit 0         | Value on:<br>POR, BOR | Details<br>on page: |

|----------------------|---------|----------------------|--------------------------------------|--------------|-----------------|----------------|------------------|--------------|---------------|-----------------------|---------------------|

| Bank 0               |         |                      |                                      |              |                 |                |                  |              |               |                       |                     |

| 00h <sup>(3)</sup>   | INDF    | Addressing           | g this locatio                       | n uses cont  | ents of FSR t   | o address da   | ata memory (     | not a physic | cal register) | 0000 0000             | 31, 150             |

| 01h                  | TMR0    | Timer0 Mo            | dule Regist                          | er           |                 |                |                  |              |               | xxxx xxxx             | 55, 150             |

| 02h <sup>(3)</sup>   | PCL     | Program C            | ounter (PC)                          | Least Sign   | ificant Byte    |                |                  |              | -             | 0000 0000             | 30, 150             |

| 03h <sup>(3)</sup>   | STATUS  | IRP                  | RP1                                  | RP0          | TO              | PD             | Z                | DC           | С             | 0001 1xxx             | 22, 150             |

| 04h <sup>(3)</sup>   | FSR     | Indirect Da          | ta Memory                            | Address Po   | inter           |                |                  |              |               | xxxx xxxx             | 31, 150             |

| 05h                  | PORTA   | _                    |                                      | PORTA Da     | ata Latch whe   | en written: PO | ORTA pins w      | hen read     |               | 0x 0000               | 43, 150             |

| 06h                  | PORTB   | PORTB Da             | ata Latch wh                         | nen written: | PORTB pins      | when read      |                  |              |               | xxxx xxxx             | 45, 150             |

| 07h                  | PORTC   | PORTC Da             | ata Latch wh                         | nen written: | PORTC pins      | when read      |                  |              |               | xxxx xxxx             | 47, 150             |

| 08h <sup>(4)</sup>   | PORTD   | PORTD Da             | ata Latch wh                         | nen written: | PORTD pins      | when read      |                  |              |               | xxxx xxxx             | 48, 150             |

| 09h <sup>(4)</sup>   | PORTE   | _                    |                                      | —            | _               | _              | RE2              | RE1          | RE0           | xxx                   | 49, 150             |

| 0Ah <sup>(1,3)</sup> | PCLATH  | _                    | _                                    | _            | Write Buffer    | for the uppe   | er 5 bits of the | e Program C  | Counter       | 0 0000                | 30, 150             |

| 0Bh <sup>(3)</sup>   | INTCON  | GIE                  | PEIE                                 | TMR0IE       | INTE            | RBIE           | TMR0IF           | INTF         | RBIF          | 0000 000x             | 24, 150             |

| 0Ch                  | PIR1    | PSPIF <sup>(3)</sup> | ADIF                                 | RCIF         | TXIF            | SSPIF          | CCP1IF           | TMR2IF       | TMR1IF        | 0000 0000             | 26, 150             |

| 0Dh                  | PIR2    | _                    | CMIF                                 | —            | EEIF            | BCLIF          | —                | _            | CCP2IF        | -0-0 00               | 28, 150             |

| 0Eh                  | TMR1L   | Holding Re           | egister for th                       | e Least Sig  | nificant Byte   | of the 16-bit  | TMR1 Regis       | ter          |               | xxxx xxxx             | 60, 150             |

| 0Fh                  | TMR1H   | Holding Re           | egister for th                       | e Most Sigr  | nificant Byte c | of the 16-bit  | TMR1 Regist      | er           |               | xxxx xxxx             | 60, 150             |

| 10h                  | T1CON   | _                    | —                                    | T1CKPS1      | T1CKPS0         | T1OSCEN        | T1SYNC           | TMR1CS       | TMR10N        | 00 0000               | 57, 150             |

| 11h                  | TMR2    | Timer2 Mo            | dule Regist                          | er           |                 |                |                  |              |               | 0000 0000             | 62, 150             |

| 12h                  | T2CON   | _                    | TOUTPS3                              | TOUTPS2      | TOUTPS1         | TOUTPS0        | TMR2ON           | T2CKPS1      | T2CKPS0       | -000 0000             | 61, 150             |

| 13h                  | SSPBUF  | Synchrono            | us Serial Po                         | ort Receive  | Buffer/Transr   | nit Register   |                  |              |               | xxxx xxxx             | 79, 150             |

| 14h                  | SSPCON  | WCOL                 | SSPOV                                | SSPEN        | СКР             | SSPM3          | SSPM2            | SSPM1        | SSPM0         | 0000 0000             | 82, 82,<br>150      |

| 15h                  | CCPR1L  | Capture/Co           | ompare/PW                            | M Register   | 1 (LSB)         |                |                  |              |               | xxxx xxxx             | 63, 150             |

| 16h                  | CCPR1H  | Capture/Co           | ompare/PW                            | M Register   | 1 (MSB)         |                |                  |              |               | xxxx xxxx             | 63, 150             |

| 17h                  | CCP1CON | _                    | _                                    | CCP1X        | CCP1Y           | CCP1M3         | CCP1M2           | CCP1M1       | CCP1M0        | 00 0000               | 64, 150             |

| 18h                  | RCSTA   | SPEN                 | RX9                                  | SREN         | CREN            | ADDEN          | FERR             | OERR         | RX9D          | 0000 000x             | 112, 150            |

| 19h                  | TXREG   | USART Tra            | ansmit Data                          | Register     |                 |                |                  |              |               | 0000 0000             | 118, 150            |

| 1Ah                  | RCREG   | USART Re             | eceive Data                          | Register     |                 |                |                  |              |               | 0000 0000             | 118, 150            |

| 1Bh                  | CCPR2L  | Capture/C            | Capture/Compare/PWM Register 2 (LSB) |              |                 |                |                  |              |               | xxxx xxxx             | 63, 150             |

| 1Ch                  | CCPR2H  | Capture/C            | ompare/PW                            | M Register   | 2 (MSB)         |                |                  |              |               | xxxx xxxx             | 63, 150             |

| 1Dh                  | CCP2CON | _                    | _                                    | CCP2X        | CCP2Y           | CCP2M3         | CCP2M2           | CCP2M1       | CCP2M0        | 00 0000               | 64, 150             |

| 1Eh                  | ADRESH  | A/D Result           | Register H                           | igh Byte     |                 |                |                  |              |               | xxxx xxxx             | 133, 150            |

| 1Fh                  | ADCON0  | ADCS1                | ADCS0                                | CHS2         | CHS1            | CHS0           | GO/DONE          |              | ADON          | 0000 00-0             | 127, 150            |

**Legend:** x = unknown, u = unchanged, q = value depends on condition, - = unimplemented, read as '0', r = reserved. Shaded locations are unimplemented, read as '0'.

**Note 1:** The upper byte of the program counter is not directly accessible. PCLATH is a holding register for the PC<12:8>, whose contents are transferred to the upper byte of the program counter.

2: Bits PSPIE and PSPIF are reserved on PIC16F873A/876A devices; always maintain these bits clear.

**3:** These registers can be addressed from any bank.

4: PORTD, PORTE, TRISD and TRISE are not implemented on PIC16F873A/876A devices, read as '0'.

5: Bit 4 of EEADRH implemented only on the PIC16F876A/877A devices.

| Address               | Name       | Bit 7                                                        | Bit 6                         | Bit 5        | Bit 4         | Bit 3        | Bit 2            | Bit 1        | Bit 0         | Value on:<br>POR, BOR | Details<br>on page: |

|-----------------------|------------|--------------------------------------------------------------|-------------------------------|--------------|---------------|--------------|------------------|--------------|---------------|-----------------------|---------------------|

| Bank 2                |            |                                                              |                               |              |               |              |                  |              |               |                       |                     |

| 100h <sup>(3)</sup>   | INDF       | Addressing                                                   | g this locatio                | n uses cont  | ents of FSR t | o address da | ata memory (     | not a physic | cal register) | 0000 0000             | 31, 150             |

| 101h                  | TMR0       | Timer0 Mo                                                    | dule Registe                  | ər           |               |              |                  |              |               | xxxx xxxx             | 55, 150             |

| 102h <sup>(3)</sup>   | PCL        | Program C                                                    | Counter's (PC                 | C) Least Sig | nificant Byte |              |                  |              |               | 0000 0000             | 30, 150             |

| 103h <sup>(3)</sup>   | STATUS     | IRP                                                          | RP1                           | RP0          | TO            | PD           | Z                | DC           | С             | 0001 1xxx             | 22, 150             |

| 104h <sup>(3)</sup>   | FSR        | Indirect Da                                                  | ata Memory                    | Address Po   | inter         |              |                  |              |               | xxxx xxxx             | 31, 150             |

| 105h                  | —          | Unimplem                                                     | ented                         |              |               |              |                  |              |               | _                     | —                   |

| 106h                  | PORTB      | PORTB Da                                                     | ata Latch wh                  | en written:  | PORTB pins    | when read    |                  |              |               | xxxx xxxx             | 45, 150             |

| 107h                  | —          | Unimplem                                                     | ented                         |              |               |              |                  |              |               | _                     | _                   |

| 108h                  | —          | Unimplem                                                     | ented                         |              |               |              |                  |              |               | _                     | —                   |

| 109h                  | —          | Unimplem                                                     | ented                         |              |               |              |                  |              |               | _                     | —                   |

| 10Ah <sup>(1,3)</sup> | PCLATH     | _                                                            | _                             | _            | Write Buffer  | for the uppe | er 5 bits of the | e Program C  | Counter       | 0 0000                | 30, 150             |

| 10Bh <sup>(3)</sup>   | INTCON     | GIE                                                          | PEIE                          | TMR0IE       | INTE          | RBIE         | TMR0IF           | INTF         | RBIF          | 0000 000x             | 24, 150             |

| 10Ch                  | EEDATA     | EEPROM                                                       | Data Regist                   | er Low Byte  | )             |              |                  |              |               | xxxx xxxx             | 39, 151             |

| 10Dh                  | EEADR      | EEPROM                                                       | Address Re                    | gister Low E | Byte          |              |                  |              |               | xxxx xxxx             | 39, 151             |

| 10Eh                  | EEDATH     |                                                              |                               | EEPROM       | Data Registe  | r High Byte  |                  |              |               | xx xxxx               | 39, 151             |

| 10Fh                  | EEADRH     | _                                                            | _                             | _            | (5)           | EEPROM A     | Address Regi     | ster High B  | yte           | xxxx                  | 39, 151             |

| Bank 3                |            |                                                              |                               |              |               | -            |                  |              |               |                       |                     |

| 180h <sup>(3)</sup>   | INDF       | Addressing                                                   | g this locatio                | n uses cont  | ents of FSR t | o address da | ata memory (     | not a physic | cal register) | 0000 0000             | 31, 150             |

| 181h                  | OPTION_REG | RBPU                                                         | INTEDG                        | TOCS         | TOSE          | PSA          | PS2              | PS1          | PS0           | 1111 1111             | 23, 150             |

| 182h <sup>(3)</sup>   | PCL        | Program C                                                    | Counter (PC)                  | Least Sign   | ificant Byte  |              |                  |              |               | 0000 0000             | 30, 150             |

| 183h <sup>(3)</sup>   | STATUS     | IRP                                                          | RP1                           | RP0          | TO            | PD           | Z                | DC           | С             | 0001 1xxx             | 22, 150             |

| 184h <sup>(3)</sup>   | FSR        | Indirect Da                                                  | ata Memory                    | Address Po   | inter         |              |                  |              |               | xxxx xxxx             | 31, 150             |

| 185h                  | _          | Unimplem                                                     | ented                         |              |               |              |                  |              |               | _                     |                     |

| 186h                  | TRISB      | PORTB Da                                                     | ata Direction                 | Register     |               |              |                  |              |               | 1111 1111             | 45, 150             |

| 187h                  | _          | Unimplem                                                     | ented                         | -            |               |              |                  |              |               | _                     | —                   |

| 188h                  | —          | Unimplem                                                     | ented                         |              |               |              |                  |              |               | _                     |                     |

| 189h                  |            | Unimplem                                                     | ented                         |              |               |              |                  |              |               | _                     | _                   |

| 18Ah <sup>(1,3)</sup> | PCLATH     | — — Write Buffer for the upper 5 bits of the Program Counter |                               |              |               |              |                  |              | 0 0000        | 30, 150               |                     |

| 18Bh <sup>(3)</sup>   | INTCON     | GIE                                                          | PEIE                          | TMR0IE       | INTE          | RBIE         | TMR0IF           | INTF         | RBIF          | 0000 000x             | 24, 150             |

| 18Ch                  | EECON1     | EEPGD                                                        | —                             | —            | —             | WRERR        | WREN             | WR           | RD            | x x000                | 34, 151             |

| 18Dh                  | EECON2     | EEPROM                                                       | Control Reg                   | ister 2 (not | a physical re | gister)      |                  |              |               |                       | 39, 151             |

| 18Eh                  | —          | Reserved;                                                    | maintain cle                  | ar           |               |              |                  |              |               | 0000 0000             | —                   |

| 18Fh                  | —          | Reserved;                                                    | Reserved; maintain clear 0000 |              |               |              |                  |              |               |                       |                     |

| TABLE 2-1: | SPECIAL FUNCTION REGISTER | SUMMARY (CON | (INUED) |

|------------|---------------------------|--------------|---------|

|            |                           |              |         |

**Legend:** x = unknown, u = unchanged, q = value depends on condition, - = unimplemented, read as '0', r = reserved. Shaded locations are unimplemented, read as '0'.

Note 1: The upper byte of the program counter is not directly accessible. PCLATH is a holding register for the PC<12:8>, whose contents are transferred to the upper byte of the program counter.

2: Bits PSPIE and PSPIF are reserved on PIC16F873A/876A devices; always maintain these bits clear.

3: These registers can be addressed from any bank.

4: PORTD, PORTE, TRISD and TRISE are not implemented on PIC16F873A/876A devices, read as '0'.

5: Bit 4 of EEADRH implemented only on the PIC16F876A/877A devices.

# 2.2.2.3 INTCON Register

The INTCON register is a readable and writable register, which contains various enable and flag bits for the TMR0 register overflow, RB port change and external RB0/INT pin interrupts. Note: Interrupt flag bits are set when an interrupt condition occurs regardless of the state of its corresponding enable bit or the global enable bit, GIE (INTCON<7>). User software should ensure the appropriate interrupt flag bits are clear prior to enabling an interrupt.

### REGISTER 2-3: INTCON REGISTER (ADDRESS 0Bh, 8Bh, 10Bh, 18Bh)

| R/W-0      | R/W-0                         | R/W-0                                    | R/W-0        | R/W-0        | R/W-0         | R/W-0        | R/W-x |

|------------|-------------------------------|------------------------------------------|--------------|--------------|---------------|--------------|-------|

| GIE        | PEIE                          | TMR0IE                                   | INTE         | RBIE         | TMR0IF        | INTF         | RBIF  |

| bit 7      |                               |                                          |              |              |               |              | bit 0 |

|            | al Interrupt E                |                                          |              |              |               |              |       |

|            | s all unmas<br>es all interru | ked interrupt<br>pts                     | ts           |              |               |              |       |

| PEIE: Peri | oheral Interr                 | upt Enable b                             | oit          |              |               |              |       |

|            |                               | ked peripher<br>eral interrup            | •            |              |               |              |       |

| TMR0IE: T  | MR0 Overfl                    | ow Interrupt                             | Enable bit   |              |               |              |       |

|            | s the TMR0                    |                                          |              |              |               |              |       |

|            | es the TMR                    | •                                        |              |              |               |              |       |

|            |                               | al Interrupt E                           |              |              |               |              |       |

|            |                               | NT external                              | •            |              |               |              |       |

|            |                               | NT external                              |              |              |               |              |       |

|            | •                             | e Interrupt Ei<br>rt change in           |              |              |               |              |       |

|            | •                             | ort change in                            | •            |              |               |              |       |

|            | •                             | ow Interrupt                             | •            |              |               |              |       |

| 1 = TMR0   | register has                  | overflowed                               | (must be cle | ared in soft | ware)         |              |       |

|            |                               | al Interrupt F                           |              |              |               |              |       |

| 1 = The RE | B0/INT exter                  | nal interrupt                            | occurred (n  |              | red in softwa | are)         |       |

| RBIF: RB I | Port Change                   | Interrupt Fl                             | ag bit       |              |               |              |       |

| the bit    | . Reading F                   | RB7:RB4 p<br>ORTB will e<br>n software). |              |              |               |              |       |

| 0 = None   | of the RB7:F                  | RB4 pins hav                             | ve changed   | state        |               |              |       |

| Legend:    |                               |                                          |              |              |               |              |       |

| R = Reada  | ble bit                       | W = W                                    | /ritable bit | U = Unin     | nplemented    | bit. read as | '0'   |

| R = Readable bit   | W = Writable bit | U = Unimplemented bit, read as '0'     |  |

|--------------------|------------------|----------------------------------------|--|

| - n = Value at POR | '1' = Bit is set | 0' = Bit is cleared x = Bit is unknown |  |

NOTES:

# 3.3 Reading Data EEPROM Memory

To read a data memory location, the user must write the address to the EEADR register, clear the EEPGD control bit (EECON1<7>) and then set control bit RD (EECON1<0>). The data is available in the very next cycle in the EEDATA register; therefore, it can be read in the next instruction (see Example 3-1). EEDATA will hold this value until another read or until it is written to by the user (during a write operation).

The steps to reading the EEPROM data memory are:

- 1. Write the address to EEADR. Make sure that the address is not larger than the memory size of the device.

- 2. Clear the EEPGD bit to point to EEPROM data memory.

- 3. Set the RD bit to start the read operation.

- 4. Read the data from the EEDATA register.

EXAMPLE 3-1: DATA EEPROM READ

| <br>• |                |   |                 |

|-------|----------------|---|-----------------|

| BSF   | STATUS, RP1    | ; |                 |

| BCF   | STATUS, RPO    | ; | Bank 2          |

| MOVF  | DATA_EE_ADDR,W | ; | Data Memory     |

| MOVWF | EEADR          | ; | Address to read |

| BSF   | STATUS, RPO    | ; | Bank 3          |

| BCF   | EECON1, EEPGD  | ; | Point to Data   |

|       |                | ; | memory          |

| BSF   | EECON1,RD      | ; | EE Read         |

| BCF   | STATUS, RPO    | ; | Bank 2          |

| MOVF  | EEDATA,W       | ; | W = EEDATA      |

|       |                |   |                 |

### 3.4 Writing to Data EEPROM Memory

To write an EEPROM data location, the user must first write the address to the EEADR register and the data to the EEDATA register. Then the user must follow a specific write sequence to initiate the write for each byte.

The write will not initiate if the write sequence is not exactly followed (write 55h to EECON2, write AAh to EECON2, then set WR bit) for each byte. We strongly recommend that interrupts be disabled during this code segment (see Example 3-2).

Additionally, the WREN bit in EECON1 must be set to enable write. This mechanism prevents accidental writes to data EEPROM due to errant (unexpected) code execution (i.e., lost programs). The user should keep the WREN bit clear at all times, except when updating EEPROM. The WREN bit is not cleared by hardware

After a write sequence has been initiated, clearing the WREN bit will not affect this write cycle. The WR bit will be inhibited from being set unless the WREN bit is set. At the completion of the write cycle, the WR bit is cleared in hardware and the EE Write Complete Interrupt Flag bit (EEIF) is set. The user can either enable this interrupt or poll this bit. EEIF must be cleared by software.

The steps to write to EEPROM data memory are:

- 1. If step 10 is not implemented, check the WR bit to see if a write is in progress.

- 2. Write the address to EEADR. Make sure that the address is not larger than the memory size of the device.

- 3. Write the 8-bit data value to be programmed in the EEDATA register.

- 4. Clear the EEPGD bit to point to EEPROM data memory.

- 5. Set the WREN bit to enable program operations.

- 6. Disable interrupts (if enabled).

- 7. Execute the special five instruction sequence:

- Write 55h to EECON2 in two steps (first to W, then to EECON2)

- Write AAh to EECON2 in two steps (first to W, then to EECON2)

- · Set the WR bit

- 8. Enable interrupts (if using interrupts).

- 9. Clear the WREN bit to disable program operations.

- At the completion of the write cycle, the WR bit is cleared and the EEIF interrupt flag bit is set. (EEIF must be cleared by firmware.) If step 1 is not implemented, then firmware should check for EEIF to be set, or WR to clear, to indicate the end of the program cycle.

#### EXAMPLE 3-2: DATA EEPROM WRITE

|                      | BSF   | STATUS, RP1             | ;                  |

|----------------------|-------|-------------------------|--------------------|

|                      | BSF   | STATUS, RPO             |                    |

|                      | BTFSC | EECON1,WR               | ;Wait for write    |

|                      | GOTO  | \$-1                    | ;to complete       |

|                      | BCF   | STATUS, RPO             | ;Bank 2            |

|                      | MOVF  | DATA_EE_ADDR,W          | ;Data Memory       |

|                      | MOVWF | EEADR                   | ;Address to write  |

|                      | MOVF  | DATA_EE_DATA,W          | ;Data Memory Value |

|                      | MOVWF | EEDATA                  | ;to write          |

|                      | BSF   | STATUS, RPO             | ;Bank 3            |

|                      | BCF   | EECON1, EEPGD           | ;Point to DATA     |

|                      |       |                         | ;memory            |

|                      | BSF   | EECON1,WREN             | ;Enable writes     |

|                      |       |                         |                    |

|                      | BCF   | INTCON,GIE              | ;Disable INTs.     |

|                      | MOVLW | 55h                     | ;                  |

| g g                  | MOVWF | EECON2<br>AAh<br>EECON2 | ;Write 55h         |

| Required<br>Sequence | MOVLW | AAh                     | ;                  |

| Seq                  | MOVWF | EECON2                  | ;Write AAh         |

| ш ()                 | BSF   | EECON1,WR               | ;Set WR bit to     |

|                      |       |                         | ;begin write       |

|                      | BSF   | INTCON, GIE             | ;Enable INTs.      |

|                      | BCF   | EECON1,WREN             | ;Disable writes    |

|                      |       |                         |                    |

# 6.7 Resetting of Timer1 Register Pair (TMR1H, TMR1L)

TMR1H and TMR1L registers are not reset to 00h on a POR, or any other Reset, except by the CCP1 and CCP2 special event triggers.

T1CON register is reset to 00h on a Power-on Reset, or a Brown-out Reset, which shuts off the timer and leaves a 1:1 prescale. In all other Resets, the register is unaffected.

# 6.8 Timer1 Prescaler

The prescaler counter is cleared on writes to the TMR1H or TMR1L registers.

# TABLE 6-2: REGISTERS ASSOCIATED WITH TIMER1 AS A TIMER/COUNTER

| Address                | Name   | Bit 7                | Bit 6                                                                      | Bit 5       | Bit 4        | Bit 3         | Bit 2        | Bit 1      | Bit 0  | Value on:<br>POR, BOR | Value on<br>all other<br>Resets |

|------------------------|--------|----------------------|----------------------------------------------------------------------------|-------------|--------------|---------------|--------------|------------|--------|-----------------------|---------------------------------|

| 0Bh,8Bh,<br>10Bh, 18Bh | INTCON | GIE                  | PEIE                                                                       | TMR0IE      | INTE         | RBIE          | TMR0IF       | INTF       | RBIF   | 0000 000x             | 0000 000u                       |

| 0Ch                    | PIR1   | PSPIF <sup>(1)</sup> | ADIF                                                                       | RCIF        | TXIF         | SSPIF         | CCP1IF       | TMR2IF     | TMR1IF | 0000 0000             | 0000 0000                       |

| 8Ch                    | PIE1   | PSPIE <sup>(1)</sup> | ADIE                                                                       | RCIE        | TXIE         | SSPIE         | CCP1IE       | TMR2IE     | TMR1IE | 0000 0000             | 0000 0000                       |

| 0Eh                    | TMR1L  | Holding R            | Register f                                                                 | or the Leas | t Significan | t Byte of the | e 16-bit TMI | R1 Registe | r      | xxxx xxxx             | uuuu uuuu                       |

| 0Fh                    | TMR1H  | Holding R            | lolding Register for the Most Significant Byte of the 16-bit TMR1 Register |             |              |               |              |            |        |                       | uuuu uuuu                       |

| 10h                    | T1CON  | _                    | _                                                                          | T1CKPS1     | T1CKPS0      | T1OSCEN       | T1SYNC       | TMR1CS     | TMR10N | 00 0000               | uu uuuu                         |

**Legend:** x = unknown, u = unchanged, - = unimplemented, read as '0'. Shaded cells are not used by the Timer1 module.

Note 1: Bits PSPIE and PSPIF are reserved on the 28-pin devices; always maintain these bits clear.

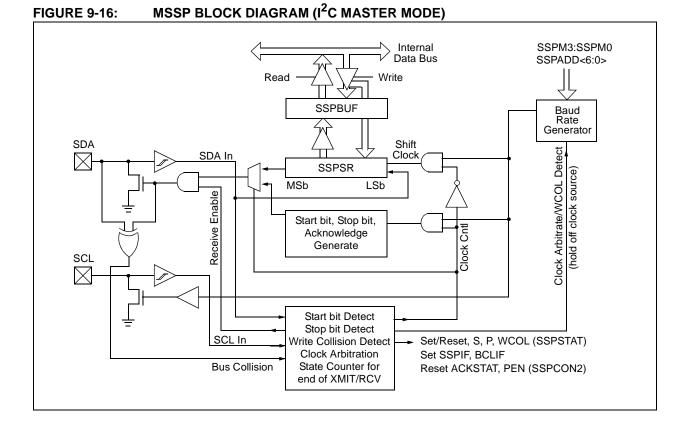

# 9.0 MASTER SYNCHRONOUS SERIAL PORT (MSSP) MODULE

# 9.1 Master SSP (MSSP) Module Overview

The Master Synchronous Serial Port (MSSP) module is a serial interface, useful for communicating with other peripheral or microcontroller devices. These peripheral devices may be serial EEPROMs, shift registers, display drivers, A/D converters, etc. The MSSP module can operate in one of two modes:

- Serial Peripheral Interface (SPI)

- Inter-Integrated Circuit (I<sup>2</sup>C)

- Full Master mode

- Slave mode (with general address call)

The I<sup>2</sup>C interface supports the following modes in hardware:

- Master mode

- Multi-Master mode

- Slave mode

# 9.2 Control Registers

The MSSP module has three associated registers. These include a status register (SSPSTAT) and two control registers (SSPCON and SSPCON2). The use of these registers and their individual configuration bits differ significantly, depending on whether the MSSP module is operated in SPI or  $I^2C$  mode.

Additional details are provided under the individual sections.

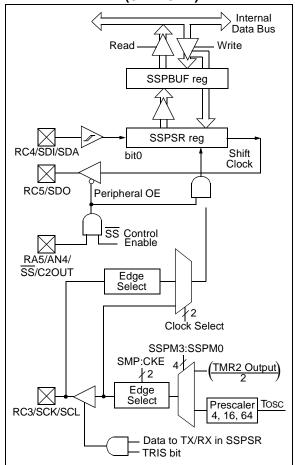

# 9.3 SPI Mode

The SPI mode allows 8 bits of data to be synchronously transmitted and received simultaneously. All four modes of SPI are supported. To accomplish communication, typically three pins are used:

- Serial Data Out (SDO) RC5/SDO

- Serial Data In (SDI) RC4/SDI/SDA

- Serial Clock (SCK) RC3/SCK/SCL

Additionally, a fourth pin may be used when in a Slave mode of operation:

Slave Select (SS) – RA5/AN4/SS/C2OUT

Figure 9-1 shows the block diagram of the MSSP module when operating in SPI mode.

#### FIGURE 9-1:

#### MSSP BLOCK DIAGRAM (SPI MODE)

| Note: | When the SPI is in Slave mode with $\overline{SS}$ pin<br>control enabled (SSPCON<3:0> = 0100),<br>the state of the SS pin can affect the state<br>read back from the TRISC<5> bit. The<br>Peripheral OE signal from the SSP mod-<br>ule in PORTC controls the state that is<br>read back from the TRISC<5> bit (see<br>Section 4.3 "PORTC and the TRISC<br>Register" for information on PORTC). If<br>Read-Modify-Write instructions, such as<br>BSF, are performed on the TRISC register<br>while the SS pin is high, this will cause the<br>TRISC of the table part thus displayed by |

|-------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|       | while the SS pin is high, this will cause the TRISC<5> bit to be set, thus disabling the SDO output.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

# 9.4.2 OPERATION

The MSSP module functions are enabled by setting MSSP Enable bit, SSPEN (SSPCON<5>).

The SSPCON register allows control of the I $^2$ C operation. Four mode selection bits (SSPCON<3:0>) allow one of the following I $^2$ C modes to be selected:

- I<sup>2</sup>C Master mode, clock = OSC/4 (SSPADD + 1)

- I<sup>2</sup>C Slave mode (7-bit address)

- I<sup>2</sup>C Slave mode (10-bit address)

- I<sup>2</sup>C Slave mode (7-bit address) with Start and Stop bit interrupts enabled

- I<sup>2</sup>C Slave mode (10-bit address) with Start and Stop bit interrupts enabled

- I<sup>2</sup>C Firmware Controlled Master mode, slave is Idle

Selection of any I<sup>2</sup>C mode, with the SSPEN bit set, forces the SCL and SDA pins to be open-drain, provided these pins are programmed to inputs by setting the appropriate TRISC bits. To ensure proper operation of the module, pull-up resistors must be provided externally to the SCL and SDA pins.

#### 9.4.3 SLAVE MODE

In Slave mode, the SCL and SDA pins must be configured as inputs (TRISC<4:3> set). The MSSP module will override the input state with the output data when required (slave-transmitter).

The I<sup>2</sup>C Slave mode hardware will always generate an interrupt on an address match. Through the mode select bits, the user can also choose to interrupt on Start and Stop bits

When an address is matched, or the data transfer after an address match is received, the hardware automatically will generate the Acknowledge ( $\overline{ACK}$ ) pulse and load the SSPBUF register with the received value currently in the SSPSR register.

Any combination of the following conditions will cause the MSSP module not to give this ACK pulse:

- The buffer full bit, BF (SSPSTAT<0>), was set before the transfer was received.

- The overflow bit, SSPOV (SSPCON<6>), was set before the transfer was received.

In this case, the SSPSR register value is not loaded into the SSPBUF, but bit SSPIF (PIR1<3>) is set. The BF bit is cleared by reading the SSPBUF register, while bit SSPOV is cleared through software.

The SCL clock input must have a minimum high and low for proper operation. The high and low times of the  $I^2C$  specification, as well as the requirement of the MSSP module, are shown in timing parameter #100 and parameter #101.

### 9.4.3.1 Addressing

Once the MSSP module has been enabled, it waits for a Start condition to occur. Following the Start condition, the 8 bits are shifted into the SSPSR register. All incoming bits are sampled with the rising edge of the clock (SCL) line. The value of register SSPSR<7:1> is compared to the value of the SSPADD register. The address is compared on the falling edge of the eighth clock (SCL) pulse. If the addresses match, and the BF and SSPOV bits are clear, the following events occur:

- 1. The SSPSR register value is loaded into the SSPBUF register.

- 2. The Buffer Full bit, BF, is set.

- 3. An ACK pulse is generated.

- 4. MSSP Interrupt Flag bit, SSPIF (PIR1<3>), is set (interrupt is generated if enabled) on the falling edge of the ninth SCL pulse.

In 10-bit Address mode, two address bytes need to be received by the slave. The five Most Significant bits (MSbs) of the first address byte specify if this is a 10-bit address. Bit R/W (SSPSTAT<2>) must specify a write so the slave device will receive the second address byte. For a 10-bit address, the first byte would equal '11110 A9 A8 0', where 'A9' and 'A8' are the two MSbs of the address. The sequence of events for 10-bit address is as follows, with steps 7 through 9 for the slave-transmitter:

- 1. Receive first (high) byte of address (bits SSPIF, BF and bit UA (SSPSTAT<1>) are set).

- Update the SSPADD register with second (low) byte of address (clears bit UA and releases the SCL line).

- 3. Read the SSPBUF register (clears bit BF) and clear flag bit SSPIF.

- 4. Receive second (low) byte of address (bits SSPIF, BF and UA are set).

- 5. Update the SSPADD register with the first (high) byte of address. If match releases SCL line, this will clear bit UA.

- 6. Read the SSPBUF register (clears bit BF) and clear flag bit SSPIF.

- 7. Receive Repeated Start condition.

- 8. Receive first (high) byte of address (bits SSPIF and BF are set).

- 9. Read the SSPBUF register (clears bit BF) and clear flag bit SSPIF.

### 9.4.6 MASTER MODE

Master mode is enabled by setting and clearing the appropriate SSPM bits in SSPCON and by setting the SSPEN bit. In Master mode, the SCL and SDA lines are manipulated by the MSSP hardware.

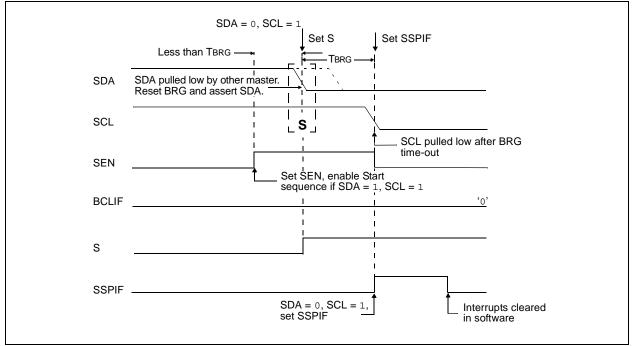

Master mode of operation is supported by interrupt generation on the detection of the Start and Stop conditions. The Stop (P) and Start (S) bits are cleared from a Reset or when the MSSP module is disabled. Control of the  $I^2C$  bus may be taken when the P bit is set or the bus is Idle, with both the S and P bits clear.

In Firmware Controlled Master mode, user code conducts all  $I^2C$  bus operations based on Start and Stop bit conditions.

Once Master mode is enabled, the user has six options.

- 1. Assert a Start condition on SDA and SCL.

- 2. Assert a Repeated Start condition on SDA and SCL.

- 3. Write to the SSPBUF register, initiating transmission of data/address.

- 4. Configure the I<sup>2</sup>C port to receive data.

- 5. Generate an Acknowledge condition at the end of a received byte of data.

- 6. Generate a Stop condition on SDA and SCL.

**Note:** The MSSP module, when configured in I<sup>2</sup>C Master mode, does not allow queueing of events. For instance, the user is not allowed to initiate a Start condition and immediately write the SSPBUF register to initiate transmission before the Start condition is complete. In this case, the SSPBUF will not be written to and the WCOL bit will be set, indicating that a write to the SSPBUF did not occur.

The following events will cause SSP Interrupt Flag bit, SSPIF, to be set (SSP interrupt if enabled):

- · Start condition

- Stop condition

- Data transfer byte transmitted/received

- Acknowledge transmit

- Repeated Start

© 2001-2013 Microchip Technology Inc.

NOTES:

# 11.5 A/D Operation During Sleep

The A/D module can operate during Sleep mode. This requires that the A/D clock source be set to RC (ADCS1:ADCS0 = 11). When the RC clock source is selected, the A/D module waits one instruction cycle before starting the conversion. This allows the SLEEP instruction to be executed which eliminates all digital switching noise from the conversion. When the conversion is completed, the GO/DONE bit will be cleared and the result loaded into the ADRES register. If the A/D interrupt is enabled, the device will wake-up from Sleep. If the A/D interrupt is not enabled, the ADON bit will remain set.

When the A/D clock source is another clock option (not RC), a SLEEP instruction will cause the present conversion to be aborted and the A/D module to be turned off, though the ADON bit will remain set.

Turning off the A/D places the A/D module in its lowest current consumption state.

| Note: | For the A/D module to operate in Sleep,   |

|-------|-------------------------------------------|

|       | the A/D clock source must be set to RC    |

|       | (ADCS1:ADCS0 = 11). To allow the con-     |

|       | version to occur during Sleep, ensure the |

|       | SLEEP instruction immediately follows the |

|       | instruction that sets the GO/DONE bit.    |

# 11.6 Effects of a Reset

A device Reset forces all registers to their Reset state. This forces the A/D module to be turned off and any conversion is aborted. All A/D input pins are configured as analog inputs.

The value that is in the ADRESH:ADRESL registers is not modified for a Power-on Reset. The ADRESH:ADRESL registers will contain unknown data after a Power-on Reset.

| Address               | Name   | Bit 7                | Bit 6                         | Bit 5                                               | Bit 4                         | Bit 3 | Bit 2   | Bit 1  | Bit 0  | Value<br>POR, |      | -    | e on<br>, WDT |

|-----------------------|--------|----------------------|-------------------------------|-----------------------------------------------------|-------------------------------|-------|---------|--------|--------|---------------|------|------|---------------|

| 0Bh,8Bh,<br>10Bh,18Bh | INTCON | GIE                  | PEIE                          | TMR0IE                                              | INTE                          | RBIE  | TMR0IF  | INTF   | RBIF   | 0000          | 000x | 0000 | 000u          |

| 0Ch                   | PIR1   | PSPIF <sup>(1)</sup> | ADIF                          | RCIF                                                | TXIF                          | SSPIF | CCP1IF  | TMR2IF | TMR1IF | 0000          | 0000 | 0000 | 0000          |

| 8Ch                   | PIE1   | PSPIE <sup>(1)</sup> | ADIE                          | RCIE                                                | TXIE                          | SSPIE | CCP1IE  | TMR2IE | TMR1IE | 0000          | 0000 | 0000 | 0000          |

| 1Eh                   | ADRESH | A/D Resu             | A/D Result Register High Byte |                                                     |                               |       |         |        |        |               |      | uuuu | uuuu          |

| 9Eh                   | ADRESL | A/D Resu             | lt Registe                    | r Low Byte                                          | ;                             |       |         |        |        | xxxx          | xxxx | uuuu | uuuu          |

| 1Fh                   | ADCON0 | ADCS1                | ADCS0                         | CHS2                                                | CHS1                          | CHS0  | GO/DONE | _      | ADON   | 0000          | 00-0 | 0000 | 00-0          |

| 9Fh                   | ADCON1 | ADFM                 | ADCS2                         | —                                                   | _                             | PCFG3 | PCFG2   | PCFG1  | PCFG0  | 00            | 0000 | 00   | 0000          |

| 85h                   | TRISA  | _                    | _                             | PORTA D                                             | PORTA Data Direction Register |       |         |        |        |               | 1111 | 11   | 1111          |

| 05h                   | PORTA  | —                    | _                             | PORTA Data Latch when written: PORTA pins when read |                               |       |         |        |        | 0x            | 0000 | 0u   | 0000          |

| 89h <sup>(1)</sup>    | TRISE  | IBF                  | OBF                           | IBOV PSPMODE — PORTE Data Direction bits            |                               |       |         |        |        | 0000          | -111 | 0000 | -111          |

| 09h <sup>(1)</sup>    | PORTE  |                      | _                             | _                                                   | _                             | _     | RE2     | RE1    | RE0    |               | -xxx |      | -uuu          |

TABLE 11-2: REGISTERS/BITS ASSOCIATED WITH A/D

Legend: x = unknown, u = unchanged, - = unimplemented, read as '0'. Shaded cells are not used for A/D conversion.

Note 1: These registers are not available on 28-pin devices.

| TABLE 14-6: INITIALIZATION CONDITIONS FOR ALL REGISTERS |     |     |      |     |                                    |                           |                                 |  |  |  |  |

|---------------------------------------------------------|-----|-----|------|-----|------------------------------------|---------------------------|---------------------------------|--|--|--|--|

| Register                                                |     | Dev | ices |     | Power-on Reset,<br>Brown-out Reset | MCLR Resets,<br>WDT Reset | Wake-up via WDT or<br>Interrupt |  |  |  |  |

| W                                                       | 73A | 74A | 76A  | 77A | XXXX XXXX                          | uuuu uuuu                 | uuuu uuuu                       |  |  |  |  |

| INDF                                                    | 73A | 74A | 76A  | 77A | N/A                                | N/A                       | N/A                             |  |  |  |  |

| TMR0                                                    | 73A | 74A | 76A  | 77A | XXXX XXXX                          | uuuu uuuu                 | uuuu uuuu                       |  |  |  |  |

| PCL                                                     | 73A | 74A | 76A  | 77A | 0000 0000                          | 0000 0000                 | PC + 1 <sup>(2)</sup>           |  |  |  |  |

| STATUS                                                  | 73A | 74A | 76A  | 77A | 0001 1xxx                          | 000q quuu <b>(3)</b>      | uuuq quuu <sup>(3)</sup>        |  |  |  |  |

| FSR                                                     | 73A | 74A | 76A  | 77A | XXXX XXXX                          | uuuu uuuu                 | uuuu uuuu                       |  |  |  |  |

| PORTA                                                   | 73A | 74A | 76A  | 77A | 0x 0000                            | 0u 0000                   | uu uuuu                         |  |  |  |  |

| PORTB                                                   | 73A | 74A | 76A  | 77A | XXXX XXXX                          | uuuu uuuu                 | uuuu uuuu                       |  |  |  |  |

| PORTC                                                   | 73A | 74A | 76A  | 77A | XXXX XXXX                          | uuuu uuuu                 | uuuu uuuu                       |  |  |  |  |

| PORTD                                                   | 73A | 74A | 76A  | 77A | XXXX XXXX                          | uuuu uuuu                 | uuuu uuuu                       |  |  |  |  |

| PORTE                                                   | 73A | 74A | 76A  | 77A | xxx                                | uuu                       | uuu                             |  |  |  |  |

| PCLATH                                                  | 73A | 74A | 76A  | 77A | 0 0000                             | 0 0000                    | u uuuu                          |  |  |  |  |

| INTCON                                                  | 73A | 74A | 76A  | 77A | 0000 000x                          | 0000 000u                 | uuuu uuuu <b>(1)</b>            |  |  |  |  |

|                                                         | 73A | 74A | 76A  | 77A | r000 0000                          | r000 0000                 | ruuu uuuu <b>(1)</b>            |  |  |  |  |

| PIR1                                                    | 73A | 74A | 76A  | 77A | 0000 0000                          | 0000 0000                 | uuuu uuuu <b>(1)</b>            |  |  |  |  |

| PIR2                                                    | 73A | 74A | 76A  | 77A | -0-0 00                            | -0-0 00                   | -u-u uu <b>(1)</b>              |  |  |  |  |

| TMR1L                                                   | 73A | 74A | 76A  | 77A | XXXX XXXX                          | uuuu uuuu                 | uuuu uuuu                       |  |  |  |  |

| TMR1H                                                   | 73A | 74A | 76A  | 77A | XXXX XXXX                          | uuuu uuuu                 | uuuu uuuu                       |  |  |  |  |

| T1CON                                                   | 73A | 74A | 76A  | 77A | 00 0000                            | uu uuuu                   | uu uuuu                         |  |  |  |  |

| TMR2                                                    | 73A | 74A | 76A  | 77A | 0000 0000                          | 0000 0000                 | uuuu uuuu                       |  |  |  |  |

| T2CON                                                   | 73A | 74A | 76A  | 77A | -000 0000                          | -000 0000                 | -uuu uuuu                       |  |  |  |  |

| SSPBUF                                                  | 73A | 74A | 76A  | 77A | XXXX XXXX                          | uuuu uuuu                 | uuuu uuuu                       |  |  |  |  |

| SSPCON                                                  | 73A | 74A | 76A  | 77A | 0000 0000                          | 0000 0000                 | uuuu uuuu                       |  |  |  |  |

| CCPR1L                                                  | 73A | 74A | 76A  | 77A | XXXX XXXX                          | uuuu uuuu                 | uuuu uuuu                       |  |  |  |  |

| CCPR1H                                                  | 73A | 74A | 76A  | 77A | XXXX XXXX                          | uuuu uuuu                 | uuuu uuuu                       |  |  |  |  |

| CCP1CON                                                 | 73A | 74A | 76A  | 77A | 00 0000                            | 00 0000                   | uu uuuu                         |  |  |  |  |

| RCSTA                                                   | 73A | 74A | 76A  | 77A | 0000 000x                          | 0000 000x                 | uuuu uuuu                       |  |  |  |  |

| TXREG                                                   | 73A | 74A | 76A  | 77A | 0000 0000                          | 0000 0000                 | uuuu uuuu                       |  |  |  |  |

| RCREG                                                   | 73A | 74A | 76A  | 77A | 0000 0000                          | 0000 0000                 | uuuu uuuu                       |  |  |  |  |

| CCPR2L                                                  | 73A | 74A | 76A  | 77A | XXXX XXXX                          | uuuu uuuu                 | uuuu uuuu                       |  |  |  |  |

| CCPR2H                                                  | 73A | 74A | 76A  | 77A | xxxx xxxx                          | uuuu uuuu                 | uuuu uuuu                       |  |  |  |  |

| CCP2CON                                                 | 73A | 74A | 76A  | 77A | 0000 0000                          | 0000 0000                 | uuuu uuuu                       |  |  |  |  |

| ADRESH                                                  | 73A | 74A | 76A  | 77A | xxxx xxxx                          | uuuu uuuu                 | uuuu uuuu                       |  |  |  |  |

| ADCON0                                                  | 73A | 74A | 76A  | 77A | 0000 00-0                          | 0000 00-0                 | uuuu uu-u                       |  |  |  |  |

| OPTION_REG                                              | 73A | 74A | 76A  | 77A | 1111 1111                          | 1111 1111                 | uuuu uuuu                       |  |  |  |  |

| TRISA                                                   | 73A | 74A | 76A  | 77A | 11 1111                            | 11 1111                   | uu uuuu                         |  |  |  |  |

| TRISB                                                   | 73A | 74A | 76A  | 77A | 1111 1111                          | 1111 1111                 | uuuu uuuu                       |  |  |  |  |

|                                                         |     |     |      |     |                                    |                           |                                 |  |  |  |  |

### TABLE 14-6: INITIALIZATION CONDITIONS FOR ALL REGISTERS

**Legend:** u = unchanged, x = unknown, - = unimplemented bit, read as '0', q = value depends on condition, r = reserved, maintain clear. Shaded cells indicate conditions do not apply for the designated device.

Note 1: One or more bits in INTCON, PIR1 and/or PIR2 will be affected (to cause wake-up).

- 2: When the wake-up is due to an interrupt and the GIE bit is set, the PC is loaded with the interrupt vector (0004h).

- 3: See Table 14-5 for Reset value for specific condition.

| TABLE 14-6: | INITIA | INITIALIZATION CONDITIONS FOR ALL REGISTERS (CONTINUED) |     |     |                                    |                           |                                 |  |  |  |  |

|-------------|--------|---------------------------------------------------------|-----|-----|------------------------------------|---------------------------|---------------------------------|--|--|--|--|

| Register    |        | Devices                                                 |     |     | Power-on Reset,<br>Brown-out Reset | MCLR Resets,<br>WDT Reset | Wake-up via WDT or<br>Interrupt |  |  |  |  |

| TRISD       | 73A    | 74A                                                     | 76A | 77A | 1111 1111                          | 1111 1111                 | uuuu uuuu                       |  |  |  |  |

| TRISE       | 73A    | 74A                                                     | 76A | 77A | 0000 -111                          | 0000 -111                 | uuuu -uuu                       |  |  |  |  |

| PIE1        | 73A    | 74A                                                     | 76A | 77A | r000 0000                          | r000 0000                 | ruuu uuuu                       |  |  |  |  |

| FICI        | 73A    | 74A                                                     | 76A | 77A | 0000 0000                          | 0000 0000                 | սսսս սսսս                       |  |  |  |  |

| PIE2        | 73A    | 74A                                                     | 76A | 77A | -0-0 00                            | -0-0 00                   | -u-u uu                         |  |  |  |  |

| PCON        | 73A    | 74A                                                     | 76A | 77A | dd                                 | uu                        | uu                              |  |  |  |  |

| SSPCON2     | 73A    | 74A                                                     | 76A | 77A | 0000 0000                          | 0000 0000                 | uuuu uuuu                       |  |  |  |  |

| PR2         | 73A    | 74A                                                     | 76A | 77A | 1111 1111                          | 1111 1111                 | 1111 1111                       |  |  |  |  |

| SSPADD      | 73A    | 74A                                                     | 76A | 77A | 0000 0000                          | 0000 0000                 | uuuu uuuu                       |  |  |  |  |

| SSPSTAT     | 73A    | 74A                                                     | 76A | 77A | 00 0000                            | 00 0000                   | uu uuuu                         |  |  |  |  |

| TXSTA       | 73A    | 74A                                                     | 76A | 77A | 0000 -010                          | 0000 -010                 | uuuu -uuu                       |  |  |  |  |

| SPBRG       | 73A    | 74A                                                     | 76A | 77A | 0000 0000                          | 0000 0000                 | uuuu uuuu                       |  |  |  |  |

| CMCON       | 73A    | 974                                                     | 76A | 77A | 0000 0111                          | 0000 0111                 | uuuu uuuu                       |  |  |  |  |

| CVRCON      | 73A    | 74A                                                     | 76A | 77A | 000- 0000                          | 000- 0000                 | uuu- uuuu                       |  |  |  |  |

| ADRESL      | 73A    | 74A                                                     | 76A | 77A | XXXX XXXX                          | սսսս սսսս                 | uuuu uuuu                       |  |  |  |  |

| ADCON1      | 73A    | 74A                                                     | 76A | 77A | 00 0000                            | 00 0000                   | uu uuuu                         |  |  |  |  |

| EEDATA      | 73A    | 74A                                                     | 76A | 77A | XXXX XXXX                          | uuuu uuuu                 | uuuu uuuu                       |  |  |  |  |

| EEADR       | 73A    | 74A                                                     | 76A | 77A | XXXX XXXX                          | uuuu uuuu                 | uuuu uuuu                       |  |  |  |  |

| EEDATH      | 73A    | 74A                                                     | 76A | 77A | XXXX XXXX                          | սսսս սսսս                 | uuuu uuuu                       |  |  |  |  |

| EEADRH      | 73A    | 74A                                                     | 76A | 77A | xxxx xxxx                          | սսսս սսսս                 | uuuu uuuu                       |  |  |  |  |

| EECON1      | 73A    | 74A                                                     | 76A | 77A | x x000                             | u u000                    | u uuuu                          |  |  |  |  |

| EECON2      | 73A    | 74A                                                     | 76A | 77A |                                    |                           |                                 |  |  |  |  |

**Legend:** u = unchanged, x = unknown, - = unimplemented bit, read as '0', q = value depends on condition, r = reserved, maintain clear. Shaded cells indicate conditions do not apply for the designated device.

Note 1: One or more bits in INTCON, PIR1 and/or PIR2 will be affected (to cause wake-up).

**2:** When the wake-up is due to an interrupt and the GIE bit is set, the PC is loaded with the interrupt vector (0004h).

3: See Table 14-5 for Reset value for specific condition.

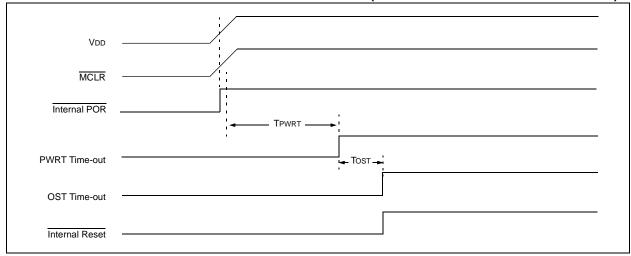

### FIGURE 14-6: TIME-OUT SEQUENCE ON POWER-UP (MCLR TIED TO VDD VIA RC NETWORK)

© 2001-2013 Microchip Technology Inc.

# 16.3 MPLAB C17 and MPLAB C18 C Compilers

The MPLAB C17 and MPLAB C18 Code Development Systems are complete ANSI C compilers for Microchip's PIC17CXXX and PIC18CXXX family of microcontrollers. These compilers provide powerful integration capabilities, superior code optimization and ease of use not found with other compilers.

For easy source level debugging, the compilers provide symbol information that is optimized to the MPLAB IDE debugger.

# 16.4 MPLINK Object Linker/ MPLIB Object Librarian

The MPLINK object linker combines relocatable objects created by the MPASM assembler and the MPLAB C17 and MPLAB C18 C compilers. It can link relocatable objects from precompiled libraries, using directives from a linker script.

The MPLIB object librarian manages the creation and modification of library files of pre-compiled code. When a routine from a library is called from a source file, only the modules that contain that routine will be linked in with the application. This allows large libraries to be used efficiently in many different applications.

The object linker/library features include:

- Efficient linking of single libraries instead of many smaller files

- Enhanced code maintainability by grouping related modules together

- Flexible creation of libraries with easy module listing, replacement, deletion and extraction

# 16.5 MPLAB C30 C Compiler

The MPLAB C30 C compiler is a full-featured, ANSI compliant, optimizing compiler that translates standard ANSI C programs into dsPIC30F assembly language source. The compiler also supports many command-line options and language extensions to take full advantage of the dsPIC30F device hardware capabilities, and afford fine control of the compiler code generator.

MPLAB C30 is distributed with a complete ANSI C standard library. All library functions have been validated and conform to the ANSI C library standard. The library includes functions for string manipulation, dynamic memory allocation, data conversion, time-keeping, and math functions (trigonometric, exponential and hyperbolic). The compiler provides symbolic information for high level source debugging with the MPLAB IDE.

# 16.6 MPLAB ASM30 Assembler, Linker, and Librarian

MPLAB ASM30 assembler produces relocatable machine code from symbolic assembly language for dsPIC30F devices. MPLAB C30 compiler uses the assembler to produce it's object file. The assembler generates relocatable object files that can then be archived or linked with other relocatable object files and archives to create an executable file. Notable features of the assembler include:

- Support for the entire dsPIC30F instruction set

- · Support for fixed-point and floating-point data

- Command line interface

- Rich directive set

- Flexible macro language

- MPLAB IDE compatibility

# 16.7 MPLAB SIM Software Simulator

The MPLAB SIM software simulator allows code development in a PC hosted environment by simulating the PIC series microcontrollers on an instruction level. On any given instruction, the data areas can be examined or modified and stimuli can be applied from a file, or user defined key press, to any pin. The execution can be performed in Single-Step, Execute Until Break, or Trace mode.

The MPLAB SIM simulator fully supports symbolic debugging using the MPLAB C17 and MPLAB C18 C Compilers, as well as the MPASM assembler. The software simulator offers the flexibility to develop and debug code outside of the laboratory environment, making it an excellent, economical software development tool.

# 16.8 MPLAB SIM30 Software Simulator

The MPLAB SIM30 software simulator allows code development in a PC hosted environment by simulating the dsPIC30F series microcontrollers on an instruction level. On any given instruction, the data areas can be examined or modified and stimuli can be applied from a file, or user defined key press, to any of the pins.

The MPLAB SIM30 simulator fully supports symbolic debugging using the MPLAB C30 C Compiler and MPLAB ASM30 assembler. The simulator runs in either a Command Line mode for automated tasks, or from MPLAB IDE. This high speed simulator is designed to debug, analyze and optimize time intensive DSP routines.

# 17.3 Timing Parameter Symbology

The timing parameter symbols have been created following one of the following formats:

| 1. TppS2pp            | bS                                  | 3. Tcc:st | (I <sup>2</sup> C specifications only) |

|-----------------------|-------------------------------------|-----------|----------------------------------------|

| 2. TppS               |                                     | 4. Ts     | (I <sup>2</sup> C specifications only) |

| Т                     |                                     |           |                                        |

| F                     | Frequency                           | Т         | Time                                   |

| Lowerca               | se letters (pp) and their meanings: |           |                                        |