Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| 2 0 0 0 0 0                |                                                                            |

|----------------------------|----------------------------------------------------------------------------|

| Product Status             | Active                                                                     |

| Core Processor             | PIC                                                                        |

| Core Size                  | 8-Bit                                                                      |

| Speed                      | 20MHz                                                                      |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                          |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                      |

| Number of I/O              | 33                                                                         |

| Program Memory Size        | 14KB (8K x 14)                                                             |

| Program Memory Type        | FLASH                                                                      |

| EEPROM Size                | 256 x 8                                                                    |

| RAM Size                   | 368 x 8                                                                    |

| Voltage - Supply (Vcc/Vdd) | 4V ~ 5.5V                                                                  |

| Data Converters            | A/D 8x10b                                                                  |

| Oscillator Type            | External                                                                   |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                          |

| Mounting Type              | Surface Mount                                                              |

| Package / Case             | 44-VQFN Exposed Pad                                                        |

| Supplier Device Package    | 44-QFN (8x8)                                                               |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16f877at-i-ml |

|                            |                                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

|                                                     | PDIP | PLCC | TQFP | QFN  | I/O/P              | Buffer                 |                                                                                                                                                                     |

|-----------------------------------------------------|------|------|------|------|--------------------|------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Pin Name                                            | Pin# | Pin# | Pin# | Pin# | Туре               | Туре                   | Description                                                                                                                                                         |

| OSC1/CLKI<br>OSC1                                   | 13   | 14   | 30   | 32   | I                  | ST/CMOS <sup>(4)</sup> | Oscillator crystal or external clock input.<br>Oscillator crystal input or external clock source<br>input. ST buffer when configured in RC mode;<br>otherwise CMOS. |

| CLKI                                                |      |      |      |      | Ι                  |                        | External clock source input. Always associated<br>with pin function OSC1 (see OSC1/CLKI,<br>OSC2/CLKO pins).                                                        |

| OSC2/CLKO<br>OSC2                                   | 14   | 15   | 31   | 33   | 0                  | _                      | Oscillator crystal or clock output.<br>Oscillator crystal output.<br>Connects to crystal or resonator in Crystal<br>Oscillator mode.                                |

| CLKO                                                |      |      |      |      | 0                  |                        | In RC mode, OSC2 pin outputs CLKO, which<br>has 1/4 the frequency of OSC1 and denotes the<br>instruction cycle rate.                                                |

| MCLR/VPP<br>MCLR                                    | 1    | 2    | 18   | 18   | I                  | ST                     | Master Clear (input) or programming voltage (output)<br>Master Clear (Reset) input. This pin is an active<br>low Reset to the device.                               |

| Vpp                                                 |      |      |      |      | Р                  |                        | Programming voltage input.                                                                                                                                          |

|                                                     |      |      | 10   | 10   |                    |                        | PORTA is a bidirectional I/O port.                                                                                                                                  |

| RA0/AN0<br>RA0<br>AN0                               | 2    | 3    | 19   | 19   | I/O<br>I           | TTL                    | Digital I/O.<br>Analog input 0.                                                                                                                                     |

| RA1/AN1<br>RA1<br>AN1                               | 3    | 4    | 20   | 20   | I/O<br>I           | TTL                    | Digital I/O.<br>Analog input 1.                                                                                                                                     |

| RA2/AN2/VREF-/CVREF<br>RA2<br>AN2<br>VREF-<br>CVREF | 4    | 5    | 21   | 21   | I/O<br>I<br>I<br>O | TTL                    | Digital I/O.<br>Analog input 2.<br>A/D reference voltage (Low) input.<br>Comparator VREF output.                                                                    |

| RA3/AN3/Vref+<br>RA3<br>AN3<br>Vref+                | 5    | 6    | 22   | 22   | I/O<br>I<br>I      | TTL                    | Digital I/O.<br>Analog input 3.<br>A/D reference voltage (High) input.                                                                                              |

| RA4/T0CKI/C1OUT<br>RA4                              | 6    | 7    | 23   | 23   | I/O                | ST                     | Digital I/O – Open-drain when configured as output.                                                                                                                 |

| T0CKI<br>C1OUT                                      |      |      |      |      | I<br>O             |                        | Timer0 external clock input.<br>Comparator 1 output.                                                                                                                |

| RA5/AN4/SS/C2OUT<br>RA5<br>AN4<br>SS<br>C2OUT       | 7    | 8    | 24   | 24   | I/O<br>I<br>0      | TTL                    | Digital I/O.<br>Analog input 4.<br>SPI slave select input.<br>Comparator 2 output.                                                                                  |

#### TABLE 1-3: PIC16F874A/877A PINOUT DESCRIPTION

— = Not used TTL = TTL input ST = Schmitt Trigger input

Note 1: This buffer is a Schmitt Trigger input when configured as the external interrupt.

This buffer is a Schmitt Trigger input when used in Serial Programming mode.

3: This buffer is a Schmitt Trigger input when configured in RC Oscillator mode and a CMOS input otherwise.

## 4.0 I/O PORTS

Some pins for these I/O ports are multiplexed with an alternate function for the peripheral features on the device. In general, when a peripheral is enabled, that pin may not be used as a general purpose I/O pin.

Additional information on I/O ports may be found in the PIC<sup>®</sup> Mid-Range Reference Manual (DS33023).

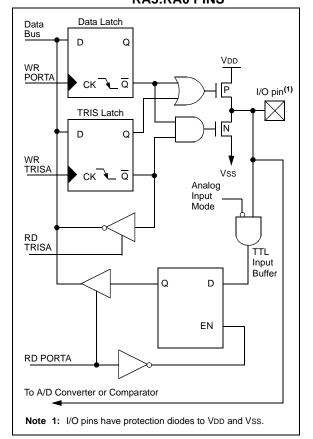

### 4.1 PORTA and the TRISA Register

PORTA is a 6-bit wide, bidirectional port. The corresponding data direction register is TRISA. Setting a TRISA bit (= 1) will make the corresponding PORTA pin an input (i.e., put the corresponding output driver in a High-Impedance mode). Clearing a TRISA bit (= 0) will make the corresponding PORTA pin an output (i.e., put the contents of the output latch on the selected pin).

Reading the PORTA register reads the status of the pins, whereas writing to it will write to the port latch. All write operations are read-modify-write operations. Therefore, a write to a port implies that the port pins are read, the value is modified and then written to the port data latch.

Pin RA4 is multiplexed with the Timer0 module clock input to become the RA4/T0CKI pin. The RA4/T0CKI pin is a Schmitt Trigger input and an open-drain output. All other PORTA pins have TTL input levels and full CMOS output drivers.

Other PORTA pins are multiplexed with analog inputs and the analog VREF input for both the A/D converters and the comparators. The operation of each pin is selected by clearing/setting the appropriate control bits in the ADCON1 and/or CMCON registers.

| Note: | On a Power-on Reset, these pins are con-  |  |  |  |  |  |  |  |  |  |  |  |

|-------|-------------------------------------------|--|--|--|--|--|--|--|--|--|--|--|

|       | figured as analog inputs and read as '0'. |  |  |  |  |  |  |  |  |  |  |  |

|       | The comparators are in the off (digital)  |  |  |  |  |  |  |  |  |  |  |  |

|       | state.                                    |  |  |  |  |  |  |  |  |  |  |  |

The TRISA register controls the direction of the port pins even when they are being used as analog inputs. The user must ensure the bits in the TRISA register are maintained set when using them as analog inputs.

#### EXAMPLE 4-1: INITIALIZING PORTA

| BCF   | STATUS, |     | ;                       |

|-------|---------|-----|-------------------------|

| BCF   | STATUS, | RP1 | ; Bank0                 |

| CLRF  | PORTA   |     | ; Initialize PORTA by   |

|       |         |     | ; clearing output       |

|       |         |     | ; data latches          |

| BSF   | STATUS, | RP0 | ; Select Bank 1         |

| MOVLW | 0x06    |     | ; Configure all pins    |

| MOVWF | ADCON1  |     | ; as digital inputs     |

| MOVLW | 0xCF    |     | ; Value used to         |

|       |         |     | ; initialize data       |

|       |         |     | ; direction             |

| MOVWF | TRISA   |     | ; Set RA<3:0> as inputs |

|       |         |     | ; RA<5:4> as outputs    |

|       |         |     | ; TRISA<7:6>are always  |

|       |         |     | ; read as '0'.          |

|       |         |     |                         |

BLOCK DIAGRAM OF RA3:RA0 PINS

| Name                   | Bit#  | Buffer                | Function                                                                                                                                          |

|------------------------|-------|-----------------------|---------------------------------------------------------------------------------------------------------------------------------------------------|

| RB0/INT                | bit 0 | TTL/ST <sup>(1)</sup> | Input/output pin or external interrupt input. Internal software programmable weak pull-up.                                                        |

| RB1                    | bit 1 | TTL                   | Input/output pin. Internal software programmable weak pull-up.                                                                                    |

| RB2                    | bit 2 | TTL                   | Input/output pin. Internal software programmable weak pull-up.                                                                                    |

| RB3/PGM <sup>(3)</sup> | bit 3 | TTL                   | Input/output pin or programming pin in LVP mode. Internal software programmable weak pull-up.                                                     |

| RB4                    | bit 4 | TTL                   | Input/output pin (with interrupt-on-change). Internal software programmable weak pull-up.                                                         |

| RB5                    | bit 5 | TTL                   | Input/output pin (with interrupt-on-change). Internal software programmable weak pull-up.                                                         |

| RB6/PGC                | bit 6 | TTL/ST <sup>(2)</sup> | Input/output pin (with interrupt-on-change) or in-circuit debugger pin.<br>Internal software programmable weak pull-up. Serial programming clock. |

| RB7/PGD                | bit 7 | TTL/ST <sup>(2)</sup> | Input/output pin (with interrupt-on-change) or in-circuit debugger pin.<br>Internal software programmable weak pull-up. Serial programming data.  |

#### TABLE 4-3:PORTB FUNCTIONS

**Legend:** TTL = TTL input, ST = Schmitt Trigger input

**Note 1:** This buffer is a Schmitt Trigger input when configured as the external interrupt.

2: This buffer is a Schmitt Trigger input when used in Serial Programming mode or in-circuit debugger.

**3:** Low-Voltage ICSP Programming (LVP) is enabled by default which disables the RB3 I/O function. LVP must be disabled to enable RB3 as an I/O pin and allow maximum compatibility to the other 28-pin and 40-pin mid-range devices.

| TABLE 4-4: S | SUMMARY OF REGISTERS ASSOCIATED WITH PORTB |

|--------------|--------------------------------------------|

|--------------|--------------------------------------------|

| Address   | Name       | Bit 7 | Bit 6                         | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0  | Value<br>POR, I |      | Valu<br>all o<br>Res | ther |

|-----------|------------|-------|-------------------------------|-------|-------|-------|-------|-------|--------|-----------------|------|----------------------|------|

| 06h, 106h | PORTB      | RB7   | RB6                           | RB5   | RB4   | RB3   | RB2   | RB1   | RB0    | XXXX :          | xxxx | uuuu                 | uuuu |

| 86h, 186h | TRISB      | PORTB | PORTB Data Direction Register |       |       |       |       |       | 1111 1 | 1111            | 1111 | 1111                 |      |

| 81h, 181h | OPTION_REG | RBPU  | INTEDG                        | TOCS  | T0SE  | PSA   | PS2   | PS1   | PS0    | 1111 1          | 1111 | 1111                 | 1111 |

|           |            |       |                               |       |       |       |       |       |        |                 |      |                      |      |

**Legend:** x = unknown, u = unchanged. Shaded cells are not used by PORTB.

#### 8.3.3 SETUP FOR PWM OPERATION

The following steps should be taken when configuring the CCP module for PWM operation:

- 1. Set the PWM period by writing to the PR2 register.

- 2. Set the PWM duty cycle by writing to the CCPR1L register and CCP1CON<5:4> bits.

- 3. Make the CCP1 pin an output by clearing the TRISC<2> bit.

- 4. Set the TMR2 prescale value and enable Timer2 by writing to T2CON.

- 5. Configure the CCP1 module for PWM operation.

| PWM Frequency              | 1.22 kHz | 4.88 kHz | 19.53 kHz | 78.12kHz | 156.3 kHz | 208.3 kHz |

|----------------------------|----------|----------|-----------|----------|-----------|-----------|

| Timer Prescaler (1, 4, 16) | 16       | 4        | 1         | 1        | 1         | 1         |

| PR2 Value                  | 0xFFh    | 0xFFh    | 0xFFh     | 0x3Fh    | 0x1Fh     | 0x17h     |

| Maximum Resolution (bits)  | 10       | 10       | 10        | 8        | 7         | 5.5       |

| TABLE 8-4: | <b>REGISTERS ASSOCIATED WITH CAPTURE, COMPARE AND TIMER1</b> |

|------------|--------------------------------------------------------------|

|------------|--------------------------------------------------------------|

| Address                | Name    | Bit 7                | Bit 6                                | Bit 5        | Bit 4         | Bit 3          | Bit 2      | Bit 1      | Bit 0  | Value on:<br>POR, BOR | Value on<br>all other<br>Resets |

|------------------------|---------|----------------------|--------------------------------------|--------------|---------------|----------------|------------|------------|--------|-----------------------|---------------------------------|

| 0Bh,8Bh,<br>10Bh, 18Bh | INTCON  | GIE                  | PEIE                                 | TMR0IE       | INTE          | RBIE           | TMR0IF     | INTF       | RBIF   | 0000 000x             | 0000 000u                       |

| 0Ch                    | PIR1    | PSPIF <sup>(1)</sup> | ADIF                                 | RCIF         | TXIF          | SSPIF          | CCP1IF     | TMR2IF     | TMR1IF | 0000 0000             | 0000 0000                       |

| 0Dh                    | PIR2    | —                    | —                                    | _            | _             | —              | —          | _          | CCP2IF | 0                     | 0                               |

| 8Ch                    | PIE1    | PSPIE <sup>(1)</sup> | ADIE                                 | RCIE         | TXIE          | SSPIE          | CCP1IE     | TMR2IE     | TMR1IE | 0000 0000             | 0000 0000                       |

| 8Dh                    | PIE2    | —                    | —                                    | _            | _             | —              | —          | _          | CCP2IE | 0                     | 0                               |

| 87h                    | TRISC   | PORTC D              | ata Direc                            | tion Registe | er            |                |            |            |        | 1111 1111             | 1111 1111                       |

| 0Eh                    | TMR1L   | Holding R            | egister fo                           | r the Least  | Significant I | Byte of the 1  | 6-bit TMR' | 1 Register |        | xxxx xxxx             | uuuu uuuu                       |

| 0Fh                    | TMR1H   | Holding R            | egister fo                           | r the Most S | Significant E | Byte of the 10 | 6-bit TMR1 | Register   |        | xxxx xxxx             | uuuu uuuu                       |

| 10h                    | T1CON   | —                    | —                                    | T1CKPS1      | T1CKPS0       | T1OSCEN        | T1SYNC     | TMR1CS     | TMR10N | 00 0000               | uu uuuu                         |

| 15h                    | CCPR1L  | Capture/C            | Compare/F                            | PWM Regis    | ter 1 (LSB)   |                |            |            |        | xxxx xxxx             | uuuu uuuu                       |

| 16h                    | CCPR1H  | Capture/C            | Capture/Compare/PWM Register 1 (MSB) |              |               |                |            |            |        |                       | uuuu uuuu                       |

| 17h                    | CCP1CON | _                    | _                                    | CCP1X        | CCP1Y         | CCP1M3         | CCP1M2     | CCP1M1     | CCP1M0 | 00 0000               | 00 0000                         |

| 1Bh                    | CCPR2L  | Capture/C            | Compare/F                            | xxxx xxxx    | uuuu uuuu     |                |            |            |        |                       |                                 |

| 1Ch                    | CCPR2H  | Capture/C            | Compare/F                            | PWM Regis    | ter 2 (MSB)   | )              |            |            |        | xxxx xxxx             | uuuu uuuu                       |

| 1Dh                    | CCP2CON | _                    |                                      | CCP2X        | CCP2Y         | CCP2M3         | CCP2M2     | CCP2M1     | CCP2M0 | 00 0000               | 00 0000                         |

Legend: x = unknown, u = unchanged, - = unimplemented, read as '0'. Shaded cells are not used by Capture and Timer1.

Note 1: The PSP is not implemented on 28-pin devices; always maintain these bits clear.

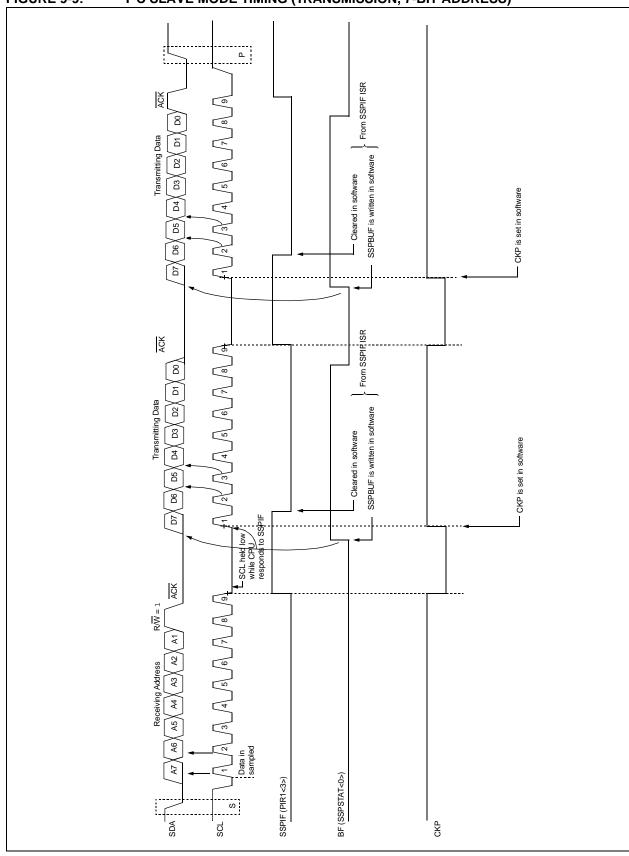

#### 9.4.3.2 Reception

When the  $R/\overline{W}$  bit of the address byte is clear and an address match occurs, the  $R/\overline{W}$  bit of the SSPSTAT register is cleared. The received address is loaded into the SSPBUF register and the SDA line is held low (ACK).

When the address byte overflow condition exists, then the No Acknowledge (ACK) pulse is given. An overflow condition is defined as either bit BF (SSPSTAT<0>) is set or bit SSPOV (SSPCON<6>) is set.

An MSSP interrupt is generated for each data transfer byte. Flag bit SSPIF (PIR1<3>) must be cleared in software. The SSPSTAT register is used to determine the status of the byte.

If SEN is enabled (SSPCON<0> = 1), RC3/SCK/SCL will be held low (clock stretch) following each data transfer. The clock must be released by setting bit CKP (SSPCON<4>). See **Section 9.4.4** "**Clock Stretching**" for more detail.

#### 9.4.3.3 Transmission

When the R/W bit of the incoming address byte is set and an address match occurs, the R/W bit of the SSPSTAT register is set. The received address is loaded into the SSPBUF register. The ACK pulse will be sent on the ninth bit and pin RC3/SCK/SCL is held low regardless of SEN (see **Section 9.4.4 "Clock Stretching"** for more detail). By stretching the clock, the master will be unable to assert another clock pulse until the slave is done preparing the transmit data. The transmit data must be loaded into the SSPBUF register, which also loads the SSPSR register. Then pin RC3/SCK/SCL should be enabled by setting bit CKP (SSPCON<4>). The eight data bits are shifted out on the falling edge of the SCL input. This ensures that the SDA signal is valid during the SCL high time (Figure 9-9).

The ACK pulse from the master-receiver is latched on the rising edge of the ninth SCL input pulse. If the SDA line is high (not ACK), then the data transfer is complete. In this case, when the ACK is latched by the slave, the slave logic is reset (resets SSPSTAT register) and the slave monitors for another occurrence of the Start bit. If the SDA line was low (ACK), the next transmit data must be loaded into the SSPBUF register. Again, pin RC3/SCK/SCL must be enabled by setting bit CKP.

An MSSP interrupt is generated for each data transfer byte. The SSPIF bit must be cleared in software and the SSPSTAT register is used to determine the status of the byte. The SSPIF bit is set on the falling edge of the ninth clock pulse.

I<sup>2</sup>C SLAVE MODE TIMING (TRANSMISSION, 7-BIT ADDRESS)

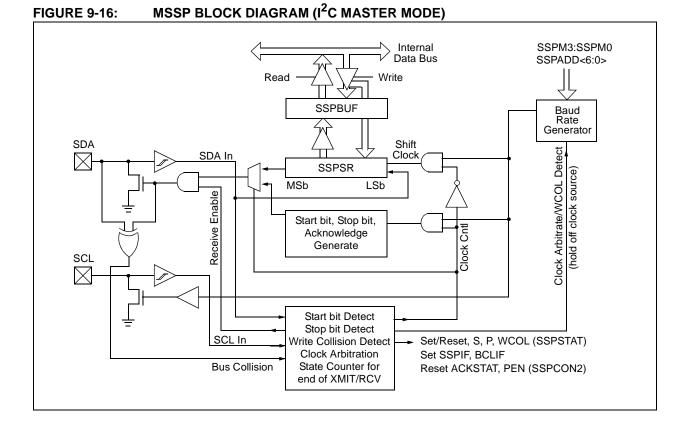

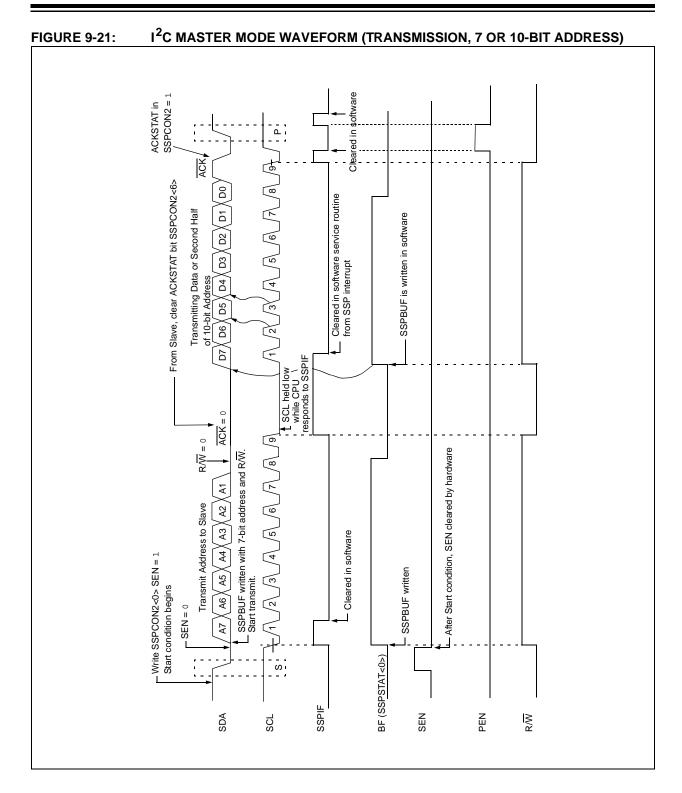

#### 9.4.6 MASTER MODE

Master mode is enabled by setting and clearing the appropriate SSPM bits in SSPCON and by setting the SSPEN bit. In Master mode, the SCL and SDA lines are manipulated by the MSSP hardware.

Master mode of operation is supported by interrupt generation on the detection of the Start and Stop conditions. The Stop (P) and Start (S) bits are cleared from a Reset or when the MSSP module is disabled. Control of the  $I^2C$  bus may be taken when the P bit is set or the bus is Idle, with both the S and P bits clear.

In Firmware Controlled Master mode, user code conducts all  $I^2C$  bus operations based on Start and Stop bit conditions.

Once Master mode is enabled, the user has six options.

- 1. Assert a Start condition on SDA and SCL.

- 2. Assert a Repeated Start condition on SDA and SCL.

- 3. Write to the SSPBUF register, initiating transmission of data/address.

- 4. Configure the I<sup>2</sup>C port to receive data.

- 5. Generate an Acknowledge condition at the end of a received byte of data.

- 6. Generate a Stop condition on SDA and SCL.

**Note:** The MSSP module, when configured in I<sup>2</sup>C Master mode, does not allow queueing of events. For instance, the user is not allowed to initiate a Start condition and immediately write the SSPBUF register to initiate transmission before the Start condition is complete. In this case, the SSPBUF will not be written to and the WCOL bit will be set, indicating that a write to the SSPBUF did not occur.

The following events will cause SSP Interrupt Flag bit, SSPIF, to be set (SSP interrupt if enabled):

- · Start condition

- Stop condition

- Data transfer byte transmitted/received

- Acknowledge transmit

- Repeated Start

© 2001-2013 Microchip Technology Inc.

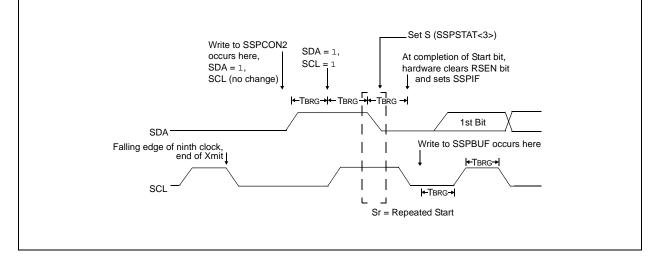

### 9.4.9 I<sup>2</sup>C MASTER MODE REPEATED START CONDITION TIMING

A Repeated Start condition occurs when the RSEN bit (SSPCON2<1>) is programmed high and the I<sup>2</sup>C logic module is in the Idle state. When the RSEN bit is set, the SCL pin is asserted low. When the SCL pin is sampled low, the Baud Rate Generator is loaded with the contents of SSPADD<5:0> and begins counting. The SDA pin is released (brought high) for one Baud Rate Generator count (TBRG). When the Baud Rate Generator times out, if SDA is sampled high, the SCL pin will be deasserted (brought high). When SCL is sampled high, the Baud Rate Generator is reloaded with the contents of SSPADD<6:0> and begins counting. SDA and SCL must be sampled high for one TBRG. This action is then followed by assertion of the SDA pin (SDA = 0) for one TBRG while SCL is high. Following this, the RSEN bit (SSPCON2<1>) will be automatically cleared and the Baud Rate Generator will not be reloaded, leaving the SDA pin held low. As soon as a Start condition is detected on the SDA and SCL pins, the S bit (SSPSTAT<3>) will be set. The SSPIF bit will not be set until the Baud Rate Generator has timed out.

- Note 1: If RSEN is programmed while any other event is in progress, it will not take effect.

- A bus collision during the Repeated Start condition occurs if:

- SDA is sampled low when SCL goes from low to high.

- SCL goes low before SDA is asserted low. This may indicate that another master is attempting to transmit a data '1'.

Immediately following the SSPIF bit getting set, the user may write the SSPBUF with the 7-bit address in 7-bit mode or the default first address in 10-bit mode. After the first eight bits are transmitted and an ACK is received, the user may then transmit an additional eight bits of address (10-bit mode) or eight bits of data (7-bit mode).

#### 9.4.9.1 WCOL Status Flag

If the user writes the SSPBUF when a Repeated Start sequence is in progress, the WCOL is set and the contents of the buffer are unchanged (the write doesn't occur).

**Note:** Because queueing of events is not allowed, writing of the lower 5 bits of SSPCON2 is disabled until the Repeated Start condition is complete.

## FIGURE 9-20: REPEAT START CONDITION WAVEFORM

| Address                                | Name   | Bit 7                | Bit 6                  | Bit 5  | Bit 4 | Bit 3 | Bit 2  | Bit 1     | Bit 0     | Value on:<br>POR, BOR | Value on<br>all other<br>Resets |

|----------------------------------------|--------|----------------------|------------------------|--------|-------|-------|--------|-----------|-----------|-----------------------|---------------------------------|

| 0Bh, 8Bh,<br>10Bh,18Bh                 | INTCON | GIE                  | PEIE                   | TMR0IE | INTE  | RBIE  | TMR0IF | INTF      | R0IF      | 0000 000x             | 0000 000u                       |

| 0Ch                                    | PIR1   | PSPIF <sup>(1)</sup> | ADIF                   | RCIF   | TXIF  | SSPIF | CCP1IF | TMR2IF    | TMR1IF    | 0000 0000             | 0000 0000                       |

| 18h                                    | RCSTA  | SPEN                 | RX9                    | SREN   | CREN  | ADDEN | FERR   | OERR      | RX9D      | 0000 000x             | 0000 000x                       |

| 1Ah                                    | RCREG  | USART Red            | USART Receive Register |        |       |       |        |           |           |                       | 0000 0000                       |

| 8Ch                                    | PIE1   | PSPIE <sup>(1)</sup> | ADIE                   | RCIE   | TXIE  | SSPIE | CCP1IE | TMR2IE    | TMR1IE    | 0000 0000             | 0000 0000                       |

| 98h                                    | TXSTA  | CSRC                 | TX9                    | TXEN   | SYNC  | _     | BRGH   | TRMT      | TX9D      | 0000 -010             | 0000 -010                       |

| 99h SPBRG Baud Rate Generator Register |        |                      |                        |        |       |       |        | 0000 0000 | 0000 0000 |                       |                                 |

Legend: x = unknown, - = unimplemented locations read as '0'. Shaded cells are not used for asynchronous reception.

Note 1: Bits PSPIE and PSPIF are reserved on 28-pin devices; always maintain these bits clear.

#### 10.3.2 USART SYNCHRONOUS MASTER RECEPTION

Once Synchronous mode is selected, reception is enabled by setting either enable bit, SREN (RCSTA<5>), or enable bit, CREN (RCSTA<4>). Data is sampled on the RC7/RX/DT pin on the falling edge of the clock. If enable bit SREN is set, then only a single word is received. If enable bit CREN is set, the reception is continuous until CREN is cleared. If both bits are set, CREN takes precedence. After clocking the last bit, the received data in the Receive Shift Register (RSR) is transferred to the RCREG register (if it is empty). When the transfer is complete, interrupt flag bit, RCIF (PIR1<5>), is set. The actual interrupt can be enabled/ disabled by setting/clearing enable bit, RCIE (PIE1<5>). Flag bit RCIF is a read-only bit which is reset by the hardware. In this case, it is reset when the RCREG register has been read and is empty. The RCREG is a double-buffered register (i.e., it is a twodeep FIFO). It is possible for two bytes of data to be received and transferred to the RCREG FIFO and a third byte to begin shifting into the RSR register. On the clocking of the last bit of the third byte, if the RCREG register is still full, then Overrun Error bit, OERR (RCSTA<1>), is set. The word in the RSR will be lost. The RCREG register can be read twice to retrieve the two bytes in the FIFO. Bit OERR has to be cleared in software (by clearing bit CREN). If bit OERR is set, transfers from the RSR to the RCREG are inhibited so it is essential to clear bit OERR if it is set. The ninth receive bit is buffered the same way as the receive

data. Reading the RCREG register will load bit RX9D with a new value, therefore, it is essential for the user to read the RCSTA register before reading RCREG in order not to lose the old RX9D information.

When setting up a Synchronous Master Reception:

- 1. Initialize the SPBRG register for the appropriate baud rate (Section 10.1 "USART Baud Rate Generator (BRG)").

- 2. Enable the synchronous master serial port by setting bits SYNC, SPEN and CSRC.

- 3. Ensure bits CREN and SREN are clear.

- 4. If interrupts are desired, then set enable bit RCIE.

- 5. If 9-bit reception is desired, then set bit RX9.

- 6. If a single reception is required, set bit SREN. For continuous reception, set bit CREN.

- Interrupt flag bit RCIF will be set when reception is complete and an interrupt will be generated if enable bit RCIE was set.

- 8. Read the RCSTA register to get the ninth bit (if enabled) and determine if any error occurred during reception.

- 9. Read the 8-bit received data by reading the RCREG register.

- 10. If any error occurred, clear the error by clearing bit CREN.

- 11. If using interrupts, ensure that GIE and PEIE (bits 7 and 6) of the INTCON register are set.

| TABLE 10-9. REGISTERS ASSOCIATED WITH STREHKONOOS MASTER RECEPTION |                                                           |                                                                                                     |                                                                                                          |                                                                                                                                                                                                  |                                                                                                                                                                                              |                                                                                                                                                                                                                                                             |                                                                                                                                                                                                                                                      |                                                                                                                                                                                                                                                                               |                                                                                                                                                                                                                                                                                                            |                                                                                                                                                                                                                                                                                                                                                                                                        |

|--------------------------------------------------------------------|-----------------------------------------------------------|-----------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Name                                                               | Bit 7                                                     | Bit 6                                                                                               | Bit 5                                                                                                    | Bit 4                                                                                                                                                                                            | Bit 3                                                                                                                                                                                        | Bit 2                                                                                                                                                                                                                                                       | Bit 1                                                                                                                                                                                                                                                | Bit 0                                                                                                                                                                                                                                                                         | Value on:<br>POR, BOR                                                                                                                                                                                                                                                                                      | Value on<br>all other<br>Resets                                                                                                                                                                                                                                                                                                                                                                        |

| INTCON                                                             | GIE                                                       | PEIE                                                                                                | TMR0IE                                                                                                   | INTE                                                                                                                                                                                             | RBIE                                                                                                                                                                                         | TMR0IF                                                                                                                                                                                                                                                      | INTF                                                                                                                                                                                                                                                 | R0IF                                                                                                                                                                                                                                                                          | 0000 000x                                                                                                                                                                                                                                                                                                  | 0000 000u                                                                                                                                                                                                                                                                                                                                                                                              |

| PIR1                                                               | PSPIF <sup>(1)</sup>                                      | ADIF                                                                                                | RCIF                                                                                                     | TXIF                                                                                                                                                                                             | SSPIF                                                                                                                                                                                        | CCP1IF                                                                                                                                                                                                                                                      | TMR2IF                                                                                                                                                                                                                                               | TMR1IF                                                                                                                                                                                                                                                                        | 0000 0000                                                                                                                                                                                                                                                                                                  | 0000 0000                                                                                                                                                                                                                                                                                                                                                                                              |

| RCSTA                                                              | SPEN                                                      | RX9                                                                                                 | SREN                                                                                                     | CREN                                                                                                                                                                                             |                                                                                                                                                                                              | FERR                                                                                                                                                                                                                                                        | OERR                                                                                                                                                                                                                                                 | RX9D                                                                                                                                                                                                                                                                          | 0000 -00x                                                                                                                                                                                                                                                                                                  | 0000 -00x                                                                                                                                                                                                                                                                                                                                                                                              |

| RCREG                                                              | USART Re                                                  | USART Receive Register                                                                              |                                                                                                          |                                                                                                                                                                                                  |                                                                                                                                                                                              |                                                                                                                                                                                                                                                             |                                                                                                                                                                                                                                                      |                                                                                                                                                                                                                                                                               | 0000 0000                                                                                                                                                                                                                                                                                                  | 0000 0000                                                                                                                                                                                                                                                                                                                                                                                              |

| PIE1                                                               | PSPIE <sup>(1)</sup>                                      | ADIE                                                                                                | RCIE                                                                                                     | TXIE                                                                                                                                                                                             | SSPIE                                                                                                                                                                                        | CCP1IE                                                                                                                                                                                                                                                      | TMR2IE                                                                                                                                                                                                                                               | TMR1IE                                                                                                                                                                                                                                                                        | 0000 0000                                                                                                                                                                                                                                                                                                  | 0000 0000                                                                                                                                                                                                                                                                                                                                                                                              |

| TXSTA                                                              | CSRC                                                      | TX9                                                                                                 | TXEN                                                                                                     | SYNC                                                                                                                                                                                             |                                                                                                                                                                                              | BRGH                                                                                                                                                                                                                                                        | TRMT                                                                                                                                                                                                                                                 | TX9D                                                                                                                                                                                                                                                                          | 0000 -010                                                                                                                                                                                                                                                                                                  | 0000 -010                                                                                                                                                                                                                                                                                                                                                                                              |

| SPBRG                                                              | Baud Rate                                                 | Generato                                                                                            | or Register                                                                                              | r                                                                                                                                                                                                |                                                                                                                                                                                              |                                                                                                                                                                                                                                                             |                                                                                                                                                                                                                                                      |                                                                                                                                                                                                                                                                               | 0000 0000                                                                                                                                                                                                                                                                                                  | 0000 0000                                                                                                                                                                                                                                                                                                                                                                                              |

|                                                                    | Name<br>INTCON<br>PIR1<br>RCSTA<br>RCREG<br>PIE1<br>TXSTA | NameBit 7INTCONGIEPIR1PSPIF <sup>(1)</sup> RCSTASPENRCREGUSART RGPIE1PSPIE <sup>(1)</sup> TXSTACSRC | NameBit 7Bit 6INTCONGIEPEIEPIR1PSPIF(1)ADIFRCSTASPENRX9RCREGUSART Receive RePIE1PSPIE(1)ADIETXSTACSRCTX9 | NameBit 7Bit 6Bit 5INTCONGIEPEIETMR0IEPIR1PSPIF <sup>(1)</sup> ADIFRCIFRCSTASPENRX9SRENRCREGUSART Receive RegisterPIE1PSPIE <sup>(1)</sup> ADIEPIE1PSPIE <sup>(1)</sup> ADIERCIETXSTACSRCTX9TXEN | NameBit 7Bit 6Bit 5Bit 4INTCONGIEPEIETMROIEINTEPIR1PSPIF <sup>(1)</sup> ADIFRCIFTXIFRCSTASPENRX9SRENCRENRCREGUSART Receive RegisterFIE1PSPIE <sup>(1)</sup> ADIERCIETXIETXSTACSRCTX9TXENSYNC | NameBit 7Bit 6Bit 5Bit 4Bit 3INTCONGIEPEIETMROIEINTERBIEPIR1PSPIF <sup>(1)</sup> ADIFRCIFTXIFSSPIFRCSTASPENRX9SRENCREN—RCREGUSART Receive RegisterFIE1PSPIE <sup>(1)</sup> ADIERCIETXIESSPIEPIE1PSPIE <sup>(1)</sup> ADIERCIETXIESSPIETXSTACSRCTX9TXENSYNC— | NameBit 7Bit 6Bit 5Bit 4Bit 3Bit 2INTCONGIEPEIETMR0IEINTERBIETMR0IFPIR1PSPIF <sup>(1)</sup> ADIFRCIFTXIFSSPIFCCP1IFRCSTASPENRX9SRENCREN—FERRRCREGUSART Receive RegisterFFFFPIE1PSPIE <sup>(1)</sup> ADIERCIETXIESSPIECCP1IETXSTACSRCTX9TXENSYNC—BRGH | NameBit 7Bit 6Bit 5Bit 4Bit 3Bit 2Bit 1INTCONGIEPEIETMROIEINTERBIETMROIFINTFPIR1PSPIF <sup>(1)</sup> ADIFRCIFTXIFSSPIFCCP1IFTMR2IFRCSTASPENRX9SRENCREN—FERROERRRCREGUSART Receive RegisterFIE1PSPIE <sup>(1)</sup> ADIERCIETXIESSPIECCP1IETMR2IETXSTACSRCTX9TXENSYNC—BRGHTRMT | NameBit 7Bit 6Bit 5Bit 4Bit 3Bit 2Bit 1Bit 0INTCONGIEPEIETMROIEINTERBIETMROIFINTFROIFPIR1PSPIF <sup>(1)</sup> ADIFRCIFTXIFSSPIFCCP1IFTMR2IFTMR1IFRCSTASPENRX9SRENCREN—FERROERRRX9DRCREGUSART Receive RegisterFIE1PSPIE <sup>(1)</sup> ADIERCIETXIESSPIECCP1IETMR2IETMR1IETXSTACSRCTX9TXENSYNC—BRGHTRMTTX9D | NameBit 7Bit 6Bit 5Bit 4Bit 3Bit 2Bit 1Bit 0Value on:<br>POR, BORINTCONGIEPEIETMROIEINTERBIETMROIFINTFROIF0000000xPIR1PSPIF <sup>(1)</sup> ADIFRCIFTXIFSSPIFCCP1IFTMR2IFTMR1IF00000000RCSTASPENRX9SRENCREN—FERROERRRX9D0000-00xRCREGUSART Receive RegisterSYPIECCP1IETMR2IETMR1IE00000000PIE1PSPIE <sup>(1)</sup> ADIERCIETXIESSPIECCP1IETMR2IETMR1IE00000000TXSTACSRCTX9TXENSYNC—BRGHTRMTTX9D0000-011 |

#### TABLE 10-9: REGISTERS ASSOCIATED WITH SYNCHRONOUS MASTER RECEPTION

Legend: x = unknown, - = unimplemented, read as '0'. Shaded cells are not used for synchronous master reception. Note 1: Bits PSPIE and PSPIF are reserved on 28-pin devices; always maintain these bits clear.

## 12.2 Comparator Operation

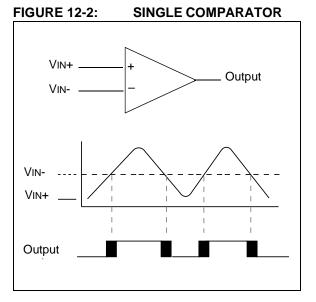

A single comparator is shown in Figure 12-2 along with the relationship between the analog input levels and the digital output. When the analog input at VIN+ is less than the analog input VIN-, the output of the comparator is a digital low level. When the analog input at VIN+ is greater than the analog input VIN-, the output of the comparator is a digital high level. The shaded areas of the output of the comparator in Figure 12-2 represent the uncertainty due to input offsets and response time.

## 12.3 Comparator Reference

An external or internal reference signal may be used depending on the comparator operating mode. The analog signal present at VIN- is compared to the signal at VIN+ and the digital output of the comparator is adjusted accordingly (Figure 12-2).

#### 12.3.1 EXTERNAL REFERENCE SIGNAL

When external voltage references are used, the comparator module can be configured to have the comparators operate from the same or different reference sources. However, threshold detector applications may require the same reference. The reference signal must be between VSS and VDD and can be applied to either pin of the comparator(s).

#### 12.3.2 INTERNAL REFERENCE SIGNAL

The comparator module also allows the selection of an internally generated voltage reference for the comparators. Section 13.0 "Comparator Voltage Reference Module" contains a detailed description of the Comparator Voltage Reference module that provides this signal. The internal reference signal is used when comparators are in mode, CM<2:0> = 110 (Figure 12-1). In this mode, the internal voltage reference is applied to the VIN+ pin of both comparators.

### 12.4 Comparator Response Time

Response time is the minimum time, after selecting a new reference voltage or input source, before the comparator output has a valid level. If the internal reference is changed, the maximum delay of the internal voltage reference must be considered when using the comparator outputs. Otherwise, the maximum delay of the comparators should be used (Section 17.0 "Electrical Characteristics").

## 12.5 Comparator Outputs

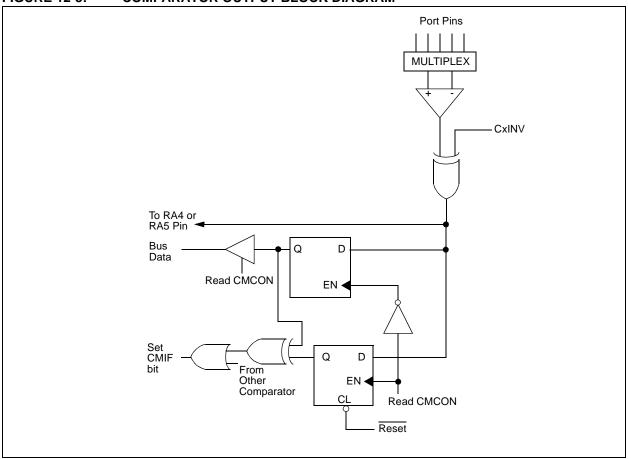

The comparator outputs are read through the CMCON register. These bits are read-only. The comparator outputs may also be directly output to the RA4 and RA5 I/O pins. When enabled, multiplexors in the output path of the RA4 and RA5 pins will switch and the output of each pin will be the unsynchronized output of the comparator. The uncertainty of each of the comparators is related to the input offset voltage and the response time given in the specifications. Figure 12-3 shows the comparator output block diagram.

The TRISA bits will still function as an output enable/ disable for the RA4 and RA5 pins while in this mode.

The polarity of the comparator outputs can be changed using the C2INV and C1INV bits (CMCON<4:5>).

- Note 1: When reading the Port register, all pins configured as analog inputs will read as a '0'. Pins configured as digital inputs will convert an analog input according to the Schmitt Trigger input specification.

- 2: Analog levels on any pin defined as a digital input may cause the input buffer to consume more current than is specified.

- **3:** RA4 is an open collector I/O pin. When used as an output, a pull-up resistor is required.

#### 12.6 Comparator Interrupts

The comparator interrupt flag is set whenever there is a change in the output value of either comparator. Software will need to maintain information about the status of the output bits, as read from CMCON<7:6>, to determine the actual change that occurred. The CMIF bit (PIR registers) is the Comparator Interrupt Flag. The CMIF bit must be reset by clearing it ('0'). Since it is also possible to write a '1' to this register, a simulated interrupt may be initiated.

The CMIE bit (PIE registers) and the PEIE bit (INTCON register) must be set to enable the interrupt. In addition, the GIE bit must also be set. If any of these bits are clear, the interrupt is not enabled, though the CMIF bit will still be set if an interrupt condition occurs.

Note: If a change in the CMCON register (C1OUT or C2OUT) should occur when a read operation is being executed (start of the Q2 cycle), then the CMIF (PIR registers) interrupt flag may not get set.

The user, in the Interrupt Service Routine, can clear the interrupt in the following manner:

- a) Any read or write of CMCON will end the mismatch condition.

- b) Clear flag bit CMIF.

A mismatch condition will continue to set flag bit CMIF. Reading CMCON will end the mismatch condition and allow flag bit CMIF to be cleared.

## 14.0 SPECIAL FEATURES OF THE CPU

All PIC16F87XA devices have a host of features intended to maximize system reliability, minimize cost through elimination of external components, provide power saving operating modes and offer code protection. These are:

- Oscillator Selection

- Reset

- Power-on Reset (POR)

- Power-up Timer (PWRT)

- Oscillator Start-up Timer (OST)

- Brown-out Reset (BOR)

- Interrupts

- Watchdog Timer (WDT)

- Sleep

- Code Protection

- ID Locations

- In-Circuit Serial Programming

- Low-Voltage In-Circuit Serial Programming

- In-Circuit Debugger

PIC16F87XA devices have a Watchdog Timer which can be shut-off only through configuration bits. It runs off its own RC oscillator for added reliability.

There are two timers that offer necessary delays on power-up. One is the Oscillator Start-up Timer (OST), intended to keep the chip in Reset until the crystal oscillator is stable. The other is the Power-up Timer (PWRT), which provides a fixed delay of 72 ms (nominal) on power-up only. It is designed to keep the part in Reset while the power supply stabilizes. With these two timers on-chip, most applications need no external Reset circuitry. Sleep mode is designed to offer a very low current power-down mode. The user can wake-up from Sleep through external Reset, Watchdog Timer wake-up or through an interrupt.

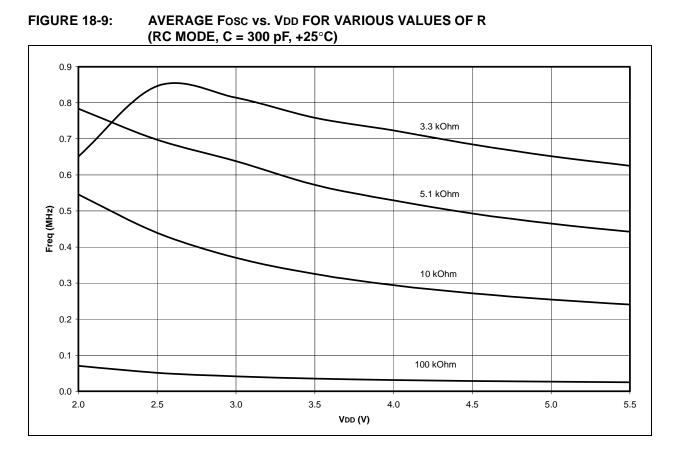

Several oscillator options are also made available to allow the part to fit the application. The RC oscillator option saves system cost while the LP crystal option saves power. A set of configuration bits is used to select various options.

Additional information on special features is available in the PIC<sup>®</sup> Mid-Range MCU Family Reference Manual (DS33023).

## 14.1 Configuration Bits

The configuration bits can be programmed (read as '0'), or left unprogrammed (read as '1') to select various device configurations. The erased or unprogrammed value of the Configuration Word register is 3FFFh. These bits are mapped in program memory location 2007h.

It is important to note that address 2007h is beyond the user program memory space which can be accessed only during programming.

| TABLE 15-2: PIC16 | F87XA INSTRUCTION SET |

|-------------------|-----------------------|

|-------------------|-----------------------|

| Mnem    | nonic, | Description                                    | Cycles        |       | 14-Bit | Status | Notes |          |       |  |

|---------|--------|------------------------------------------------|---------------|-------|--------|--------|-------|----------|-------|--|

| Oper    | ands   | Description                                    | Cycles        | MSb   |        |        | LSb   | Affected | Notes |  |

|         |        | BYTE-ORIENTED FILE                             | EREGISTER OPE | RATIC | NS     |        |       |          |       |  |

| ADDWF   | f, d   | Add W and f                                    | 1             | 00    | 0111   | dfff   | ffff  | C,DC,Z   | 1,2   |  |

| ANDWF   | f, d   | AND W with f                                   | 1             | 00    | 0101   | dfff   | ffff  | Z        | 1,2   |  |

| CLRF    | f      | Clear f                                        | 1             | 00    | 0001   | lfff   | ffff  | Z        | 2     |  |

| CLRW    | -      | Clear W                                        | 1             | 00    | 0001   | 0xxx   | xxxx  | Z        |       |  |

| COMF    | f, d   | Complement f                                   | 1             | 00    | 1001   | dfff   | ffff  | Z        | 1,2   |  |

| DECF    | f, d   | Decrement f                                    | 1             | 00    | 0011   | dfff   | ffff  | Z        | 1,2   |  |

| DECFSZ  | f, d   | Decrement f, Skip if 0                         | 1(2)          | 00    | 1011   | dfff   | ffff  |          | 1,2,3 |  |

| INCF    | f, d   | Increment f                                    | 1             | 00    | 1010   | dfff   | ffff  | Z        | 1,2   |  |

| INCFSZ  | f, d   | Increment f, Skip if 0                         | 1(2)          | 00    | 1111   | dfff   | ffff  |          | 1,2,3 |  |

| IORWF   | f, d   | Inclusive OR W with f                          | 1             | 00    | 0100   | dfff   | ffff  | Z        | 1,2   |  |

| MOVF    | f, d   | Move f                                         | 1             | 00    | 1000   | dfff   | ffff  | Z        | 1,2   |  |

| MOVWF   | f      | Move W to f                                    | 1             | 00    | 0000   | lfff   | ffff  |          |       |  |

| NOP     | -      | No Operation                                   | 1             | 00    | 0000   | 0xx0   | 0000  |          |       |  |

| RLF     | f, d   | Rotate Left f through Carry                    | 1             | 00    | 1101   | dfff   | ffff  | С        | 1,2   |  |

| RRF     | f, d   | Rotate Right f through Carry                   | 1             | 00    | 1100   | dfff   | ffff  | С        | 1,2   |  |

| SUBWF   | f, d   | Subtract W from f                              | 1             | 00    | 0010   | dfff   | ffff  | C,DC,Z   | 1,2   |  |

| SWAPF   | f, d   | Swap nibbles in f                              | 1             | 00    | 1110   | dfff   | ffff  |          | 1,2   |  |

| XORWF   | f, d   | Exclusive OR W with f                          | 1             | 00    | 0110   | dfff   | ffff  | Z        | 1,2   |  |

|         |        | BIT-ORIENTED FILE                              | REGISTER OPER | ATION | ١S     |        |       |          |       |  |

| BCF     | f, b   | Bit Clear f                                    | 1             | 01    | 00bb   | bfff   | ffff  |          | 1,2   |  |

| BSF     | f, b   | Bit Set f                                      | 1             | 01    | 01bb   | bfff   | ffff  |          | 1,2   |  |

| BTFSC   | f, b   | Bit Test f, Skip if Clear                      | 1 (2)         | 01    | 10bb   | bfff   | ffff  |          | 3     |  |

| BTFSS   | f, b   | Bit Test f, Skip if Set                        | 1 (2)         | 01    | 11bb   | bfff   | ffff  |          | 3     |  |

|         |        | LITERAL AND CO                                 | NTROL OPERAT  | IONS  |        |        |       |          |       |  |

| ADDLW   | k      | Add Literal and W                              | 1             | 11    | 111x   | kkkk   | kkkk  | C,DC,Z   |       |  |

| ANDLW   | k      | AND Literal with W                             | 1             | 11    | 1001   | kkkk   | kkkk  | Z        |       |  |

| CALL    | k      | Call Subroutine                                | 2             | 10    | 0kkk   | kkkk   | kkkk  |          |       |  |

| CLRWDT  | -      | Clear Watchdog Timer                           | 1             | 00    | 0000   | 0110   | 0100  | TO,PD    |       |  |

| GOTO    | k      | Go to Address                                  | 2             | 10    | 1kkk   | kkkk   | kkkk  | -        |       |  |

| IORLW   | k      | Inclusive OR Literal with W                    | 1             | 11    | 1000   | kkkk   | kkkk  | Z        |       |  |

| MOVLW   | k      | Move Literal to W                              | 1             | 11    | 00xx   | kkkk   | kkkk  |          |       |  |

| RETFIE  | -      | Return from Interrupt                          | 2             | 00    | 0000   | 0000   | 1001  |          |       |  |

| RETLW   | k      | Return with Literal in W                       | 2             | 11    | 01xx   | kkkk   |       |          |       |  |

| RETURN  | -      | Return from Subroutine                         | 2             | 00    | 0000   | 0000   | 1000  |          |       |  |

| SLEEP   | -      | Go into Standby mode                           | 1             | 00    | 0000   | 0110   | 0011  | TO,PD    |       |  |

| SUBLW   | k      | Subtract W from Literal                        | 1             | 11    |        | kkkk   |       | C,DC,Z   |       |  |

| XORLW   | k      | Exclusive OR Literal with W                    | 1             | 11    | 1010   | kkkk   |       | Z        |       |  |

| Note 1: |        | I/O register is modified as a function of itse |               |       |        |        |       |          |       |  |

Note 1: When an I/O register is modified as a function of itself (e.g., MOVF PORTE, 1), the value used will be that value present on the pins themselves. For example, if the data latch is '1' for a pin configured as input and is driven low by an external device, the data will be written back with a '0'.

2: If this instruction is executed on the TMR0 register (and where applicable, d = 1), the prescaler will be cleared if assigned to the Timer0 module.

3: If Program Counter (PC) is modified, or a conditional test is true, the instruction requires two cycles. The second cycle is executed as a NOP.

**Note:** Additional information on the mid-range instruction set is available in the PIC<sup>®</sup> Mid-Range MCU Family Reference Manual (DS33023).

NOTES:

#### 17.1 DC Characteristics: PIC16F873A/874A/876A/877A (Industrial, Extended) PIC16LF873A/874A/876A/877A (Industrial)

| PIC16LF873A/874A/876A/877A<br>(Industrial)          |        |                                                                  |      | Standard Operating Conditions (unless otherwise stated)Operating temperature $-40^{\circ}C \le TA \le +85^{\circ}C$ for industrial |      |       |                                                        |  |  |  |  |

|-----------------------------------------------------|--------|------------------------------------------------------------------|------|------------------------------------------------------------------------------------------------------------------------------------|------|-------|--------------------------------------------------------|--|--|--|--|

| PIC16F873A/874A/876A/877A<br>(Industrial, Extended) |        |                                                                  |      | $\begin{array}{llllllllllllllllllllllllllllllllllll$                                                                               |      |       |                                                        |  |  |  |  |

| Param<br>No.                                        | Symbol | Characteristic/<br>Device                                        | Min  | Тур†                                                                                                                               | Max  | Units | Conditions                                             |  |  |  |  |

|                                                     | Vdd    | Supply Voltage                                                   |      |                                                                                                                                    |      |       |                                                        |  |  |  |  |

| D001                                                |        | 16LF87XA                                                         | 2.0  | —                                                                                                                                  | 5.5  | V     | All configurations<br>(DC to 10 MHz)                   |  |  |  |  |

| D001                                                |        | 16F87XA                                                          | 4.0  |                                                                                                                                    | 5.5  | V     | All configurations                                     |  |  |  |  |

| D001A                                               |        |                                                                  | VBOR |                                                                                                                                    | 5.5  | V     | BOR enabled, FMAX = 14 MHz <sup>(7)</sup>              |  |  |  |  |

| D002                                                | Vdr    | RAM Data Retention<br>Voltage <sup>(1)</sup>                     | —    | 1.5                                                                                                                                |      | V     |                                                        |  |  |  |  |

| D003                                                | VPOR   | VDD Start Voltage to<br>ensure internal Power-on<br>Reset signal | —    | Vss                                                                                                                                | _    | V     | See Section 14.5 "Power-on<br>Reset (POR)" for details |  |  |  |  |

| D004                                                | Svdd   | VDD Rise Rate to ensure<br>internal Power-on Reset<br>signal     | 0.05 | —                                                                                                                                  | —    | V/ms  | See Section 14.5 "Power-on<br>Reset (POR)" for details |  |  |  |  |

| D005                                                | VBOR   | Brown-out Reset<br>Voltage                                       | 3.65 | 4.0                                                                                                                                | 4.35 | V     | BODEN bit in configuration word<br>enabled             |  |  |  |  |

Legend: Rows with standard voltage device data only are shaded for improved readability.

- † Data in "Typ" column is at 5V, 25°C, unless otherwise stated. These parameters are for design guidance only and are not tested.

- **Note 1:** This is the limit to which VDD can be lowered without losing RAM data.

- 2: The supply current is mainly a function of the operating voltage and frequency. Other factors, such as I/O pin loading, switching rate, oscillator type, internal code execution pattern and temperature, also have an impact on the current consumption.

- The test conditions for all IDD measurements in active operation mode are:

- OSC1 = external square wave, from rail-to-rail; all I/O pins tri-stated, pulled to VDD;

- MCLR = VDD; WDT enabled/disabled as specified.

- **3:** The power-down current in Sleep mode does not depend on the oscillator type. Power-down current is measured with the part in Sleep mode, with all I/O pins in high-impedance state and tied to VDD and Vss.

- **4:** For RC osc configuration, current through REXT is not included. The current through the resistor can be estimated by the formula Ir = VDD/2REXT (mA) with REXT in kΩ.

- **5:** Timer1 oscillator (when enabled) adds approximately 20 μA to the specification. This value is from characterization and is for design guidance only. This is not tested.

- 6: The  $\Delta$  current is the additional current consumed when this peripheral is enabled. This current should be added to the base IDD or IPD measurement.

- 7: When BOR is enabled, the device will operate correctly until the VBOR voltage trip point is reached.

100 Max (125°C) 10 Max (85°C) 1 IPD (NA) 0.1 0.01 Тур (25°С) Typical: statistical mean @ 25°C Maximum: mean +  $3\sigma$  (-40°C to +125°C) Minimum: mean -  $3\sigma$  (-40°C to +125°C) 0.001 2.0 2.5 3.0 3.5 4.0 4.5 5.0 5.5 VDD (V)

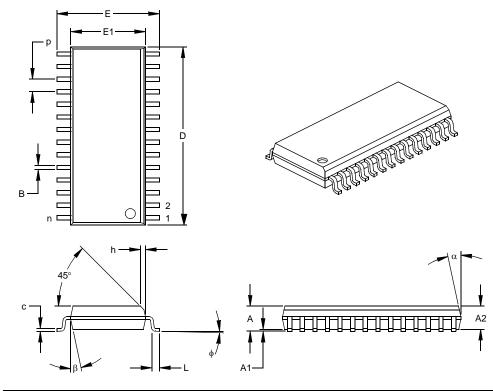

## 28-Lead Plastic Small Outline (SO) – Wide, 300 mil (SOIC)

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

|                          | Units       |      |      |      | MILLIMETERS |       |       |  |

|--------------------------|-------------|------|------|------|-------------|-------|-------|--|

| Dimens                   | sion Limits | MIN  | NOM  | MAX  | MIN         | NOM   | MAX   |  |

| Number of Pins           | n           |      | 28   |      |             | 28    |       |  |

| Pitch                    | р           |      | .050 |      |             | 1.27  |       |  |

| Overall Height           | А           | .093 | .099 | .104 | 2.36        | 2.50  | 2.64  |  |

| Molded Package Thickness | A2          | .088 | .091 | .094 | 2.24        | 2.31  | 2.39  |  |

| Standoff §               | A1          | .004 | .008 | .012 | 0.10        | 0.20  | 0.30  |  |

| Overall Width            | E           | .394 | .407 | .420 | 10.01       | 10.34 | 10.67 |  |

| Molded Package Width     | E1          | .288 | .295 | .299 | 7.32        | 7.49  | 7.59  |  |