Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                     |

|----------------------------|----------------------------------------------------------------------------|

| Core Processor             | PIC                                                                        |

| Core Size                  | 8-Bit                                                                      |

| Speed                      | 20MHz                                                                      |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                          |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                      |

| Number of I/O              | 33                                                                         |

| Program Memory Size        | 14KB (8K x 14)                                                             |

| Program Memory Type        | FLASH                                                                      |

| EEPROM Size                | 256 x 8                                                                    |

| RAM Size                   | 368 x 8                                                                    |

| Voltage - Supply (Vcc/Vdd) | 4V ~ 5.5V                                                                  |

| Data Converters            | A/D 8x10b                                                                  |

| Oscillator Type            | External                                                                   |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                          |

| Mounting Type              | Surface Mount                                                              |

| Package / Case             | 44-TQFP                                                                    |

| Supplier Device Package    | 44-TQFP (10x10)                                                            |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16f877at-i-pt |

|                            |                                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

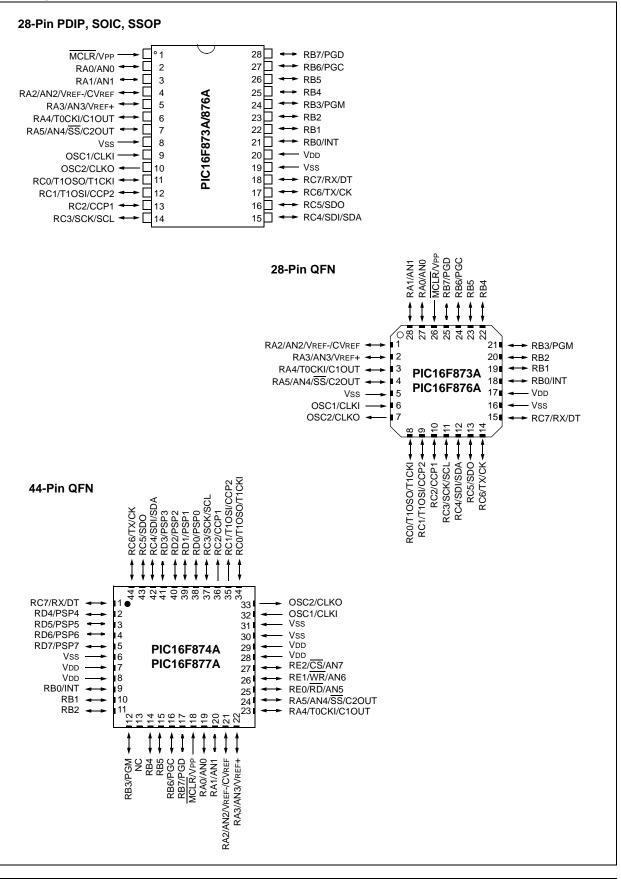

#### **Pin Diagrams**

| Pin Name        | PDIP, SOIC,<br>SSOP Pin# | QFN<br>Pin# | I/O/P<br>Type | Buffer<br>Type        | Description                                                                         |

|-----------------|--------------------------|-------------|---------------|-----------------------|-------------------------------------------------------------------------------------|

|                 |                          |             |               |                       | PORTB is a bidirectional I/O port. PORTB can be software                            |

|                 |                          |             |               |                       | programmed for internal weak pull-ups on all inputs.                                |

| RB0/INT         | 21                       | 18          |               | TTL/ST <sup>(1)</sup> |                                                                                     |

| RB0             |                          |             | I/O           |                       | Digital I/O.                                                                        |

| INT             |                          |             | I             |                       | External interrupt.                                                                 |

| RB1             | 22                       | 19          | I/O           | TTL                   | Digital I/O.                                                                        |

| RB2             | 23                       | 20          | I/O           | TTL                   | Digital I/O.                                                                        |

| RB3/PGM         | 24                       | 21          |               | TTL                   |                                                                                     |

| RB3             |                          |             | I/O           |                       | Digital I/O.                                                                        |

| PGM             |                          |             | I             |                       | Low-voltage (single-supply) ICSP programming enable pir                             |

| RB4             | 25                       | 22          | I/O           | TTL                   | Digital I/O.                                                                        |

| RB5             | 26                       | 23          | I/O           | TTL                   | Digital I/O.                                                                        |

| RB6/PGC         | 27                       | 24          |               | TTL/ST <sup>(2)</sup> |                                                                                     |

| RB6             |                          |             | I/O           |                       | Digital I/O.                                                                        |

| PGC             |                          |             | I             |                       | In-circuit debugger and ICSP programming clock.                                     |

| RB7/PGD         | 28                       | 25          |               | TTL/ST <sup>(2)</sup> |                                                                                     |

| RB7             | -                        | -           | I/O           |                       | Digital I/O.                                                                        |

| PGD             |                          |             | I/O           |                       | In-circuit debugger and ICSP programming data.                                      |

|                 |                          |             |               |                       | PORTC is a bidirectional I/O port.                                                  |

| RC0/T1OSO/T1CKI | 11                       | 8           |               | ST                    |                                                                                     |

| RC0             |                          | -           | I/O           |                       | Digital I/O.                                                                        |

| T1OSO           |                          |             | 0             |                       | Timer1 oscillator output.                                                           |

| T1CKI           |                          |             | I             |                       | Timer1 external clock input.                                                        |

| RC1/T1OSI/CCP2  | 12                       | 9           |               | ST                    |                                                                                     |

| RC1             |                          |             | I/O           |                       | Digital I/O.                                                                        |

| T1OSI           |                          |             | 1             |                       | Timer1 oscillator input.                                                            |

| CCP2            |                          |             | I/O           |                       | Capture2 input, Compare2 output, PWM2 output.                                       |

| RC2/CCP1        | 13                       | 10          |               | ST                    |                                                                                     |

| RC2             |                          |             | I/O           |                       | Digital I/O.                                                                        |

| CCP1            |                          |             | I/O           |                       | Capture1 input, Compare1 output, PWM1 output.                                       |

| RC3/SCK/SCL     | 14                       | 11          | 1/0           | ST                    | District VO                                                                         |

| RC3<br>SCK      |                          |             | I/O<br>I/O    |                       | Digital I/O.<br>Synchronous serial clock input/output for SPI mode.                 |

| SCL             |                          |             | 1/O           |                       | Synchronous serial clock input/output for Sr I mode.                                |

| RC4/SDI/SDA     | 15                       | 12          | ., 0          | ST                    |                                                                                     |

| RC4             | 15                       | 12          | I/O           | 51                    | Digital I/O.                                                                        |

| SDI             |                          |             | ., c          |                       | SPI data in.                                                                        |

| SDA             |                          |             | I/O           |                       | I <sup>2</sup> C data I/O.                                                          |

| RC5/SDO         | 16                       | 13          |               | ST                    |                                                                                     |

| RC5             |                          |             | I/O           |                       | Digital I/O.                                                                        |

| SDO             |                          |             | 0             |                       | SPI data out.                                                                       |

| RC6/TX/CK       | 17                       | 14          |               | ST                    |                                                                                     |

| RC6             |                          |             | I/O           |                       | Digital I/O.                                                                        |

| TX              |                          |             | 0             |                       | USART asynchronous transmit.                                                        |

| CK              |                          |             | I/O           |                       | USART1 synchronous clock.                                                           |

| RC7/RX/DT       | 18                       | 15          |               | ST                    |                                                                                     |

| RC7             |                          |             | I/O           |                       | Digital I/O.                                                                        |

| RX<br>DT        |                          |             | I/O           |                       | USART asynchronous receive.                                                         |

|                 | 0.40                     | <b>F A</b>  |               |                       | USART synchronous data.                                                             |

| Vss             | 8, 19<br>20              | 5,6         | P             |                       | Ground reference for logic and I/O pins.<br>Positive supply for logic and I/O pins. |

| Vdd             |                          | 17          | Р             |                       |                                                                                     |

| TABLE 1-2: PIC16F873A/876A PINOUT DESCRIPTION (CONTINUE |

|---------------------------------------------------------|

|---------------------------------------------------------|

**Note 1:** This buffer is a Schmitt Trigger input when configured as the external interrupt.

2: This buffer is a Schmitt Trigger input when used in Serial Programming mode.

3: This buffer is a Schmitt Trigger input when configured in RC Oscillator mode and a CMOS input otherwise.

|                                                     | PDIP | IP PLCC | TQFP | QFN  | I/O/P              | Buffer                 |                                                                                                                                                                     |

|-----------------------------------------------------|------|---------|------|------|--------------------|------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Pin Name                                            | Pin# | Pin#    | Pin# | Pin# | Туре               | Туре                   | Description                                                                                                                                                         |

| OSC1/CLKI<br>OSC1                                   | 13   | 14      | 30   | 32   | I                  | ST/CMOS <sup>(4)</sup> | Oscillator crystal or external clock input.<br>Oscillator crystal input or external clock source<br>input. ST buffer when configured in RC mode;<br>otherwise CMOS. |

| CLKI                                                |      |         |      |      | Ι                  |                        | External clock source input. Always associated<br>with pin function OSC1 (see OSC1/CLKI,<br>OSC2/CLKO pins).                                                        |

| OSC2/CLKO<br>OSC2                                   | 14   | 15      | 31   | 33   | 0                  | _                      | Oscillator crystal or clock output.<br>Oscillator crystal output.<br>Connects to crystal or resonator in Crystal<br>Oscillator mode.                                |

| CLKO                                                |      |         |      |      | 0                  |                        | In RC mode, OSC2 pin outputs CLKO, which<br>has 1/4 the frequency of OSC1 and denotes the<br>instruction cycle rate.                                                |

| MCLR/VPP<br>MCLR                                    | 1    | 2       | 18   | 18   | I                  | ST                     | Master Clear (input) or programming voltage (output)<br>Master Clear (Reset) input. This pin is an active<br>low Reset to the device.                               |

| Vpp                                                 |      |         |      |      | Р                  |                        | Programming voltage input.                                                                                                                                          |

|                                                     |      |         | 10   | 10   |                    |                        | PORTA is a bidirectional I/O port.                                                                                                                                  |

| RA0/AN0<br>RA0<br>AN0                               | 2    | 3       | 19   | 19   | I/O<br>I           | TTL                    | Digital I/O.<br>Analog input 0.                                                                                                                                     |

| RA1/AN1<br>RA1<br>AN1                               | 3    | 4       | 20   | 20   | I/O<br>I           | TTL                    | Digital I/O.<br>Analog input 1.                                                                                                                                     |

| RA2/AN2/VREF-/CVREF<br>RA2<br>AN2<br>VREF-<br>CVREF | 4    | 5       | 21   | 21   | I/O<br>I<br>I<br>O | TTL                    | Digital I/O.<br>Analog input 2.<br>A/D reference voltage (Low) input.<br>Comparator VREF output.                                                                    |

| RA3/AN3/Vref+<br>RA3<br>AN3<br>Vref+                | 5    | 6       | 22   | 22   | I/O<br>I<br>I      | TTL                    | Digital I/O.<br>Analog input 3.<br>A/D reference voltage (High) input.                                                                                              |

| RA4/T0CKI/C1OUT<br>RA4                              | 6    | 7       | 23   | 23   | I/O                | ST                     | Digital I/O – Open-drain when configured as output.                                                                                                                 |

| T0CKI<br>C1OUT                                      |      |         |      |      | I<br>O             |                        | Timer0 external clock input.<br>Comparator 1 output.                                                                                                                |

| RA5/AN4/SS/C2OUT<br>RA5<br>AN4<br>SS<br>C2OUT       | 7    | 8       | 24   | 24   | I/O<br>I<br>0      | TTL                    | Digital I/O.<br>Analog input 4.<br>SPI slave select input.<br>Comparator 2 output.                                                                                  |

#### TABLE 1-3: PIC16F874A/877A PINOUT DESCRIPTION

— = Not used TTL = TTL input ST = Schmitt Trigger input

Note 1: This buffer is a Schmitt Trigger input when configured as the external interrupt.

This buffer is a Schmitt Trigger input when used in Serial Programming mode.

3: This buffer is a Schmitt Trigger input when configured in RC Oscillator mode and a CMOS input otherwise.

| Address              | Name       | Bit 7                | Bit 6                               | Bit 5                     | Bit 4          | Bit 3        | Bit 2            | Bit 1         | Bit 0        | Value on:<br>POR, BOR | Details<br>on page |

|----------------------|------------|----------------------|-------------------------------------|---------------------------|----------------|--------------|------------------|---------------|--------------|-----------------------|--------------------|

| Bank 1               |            |                      |                                     |                           |                |              |                  |               |              |                       |                    |

| 80h <sup>(3)</sup>   | INDF       | Addressing           | this locatio                        | n uses cont               | ents of FSR t  | o address d  | ata memory (     | not a physic  | al register) | 0000 0000             | 31, 150            |

| 81h                  | OPTION_REG | RBPU                 | INTEDG                              | TOCS                      | T0SE           | PSA          | PS2              | PS1           | PS0          | 1111 1111             | 23, 150            |

| 82h <sup>(3)</sup>   | PCL        | Program C            | ounter (PC)                         | Least Sign                | ificant Byte   |              |                  |               |              | 0000 0000             | 30, 150            |

| 83h <sup>(3)</sup>   | STATUS     | IRP                  | RP1                                 | RP0                       | TO             | PD           | Z                | DC            | С            | 0001 1xxx             | 22, 150            |

| 84h <sup>(3)</sup>   | FSR        | Indirect Da          | ndirect Data Memory Address Pointer |                           |                |              |                  |               |              |                       |                    |

| 85h                  | TRISA      |                      |                                     | PORTA Da                  | ta Direction F | Register     |                  |               |              | 11 1111               | 43, 150            |

| 86h                  | TRISB      | PORTB Da             | ata Direction                       | Register                  |                |              |                  |               |              | 1111 1111             | 45, 150            |

| 87h                  | TRISC      | PORTC Da             | ata Directior                       | Register                  |                |              |                  |               |              | 1111 1111             | 47, 150            |

| 88h <sup>(4)</sup>   | TRISD      | PORTD Da             | ata Directior                       | n Register                |                |              |                  |               |              | 1111 1111             | 48, 151            |

| 89h <sup>(4)</sup>   | TRISE      | IBF                  | OBF                                 | IBOV                      | PSPMODE        |              | PORTE Dat        | a Direction I | bits         | 0000 -111             | 50, 151            |

| 8Ah <sup>(1,3)</sup> | PCLATH     | —                    |                                     |                           | Write Buffer   | for the uppe | er 5 bits of the | e Program C   | Counter      | 0 0000                | 30, 150            |

| 8Bh <sup>(3)</sup>   | INTCON     | GIE                  | PEIE                                | TMR0IE                    | INTE           | RBIE         | TMR0IF           | INTF          | RBIF         | 0000 000x             | 24, 150            |

| 8Ch                  | PIE1       | PSPIE <sup>(2)</sup> | ADIE                                | RCIE                      | TXIE           | SSPIE        | CCP1IE           | TMR2IE        | TMR1IE       | 0000 0000             | 25, 151            |

| 8Dh                  | PIE2       | —                    | CMIE                                |                           | EEIE           | BCLIE        | —                | _             | CCP2IE       | -0-0 00               | 27, 151            |

| 8Eh                  | PCON       | _                    |                                     |                           | _              |              | _                | POR           | BOR          | dd                    | 29, 151            |

| 8Fh                  | —          | Unimpleme            | ented                               |                           |                |              |                  |               |              | —                     |                    |

| 90h                  | —          | Unimpleme            | ented                               |                           |                |              |                  |               |              | _                     | _                  |

| 91h                  | SSPCON2    | GCEN                 | ACKSTAT                             | ACKDT                     | ACKEN          | RCEN         | PEN              | RSEN          | SEN          | 0000 0000             | 83, 151            |

| 92h                  | PR2        | Timer2 Per           | riod Registe                        | r                         |                |              |                  |               |              | 1111 1111             | 62, 151            |

| 93h                  | SSPADD     | Synchrono            | us Serial Po                        | ort (I <sup>2</sup> C mod | e) Address R   | egister      |                  |               |              | 0000 0000             | 79, 151            |

| 94h                  | SSPSTAT    | SMP                  | CKE                                 | D/A                       | Р              | S            | R/W              | UA            | BF           | 0000 0000             | 79, 151            |

| 95h                  | —          | Unimpleme            | ented                               |                           | •              |              |                  |               |              | —                     |                    |

| 96h                  | _          | Unimpleme            | ented                               |                           |                |              |                  |               |              | —                     |                    |

| 97h                  | —          | Unimpleme            | ented                               |                           |                |              |                  |               |              | —                     |                    |

| 98h                  | TXSTA      | CSRC                 | TX9                                 | TXEN                      | SYNC           | _            | BRGH             | TRMT          | TX9D         | 0000 -010             | 111, 151           |

| 99h                  | SPBRG      | Baud Rate            | Generator                           | Register                  | •              |              |                  |               |              | 0000 0000             | 113, 151           |

| 9Ah                  | —          | Unimpleme            | ented                               |                           |                |              |                  |               |              | _                     | _                  |

| 9Bh                  | _          | Unimpleme            | ented                               |                           |                |              |                  |               |              | _                     | —                  |

| 9Ch                  | CMCON      | C2OUT                | C1OUT                               | C2INV                     | C1INV          | CIS          | CM2              | CM1           | CM0          | 0000 0111             | 135, 151           |

| 9Dh                  | CVRCON     | CVREN                | CVROE                               | CVRR                      | _              | CVR3         | CVR2             | CVR1          | CVR0         | 000- 0000             | 141, 151           |

| 9Eh                  | ADRESL     | A/D Result           | Register Lo                         | w Byte                    |                |              |                  |               |              | xxxx xxxx             | 133, 151           |

| 9Fh                  | ADCON1     | ADFM                 | ADCS2                               | _                         | _              | PCFG3        | PCFG2            | PCFG1         | PCFG0        | 00 0000               | 128, 151           |

####

x = unknown, u = unchanged, q = value depends on condition, - = unimplemented, read as '0', r = reserved. Legend: Shaded locations are unimplemented, read as '0'.

Note 1: The upper byte of the program counter is not directly accessible. PCLATH is a holding register for the PC<12:8>, whose contents are transferred to the upper byte of the program counter.

2: Bits PSPIE and PSPIF are reserved on PIC16F873A/876A devices; always maintain these bits clear.

3: These registers can be addressed from any bank.

4: PORTD, PORTE, TRISD and TRISE are not implemented on PIC16F873A/876A devices, read as '0'.

5: Bit 4 of EEADRH implemented only on the PIC16F876A/877A devices.

#### 2.2.2.5 PIR1 Register

The PIR1 register contains the individual flag bits for the peripheral interrupts.

# **Note:** Interrupt flag bits are set when an interrupt condition occurs regardless of the state of its corresponding enable bit or the global enable bit, GIE (INTCON<7>). User software should ensure the appropriate interrupt bits are clear prior to enabling an interrupt.

| <b>REGISTER 2-5:</b> | PIR1 REGI                                                                                                                                       | STER (AD                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | DRESS 0                                      | Ch)            |                           |           |                         |            |  |  |  |

|----------------------|-------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------|----------------|---------------------------|-----------|-------------------------|------------|--|--|--|

|                      | R/W-0                                                                                                                                           | R/W-0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | R-0                                          | ,<br>R-0       | R/W-0                     | R/W-0     | R/W-0                   | R/W-0      |  |  |  |

|                      | PSPIF <sup>(1)</sup>                                                                                                                            | ADIF                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | RCIF                                         | TXIF           | SSPIF                     | CCP1IF    | TMR2IF                  | TMR1IF     |  |  |  |

|                      | bit 7                                                                                                                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                              |                |                           |           |                         | bit 0      |  |  |  |

| bit 7                | <b>PSPIF:</b> Par                                                                                                                               | allel Slave I                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | Port Read/W                                  | /rite Interrup | t Flag bit <sup>(1)</sup> |           |                         |            |  |  |  |

|                      | 1 = A read<br>0 = No read                                                                                                                       | or a write op<br>I or write ha                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | peration has<br>as occurred                  | taken place    | e (must be cl             |           | tware)<br>maintain this | bit clear. |  |  |  |

| bit 6                |                                                                                                                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | nterrupt Flag                                |                |                           |           |                         |            |  |  |  |

|                      | 1 = An A/D                                                                                                                                      | conversion                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                              |                |                           |           |                         |            |  |  |  |

| bit 5                | RCIF: USA                                                                                                                                       | RCIF: USART Receive Interrupt Flag bit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                              |                |                           |           |                         |            |  |  |  |

|                      |                                                                                                                                                 | <ul> <li>1 = The USART receive buffer is full</li> <li>0 = The USART receive buffer is empty</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                              |                |                           |           |                         |            |  |  |  |

| bit 4                | TXIF: USAF                                                                                                                                      | RT Transmit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | t Interrupt Fl                               | ag bit         |                           |           |                         |            |  |  |  |

|                      |                                                                                                                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | nit buffer is e<br>nit buffer is f           |                |                           |           |                         |            |  |  |  |

| bit 3                | -                                                                                                                                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                              |                | -                         |           |                         |            |  |  |  |

|                      | from th<br>• SPI -<br>• I <sup>2</sup> C M<br>• I <sup>2</sup> C M<br>- A f<br>- Th<br>- Th<br>- Th<br>- Th<br>- Th<br>- A f                    | <ul> <li>SSPIF: Synchronous Serial Port (SSP) Interrupt Flag bit</li> <li>1 = The SSP interrupt condition has occurred and must be cleared in software before returning from the Interrupt Service Routine. The conditions that will set this bit are:</li> <li>SPI – A transmission/reception has taken place.</li> <li>I<sup>2</sup>C Slave – A transmission/reception has taken place.</li> <li>I<sup>2</sup>C Master <ul> <li>A transmission/reception has taken place.</li> <li>The initiated Start condition was completed by the SSP module.</li> <li>The initiated Restart condition was completed by the SSP module.</li> <li>The initiated Restart condition was completed by the SSP module.</li> <li>The initiated Acknowledge condition was completed by the SSP module.</li> <li>A start condition occurred while the SSP module was Idle (multi-master system).</li> <li>A Stop condition occurred while the SSP module was Idle (multi-master system).</li> </ul> </li> </ul> |                                              |                |                           |           |                         |            |  |  |  |

| bit 2                | CCP1IF: CO                                                                                                                                      | CP1 Interru                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | pt Flag bit                                  |                |                           |           |                         |            |  |  |  |

|                      | <u>Capture mode:</u><br>1 = A TMR1 register capture occurred (must be cleared in software)<br>0 = No TMR1 register capture occurred             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                              |                |                           |           |                         |            |  |  |  |

|                      | <u>Compare mode:</u><br>1 = A TMR1 register compare match occurred (must be cleared in software)<br>0 = No TMR1 register compare match occurred |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                              |                |                           |           |                         |            |  |  |  |

|                      | <u>PWM mode:</u><br>Unused in this mode.                                                                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                              |                |                           |           |                         |            |  |  |  |

| bit 1                | TMR2IF: TM                                                                                                                                      | /IR2 to PR2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 2 Match Inter                                | rrupt Flag bit | t                         |           |                         |            |  |  |  |

|                      |                                                                                                                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | ch occurred<br>natch occurr                  |                | ared in soft              | vare)     |                         |            |  |  |  |

| bit 0                | 1 = TMR1 r                                                                                                                                      | egister over                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | ow Interrupt<br>rflowed (mus<br>not overflow | st be cleared  | d in software             | )         |                         |            |  |  |  |

|                      | Legend:                                                                                                                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                              |                |                           |           |                         | ]          |  |  |  |

|                      | R = Readat                                                                                                                                      | ole bit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | W = W                                        | ritable bit    | U = Unim                  | plemented | bit, read as '          | 0'         |  |  |  |

|                      | - n = Value                                                                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | '1' = B                                      | it is set      |                           | s cleared | x = Bit is u            |            |  |  |  |

#### 9.4.14 SLEEP OPERATION

While in Sleep mode, the  $I^2C$  module can receive addresses or data and when an address match or complete byte transfer occurs, wake the processor from Sleep (if the MSSP interrupt is enabled).

#### 9.4.15 EFFECT OF A RESET

A Reset disables the MSSP module and terminates the current transfer.

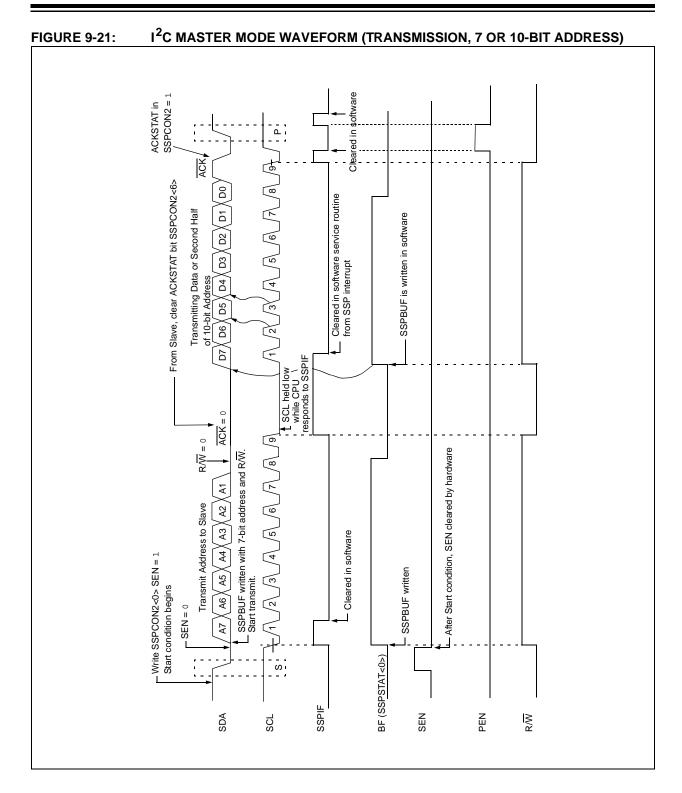

#### 9.4.16 MULTI-MASTER MODE

In Multi-Master mode, the interrupt generation on the detection of the Start and Stop conditions allows the determination of when the bus is free. The Stop (P) and Start (S) bits are cleared from a Reset or when the MSSP module is disabled. Control of the  $I^2C$  bus may be taken when the P bit (SSPSTAT<4>) is set, or the bus is Idle, with both the S and P bits clear. When the bus is busy, enabling the SSP interrupt will generate the interrupt when the Stop condition occurs.

In multi-master operation, the SDA line must be monitored for arbitration to see if the signal level is at the expected output level. This check is performed in hardware with the result placed in the BCLIF bit.

The states where arbitration can be lost are:

- · Address Transfer

- Data Transfer

- A Start Condition

- A Repeated Start Condition

- An Acknowledge Condition

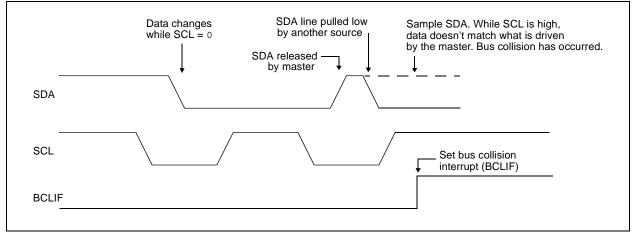

#### 9.4.17 MULTI -MASTER COMMUNICATION, BUS COLLISION AND BUS ARBITRATION

Multi-Master mode support is achieved by bus arbitration. When the master outputs address/data bits onto the SDA pin, arbitration takes place when the master outputs a '1' on SDA by letting SDA float high and another master asserts a '0'. When the SCL pin floats high, data should be stable. If the expected data on SDA is a '1' and the data sampled on the SDA pin = 0, then a bus collision has taken place. The master will set the Bus Collision Interrupt Flag, BCLIF, and reset the  $I^2C$  port to its Idle state (Figure 9-25).

If a transmit was in progress when the bus collision occurred, the transmission is halted, the BF flag is cleared, the SDA and SCL lines are deasserted and the SSPBUF can be written to. When the user services the bus collision Interrupt Service Routine and if the  $I^2C$  bus is free, the user can resume communication by asserting a Start condition.

If a Start, Repeated Start, Stop or Acknowledge condition was in progress when the bus collision occurred, the condition is aborted, the SDA and SCL lines are deasserted and the respective control bits in the SSPCON2 register are cleared. When the user services the bus collision Interrupt Service Routine and if the I<sup>2</sup>C bus is free, the user can resume communication by asserting a Start condition.

The Master will continue to monitor the SDA and SCL pins. If a Stop condition occurs, the SSPIF bit will be set.

A write to the SSPBUF will start the transmission of data at the first data bit regardless of where the transmitter left off when the bus collision occurred.

In Multi-Master mode, the interrupt generation on the detection of Start and Stop conditions allows the determination of when the bus is free. Control of the  $I^2C$  bus can be taken when the P bit is set in the SSPSTAT register or the bus is Idle and the S and P bits are cleared.

#### FIGURE 9-25: BUS COLLISION TIMING FOR TRANSMIT AND ACKNOWLEDGE

© 2001-2013 Microchip Technology Inc.

#### 10.2 USART Asynchronous Mode

In this mode, the USART uses standard Non-Returnto-Zero (NRZ) format (one Start bit, eight or nine data bits and one Stop bit). The most common data format is 8 bits. An on-chip, dedicated, 8-bit Baud Rate Generator can be used to derive standard baud rate frequencies from the oscillator. The USART transmits and receives the LSb first. The transmitter and receiver are functionally independent but use the same data format and baud rate. The baud rate generator produces a clock, either x16 or x64 of the bit shift rate, depending on bit BRGH (TXSTA<2>). Parity is not supported by the hardware but can be implemented in software (and stored as the ninth data bit). Asynchronous mode is stopped during Sleep.

Asynchronous mode is selected by clearing bit SYNC (TXSTA<4>).

The USART Asynchronous module consists of the following important elements:

- Baud Rate Generator

- Sampling Circuit

- Asynchronous Transmitter

- Asynchronous Receiver

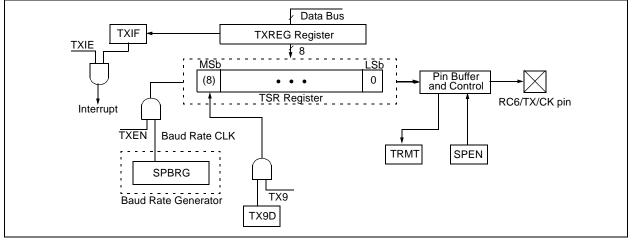

#### 10.2.1 USART ASYNCHRONOUS TRANSMITTER

The USART transmitter block diagram is shown in Figure 10-1. The heart of the transmitter is the Transmit (Serial) Shift Register (TSR). The shift register obtains its data from the Read/Write Transmit Buffer, TXREG. The TXREG register is loaded with data in software. The TSR register is not loaded until the Stop bit has been transmitted from the previous load. As soon as the Stop bit is transmitted, the TSR is loaded with new data from the TXREG register (if available). Once the TXREG register transfers the data to the TSR register (occurs in one TcY), the TXREG register is empty and flag bit, TXIF (PIR1<4>), is set. This interrupt can be

enabled/disabled by setting/clearing enable bit, TXIE (PIE1<4>). Flag bit TXIF will be set regardless of the state of enable bit TXIE and cannot be cleared in software. It will reset only when new data is loaded into the TXREG register. While flag bit TXIF indicates the status of the TXREG register, another bit, TRMT (TXSTA<1>), shows the status of the TSR register. Status bit TRMT is a read-only bit which is set when the TSR register is empty. No interrupt logic is tied to this bit so the user has to poll this bit in order to determine if the TSR register is empty.

- **Note 1:** The TSR register is not mapped in data memory so it is not available to the user.

- 2: Flag bit TXIF is set when enable bit TXEN is set. TXIF is cleared by loading TXREG.

Transmission is enabled by setting enable bit, TXEN (TXSTA<5>). The actual transmission will not occur until the TXREG register has been loaded with data and the Baud Rate Generator (BRG) has produced a shift clock (Figure 10-2). The transmission can also be started by first loading the TXREG register and then setting enable bit TXEN. Normally, when transmission is first started, the TSR register is empty. At that point, transfer to the TXREG register will result in an immediate transfer to TSR, resulting in an empty TXREG. A back-to-back transfer is thus possible (Figure 10-3). Clearing enable bit TXEN during a transmission will cause the transmission to be aborted and will reset the transmitter. As a result, the RC6/TX/CK pin will revert to high-impedance.

In order to select 9-bit transmission, transmit bit TX9 (TXSTA<6>) should be set and the ninth bit should be written to TX9D (TXSTA<0>). The ninth bit must be written before writing the 8-bit data to the TXREG register. This is because a data write to the TXREG register can result in an immediate transfer of the data to the TSR register (if the TSR is empty). In such a case, an incorrect ninth data bit may be loaded in the TSR register.

| Address                | Name   | Bit 7        | Bit 6         | Bit 5   | Bit 4     | Bit 3      | Bit 2  | Bit 1  | Bit 0  | Value on<br>POR | Value on<br>all other<br>Resets |

|------------------------|--------|--------------|---------------|---------|-----------|------------|--------|--------|--------|-----------------|---------------------------------|

| 9Ch                    | CMCON  | C2OUT        | C10UT         | C2INV   | C1INV     | CIS        | CM2    | CM1    | CM0    | 0000 0111       | 0000 0111                       |

| 9Dh                    | CVRCON | CVREN        | CVROE         | CVRR    | _         | CVR3       | CVR2   | CVR1   | CVR0   | 000- 0000       | 000- 0000                       |

| 0Bh, 8Bh,<br>10Bh,18Bh | INTCON | GIE/<br>GIEH | PEIE/<br>GIEL | TMR0IE  | INTIE     | RBIE       | TMR0IF | INTIF  | RBIF   | x000 000x       | 0000 000u                       |

| 0Dh                    | PIR2   | _            | CMIF          | _       | _         | BCLIF      | LVDIF  | TMR3IF | CCP2IF | -0 0000         | -0 0000                         |

| 8Dh                    | PIE2   | —            | CMIE          | —       | —         | BCLIE      | LVDIE  | TMR3IE | CCP2IE | -0 0000         | -0 0000                         |

| 05h                    | PORTA  | —            | —             | RA5     | RA4       | RA3        | RA2    | RA1    | RA0    | 0x 0000         | Ou 0000                         |

| 85h                    | TRISA  | _            | —             | PORTA D | ata Direc | tion Regis | ster   |        |        | 11 1111         | 11 1111                         |

#### TABLE 12-1: REGISTERS ASSOCIATED WITH COMPARATOR MODULE

**Legend:** x = unknown, u = unchanged, - = unimplemented, read as '0'. Shaded cells are unused by the comparator module.

#### 14.0 SPECIAL FEATURES OF THE CPU

All PIC16F87XA devices have a host of features intended to maximize system reliability, minimize cost through elimination of external components, provide power saving operating modes and offer code protection. These are:

- Oscillator Selection

- Reset

- Power-on Reset (POR)

- Power-up Timer (PWRT)

- Oscillator Start-up Timer (OST)

- Brown-out Reset (BOR)

- Interrupts

- Watchdog Timer (WDT)

- Sleep

- Code Protection

- ID Locations

- In-Circuit Serial Programming

- Low-Voltage In-Circuit Serial Programming

- In-Circuit Debugger

PIC16F87XA devices have a Watchdog Timer which can be shut-off only through configuration bits. It runs off its own RC oscillator for added reliability.

There are two timers that offer necessary delays on power-up. One is the Oscillator Start-up Timer (OST), intended to keep the chip in Reset until the crystal oscillator is stable. The other is the Power-up Timer (PWRT), which provides a fixed delay of 72 ms (nominal) on power-up only. It is designed to keep the part in Reset while the power supply stabilizes. With these two timers on-chip, most applications need no external Reset circuitry. Sleep mode is designed to offer a very low current power-down mode. The user can wake-up from Sleep through external Reset, Watchdog Timer wake-up or through an interrupt.

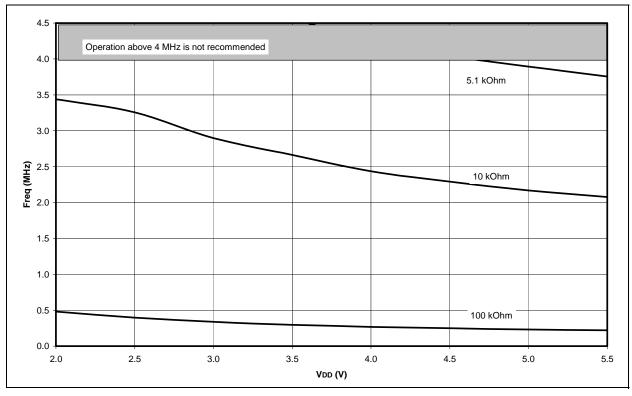

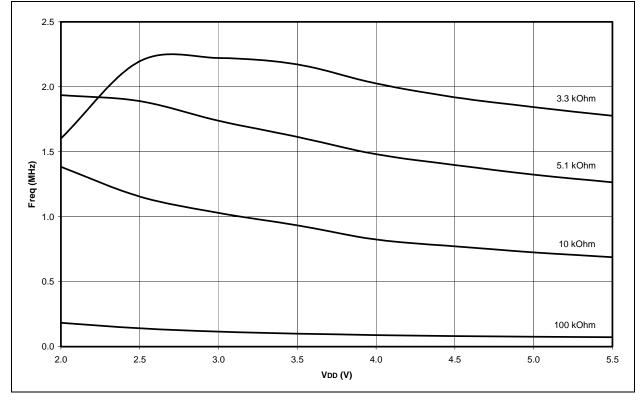

Several oscillator options are also made available to allow the part to fit the application. The RC oscillator option saves system cost while the LP crystal option saves power. A set of configuration bits is used to select various options.

Additional information on special features is available in the PIC<sup>®</sup> Mid-Range MCU Family Reference Manual (DS33023).

#### 14.1 Configuration Bits

The configuration bits can be programmed (read as '0'), or left unprogrammed (read as '1') to select various device configurations. The erased or unprogrammed value of the Configuration Word register is 3FFFh. These bits are mapped in program memory location 2007h.

It is important to note that address 2007h is beyond the user program memory space which can be accessed only during programming.

#### 14.2 Oscillator Configurations

#### 14.2.1 OSCILLATOR TYPES

The PIC16F87XA can be operated in four different oscillator modes. The user can program two configuration bits (FOsc1 and FOsc0) to select one of these four modes:

- LP Low-Power Crystal

- XT Crystal/Resonator

- HS High-Speed Crystal/Resonator

- RC Resistor/Capacitor

## 14.2.2 CRYSTAL OSCILLATOR/CERAMIC RESONATORS

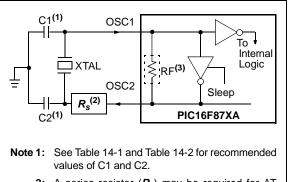

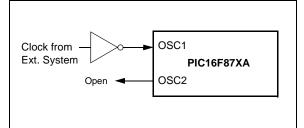

In XT, LP or HS modes, a crystal or ceramic resonator is connected to the OSC1/CLKI and OSC2/CLKO pins to establish oscillation (Figure 14-1). The PIC16F87XA oscillator design requires the use of a parallel cut crystal. Use of a series cut crystal may give a frequency out of the crystal manufacturer's specifications. When in XT, LP or HS modes, the device can have an external clock source to drive the OSC1/CLKI pin (Figure 14-2).

#### FIGURE 14-1: CRYSTAL/CERAMIC RESONATOR OPERATION (HS, XT OR LP OSC CONFIGURATION)

- A series resistor (*R<sub>s</sub>*) may be required for AT strip cut crystals.

- 3: RF varies with the crystal chosen.

#### FIGURE 14-2:

#### EXTERNAL CLOCK INPUT OPERATION (HS, XT OR LP OSC CONFIGURATION)

#### TABLE 14-1: CERAMIC RESONATORS

|      | Ranges Tested: |           |           |  |  |  |  |  |  |  |  |

|------|----------------|-----------|-----------|--|--|--|--|--|--|--|--|

| Mode |                |           |           |  |  |  |  |  |  |  |  |

| XT   | 455 kHz        | 68-100 pF | 68-100 pF |  |  |  |  |  |  |  |  |

|      | 2.0 MHz        | 15-68 pF  | 15-68 pF  |  |  |  |  |  |  |  |  |

|      | 4.0 MHz        | 15-68 pF  | 15-68 pF  |  |  |  |  |  |  |  |  |

| HS   | 8.0 MHz        | 10-68 pF  | 10-68 pF  |  |  |  |  |  |  |  |  |

|      | 16.0 MHz       | 10-22 pF  | 10-22 pF  |  |  |  |  |  |  |  |  |

**These values are for design guidance only.** See notes following Table 14-2.

| Resonators Used: |                                |             |  |  |  |  |  |  |

|------------------|--------------------------------|-------------|--|--|--|--|--|--|

| 2.0 MHz          | Murata Erie CSA2.00MG          | $\pm 0.5\%$ |  |  |  |  |  |  |

| 4.0 MHz          | $\pm 0.5\%$                    |             |  |  |  |  |  |  |

| 8.0 MHz          | Murata Erie CSA8.00MT          | $\pm 0.5\%$ |  |  |  |  |  |  |

| 16.0 MHz         | Murata Erie CSA16.00MX         | $\pm 0.5\%$ |  |  |  |  |  |  |

| All resonate     | ors used did not have built-in | capacitors. |  |  |  |  |  |  |

#### 14.3 Reset

The PIC16F87XA differentiates between various kinds of Reset:

- Power-on Reset (POR)

- MCLR Reset during normal operation

- MCLR Reset during Sleep

- WDT Reset (during normal operation)

- WDT Wake-up (during Sleep)

- Brown-out Reset (BOR)

Some registers are not affected in any Reset condition. Their status is unknown on POR and unchanged in any other Reset. Most other registers are reset to a "Reset state" on Power-on Reset (POR), on the MCLR and WDT Reset, on MCLR Reset during Sleep and Brownout Reset (BOR). They are not affected by a WDT wake-up which is viewed as the resumption of normal operation. The TO and PD bits are set or cleared differently in different Reset situations as indicated in Table 14-4. These bits are used in software to determine the nature of the Reset. See Table 14-6 for a full description of Reset states of all registers.

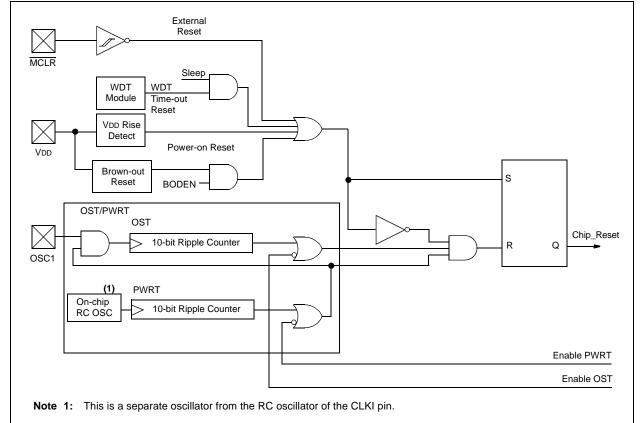

A simplified block diagram of the on-chip Reset circuit is shown in Figure 14-4.

#### FIGURE 14-4: SIMPLIFIED BLOCK DIAGRAM OF ON-CHIP RESET CIRCUIT

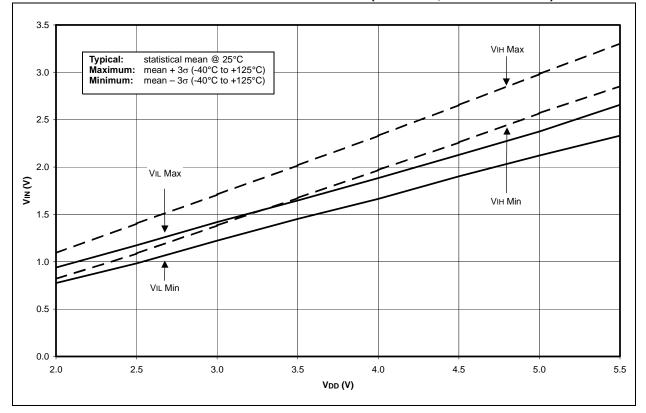

#### 17.1 DC Characteristics: PIC16F873A/874A/876A/877A (Industrial, Extended) PIC16LF873A/874A/876A/877A (Industrial)

| PIC16LF8<br>(Indus |                                                     | /876A/877A                                                       | Standard Operating Conditions (unless otherwise stated)Operating temperature $-40^{\circ}C \le TA \le +85^{\circ}C$ for industrial |                                                      |      |      |                                                        |  |  |

|--------------------|-----------------------------------------------------|------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------|------|------|--------------------------------------------------------|--|--|

|                    | PIC16F873A/874A/876A/877A<br>(Industrial, Extended) |                                                                  |                                                                                                                                    | $\begin{array}{llllllllllllllllllllllllllllllllllll$ |      |      |                                                        |  |  |

| Param<br>No.       | Symbol                                              | Characteristic/<br>Device                                        | Min Typ† Max Units Conditions                                                                                                      |                                                      |      |      | Conditions                                             |  |  |

|                    | Vdd                                                 | Supply Voltage                                                   |                                                                                                                                    |                                                      |      |      |                                                        |  |  |

| D001               |                                                     | 16LF87XA                                                         | 2.0                                                                                                                                | —                                                    | 5.5  | V    | All configurations<br>(DC to 10 MHz)                   |  |  |

| D001               |                                                     | 16F87XA                                                          | 4.0                                                                                                                                |                                                      | 5.5  | V    | All configurations                                     |  |  |