Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XF

| Product Status             | Active                                                                      |

|----------------------------|-----------------------------------------------------------------------------|

| Core Processor             | PIC                                                                         |

| Core Size                  | 8-Bit                                                                       |

| Speed                      | 10MHz                                                                       |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                           |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                       |

| Number of I/O              | 22                                                                          |

| Program Memory Size        | 7KB (4K x 14)                                                               |

| Program Memory Type        | FLASH                                                                       |

| EEPROM Size                | 128 x 8                                                                     |

| RAM Size                   | 192 x 8                                                                     |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 5.5V                                                                   |

| Data Converters            | A/D 5x10b                                                                   |

| Oscillator Type            | External                                                                    |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                           |

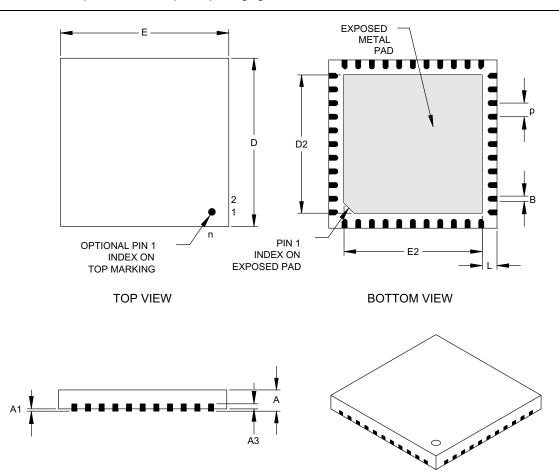

| Mounting Type              | Surface Mount                                                               |

| Package / Case             | 28-VQFN Exposed Pad                                                         |

| Supplier Device Package    | 28-QFN (6x6)                                                                |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16lf873at-i-ml |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| 1 1 4 1 | սու | 2-3: |  |

|---------|-----|------|--|

### PIC16F876A/877A REGISTER FILE MAP

| Indirect addr.(*)    | 00h         | Indirect addr.(*)             |           | Indirect addr.(*)   | 100h          | Indirect addr.(*)       | 10 |

|----------------------|-------------|-------------------------------|-----------|---------------------|---------------|-------------------------|----|

| TMR0                 | 00n<br>01h  | OPTION REG                    | 80h       | TMR0                | 100h          | OPTION_REG              | 18 |

| PCL                  | 01h<br>02h  |                               | 81h       | PCL                 | 10111<br>102h |                         | 18 |

|                      | 02n<br>03h  | PCL<br>STATUS                 | 82h       | STATUS              | 10211<br>103h | PCL<br>STATUS           | 18 |

| STATUS               | 03n<br>04h  |                               | 83h       | FSR                 | 103n<br>104h  |                         | 18 |

| FSR                  |             | FSR                           | 84h       | FSR                 | 1041<br>105h  | FSR                     | 18 |

| PORTA                | 05h<br>06h  | TRISA                         | 85h       | DODTD               | 105h          | TRISB                   | 18 |

| PORTB                |             | TRISB                         | 86h       | PORTB               | 106n<br>107h  | TRISB                   | 18 |

|                      | 07h         | TRISC<br>TRISD <sup>(1)</sup> | 87h       |                     | 10711<br>108h |                         | 18 |

| PORTD <sup>(1)</sup> | 08h         | TRISD <sup>(1)</sup>          | 88h       |                     | 109h          |                         | 18 |

| PORTE <sup>(1)</sup> | 09h         |                               | 89h       | PCLATH              | 1091<br>10Ah  | PCLATH                  | 18 |

| PCLATH               | 0Ah         | PCLATH                        | 8Ah       |                     | 10An<br>10Bh  | INTCON                  | 18 |

| INTCON               | 0Bh         | INTCON                        | 8Bh       | INTCON              | 10Bn<br>10Ch  | EECON1                  | 18 |

| PIR1                 | 0Ch         | PIE1                          | 8Ch       | EEDATA              |               |                         | 18 |

| PIR2                 | 0Dh         | PIE2                          | 8Dh       | EEADR               | 10Dh          | EECON2                  | 18 |

| TMR1L                | 0Eh         | PCON                          | 8Eh       | EEDATH              | 10Eh          | Reserved <sup>(2)</sup> | 18 |

| TMR1H                | 0Fh         |                               | 8Fh       | EEADRH              | 10Fh          | Reserved <sup>(2)</sup> | 18 |

| T1CON                | 10h         |                               | 90h       |                     | 110h          |                         | 19 |

| TMR2                 | 11h         | SSPCON2                       | 91h       |                     | 111h          |                         | 19 |

| T2CON                | 12h         | PR2                           | 92h       |                     | 112h          |                         | 19 |

| SSPBUF               | 13h         | SSPADD                        | 93h       |                     | 113h          |                         | 19 |

| SSPCON               | 14h         | SSPSTAT                       | 94h       |                     | 114h          |                         | 19 |

| CCPR1L               | 15h         |                               | 95h       |                     | 115h          |                         | 19 |

| CCPR1H               | 16h         |                               | 96h       | Conorol             | 116h          | Conorol                 | 19 |

| CCP1CON              | 17h         |                               | 97h       | General<br>Purpose  | 117h          | General<br>Purpose      | 19 |

| RCSTA                | 18h         | TXSTA                         | 98h       | Register            | 118h          | Register                | 19 |

| TXREG                | 19h         | SPBRG                         | 99h       | 16 Bytes            | 119h          | 16 Bytes                | 19 |

| RCREG                | 1Ah         |                               | 9Ah       |                     | 11Ah          |                         | 19 |

| CCPR2L               | 1Bh         |                               | 9Bh       |                     | 11Bh          |                         | 19 |

| CCPR2H               | 1Ch         | CMCON                         | 9Ch       |                     | 11Ch          |                         | 19 |

| CCP2CON              | 1Dh         | CVRCON                        | 9Dh       |                     | 11Dh          |                         | 19 |

| ADRESH               | 1Eh         | ADRESL                        | 9Eh       |                     | 11Eh          |                         | 19 |

| ADCON0               | 1Fh         | ADCON1                        | 9Fh       |                     | 11Fh          |                         | 19 |

|                      | 20h         |                               | A0h       |                     | 120h          |                         | 1A |

|                      |             | General                       |           | General             |               | General                 |    |

| General              |             | Purpose                       |           | Purpose             |               | Purpose                 |    |

| Purpose              |             | Register                      |           | Register            |               | Register                |    |

| Register             |             | 80 Bytes                      |           | 80 Bytes            |               | 80 Bytes                |    |

| 96 Bytes             |             |                               | EFh       |                     | 16Fh          |                         | 1E |

|                      |             | accesses                      | F0h       | 200005005           | 170h          | accesses                | 1F |

|                      |             | 70h-7Fh                       |           | accesses<br>70h-7Fh |               | 70h - 7Fh               |    |

| <b>_</b>             | 7Fh         |                               | FFh       |                     | 17Fh          |                         | 1F |

| Bank 0               |             | Bank 1                        |           | Bank 2              |               | Bank 3                  |    |

| Unimple              | mented d    | ata memory locati             | ons. read | <b>as</b> '0'.      |               |                         |    |

|                      | iysical reg | -                             |           |                     |               |                         |    |

## 2.2.2 SPECIAL FUNCTION REGISTERS

The Special Function Registers are registers used by the CPU and peripheral modules for controlling the desired operation of the device. These registers are implemented as static RAM. A list of these registers is given in Table 2-1. The Special Function Registers can be classified into two sets: core (CPU) and peripheral. Those registers associated with the core functions are described in detail in this section. Those related to the operation of the peripheral features are described in detail in the peripheral features section.

TABLE 2-1:SPECIAL FUNCTION REGISTER SUMMARY

| Address              | Name    | Bit 7                | Bit 6                                | Bit 5        | Bit 4           | Bit 3          | Bit 2            | Bit 1        | Bit 0         | Value on:<br>POR, BOR | Details<br>on page: |

|----------------------|---------|----------------------|--------------------------------------|--------------|-----------------|----------------|------------------|--------------|---------------|-----------------------|---------------------|

| Bank 0               |         |                      |                                      |              |                 |                |                  |              |               |                       |                     |

| 00h <sup>(3)</sup>   | INDF    | Addressing           | g this locatio                       | n uses cont  | ents of FSR t   | o address da   | ata memory (     | not a physic | cal register) | 0000 0000             | 31, 150             |

| 01h                  | TMR0    | Timer0 Mo            | ner0 Module Register                 |              |                 |                |                  |              |               |                       | 55, 150             |

| 02h <sup>(3)</sup>   | PCL     | Program C            | ounter (PC)                          | -            | 0000 0000       | 30, 150        |                  |              |               |                       |                     |

| 03h <sup>(3)</sup>   | STATUS  | IRP                  | RP1                                  | RP0          | TO              | PD             | Z                | DC           | С             | 0001 1xxx             | 22, 150             |

| 04h <sup>(3)</sup>   | FSR     | Indirect Da          | ta Memory                            | Address Po   | inter           |                |                  |              |               | xxxx xxxx             | 31, 150             |

| 05h                  | PORTA   | _                    |                                      | PORTA Da     | ata Latch whe   | en written: PO | ORTA pins w      | hen read     |               | 0x 0000               | 43, 150             |

| 06h                  | PORTB   | PORTB Da             | ata Latch wh                         | nen written: | PORTB pins      | when read      |                  |              |               | xxxx xxxx             | 45, 150             |

| 07h                  | PORTC   | PORTC Da             | ata Latch wh                         | nen written: | PORTC pins      | when read      |                  |              |               | xxxx xxxx             | 47, 150             |

| 08h <sup>(4)</sup>   | PORTD   | PORTD Da             | ata Latch wh                         | nen written: | PORTD pins      | when read      |                  |              |               | xxxx xxxx             | 48, 150             |

| 09h <sup>(4)</sup>   | PORTE   | _                    |                                      | —            | _               | _              | RE2              | RE1          | RE0           | xxx                   | 49, 150             |

| 0Ah <sup>(1,3)</sup> | PCLATH  | _                    | _                                    | _            | Write Buffer    | for the uppe   | er 5 bits of the | e Program C  | Counter       | 0 0000                | 30, 150             |

| 0Bh <sup>(3)</sup>   | INTCON  | GIE                  | PEIE                                 | TMR0IE       | INTE            | RBIE           | TMR0IF           | INTF         | RBIF          | 0000 000x             | 24, 150             |

| 0Ch                  | PIR1    | PSPIF <sup>(3)</sup> | ADIF                                 | RCIF         | TXIF            | SSPIF          | CCP1IF           | TMR2IF       | TMR1IF        | 0000 0000             | 26, 150             |

| 0Dh                  | PIR2    | _                    | CMIF                                 | —            | EEIF            | BCLIF          | —                | _            | CCP2IF        | -0-0 00               | 28, 150             |

| 0Eh                  | TMR1L   | Holding Re           | egister for th                       | e Least Sig  | nificant Byte   | of the 16-bit  | TMR1 Regis       | ter          |               | xxxx xxxx             | 60, 150             |

| 0Fh                  | TMR1H   | Holding Re           | egister for th                       | e Most Sigr  | nificant Byte c | of the 16-bit  | TMR1 Regist      | er           |               | xxxx xxxx             | 60, 150             |

| 10h                  | T1CON   | _                    | —                                    | T1CKPS1      | T1CKPS0         | T1OSCEN        | T1SYNC           | TMR1CS       | TMR10N        | 00 0000               | 57, 150             |

| 11h                  | TMR2    | Timer2 Mo            | dule Regist                          | er           |                 |                |                  |              |               | 0000 0000             | 62, 150             |

| 12h                  | T2CON   | _                    | TOUTPS3                              | TOUTPS2      | TOUTPS1         | TOUTPS0        | TMR2ON           | T2CKPS1      | T2CKPS0       | -000 0000             | 61, 150             |

| 13h                  | SSPBUF  | Synchrono            | us Serial Po                         | ort Receive  | Buffer/Transr   | nit Register   |                  |              |               | xxxx xxxx             | 79, 150             |

| 14h                  | SSPCON  | WCOL                 | SSPOV                                | SSPEN        | СКР             | SSPM3          | SSPM2            | SSPM1        | SSPM0         | 0000 0000             | 82, 82,<br>150      |

| 15h                  | CCPR1L  | Capture/Co           | ompare/PW                            | M Register   | 1 (LSB)         |                |                  |              |               | xxxx xxxx             | 63, 150             |

| 16h                  | CCPR1H  | Capture/Co           | ompare/PW                            | M Register   | 1 (MSB)         |                |                  |              |               | xxxx xxxx             | 63, 150             |

| 17h                  | CCP1CON | _                    | _                                    | CCP1X        | CCP1Y           | CCP1M3         | CCP1M2           | CCP1M1       | CCP1M0        | 00 0000               | 64, 150             |

| 18h                  | RCSTA   | SPEN                 | RX9                                  | SREN         | CREN            | ADDEN          | FERR             | OERR         | RX9D          | 0000 000x             | 112, 150            |

| 19h                  | TXREG   | USART Tra            | ansmit Data                          | Register     |                 |                |                  |              |               | 0000 0000             | 118, 150            |

| 1Ah                  | RCREG   | USART Re             | SART Receive Data Register           |              |                 |                |                  |              |               |                       | 118, 150            |

| 1Bh                  | CCPR2L  | Capture/C            | Capture/Compare/PWM Register 2 (LSB) |              |                 |                |                  |              |               |                       | 63, 150             |

| 1Ch                  | CCPR2H  | Capture/C            | Capture/Compare/PWM Register 2 (MSB) |              |                 |                |                  |              |               | xxxx xxxx             | 63, 150             |

| 1Dh                  | CCP2CON | _                    | _                                    | CCP2X        | CCP2Y           | CCP2M3         | CCP2M2           | CCP2M1       | CCP2M0        | 00 0000               | 64, 150             |

| 1Eh                  | ADRESH  | A/D Result           | Register H                           |              | xxxx xxxx       | 133, 150       |                  |              |               |                       |                     |

| 1Fh                  | ADCON0  | ADCS1                | ADCS0                                | CHS2         | CHS1            | CHS0           | GO/DONE          |              | ADON          | 0000 00-0             | 127, 150            |

**Legend:** x = unknown, u = unchanged, q = value depends on condition, - = unimplemented, read as '0', r = reserved. Shaded locations are unimplemented, read as '0'.

**Note 1:** The upper byte of the program counter is not directly accessible. PCLATH is a holding register for the PC<12:8>, whose contents are transferred to the upper byte of the program counter.

2: Bits PSPIE and PSPIF are reserved on PIC16F873A/876A devices; always maintain these bits clear.

**3:** These registers can be addressed from any bank.

4: PORTD, PORTE, TRISD and TRISE are not implemented on PIC16F873A/876A devices, read as '0'.

5: Bit 4 of EEADRH implemented only on the PIC16F876A/877A devices.

|                        | =       |                      |                                      | •           |           |         |                       |         |         | _             |      |       |                        |

|------------------------|---------|----------------------|--------------------------------------|-------------|-----------|---------|-----------------------|---------|---------|---------------|------|-------|------------------------|

| Address                | Name    | Bit 7                | Bit 6                                | Bit 5       | Bit 4     | Bit 3   | t 3 Bit 2 Bit 1 Bit 0 |         |         | Value<br>POR, |      | all o | ie on<br>other<br>sets |

| 0Bh,8Bh,<br>10Bh, 18Bh | INTCON  | GIE                  | PEIE                                 | TMR0IE      | INTE      | RBIE    | TMR0IF                | INTF    | RBIF    | 0000          | 000x | 0000  | 000u                   |

| 0Ch                    | PIR1    | PSPIF <sup>(1)</sup> | ADIF                                 | RCIF        | TXIF      | SSPIF   | CCP1IF                | TMR2IF  | TMR1IF  | 0000          | 0000 | 0000  | 0000                   |

| 0Dh                    | PIR2    | _                    | _                                    | _           | _         | _       | _                     | _       | CCP2IF  |               | 0    |       | 0                      |

| 8Ch                    | PIE1    | PSPIE <sup>(1)</sup> | ADIE                                 | RCIE        | TXIE      | SSPIE   | CCP1IE                | TMR2IE  | TMR1IE  | 0000          | 0000 | 0000  | 0000                   |

| 8Dh                    | PIE2    | —                    | —                                    | _           | —         | _       | —                     | —       | CCP2IE  |               | 0    |       | 0                      |

| 87h                    | TRISC   | PORTC D              | Data Directio                        | n Register  |           |         |                       |         |         | 1111          | 1111 | 1111  | 1111                   |

| 11h                    | TMR2    | Timer2 M             | odule's Reg                          | ister       |           |         |                       |         |         | 0000          | 0000 | 0000  | 0000                   |

| 92h                    | PR2     | Timer2 M             | odule's Peri                         | od Register |           |         |                       |         |         | 1111          | 1111 | 1111  | 1111                   |

| 12h                    | T2CON   | _                    | TOUTPS3                              | TOUTPS2     | TOUTPS1   | TOUTPS0 | TMR2ON                | T2CKPS1 | T2CKPS0 | -000          | 0000 | -000  | 0000                   |

| 15h                    | CCPR1L  | Capture/C            | Compare/PV                           | VM Registe  | r 1 (LSB) |         |                       |         |         | xxxx          | xxxx | uuuu  | uuuu                   |

| 16h                    | CCPR1H  | Capture/C            | Compare/PV                           | VM Registe  | r 1 (MSB) |         |                       |         |         | xxxx          | xxxx | uuuu  | uuuu                   |

| 17h                    | CCP1CON | _                    | _                                    | CCP1X       | CCP1Y     | CCP1M3  | CCP1M2                | CCP1M1  | CCP1M0  | 00            | 0000 | 00    | 0000                   |

| 1Bh                    | CCPR2L  | Capture/C            | Capture/Compare/PWM Register 2 (LSB) |             |           |         |                       |         |         |               |      | uuuu  | uuuu                   |

| 1Ch                    | CCPR2H  | Capture/C            | Capture/Compare/PWM Register 2 (MSB) |             |           |         |                       |         |         | xxxx          | xxxx | uuuu  | uuuu                   |

| 1Dh                    | CCP2CON | _                    | —                                    | CCP2X       | CCP2Y     | CCP2M3  | CCP2M2                | CCP2M1  | CCP2M0  | 00            | 0000 | 00    | 0000                   |

TABLE 8-5: REGISTERS ASSOCIATED WITH PWM AND TIMER2

Legend: x = unknown, u = unchanged, - = unimplemented, read as '0'. Shaded cells are not used by PWM and Timer2.

Note 1: Bits PSPIE and PSPIF are reserved on 28-pin devices; always maintain these bits clear.

| ER 9-2: | SSPCON                                           | SSPCON1: MSSP CONTROL REGISTER 1 (SPI MODE) (ADDRESS 14h)                       |                                                               |                                                |                             |               |               |               |  |  |  |  |  |

|---------|--------------------------------------------------|---------------------------------------------------------------------------------|---------------------------------------------------------------|------------------------------------------------|-----------------------------|---------------|---------------|---------------|--|--|--|--|--|

|         | R/W-0                                            | R/W-0                                                                           | R/W-0                                                         | R/W-0                                          | R/W-0                       | R/W-0         | R/W-0         | R/W-0         |  |  |  |  |  |

|         | WCOL                                             | SSPOV                                                                           | SSPEN                                                         | CKP                                            | SSPM3                       | SSPM2         | SSPM1         | SSPM0         |  |  |  |  |  |

|         | bit 7 bit 0                                      |                                                                                 |                                                               |                                                |                             |               |               |               |  |  |  |  |  |

| bit 7   |                                                  | /rite Collision                                                                 | -                                                             |                                                |                             |               |               |               |  |  |  |  |  |

|         |                                                  | SSPBUF reg<br>ed in software<br>ollision                                        |                                                               | en while it i                                  | s still transm              | nitting the p | revious wor   | d. (Must be   |  |  |  |  |  |

| bit 6   | SSPOV: R                                         | Receive Over                                                                    | flow Indicato                                                 | or bit                                         |                             |               |               |               |  |  |  |  |  |

|         | <u>SPI Slave</u>                                 | mode:                                                                           |                                                               |                                                |                             |               |               |               |  |  |  |  |  |

|         | of ove<br>must<br>cleare                         | v byte is rece<br>erflow, the da<br>read the SSI<br>ed in software              | ata in SSPSF<br>PBUF, even                                    | R is lost. Ov                                  | verflow can o               | only occur in | Slave mod     | e. The user   |  |  |  |  |  |

|         | 0 = No ov                                        |                                                                                 |                                                               |                                                |                             |               |               |               |  |  |  |  |  |

|         | Note:                                            |                                                                                 |                                                               |                                                | t is not set<br>to the SSPE |               |               | eption (and   |  |  |  |  |  |

| bit 5   | SSPEN: S                                         | Synchronous                                                                     | Serial Port E                                                 | Enable bit                                     |                             |               |               |               |  |  |  |  |  |

|         |                                                  | es serial port<br>les serial por                                                |                                                               |                                                |                             |               | ial port pins |               |  |  |  |  |  |

|         | Note:                                            | When enal                                                                       | oled, these p                                                 | oins must be                                   | e properly co               | nfigured as   | input or out  | put.          |  |  |  |  |  |

| bit 4   | CKP: Cloo                                        | ck Polarity Se                                                                  | elect bit                                                     |                                                |                             |               |               |               |  |  |  |  |  |

|         |                                                  | ate for clock<br>ate for clock                                                  | •                                                             |                                                |                             |               |               |               |  |  |  |  |  |

| bit 3-0 | SSPM3:S                                          | SPM0: Sync                                                                      | hronous Ser                                                   | ial Port Mod                                   | de Select bits              | 5             |               |               |  |  |  |  |  |

|         | 0100 = SF<br>0011 = SF<br>0010 = SF<br>0001 = SF | PI Slave mod<br>PI Slave mod<br>PI Master mod<br>PI Master mod<br>PI Master mod | le, clock = S<br>ode, clock =<br>ode, clock =<br>ode, clock = | CK pin. SS<br>TMR2 outpu<br>Fosc/64<br>Fosc/16 | pin control e               |               | can be usec   | l as I/O pin. |  |  |  |  |  |

|         |                                                  | PI Master mo                                                                    |                                                               |                                                |                             |               |               |               |  |  |  |  |  |

|         | Note:                                            | Bit combin<br>I <sup>2</sup> C mode o                                           |                                                               | becifically lis                                | sted here are               | either rese   | rved or imp   | lemented in   |  |  |  |  |  |

|         |                                                  |                                                                                 |                                                               |                                                |                             |               |               |               |  |  |  |  |  |

|         | I a manual.                                      |                                                                                 |                                                               |                                                |                             |               |               |               |  |  |  |  |  |

| Legend:            |                  |                      |                    |

|--------------------|------------------|----------------------|--------------------|

| R = Readable bit   | W = Writable bit | U = Unimplemented    | bit, read as '0'   |

| - n = Value at POR | '1' = Bit is set | '0' = Bit is cleared | x = Bit is unknown |

# REGISTER 9-2: SSPCON1: MSSP CONTROL REGISTER 1 (SPI MODE) (ADDRESS 14h)

| BAUD        | F       | osc = 20 M | IHz                         | F       | osc = 16 N | IHz                         | Fosc = 10 MHz |            |                             |  |

|-------------|---------|------------|-----------------------------|---------|------------|-----------------------------|---------------|------------|-----------------------------|--|

| RATE<br>(K) | KBAUD   | %<br>ERROR | SPBRG<br>value<br>(decimal) | KBAUD   | %<br>ERROR | SPBRG<br>value<br>(decimal) | KBAUD         | %<br>ERROR | SPBRG<br>value<br>(decimal) |  |

| 0.3         | -       | -          | -                           | -       | -          | -                           | -             | -          | -                           |  |

| 1.2         | 1.221   | 1.75       | 255                         | 1.202   | 0.17       | 207                         | 1.202         | 0.17       | 129                         |  |

| 2.4         | 2.404   | 0.17       | 129                         | 2.404   | 0.17       | 103                         | 2.404         | 0.17       | 64                          |  |

| 9.6         | 9.766   | 1.73       | 31                          | 9.615   | 0.16       | 25                          | 9.766         | 1.73       | 15                          |  |

| 19.2        | 19.531  | 1.72       | 15                          | 19.231  | 0.16       | 12                          | 19.531        | 1.72       | 7                           |  |

| 28.8        | 31.250  | 8.51       | 9                           | 27.778  | 3.55       | 8                           | 31.250        | 8.51       | 4                           |  |

| 33.6        | 34.722  | 3.34       | 8                           | 35.714  | 6.29       | 6                           | 31.250        | 6.99       | 4                           |  |

| 57.6        | 62.500  | 8.51       | 4                           | 62.500  | 8.51       | 3                           | 52.083        | 9.58       | 2                           |  |

| HIGH        | 1.221   | -          | 255                         | 0.977   | -          | 255                         | 0.610         | -          | 255                         |  |

| LOW         | 312.500 | -          | 0                           | 250.000 | -          | 0                           | 156.250       | -          | 0                           |  |

# TABLE 10-3: BAUD RATES FOR ASYNCHRONOUS MODE (BRGH = 0)

| BAUD        |        | Fosc = 4 M | Hz                          | Fosc = 3.6864 MHz |            |                             |  |  |

|-------------|--------|------------|-----------------------------|-------------------|------------|-----------------------------|--|--|

| RATE<br>(K) | KBAUD  | %<br>ERROR | SPBRG<br>value<br>(decimal) | KBAUD             | %<br>ERROR | SPBRG<br>value<br>(decimal) |  |  |

| 0.3         | 0.300  | 0          | 207                         | 0.3               | 0          | 191                         |  |  |

| 1.2         | 1.202  | 0.17       | 51                          | 1.2               | 0          | 47                          |  |  |

| 2.4         | 2.404  | 0.17       | 25                          | 2.4               | 0          | 23                          |  |  |

| 9.6         | 8.929  | 6.99       | 6                           | 9.6               | 0          | 5                           |  |  |

| 19.2        | 20.833 | 8.51       | 2                           | 19.2              | 0          | 2                           |  |  |

| 28.8        | 31.250 | 8.51       | 1                           | 28.8              | 0          | 1                           |  |  |

| 33.6        | -      | -          | -                           | -                 | -          | -                           |  |  |

| 57.6        | 62.500 | 8.51       | 0                           | 57.6              | 0          | 0                           |  |  |

| HIGH        | 0.244  | -          | 255                         | 0.225             | -          | 255                         |  |  |

| LOW         | 62.500 | -          | 0                           | 57.6              | -          | 0                           |  |  |

# TABLE 10-4: BAUD RATES FOR ASYNCHRONOUS MODE (BRGH = 1)

| BAUD        | F        | osc = 20 M | Hz                          | F        | osc = 16 M | Hz                          | F       | osc = 10 M | Hz                          |

|-------------|----------|------------|-----------------------------|----------|------------|-----------------------------|---------|------------|-----------------------------|

| RATE<br>(K) | KBAUD    | %<br>ERROR | SPBRG<br>value<br>(decimal) | KBAUD    | %<br>ERROR | SPBRG<br>value<br>(decimal) | KBAUD   | %<br>ERROR | SPBRG<br>value<br>(decimal) |

| 0.3         | -        | -          | -                           | -        | -          | -                           | -       | -          | -                           |

| 1.2         | -        | -          | -                           | -        | -          | -                           | -       | -          | -                           |

| 2.4         | -        | -          | -                           | -        | -          | -                           | 2.441   | 1.71       | 255                         |

| 9.6         | 9.615    | 0.16       | 129                         | 9.615    | 0.16       | 103                         | 9.615   | 0.16       | 64                          |

| 19.2        | 19.231   | 0.16       | 64                          | 19.231   | 0.16       | 51                          | 19.531  | 1.72       | 31                          |

| 28.8        | 29.070   | 0.94       | 42                          | 29.412   | 2.13       | 33                          | 28.409  | 1.36       | 21                          |

| 33.6        | 33.784   | 0.55       | 36                          | 33.333   | 0.79       | 29                          | 32.895  | 2.10       | 18                          |

| 57.6        | 59.524   | 3.34       | 20                          | 58.824   | 2.13       | 16                          | 56.818  | 1.36       | 10                          |

| HIGH        | 4.883    | -          | 255                         | 3.906    | -          | 255                         | 2.441   | -          | 255                         |

| LOW         | 1250.000 | -          | 0                           | 1000.000 |            | 0                           | 625.000 | -          | 0                           |

| BAUD        | F       | osc = 4 MH | łz                          | Fos   | c = 3.6864 | MHz                         |

|-------------|---------|------------|-----------------------------|-------|------------|-----------------------------|

| RATE<br>(K) | KBAUD   | %<br>ERROR | SPBRG<br>value<br>(decimal) | KBAUD | %<br>ERROR | SPBRG<br>value<br>(decimal) |

| 0.3         | -       | -          | -                           | -     | -          | -                           |

| 1.2         | 1.202   | 0.17       | 207                         | 1.2   | 0          | 191                         |

| 2.4         | 2.404   | 0.17       | 103                         | 2.4   | 0          | 95                          |

| 9.6         | 9.615   | 0.16       | 25                          | 9.6   | 0          | 23                          |

| 19.2        | 19.231  | 0.16       | 12                          | 19.2  | 0          | 11                          |

| 28.8        | 27.798  | 3.55       | 8                           | 28.8  | 0          | 7                           |

| 33.6        | 35.714  | 6.29       | 6                           | 32.9  | 2.04       | 6                           |

| 57.6        | 62.500  | 8.51       | 3                           | 57.6  | 0          | 3                           |

| HIGH        | 0.977   | -          | 255                         | 0.9   | -          | 255                         |

| LOW         | 250.000 | -          | 0                           | 230.4 | -          | 0                           |

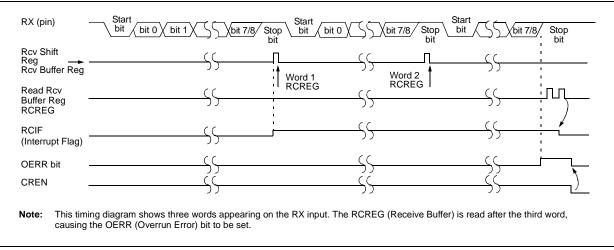

When setting up an Asynchronous Reception, follow these steps:

- Initialize the SPBRG register for the appropriate baud rate. If a high-speed baud rate is desired, set bit BRGH (Section 10.1 "USART Baud Rate Generator (BRG)").

- 2. Enable the asynchronous serial port by clearing bit SYNC and setting bit SPEN.

- 3. If interrupts are desired, then set enable bit RCIE.

- 4. If 9-bit reception is desired, then set bit RX9.

- 5. Enable the reception by setting bit CREN.

- Flag bit RCIF will be set when reception is complete and an interrupt will be generated if enable bit RCIE is set.

- 7. Read the RCSTA register to get the ninth bit (if enabled) and determine if any error occurred during reception.

- 8. Read the 8-bit received data by reading the RCREG register.

- 9. If any error occurred, clear the error by clearing enable bit CREN.

- 10. If using interrupts, ensure that GIE and PEIE (bits 7 and 6) of the INTCON register are set.

| Address                | Name   | Bit 7                | Bit 6                        | Bit 5  | Bit 4 | Bit 3 | Bit 2  | Bit 1  | Bit 0  | Value on:<br>POR, BOR | Value on<br>all other<br>Resets |

|------------------------|--------|----------------------|------------------------------|--------|-------|-------|--------|--------|--------|-----------------------|---------------------------------|

| 0Bh, 8Bh,<br>10Bh,18Bh | INTCON | GIE                  | PEIE                         | TMR0IE | INTE  | RBIE  | TMR0IF | INTF   | R0IF   | 0000 000x             | 0000 000u                       |

| 0Ch                    | PIR1   | PSPIF <sup>(1)</sup> | ADIF                         | RCIF   | TXIF  | SSPIF | CCP1IF | TMR2IF | TMR1IF | 0000 0000             | 0000 0000                       |

| 18h                    | RCSTA  | SPEN                 | RX9                          | SREN   | CREN  | —     | FERR   | OERR   | RX9D   | x00- 0000             | 0000 -00x                       |

| 1Ah                    | RCREG  | USART R              | eceive Reg                   | jister |       |       |        |        |        | 0000 0000             | 0000 0000                       |

| 8Ch                    | PIE1   | PSPIE <sup>(1)</sup> | ADIE                         | RCIE   | TXIE  | SSPIE | CCP1IE | TMR2IE | TMR1IE | 0000 0000             | 0000 0000                       |

| 98h                    | TXSTA  | CSRC                 | TX9                          | TXEN   | SYNC  | —     | BRGH   | TRMT   | TX9D   | 0000 -010             | 0000 -010                       |

| 99h                    | SPBRG  | Baud Rate            | Baud Rate Generator Register |        |       |       |        |        |        | 0000 0000             | 0000 0000                       |

#### TABLE 10-6: REGISTERS ASSOCIATED WITH ASYNCHRONOUS RECEPTION

Legend: x = unknown, - = unimplemented locations read as '0'. Shaded cells are not used for asynchronous reception.

Note 1: Bits PSPIE and PSPIF are reserved on 28-pin devices; always maintain these bits clear.

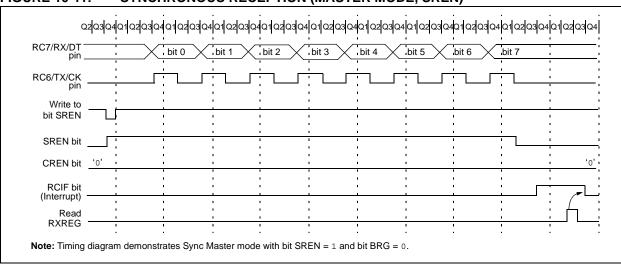

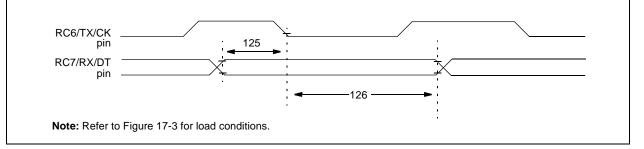

## FIGURE 10-11: SYNCHRONOUS RECEPTION (MASTER MODE, SREN)

# 10.4 USART Synchronous Slave Mode

Synchronous Slave mode differs from the Master mode in the fact that the shift clock is supplied externally at the RC6/TX/CK pin (instead of being supplied internally in Master mode). This allows the device to transfer or receive data while in Sleep mode. Slave mode is entered by clearing bit, CSRC (TXSTA<7>).

#### 10.4.1 USART SYNCHRONOUS SLAVE TRANSMIT

The operation of the Synchronous Master and Slave modes is identical, except in the case of the Sleep mode.

If two words are written to the TXREG and then the SLEEP instruction is executed, the following will occur:

- a) The first word will immediately transfer to the TSR register and transmit.

- b) The second word will remain in TXREG register.

- c) Flag bit TXIF will not be set.

- d) When the first word has been shifted out of TSR, the TXREG register will transfer the second word to the TSR and flag bit TXIF will now be set.

- e) If enable bit TXIE is set, the interrupt will wake the chip from Sleep and if the global interrupt is enabled, the program will branch to the interrupt vector (0004h).

When setting up a Synchronous Slave Transmission, follow these steps:

- 1. Enable the synchronous slave serial port by setting bits SYNC and SPEN and clearing bit CSRC.

- 2. Clear bits CREN and SREN.

- 3. If interrupts are desired, then set enable bit TXIE.

- 4. If 9-bit transmission is desired, then set bit TX9.

- 5. Enable the transmission by setting enable bit TXEN.

- 6. If 9-bit transmission is selected, the ninth bit should be loaded in bit TX9D.

- 7. Start transmission by loading data to the TXREG register.

- 8. If using interrupts, ensure that GIE and PEIE (bits 7 and 6) of the INTCON register are set.

bit 0

# **13.0 COMPARATOR VOLTAGE REFERENCE MODULE**

The Comparator Voltage Reference Generator is a 16-tap resistor ladder network that provides a fixed voltage reference when the comparators are in mode '110'. A programmable register controls the function of the reference generator. Register 13-1 lists the bit functions of the CVRCON register.

As shown in Figure 13-1, the resistor ladder is segmented to provide two ranges of CVREF values and has a power-down function to conserve power when the reference is not being used. The comparator reference supply voltage (also referred to as CVRSRC) comes directly from VDD. It should be noted, however, that the voltage at the top of the ladder is CVRSRC - VSAT, where VSAT is the saturation voltage of the power switch transistor. This reference will only be as accurate as the values of CVRSRC and VSAT.

The output of the reference generator may be connected to the RA2/AN2/VREF-/CVREF pin. This can be used as a simple D/A function by the user if a very highimpedance load is used. The primary purpose of this function is to provide a test path for testing the reference generator function.

|       | R/W-0     | R/W-0        | R/W-0       | U-0         | R/W-0 | R/W-0 | R/W-0 | R/W-0 |

|-------|-----------|--------------|-------------|-------------|-------|-------|-------|-------|

|       | CVREN     | CVROE        | CVRR        | —           | CVR3  | CVR2  | CVR1  | CVR0  |

|       | bit 7     |              |             |             |       |       |       | bit ( |

|       |           |              |             |             |       |       |       |       |

| bit 7 | CVREN: C  | omparator V  | oltage Refe | rence Enabl | e bit |       |       |       |

|       | 1 = CVREF | circuit powe | ered on     |             |       |       |       |       |

## REGISTER 13-1: CVRCON CONTROL REGISTER (ADDRESS 9Dh)

|         | CVREN. Comparator voltage Reference Enable bit                                                         |

|---------|--------------------------------------------------------------------------------------------------------|

|         | 1 = CVREF circuit powered on                                                                           |

|         | 0 = CVREF circuit powered down                                                                         |

| hit C   | · · · · · · · · · · · · · · · · · · ·                                                                  |

| bit 6   | CVROE: Comparator VREF Output Enable bit                                                               |

|         | 1 = CVREF voltage level is output on RA2/AN2/VREF-/CVREF pin                                           |

|         | 0 = CVREF voltage level is disconnected from RA2/AN2/VREF-/CVREF pin                                   |

| bit 5   | CVRR: Comparator VREF Range Selection bit                                                              |

|         | 1 = 0 to 0.75 CVRSRC, with CVRSRC/24 step size                                                         |

|         | 0 = 0.25 CVRSRC to 0.75 CVRSRC, with CVRSRC/32 step size                                               |

| L:L 4   |                                                                                                        |

| bit 4   | Unimplemented: Read as '0'                                                                             |

| bit 3-0 | <b>CVR3:CVR0:</b> Comparator VREF Value Selection bits $0 \le VR3:VR0 \le 15$                          |

|         | When $CVRR = 1$ :                                                                                      |

|         | $\overline{\text{CVREF}} = (\text{VR} < 3:0 > / 24) \bullet (\text{CVRSRC})$                           |

|         | When CVRR = 0:                                                                                         |

|         | $\overline{\text{CVREF}} = 1/4 \bullet (\text{CVRSRC}) + (\text{VR3:VR0/ 32}) \bullet (\text{CVRSRC})$ |

|         |                                                                                                        |

|         |                                                                                                        |

| Legend:           |                  |                      |                    |

|-------------------|------------------|----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented    | bit, read as '0'   |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared | x = Bit is unknown |

| TABLE 14-0: | ABLE 14-6: INITIALIZATION CONDITIONS FOR ALL REGISTERS (CONTINUED) |         |     |                                    |                           |                                 |           |  |

|-------------|--------------------------------------------------------------------|---------|-----|------------------------------------|---------------------------|---------------------------------|-----------|--|

| Register    |                                                                    | Devices |     | Power-on Reset,<br>Brown-out Reset | MCLR Resets,<br>WDT Reset | Wake-up via WDT or<br>Interrupt |           |  |

| TRISD       | 73A                                                                | 74A     | 76A | 77A                                | 1111 1111                 | 1111 1111                       | uuuu uuuu |  |

| TRISE       | 73A                                                                | 74A     | 76A | 77A                                | 0000 -111                 | 0000 -111                       | uuuu -uuu |  |

| PIE1        | 73A                                                                | 74A     | 76A | 77A                                | r000 0000                 | r000 0000                       | ruuu uuuu |  |

| FICI        | 73A                                                                | 74A     | 76A | 77A                                | 0000 0000                 | 0000 0000                       | սսսս սսսս |  |

| PIE2        | 73A                                                                | 74A     | 76A | 77A                                | -0-0 00                   | -0-0 00                         | -u-u uu   |  |

| PCON        | 73A                                                                | 74A     | 76A | 77A                                | dd                        | uu                              | uu        |  |

| SSPCON2     | 73A                                                                | 74A     | 76A | 77A                                | 0000 0000                 | 0000 0000                       | uuuu uuuu |  |

| PR2         | 73A                                                                | 74A     | 76A | 77A                                | 1111 1111                 | 1111 1111                       | 1111 1111 |  |

| SSPADD      | 73A                                                                | 74A     | 76A | 77A                                | 0000 0000                 | 0000 0000                       | uuuu uuuu |  |

| SSPSTAT     | 73A                                                                | 74A     | 76A | 77A                                | 00 0000                   | 00 0000                         | uu uuuu   |  |

| TXSTA       | 73A                                                                | 74A     | 76A | 77A                                | 0000 -010                 | 0000 -010                       | uuuu -uuu |  |

| SPBRG       | 73A                                                                | 74A     | 76A | 77A                                | 0000 0000                 | 0000 0000                       | uuuu uuuu |  |

| CMCON       | 73A                                                                | 974     | 76A | 77A                                | 0000 0111                 | 0000 0111                       | uuuu uuuu |  |

| CVRCON      | 73A                                                                | 74A     | 76A | 77A                                | 000- 0000                 | 000- 0000                       | uuu- uuuu |  |

| ADRESL      | 73A                                                                | 74A     | 76A | 77A                                | XXXX XXXX                 | սսսս սսսս                       | uuuu uuuu |  |

| ADCON1      | 73A                                                                | 74A     | 76A | 77A                                | 00 0000                   | 00 0000                         | uu uuuu   |  |

| EEDATA      | 73A                                                                | 74A     | 76A | 77A                                | XXXX XXXX                 | uuuu uuuu                       | uuuu uuuu |  |

| EEADR       | 73A                                                                | 74A     | 76A | 77A                                | XXXX XXXX                 | uuuu uuuu                       | uuuu uuuu |  |

| EEDATH      | 73A                                                                | 74A     | 76A | 77A                                | XXXX XXXX                 | սսսս սսսս                       | uuuu uuuu |  |

| EEADRH      | 73A                                                                | 74A     | 76A | 77A                                | xxxx xxxx                 | սսսս սսսս                       | uuuu uuuu |  |

| EECON1      | 73A                                                                | 74A     | 76A | 77A                                | x x000                    | u u000                          | u uuuu    |  |

| EECON2      | 73A                                                                | 74A     | 76A | 77A                                |                           |                                 |           |  |

**Legend:** u = unchanged, x = unknown, - = unimplemented bit, read as '0', q = value depends on condition, r = reserved, maintain clear. Shaded cells indicate conditions do not apply for the designated device.

Note 1: One or more bits in INTCON, PIR1 and/or PIR2 will be affected (to cause wake-up).

**2:** When the wake-up is due to an interrupt and the GIE bit is set, the PC is loaded with the interrupt vector (0004h).

3: See Table 14-5 for Reset value for specific condition.

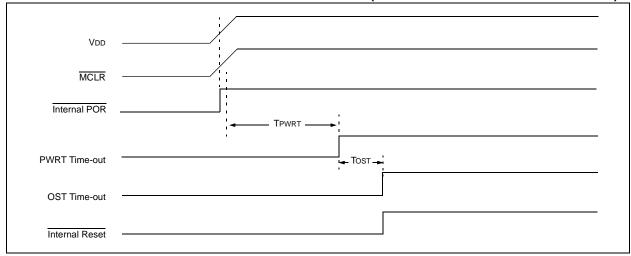

### FIGURE 14-6: TIME-OUT SEQUENCE ON POWER-UP (MCLR TIED TO VDD VIA RC NETWORK)

© 2001-2013 Microchip Technology Inc.

# 15.0 INSTRUCTION SET SUMMARY

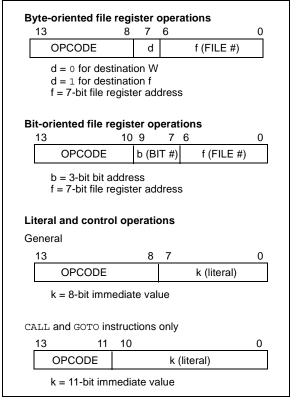

The PIC16 instruction set is highly orthogonal and is comprised of three basic categories:

- Byte-oriented operations

- Bit-oriented operations

- Literal and control operations

Each PIC16 instruction is a 14-bit word divided into an **opcode** which specifies the instruction type and one or more **operands** which further specify the operation of the instruction. The formats for each of the categories is presented in Figure 15-1, while the various opcode fields are summarized in Table 15-1.

Table 15-2 lists the instructions recognized by the MPASM<sup>™</sup> Assembler. A complete description of each instruction is also available in the PIC<sup>®</sup> Mid-Range MCU Family Reference Manual (DS33023).

For **byte-oriented** instructions, 'f' represents a file register designator and 'd' represents a destination designator. The file register designator specifies which file register is to be used by the instruction.

The destination designator specifies where the result of the operation is to be placed. If 'd' is zero, the result is placed in the W register. If 'd' is one, the result is placed in the file register specified in the instruction.

For **bit-oriented** instructions, 'b' represents a bit field designator which selects the bit affected by the operation, while 'f' represents the address of the file in which the bit is located.

For **literal and control** operations, 'k' represents an eight or eleven-bit constant or literal value

One instruction cycle consists of four oscillator periods; for an oscillator frequency of 4 MHz, this gives a normal instruction execution time of 1  $\mu$ s. All instructions are executed within a single instruction cycle, unless a conditional test is true, or the program counter is changed as a result of an instruction. When this occurs, the execution takes two instruction cycles with the second cycle executed as a NOP.

| Note: | To maintain upward compatibility with  |

|-------|----------------------------------------|

|       | future PIC16F87XA products, do not use |

|       | the OPTION and TRIS instructions.      |

All instruction examples use the format ' $0 \times hh$ ' to represent a hexadecimal number, where 'h' signifies a hexadecimal digit.

## 15.1 READ-MODIFY-WRITE OPERATIONS

Any instruction that specifies a file register as part of the instruction performs a Read-Modify-Write (R-M-W) operation. The register is read, the data is modified, and the result is stored according to either the instruction or the destination designator 'd'. A read operation is performed on a register even if the instruction writes to that register. For example, a "CLRF PORTB" instruction will read PORTB, clear all the data bits, then write the result back to PORTB. This example would have the unintended result that the condition that sets the RBIF flag would be cleared.

# TABLE 15-1: OPCODE FIELD DESCRIPTIONS

| Field | Description                                                                                                                                                                       |

|-------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| f     | Register file address (0x00 to 0x7F)                                                                                                                                              |

| W     | Working register (accumulator)                                                                                                                                                    |

| b     | Bit address within an 8-bit file register                                                                                                                                         |

| k     | Literal field, constant data or label                                                                                                                                             |

| х     | Don't care location (= $0$ or 1).<br>The assembler will generate code with x = $0$ .<br>It is the recommended form of use for<br>compatibility with all Microchip software tools. |

| d     | Destination select; $d = 0$ : store result in W,<br>d = 1: store result in file register f.<br>Default is $d = 1$ .                                                               |

| PC    | Program Counter                                                                                                                                                                   |

| ТО    | Time-out bit                                                                                                                                                                      |

| PD    | Power-down bit                                                                                                                                                                    |

# FIGURE 15-1: GENERAL FORMAT FOR INSTRUCTIONS

# 16.0 DEVELOPMENT SUPPORT

The PIC<sup>®</sup> microcontrollers are supported with a full range of hardware and software development tools:

- Integrated Development Environment

- MPLAB<sup>®</sup> IDE Software

- Assemblers/Compilers/Linkers

- MPASM<sup>™</sup> Assembler

- MPLAB C17 and MPLAB C18 C Compilers

- MPLINK<sup>™</sup> Object Linker/

- MPLIB<sup>™</sup> Object Librarian

- MPLAB C30 C Compiler

- MPLAB ASM30 Assembler/Linker/Library

- Simulators

- MPLAB SIM Software Simulator

- MPLAB dsPIC30 Software Simulator

- Emulators

- MPLAB ICE 2000 In-Circuit Emulator

- MPLAB ICE 4000 In-Circuit Emulator

- In-Circuit Debugger

- MPLAB ICD 2

- Device Programmers

- PRO MATE<sup>®</sup> II Universal Device Programmer

- PICSTART<sup>®</sup> Plus Development Programmer

- Low Cost Demonstration Boards

- PICDEM<sup>™</sup> 1 Demonstration Board

- PICDEM.net<sup>™</sup> Demonstration Board

- PICDEM 2 Plus Demonstration Board

- PICDEM 3 Demonstration Board

- PICDEM 4 Demonstration Board

- PICDEM 17 Demonstration Board

- PICDEM 18R Demonstration Board

- PICDEM LIN Demonstration Board

- PICDEM USB Demonstration Board

- Evaluation Kits

- KEELOQ<sup>®</sup>

- PICDEM MSC

- microID<sup>®</sup>

- CAN

- PowerSmart<sup>®</sup>

- Analog

## 16.1 MPLAB Integrated Development Environment Software

The MPLAB IDE software brings an ease of software development previously unseen in the 8/16-bit microcontroller market. The MPLAB IDE is a Windows<sup>®</sup> based application that contains:

- · An interface to debugging tools

- simulator

- programmer (sold separately)

- emulator (sold separately)

- in-circuit debugger (sold separately)

- · A full-featured editor with color coded context

- A multiple project manager

- Customizable data windows with direct edit of contents

- High level source code debugging

- Mouse over variable inspection

- Extensive on-line help

- The MPLAB IDE allows you to:

- Edit your source files (either assembly or C)

- One touch assemble (or compile) and download to PIC MCU emulator and simulator tools (automatically updates all project information)

- Debug using:

- source files (assembly or C)

- absolute listing file (mixed assembly and C)

- machine code

MPLAB IDE supports multiple debugging tools in a single development paradigm, from the cost effective simulators, through low cost in-circuit debuggers, to full-featured emulators. This eliminates the learning curve when upgrading to tools with increasing flexibility and power.

## 16.2 MPASM Assembler

The MPASM assembler is a full-featured, universal macro assembler for all PIC MCUs.

The MPASM assembler generates relocatable object files for the MPLINK object linker, Intel<sup>®</sup> standard HEX files, MAP files to detail memory usage and symbol reference, absolute LST files that contain source lines and generated machine code and COFF files for debugging.

The MPASM assembler features include:

- Integration into MPLAB IDE projects

- · User defined macros to streamline assembly code

- Conditional assembly for multi-purpose source files

- Directives that allow complete control over the assembly process

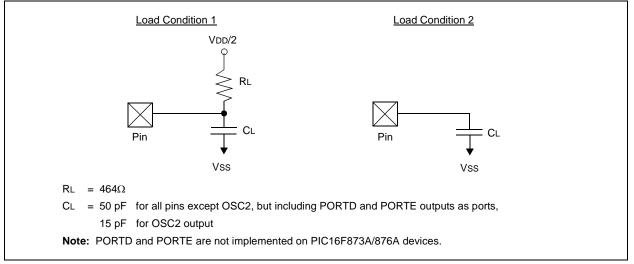

# 17.0 ELECTRICAL CHARACTERISTICS

# Absolute Maximum Ratings †

| Ambient temperature under bias                                                                                        | 55 to +125°C      |

|-----------------------------------------------------------------------------------------------------------------------|-------------------|

| Storage temperature                                                                                                   | -65°C to +150°C   |

| Voltage on any pin with respect to Vss (except VDD, MCLR. and RA4)                                                    | / to (VDD + 0.3V) |

| Voltage on VDD with respect to VSS                                                                                    | 0.3 to +7.5V      |

| Voltage on MCLR with respect to Vss (Note 2)                                                                          | 0 to +14V         |

| Voltage on RA4 with respect to Vss                                                                                    | 0 to +8.5V        |

| Total power dissipation (Note 1)                                                                                      | 1.0W              |

| Maximum current out of Vss pin                                                                                        | 300 mA            |

| Maximum current into Vod pin                                                                                          | 250 mA            |

| Input clamp current, Iк (Vi < 0 or Vi > VDD)                                                                          | ± 20 mA           |

| Output clamp current, Ioк (Vo < 0 or Vo > VDD)                                                                        | ± 20 mA           |

| Maximum output current sunk by any I/O pin                                                                            | 25 mA             |

| Maximum output current sourced by any I/O pin                                                                         | 25 mA             |

| Maximum current sunk by PORTA, PORTB and PORTE (combined) (Note 3)                                                    | 200 mA            |

| Maximum current sourced by PORTA, PORTB and PORTE (combined) (Note 3)                                                 | 200 mA            |

| Maximum current sunk by PORTC and PORTD (combined) (Note 3)                                                           | 200 mA            |

| Maximum current sourced by PORTC and PORTD (combined) (Note 3)                                                        | 200 mA            |

| <b>Note 1:</b> Power dissipation is calculated as follows: Pdis = VDD x {IDD - $\sum$ IOH} + $\sum$ {(VDD - VOH) x IO | H} + ∑(VOI x IOL) |

| 2: Voltage spikes below Vss at the MCLR pin, inducing currents greater than 80 mA, may                                | cause latch-up.   |

- 2: Voltage spikes below VSS at the MCLR pin, inducing currents greater than 80 mA, may cause latch-up. Thus, a series resistor of 50-100Ω should be used when applying a "low" level to the MCLR pin rather than pulling this pin directly to VSS.

- 3: PORTD and PORTE are not implemented on PIC16F873A/876A devices.

† NOTICE: Stresses above those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress rating only and functional operation of the device at those or any other conditions above those indicated in the operation listings of this specification is not implied. Exposure to maximum rating conditions for extended periods may affect device reliability.

## 17.1 DC Characteristics: PIC16F873A/874A/876A/877A (Industrial, Extended) PIC16LF873A/874A/876A/877A (Industrial)

| PIC16LF873A/874A/876A/877A<br>(Industrial)          |      |                                                                  | Standard Operating Conditions (unless otherwise stated)Operating temperature $-40^{\circ}C \le TA \le +85^{\circ}C$ for industrial |                                                                                                                                                                                         |      |       |                                                        |  |  |

|-----------------------------------------------------|------|------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|-------|--------------------------------------------------------|--|--|

| PIC16F873A/874A/876A/877A<br>(Industrial, Extended) |      |                                                                  |                                                                                                                                    | Standard Operating Conditions (unless otherwise stated)Operating temperature $-40^{\circ}C \le TA \le +85^{\circ}C$ for industrial $-40^{\circ}C \le TA \le +125^{\circ}C$ for extended |      |       |                                                        |  |  |

| Param<br>No. Symbol Characteristic/<br>Device       |      |                                                                  | Min                                                                                                                                | Тур†                                                                                                                                                                                    | Max  | Units | Conditions                                             |  |  |

|                                                     | Vdd  | Supply Voltage                                                   |                                                                                                                                    |                                                                                                                                                                                         |      |       |                                                        |  |  |

| D001                                                |      | 16LF87XA                                                         | 2.0                                                                                                                                | —                                                                                                                                                                                       | 5.5  | V     | All configurations<br>(DC to 10 MHz)                   |  |  |

| D001                                                |      | 16F87XA                                                          | 4.0                                                                                                                                |                                                                                                                                                                                         | 5.5  | V     | All configurations                                     |  |  |

| D001A                                               |      |                                                                  | VBOR                                                                                                                               |                                                                                                                                                                                         | 5.5  | V     | BOR enabled, FMAX = 14 MHz <sup>(7)</sup>              |  |  |

| D002                                                | Vdr  | RAM Data Retention<br>Voltage <sup>(1)</sup>                     | —                                                                                                                                  | 1.5                                                                                                                                                                                     |      | V     |                                                        |  |  |

| D003                                                | VPOR | VDD Start Voltage to<br>ensure internal Power-on<br>Reset signal | —                                                                                                                                  | Vss                                                                                                                                                                                     | _    | V     | See Section 14.5 "Power-on<br>Reset (POR)" for details |  |  |

| D004                                                | Svdd | VDD Rise Rate to ensure<br>internal Power-on Reset<br>signal     | 0.05                                                                                                                               | —                                                                                                                                                                                       | —    | V/ms  | See Section 14.5 "Power-on<br>Reset (POR)" for details |  |  |

| D005                                                | VBOR | Brown-out Reset<br>Voltage                                       | 3.65                                                                                                                               | 4.0                                                                                                                                                                                     | 4.35 | V     | BODEN bit in configuration word<br>enabled             |  |  |

Legend: Rows with standard voltage device data only are shaded for improved readability.

- † Data in "Typ" column is at 5V, 25°C, unless otherwise stated. These parameters are for design guidance only and are not tested.

- **Note 1:** This is the limit to which VDD can be lowered without losing RAM data.

- 2: The supply current is mainly a function of the operating voltage and frequency. Other factors, such as I/O pin loading, switching rate, oscillator type, internal code execution pattern and temperature, also have an impact on the current consumption.

- The test conditions for all IDD measurements in active operation mode are:

- OSC1 = external square wave, from rail-to-rail; all I/O pins tri-stated, pulled to VDD;

- MCLR = VDD; WDT enabled/disabled as specified.

- **3:** The power-down current in Sleep mode does not depend on the oscillator type. Power-down current is measured with the part in Sleep mode, with all I/O pins in high-impedance state and tied to VDD and Vss.

- **4:** For RC osc configuration, current through REXT is not included. The current through the resistor can be estimated by the formula Ir = VDD/2REXT (mA) with REXT in kΩ.

- **5:** Timer1 oscillator (when enabled) adds approximately 20 μA to the specification. This value is from characterization and is for design guidance only. This is not tested.

- 6: The  $\Delta$  current is the additional current consumed when this peripheral is enabled. This current should be added to the base IDD or IPD measurement.

- 7: When BOR is enabled, the device will operate correctly until the VBOR voltage trip point is reached.

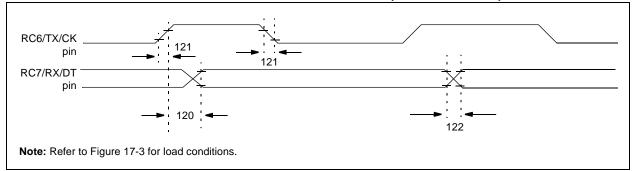

# 17.3 Timing Parameter Symbology

The timing parameter symbols have been created following one of the following formats:

| 1. TppS2ppS           |                                     | 3. Tcc:st | (I <sup>2</sup> C specifications only) |

|-----------------------|-------------------------------------|-----------|----------------------------------------|

| 2. TppS               |                                     | 4. Ts     | (I <sup>2</sup> C specifications only) |

| Т                     |                                     |           |                                        |

| F                     | Frequency                           | Т         | Time                                   |

| Lowerca               | se letters (pp) and their meanings: |           |                                        |

| рр                    |                                     |           |                                        |