Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Details                    |                                                                              |

|----------------------------|------------------------------------------------------------------------------|

| Product Status             | Obsolete                                                                     |

| Core Processor             | PIC                                                                          |

| Core Size                  | 8-Bit                                                                        |

| Speed                      | 10MHz                                                                        |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                            |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                        |

| Number of I/O              | 22                                                                           |

| Program Memory Size        | 7KB (4K x 14)                                                                |

| Program Memory Type        | FLASH                                                                        |

| EEPROM Size                | 128 x 8                                                                      |

| RAM Size                   | 192 x 8                                                                      |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 5.5V                                                                    |

| Data Converters            | A/D 5x10b                                                                    |

| Oscillator Type            | External                                                                     |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                            |

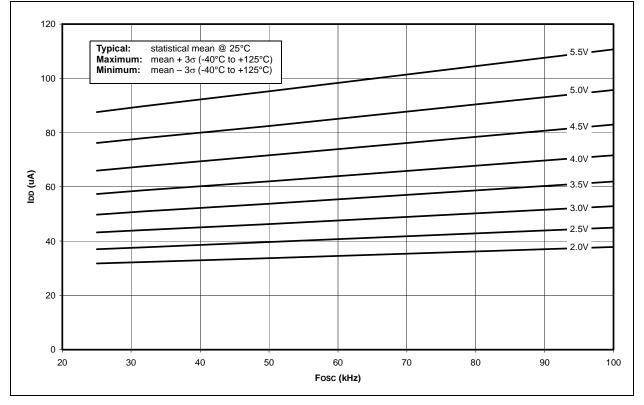

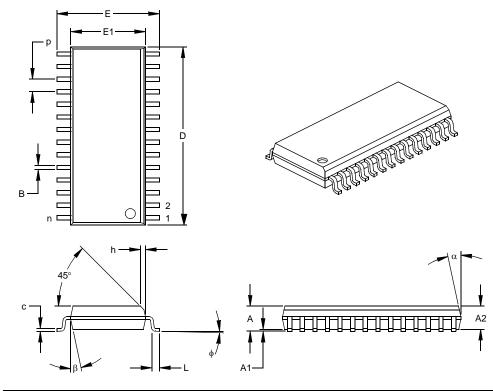

| Mounting Type              | Surface Mount                                                                |

| Package / Case             | 28-SOIC (0.295", 7.50mm Width)                                               |

| Supplier Device Package    | 28-SOIC                                                                      |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16lf873at-i-sog |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| Address | Name   | Bit 7 | Bit 6 | Bit 5 | Bit 4   | Bit 3 | Bit 2   | Bit 1      | Bit 0     | Value on:<br>POR, BOR | Value on<br>all other<br>Resets |

|---------|--------|-------|-------|-------|---------|-------|---------|------------|-----------|-----------------------|---------------------------------|

| 09h     | PORTE  | —     | —     | _     | —       |       | RE2     | RE1        | RE0       | xxx                   | uuu                             |

| 89h     | TRISE  | IBF   | OBF   | IBOV  | PSPMODE | —     | PORTE D | Data Direc | tion bits | 0000 -111             | 0000 -111                       |

| 9Fh     | ADCON1 | ADFM  | ADCS2 | _     | —       | PCFG3 | PCFG2   | PCFG1      | PCFG0     | 00 0000               | 00 0000                         |

#### **TABLE 4-10:** SUMMARY OF REGISTERS ASSOCIATED WITH PORTE

Legend: x = unknown, u = unchanged, - = unimplemented, read as '0'. Shaded cells are not used by PORTE.

#### **REGISTER 4-1: TRISE REGISTER (ADDRESS 89h)**

| R-0   | R-0 | R/W-0 | R/W-0   | U-0 | R/W-1 | R/W-1 | R/W-1 |

|-------|-----|-------|---------|-----|-------|-------|-------|

| IBF   | OBF | IBOV  | PSPMODE | —   | Bit 2 | Bit 1 | Bit 0 |

| bit 7 |     |       |         |     |       |       | bit 0 |

#### Parallel Slave Port Status/Control Bits:

| bit 7 | IBF: Input Buffer Full Stat          | tus bit                              |                      |                        |

|-------|--------------------------------------|--------------------------------------|----------------------|------------------------|

|       | 1 = A word has been rece             | eived and is waiting to              | be read by the CPU   |                        |

|       | 0 = No word has been re-             | ceived                               |                      |                        |

| bit 6 | <b>OBF</b> : Output Buffer Full      | Status bit                           |                      |                        |

|       | 1 = The output buffer still          | holds a previously wri               | tten word            |                        |

|       | 0 = The output buffer has            | been read                            |                      |                        |

| bit 5 | IBOV: Input Buffer Overf             | low Detect bit (in Micro             | processor mode)      |                        |

|       | 1 = A write occurred wh<br>software) | en a previously input                | word has not been re | ad (must be cleared in |

|       | 0 = No overflow occurred             | b                                    |                      |                        |

| bit 4 | PSPMODE: Parallel Slav               | e Port Mode Select bit               |                      |                        |

|       | 1 = PORTD functions in F             | Parallel Slave Port mo               | de                   |                        |

|       | 0 = PORTD functions in g             | general purpose I/O m                | ode                  |                        |

| bit 3 | Unimplemented: Read a                | <b>as</b> '0'                        |                      |                        |

|       | PORTE Data Direction E               | <u>Bits:</u>                         |                      |                        |

| bit 2 | Bit 2: Direction Control bi          | it for pin RE2/ $\overline{CS}$ /AN7 |                      |                        |

|       | 1 = Input                            |                                      |                      |                        |

|       | 0 = Output                           |                                      |                      |                        |

| bit 1 | Bit 1: Direction Control bi          | it for pin RE1/WR/AN6                |                      |                        |

|       | 1 = Input                            |                                      |                      |                        |

|       | 0 = Output                           |                                      |                      |                        |

| bit 0 | Bit 0: Direction Control bi          | it for pin RE0/RD/AN5                |                      |                        |

|       | 1 = Input                            |                                      |                      |                        |

|       | 0 = Output                           |                                      |                      |                        |

|       |                                      |                                      |                      |                        |

|       | Legend:                              |                                      |                      |                        |

|       | R = Readable bit                     | W = Writable bit                     | U = Unimplemented    | bit, read as '0'       |

|       | - n = Value at POR                   | '1' = Bit is set                     | '0' = Bit is cleared | x = Bit is unknown     |

|       | L                                    |                                      |                      |                        |

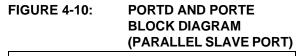

## 4.6 Parallel Slave Port

The Parallel Slave Port (PSP) is not implemented on the PIC16F873A or PIC16F876A.

PORTD operates as an 8-bit wide Parallel Slave Port, or microprocessor port, when control bit PSPMODE (TRISE<4>) is set. In Slave mode, it is asynchronously readable and writable by the external world through RD control input pin, RE0/RD/AN5, and WR control input pin, RE1/WR/AN6.

The PSP can directly interface to an 8-bit microprocessor data bus. The external microprocessor can read or write the PORTD latch as an 8-bit latch. Setting bit PSPMODE enables port pin RE0/RD/AN5 to be the RD input, RE1/WR/AN6 to be the WR input and RE2/CS/AN7 to be the CS (Chip Select) input. For this functionality, the corresponding data direction bits of the TRISE register (TRISE<2:0>) must be configured as inputs (set). The A/D port configuration bits, PCFG3:PCFG0 (ADCON1<3:0>), must be set to configure pins RE2:RE0 as digital I/O.

There are actually two 8-bit latches: one for data output and one for data input. The user writes 8-bit data to the PORTD data latch and reads data from the port pin latch (note that they have the same address). In this mode, the TRISD register is ignored since the external device is controlling the direction of data flow.

A write to the PSP occurs when both the  $\overline{CS}$  and  $\overline{WR}$ lines are first detected low. When either the  $\overline{CS}$  or  $\overline{WR}$ lines become high (level triggered), the Input Buffer Full (IBF) status flag bit (TRISE<7>) is set on the Q4 clock cycle, following the next Q2 cycle, to signal the write is complete (Figure 4-11). The interrupt flag bit, PSPIF (PIR1<7>), is also set on the same Q4 clock cycle. IBF can only be cleared by reading the PORTD input latch. The Input Buffer Overflow (IBOV) status flag bit (TRISE<5>) is set if a second write to the PSP is attempted when the previous byte has not been read out of the buffer.

A read from the PSP occurs when both the CS and RD lines are first detected low. The Output Buffer Full (OBF) status flag bit (TRISE<6>) is cleared immediately (Figure 4-12), indicating that the PORTD latch is waiting to be read by the external bus. When either the CS or RD pin becomes high (level triggered), the interrupt flag bit PSPIF is set on the Q4 clock cycle, following the next Q2 cycle, indicating that the read is complete. OBF remains low until data is written to PORTD by the user firmware. When not in PSP mode, the IBF and OBF bits are held clear. However, if flag bit IBOV was previously set, it must be cleared in firmware.

An interrupt is generated and latched into flag bit PSPIF when a read or write operation is completed. PSPIF must be cleared by the user in firmware and the interrupt can be disabled by clearing the interrupt enable bit PSPIE (PIE1<7>).

## 7.1 Timer2 Prescaler and Postscaler

The prescaler and postscaler counters are cleared when any of the following occurs:

- a write to the TMR2 register

- a write to the T2CON register

- any device Reset (POR, MCLR Reset, WDT Reset or BOR)

TMR2 is not cleared when T2CON is written.

# 7.2 Output of TMR2

The output of TMR2 (before the postscaler) is fed to the SSP module, which optionally uses it to generate the shift clock.

| TABLE 7-1:       | REGISTERS ASSOCIATED WITH TIMER2 AS A TIMER/COUNTER |

|------------------|-----------------------------------------------------|

| $IADEE I^{-1}$ . |                                                     |

| Address                 | Name   | Bit 7                | Bit 6       | Bit 5   | Bit 4   | Bit 3   | Bit 2  | Bit 1   | Bit 0   | Value<br>POR, |      |      | e on<br>other<br>sets |

|-------------------------|--------|----------------------|-------------|---------|---------|---------|--------|---------|---------|---------------|------|------|-----------------------|

| 0Bh, 8Bh,<br>10Bh, 18Bh | INTCON | GIE                  | PEIE        | TMR0IE  | INTE    | RBIE    | TMR0IF | INTF    | RBIF    | 0000          | 000x | 0000 | 000u                  |

| 0Ch                     | PIR1   | PSPIF <sup>(1)</sup> | ADIF        | RCIF    | TXIF    | SSPIF   | CCP1IF | TMR2IF  | TMR1IF  | 0000          | 0000 | 0000 | 0000                  |

| 8Ch                     | PIE1   | PSPIE <sup>(1)</sup> | ADIE        | RCIE    | TXIE    | SSPIE   | CCP1IE | TMR2IE  | TMR1IE  | 0000          | 0000 | 0000 | 0000                  |

| 11h                     | TMR2   | Timer2 M             | lodule's Re | gister  |         |         |        |         |         | 0000          | 0000 | 0000 | 0000                  |

| 12h                     | T2CON  | —                    | TOUTPS3     | TOUTPS2 | TOUTPS1 | TOUTPS0 | TMR2ON | T2CKPS1 | T2CKPS0 | -000          | 0000 | -000 | 0000                  |

| 92h                     | PR2    | Timer2 P             | eriod Regis | ter     |         |         |        |         |         | 1111          | 1111 | 1111 | 1111                  |

Legend: x = unknown, u = unchanged, - = unimplemented, read as '0'. Shaded cells are not used by the Timer2 module.

Note 1: Bits PSPIE and PSPIF are reserved on 28-pin devices; always maintain these bits clear.

|                        | =       |                      |               | •           |           |         |        |         |         | _             |      |       |                        |

|------------------------|---------|----------------------|---------------|-------------|-----------|---------|--------|---------|---------|---------------|------|-------|------------------------|

| Address                | Name    | Bit 7                | Bit 6         | Bit 5       | Bit 4     | Bit 3   | Bit 2  | Bit 1   | Bit 0   | Value<br>POR, |      | all o | ie on<br>other<br>sets |

| 0Bh,8Bh,<br>10Bh, 18Bh | INTCON  | GIE                  | PEIE          | TMR0IE      | INTE      | RBIE    | TMR0IF | INTF    | RBIF    | 0000          | 000x | 0000  | 000u                   |

| 0Ch                    | PIR1    | PSPIF <sup>(1)</sup> | ADIF          | RCIF        | TXIF      | SSPIF   | CCP1IF | TMR2IF  | TMR1IF  | 0000          | 0000 | 0000  | 0000                   |

| 0Dh                    | PIR2    | _                    | _             | _           | _         | _       | _      | _       | CCP2IF  |               | 0    |       | 0                      |

| 8Ch                    | PIE1    | PSPIE <sup>(1)</sup> | ADIE          | RCIE        | TXIE      | SSPIE   | CCP1IE | TMR2IE  | TMR1IE  | 0000          | 0000 | 0000  | 0000                   |

| 8Dh                    | PIE2    | —                    | —             | _           | —         | _       | —      | —       | CCP2IE  |               | 0    |       | 0                      |

| 87h                    | TRISC   | PORTC D              | Data Directio | n Register  |           |         |        |         |         | 1111          | 1111 | 1111  | 1111                   |

| 11h                    | TMR2    | Timer2 M             | odule's Reg   | ister       |           |         |        |         |         | 0000          | 0000 | 0000  | 0000                   |

| 92h                    | PR2     | Timer2 M             | odule's Peri  | od Register |           |         |        |         |         | 1111          | 1111 | 1111  | 1111                   |

| 12h                    | T2CON   | _                    | TOUTPS3       | TOUTPS2     | TOUTPS1   | TOUTPS0 | TMR2ON | T2CKPS1 | T2CKPS0 | -000          | 0000 | -000  | 0000                   |

| 15h                    | CCPR1L  | Capture/C            | Compare/PV    | VM Registe  | r 1 (LSB) |         |        |         |         | xxxx          | xxxx | uuuu  | uuuu                   |

| 16h                    | CCPR1H  | Capture/C            | Compare/PV    | VM Registe  | r 1 (MSB) |         |        |         |         | xxxx          | xxxx | uuuu  | uuuu                   |

| 17h                    | CCP1CON | _                    | _             | CCP1X       | CCP1Y     | CCP1M3  | CCP1M2 | CCP1M1  | CCP1M0  | 00            | 0000 | 00    | 0000                   |

| 1Bh                    | CCPR2L  | Capture/C            |               | xxxx        | xxxx      | uuuu    | uuuu   |         |         |               |      |       |                        |

| 1Ch                    | CCPR2H  | Capture/C            | Compare/PV    | VM Registe  | r 2 (MSB) |         |        |         |         | xxxx          | xxxx | uuuu  | uuuu                   |

| 1Dh                    | CCP2CON | _                    | —             | CCP2X       | CCP2Y     | CCP2M3  | CCP2M2 | CCP2M1  | CCP2M0  | 00            | 0000 | 00    | 0000                   |

TABLE 8-5: REGISTERS ASSOCIATED WITH PWM AND TIMER2

Legend: x = unknown, u = unchanged, - = unimplemented, read as '0'. Shaded cells are not used by PWM and Timer2.

Note 1: Bits PSPIE and PSPIF are reserved on 28-pin devices; always maintain these bits clear.

#### 9.3.1 REGISTERS

The MSSP module has four registers for SPI mode operation. These are:

- MSSP Control Register (SSPCON)

- MSSP Status Register (SSPSTAT)

- Serial Receive/Transmit Buffer Register (SSPBUF)

- MSSP Shift Register (SSPSR) Not directly accessible

SSPCON and SSPSTAT are the control and status registers in SPI mode operation. The SSPCON register is readable and writable. The lower six bits of the SSPSTAT are read-only. The upper two bits of the SSPSTAT are read/write. SSPSR is the shift register used for shifting data in or out. SSPBUF is the buffer register to which data bytes are written to or read from.

In receive operations, SSPSR and SSPBUF together create a double-buffered receiver. When SSPSR receives a complete byte, it is transferred to SSPBUF and the SSPIF interrupt is set.

During transmission, the SSPBUF is not doublebuffered. A write to SSPBUF will write to both SSPBUF and SSPSR.

#### REGISTER 9-1: SSPSTAT: MSSP STATUS REGISTER (SPI MODE) (ADDRESS 94h)

|       | R/W-0                    | R/W-0           | R-0             | R-0          | R-0           | R-0           | R-0          | R-0           |

|-------|--------------------------|-----------------|-----------------|--------------|---------------|---------------|--------------|---------------|

|       | SMP                      | CKE             | D/A             | Р            | S             | R/W           | UA           | BF            |

|       | bit 7                    |                 |                 |              |               |               |              | bit 0         |

| bit 7 | SMP: Sam                 | ple bit         |                 |              |               |               |              |               |

|       | SPI Master               |                 |                 |              |               |               |              |               |

|       |                          | ata sampled     |                 |              |               |               |              |               |

|       |                          | ata sampled     | at middle o     | r data outpu | tume          |               |              |               |

|       | SMP must                 | be cleared v    | when SPI is     | used in Slav | ve mode       |               |              |               |

| bit 6 |                          | Clock Select    |                 |              | o modo.       |               |              |               |

|       | 1 = Transm               | nit occurs on   | transition fr   | om active to | ldle clock s  | state         |              |               |

|       | 0 = Transm               | nit occurs on   | transition fr   | om Idle to a | ctive clock s | state         |              |               |

|       | Note:                    | Polarity of o   | clock state is  | s set by the | CKP bit (SS   | PCON1<4>      | ).           |               |

| bit 5 | D/A: Data/               | Address bit     |                 |              |               |               |              |               |

|       | Used in I <sup>2</sup> C | c mode only.    |                 |              |               |               |              |               |

| bit 4 | P: Stop bit              |                 |                 |              |               |               |              |               |

|       | Used in I <sup>2</sup> C | mode only.      | This bit is cle | ared when t  | he MSSP me    | odule is disa | bled, SSPEI  | N is cleared. |

| bit 3 | S: Start bit             |                 |                 |              |               |               |              |               |

|       | Used in I <sup>2</sup> C | c mode only.    |                 |              |               |               |              |               |

| bit 2 | R/W: Read                | I/Write bit inf | ormation        |              |               |               |              |               |

|       | Used in I <sup>2</sup> C | c mode only.    |                 |              |               |               |              |               |

| bit 1 | UA: Update               | e Address b     | it              |              |               |               |              |               |

|       | Used in I <sup>2</sup> C | c mode only.    |                 |              |               |               |              |               |

| bit 0 | BF: Buffer               | Full Status b   | oit (Receive    | mode only)   |               |               |              |               |

|       | 1 = Receiv               | e complete,     | SSPBUF is       | full         |               |               |              |               |

|       | 0 = Receiv               | e not comple    | ete, SSPBU      | F is empty   |               |               |              |               |

|       | Legend:                  |                 |                 |              |               |               |              |               |

|       | R = Reada                | ble bit         | W = W           | ritable bit  | U = Unim      | plemented     | bit, read as | '0'           |

|       | - n = Value              | at POR          | '1' = B         | it is set    | '0' = Bit i   | s cleared     | x = Bit is ι | Inknown       |

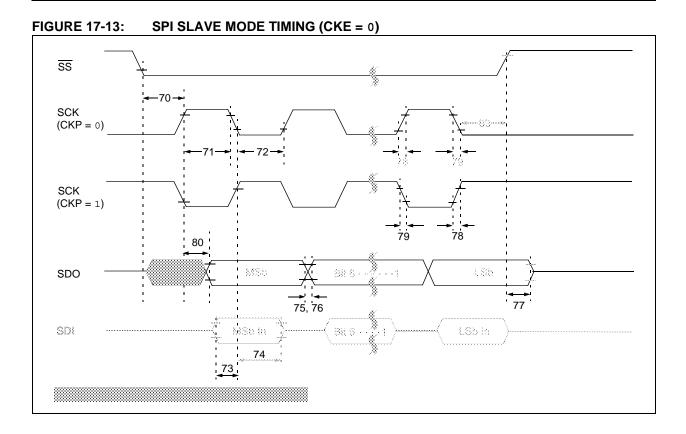

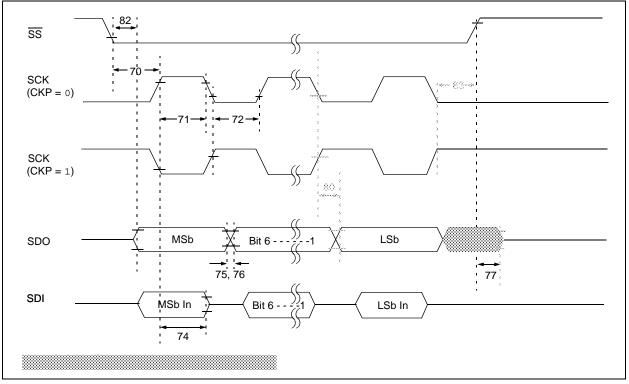

#### 9.3.6 SLAVE MODE

In Slave mode, the data is transmitted and received as the external clock pulses appear on SCK. When the last bit is latched, the SSPIF interrupt flag bit is set.

While in Slave mode, the external clock is supplied by the external clock source on the SCK pin. This external clock must meet the minimum high and low times as specified in the electrical specifications.

While in Sleep mode, the slave can transmit/receive data. When a byte is received, the device will wake-up from Sleep.

#### 9.3.7 SLAVE SELECT SYNCHRONIZATION

The  $\overline{SS}$  pin allows a Synchronous Slave mode. The SPI must be in Slave mode with  $\overline{SS}$  pin control enabled (SSPCON<3:0> = 04h). The pin must not be driven low for the  $\overline{SS}$  pin to function as an input. The data latch must be high. When the  $\overline{SS}$  pin is low, transmission and reception are enabled and the SDO pin is driven. When

the  $\overline{SS}$  pin goes high, the SDO pin is no longer driven even if in the middle of a transmitted byte and becomes a floating output. External pull-up/pull-down resistors may be desirable, depending on the application.

| Note 1: | When the SPI is in Slave mode with $\overline{SS}$ pin      |

|---------|-------------------------------------------------------------|

|         | control enabled (SSPCON< $3:0> = 0100$ ),                   |

|         | the SPI module will reset if the $\overline{SS}$ pin is set |

|         | to VDD.                                                     |

2: If the SPI is used in Slave Mode with CKE set, then the SS pin control must be enabled.

When the SPI module resets, the bit counter is forced to '0'. This can be done by either forcing the  $\overline{SS}$  pin to a high level or clearing the SSPEN bit.

To emulate two-wire communication, the SDO pin can be connected to the SDI pin. When the SPI needs to operate as a receiver, the SDO pin can be configured as an input. This disables transmissions from the SDO. The SDI can always be left as an input (SDI function) since it cannot create a bus conflict.

#

#### FIGURE 9-4: SLAVE SYNCHRONIZATION WAVEFORM

#### 9.3.8 SLEEP OPERATION

In Master mode, all module clocks are halted and the transmission/reception will remain in that state until the device wakes from Sleep. After the device returns to normal mode, the module will continue to transmit/ receive data.

In Slave mode, the SPI Transmit/Receive Shift register operates asynchronously to the device. This allows the device to be placed in Sleep mode and data to be shifted into the SPI Transmit/Receive Shift register. When all 8 bits have been received, the MSSP interrupt flag bit will be set and if enabled, will wake the device from Sleep.

#### 9.3.9 EFFECTS OF A RESET

A Reset disables the MSSP module and terminates the current transfer.

#### 9.3.10 BUS MODE COMPATIBILITY

Table 9-1 shows the compatibility between the standard SPI modes and the states of the CKP and CKE control bits.

#### TABLE 9-1: SPI BUS MODES

| Standard SPI Mode | Control Bits State |     |  |  |  |  |

|-------------------|--------------------|-----|--|--|--|--|

| Terminology       | СКР                | CKE |  |  |  |  |

| 0, 0              | 0                  | 1   |  |  |  |  |

| 0, 1              | 0                  | 0   |  |  |  |  |

| 1, 0              | 1                  | 1   |  |  |  |  |

| 1, 1              | 1                  | 0   |  |  |  |  |

There is also a SMP bit which controls when the data is sampled.

| Name    | Bit 7                | Bit 6                         | Bit 5      | Bit 4      | Bit 3       | Bit 2    | Bit 1  | Bit 0  | Valu<br>POR, | e on<br>BOR | Valu<br>all o<br>Res | ther |

|---------|----------------------|-------------------------------|------------|------------|-------------|----------|--------|--------|--------------|-------------|----------------------|------|

| INTCON  | GIE/<br>GIEH         | PEIE/<br>GIEL                 | TMR0IE     | INTOIE     | RBIE        | TMR0IF   | INTOIF | RBIF   | 0000         | 000x        | 0000                 | 000u |

| PIR1    | PSPIF <sup>(1)</sup> | ADIF                          | RCIF       | TXIF       | SSPIF       | CCP1IF   | TMR2IF | TMR1IF | 0000         | 0000        | 0000                 | 0000 |

| PIE1    | PSPIE <sup>(1)</sup> | ADIE                          | RCIE       | TXIE       | SSPIE       | CCP1IE   | TMR2IE | TMR1IE | 0000         | 0000        | 0000                 | 0000 |

| TRISC   | PORTC D              | ata Direc                     | tion Regis | ter        |             |          |        |        | 1111         | 1111        | 1111                 | 1111 |

| SSPBUF  | Synchron             | ous Seria                     | I Port Rec | eive Buffe | er/Transmit | Register |        |        | xxxx         | xxxx        | uuuu                 | uuuu |

| SSPCON  | WCOL                 | SSPOV                         | SSPEN      | CKP        | SSPM3       | SSPM2    | SSPM1  | SSPM0  | 0000         | 0000        | 0000                 | 0000 |

| TRISA   | —                    | PORTA Data Direction Register |            |            |             |          |        |        | 11           | 1111        | 11                   | 1111 |

| SSPSTAT | SMP                  | CKE                           | D/Ā        | Р          | S           | R/W      | UA     | BF     | 0000         | 0000        | 0000                 | 0000 |

#### TABLE 9-2: REGISTERS ASSOCIATED WITH SPI OPERATION

Legend: x = unknown, u = unchanged, - = unimplemented, read as '0'. Shaded cells are not used by the MSSP in SPI mode.

Note 1: The PSPIF, PSPIE and PSPIP bits are reserved on 28-pin devices; always maintain these bits clear.

#### 9.4.10 I<sup>2</sup>C MASTER MODE TRANSMISSION

Transmission of a data byte, a 7-bit address or the other half of a 10-bit address is accomplished by simply writing a value to the SSPBUF register. This action will set the Buffer Full flag bit, BF, and allow the Baud Rate Generator to begin counting and start the next transmission. Each bit of address/data will be shifted out onto the SDA pin after the falling edge of SCL is asserted (see data hold time specification, parameter #106). SCL is held low for one Baud Rate Generator rollover count (TBRG). Data should be valid before SCL is released high (see data setup time specification, parameter #107). When the SCL pin is released high, it is held that way for TBRG. The data on the SDA pin must remain stable for that duration and some hold time after the next falling edge of SCL. After the eighth bit is shifted out (the falling edge of the eighth clock), the BF flag is cleared and the master releases SDA. This allows the slave device being addressed to respond with an ACK bit during the ninth bit time, if an address match occurred or if data was received properly. The status of ACK is written into the ACKDT bit on the falling edge of the ninth clock. If the master receives an Acknowledge, the Acknowledge Status bit, ACKSTAT, is cleared. If not, the bit is set. After the ninth clock, the SSPIF bit is set and the master clock (Baud Rate Generator) is suspended until the next data byte is loaded into the SSPBUF, leaving SCL low and SDA unchanged (Figure 9-21).

After the write to the SSPBUF, each bit of address will be shifted out on the falling edge of SCL, until all seven address bits and the R/W bit are completed. On the falling edge of the eighth clock, the master will deassert the SDA pin, allowing the slave to respond with an Acknowledge. On the falling edge of the ninth clock, the master will sample the SDA pin to see if the address was recognized by a slave. The status of the ACK bit is loaded into the ACKSTAT status bit (SSPCON2<6>). Following the falling edge of the ninth clock transmission of the address, the SSPIF is set, the BF flag is cleared and the Baud Rate Generator is turned off until another write to the SSPBUF takes place, holding SCL low and allowing SDA to float.

#### 9.4.10.1 BF Status Flag

In Transmit mode, the BF bit (SSPSTAT<0>) is set when the CPU writes to SSPBUF and is cleared when all eight bits are shifted out.

#### 9.4.10.2 WCOL Status Flag

If the user writes the SSPBUF when a transmit is already in progress (i.e., SSPSR is still shifting out a data byte), the WCOL is set and the contents of the buffer are unchanged (the write doesn't occur).

WCOL must be cleared in software.

### 9.4.10.3 ACKSTAT Status Flag

In Transmit mode, the ACKSTAT bit (SSPCON2<6>) is cleared when the slave has sent an Acknowledge  $(\overline{ACK} = 0)$  and is set when the slave does Not Acknowledge  $(\overline{ACK} = 1)$ . A slave sends an Acknowledge when it has recognized its address (including a general call) or when the slave has properly received its data.

### 9.4.11 I<sup>2</sup>C MASTER MODE RECEPTION

Master mode reception is enabled by programming the Receive Enable bit, RCEN (SSPCON2<3>).

Note: The MSSP module must be in an Idle state before the RCEN bit is set or the RCEN bit will be disregarded.

The Baud Rate Generator begins counting and on each rollover, the state of the SCL pin changes (high to low/ low to high) and data is shifted into the SSPSR. After the falling edge of the eighth clock, the receive enable flag is automatically cleared, the contents of the SSPSR are loaded into the SSPBUF, the BF flag bit is set, the SSPIF flag bit is set and the Baud Rate Generator is suspended from counting, holding SCL low. The MSSP is now in Idle state, awaiting the next command. When the buffer is read by the CPU, the BF flag bit is automatically cleared. The user can then send an Acknowledge bit at the end of reception by setting the Acknowledge Sequence Enable bit, ACKEN (SSPCON2<4>).

#### 9.4.11.1 BF Status Flag

In receive operation, the BF bit is set when an address or data byte is loaded into SSPBUF from SSPSR. It is cleared when the SSPBUF register is read.

#### 9.4.11.2 SSPOV Status Flag

In receive operation, the SSPOV bit is set when 8 bits are received into the SSPSR and the BF flag bit is already set from a previous reception.

#### 9.4.11.3 WCOL Status Flag

If the user writes the SSPBUF when a receive is already in progress (i.e., SSPSR is still shifting in a data byte), the WCOL bit is set and the contents of the buffer are unchanged (the write doesn't occur).

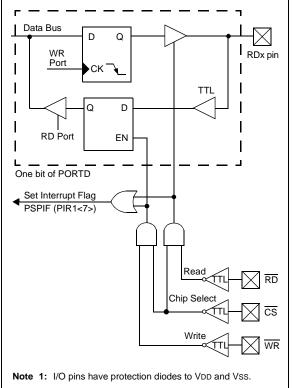

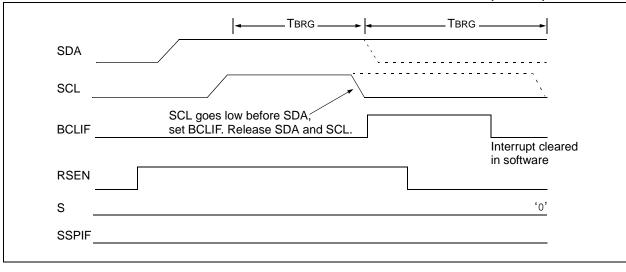

#### Bus Collision During a Repeated 9.4.17.2 Start Condition

During a Repeated Start condition, a bus collision occurs if:

- a) A low level is sampled on SDA when SCL goes from low level to high level.

- b) SCL goes low before SDA is asserted low, indicating that another master is attempting to transmit a data '1'.

When the user deasserts SDA and the pin is allowed to float high, the BRG is loaded with SSPADD<6:0> and counts down to 0. The SCL pin is then deasserted and when sampled high, the SDA pin is sampled.

If SDA is low, a bus collision has occurred (i.e., another master is attempting to transmit a data '0', see Figure 9-29). If SDA is sampled high, the BRG is

reloaded and begins counting. If SDA goes from high to low before the BRG times out, no bus collision occurs because no two masters can assert SDA at exactly the same time.

If SCL goes from high to low before the BRG times out and SDA has not already been asserted, a bus collision occurs. In this case, another master is attempting to transmit a data '1' during the Repeated Start condition (Figure 9-30).

If at the end of the BRG time-out, both SCL and SDA are still high, the SDA pin is driven low and the BRG is reloaded and begins counting. At the end of the count, regardless of the status of the SCL pin, the SCL pin is driven low and the Repeated Start condition is complete.

#### FIGURE 9-29: **BUS COLLISION DURING A REPEATED START CONDITION (CASE 1)**

# 10.0 ADDRESSABLE UNIVERSAL SYNCHRONOUS ASYNCHRONOUS RECEIVER TRANSMITTER (USART)

The Universal Synchronous Asynchronous Receiver Transmitter (USART) module is one of the two serial I/O modules. (USART is also known as a Serial Communications Interface or SCI.) The USART can be configured as a full-duplex asynchronous system that can communicate with peripheral devices, such as CRT terminals and personal computers, or it can be configured as a half-duplex synchronous system that can communicate with peripheral devices, such as A/D or D/A integrated circuits, serial EEPROMs, etc. The USART can be configured in the following modes:

- Asynchronous (full-duplex)

- Synchronous Master (half-duplex)

- Synchronous Slave (half-duplex)

Bit SPEN (RCSTA<7>) and bits TRISC<7:6> have to be set in order to configure pins RC6/TX/CK and RC7/RX/DT as the Universal Synchronous Asynchronous Receiver Transmitter.

The USART module also has a multi-processor communication capability using 9-bit address detection.

#### REGISTER 10-1: TXSTA: TRANSMIT STATUS AND CONTROL REGISTER (ADDRESS 98h)

|       | R/W-0                                                                                                                            | R/W-0           | R/W-0        | R/W-0         | U-0            | R/W-0     | R-1            | R/W-0  |  |  |  |  |

|-------|----------------------------------------------------------------------------------------------------------------------------------|-----------------|--------------|---------------|----------------|-----------|----------------|--------|--|--|--|--|

|       | CSRC                                                                                                                             | TX9             | TXEN         | SYNC          | _              | BRGH      | TRMT           | TX9D   |  |  |  |  |

|       | bit 7                                                                                                                            | 1               | 1            |               |                |           | 1              | bit 0  |  |  |  |  |

|       |                                                                                                                                  |                 |              |               |                |           |                |        |  |  |  |  |

| bit 7 | CSRC: Cloc                                                                                                                       | k Source Se     | elect bit    |               |                |           |                |        |  |  |  |  |

|       | <u>Asynchronou</u><br>Don't care.                                                                                                | <u>us mode:</u> |              |               |                |           |                |        |  |  |  |  |

|       | <u>Synchronous mode:</u><br>1 = Master mode (clock generated internally from BRG)<br>0 = Slave mode (clock from external source) |                 |              |               |                |           |                |        |  |  |  |  |

| bit 6 | <b>TX9</b> : 9-bit Tr                                                                                                            | ansmit Enat     | ole bit      |               |                |           |                |        |  |  |  |  |

|       | 1 = Selects 9<br>0 = Selects 8                                                                                                   |                 |              |               |                |           |                |        |  |  |  |  |

| bit 5 | TXEN: Trans                                                                                                                      | smit Enable     | bit          |               |                |           |                |        |  |  |  |  |

|       | 1 = Transmit<br>0 = Transmit                                                                                                     |                 |              |               |                |           |                |        |  |  |  |  |

|       | Note: S                                                                                                                          | SREN/CREN       | l overrides  | TXEN in Sy    | nc mode.       |           |                |        |  |  |  |  |

| bit 4 | SYNC: USA                                                                                                                        | RT Mode Se      | elect bit    |               |                |           |                |        |  |  |  |  |

|       | 1 = Synchron                                                                                                                     |                 |              |               |                |           |                |        |  |  |  |  |

|       | 0 = Asynchro                                                                                                                     |                 |              |               |                |           |                |        |  |  |  |  |

| bit 3 | Unimpleme                                                                                                                        |                 |              |               |                |           |                |        |  |  |  |  |

| bit 2 | BRGH: High                                                                                                                       |                 | Select bit   |               |                |           |                |        |  |  |  |  |

|       | Asynchronou<br>1 = High spe<br>0 = Low spe                                                                                       | ed              |              |               |                |           |                |        |  |  |  |  |

|       | Synchronous                                                                                                                      |                 |              |               |                |           |                |        |  |  |  |  |

|       | Unused in th                                                                                                                     | is mode.        |              |               |                |           |                |        |  |  |  |  |

| bit 1 | TRMT: Trans                                                                                                                      | smit Shift Re   | gister Statu | s bit         |                |           |                |        |  |  |  |  |

|       | 1 = TSR emp<br>0 = TSR full                                                                                                      | pty             |              |               |                |           |                |        |  |  |  |  |

| bit 0 | <b>TX9D:</b> 9th bi                                                                                                              | it of Transmi   | it Data, can | be Parity bit | I              |           |                |        |  |  |  |  |

|       | Legend:                                                                                                                          |                 |              |               |                |           |                |        |  |  |  |  |

|       | R = Readabl                                                                                                                      | le bit          | W = Wr       | itable bit    | U = Unimpl     | emented b | it, read as '( | )'     |  |  |  |  |

|       | - n = Value a                                                                                                                    | t POR           | '1' = Bit    | is set        | '0' = Bit is c | leared    | x = Bit is ur  | nknown |  |  |  |  |

|       |                                                                                                                                  |                 |              |               |                |           |                |        |  |  |  |  |

#### 10.3.2 USART SYNCHRONOUS MASTER RECEPTION

Once Synchronous mode is selected, reception is enabled by setting either enable bit, SREN (RCSTA<5>), or enable bit, CREN (RCSTA<4>). Data is sampled on the RC7/RX/DT pin on the falling edge of the clock. If enable bit SREN is set, then only a single word is received. If enable bit CREN is set, the reception is continuous until CREN is cleared. If both bits are set, CREN takes precedence. After clocking the last bit, the received data in the Receive Shift Register (RSR) is transferred to the RCREG register (if it is empty). When the transfer is complete, interrupt flag bit, RCIF (PIR1<5>), is set. The actual interrupt can be enabled/ disabled by setting/clearing enable bit, RCIE (PIE1<5>). Flag bit RCIF is a read-only bit which is reset by the hardware. In this case, it is reset when the RCREG register has been read and is empty. The RCREG is a double-buffered register (i.e., it is a twodeep FIFO). It is possible for two bytes of data to be received and transferred to the RCREG FIFO and a third byte to begin shifting into the RSR register. On the clocking of the last bit of the third byte, if the RCREG register is still full, then Overrun Error bit, OERR (RCSTA<1>), is set. The word in the RSR will be lost. The RCREG register can be read twice to retrieve the two bytes in the FIFO. Bit OERR has to be cleared in software (by clearing bit CREN). If bit OERR is set, transfers from the RSR to the RCREG are inhibited so it is essential to clear bit OERR if it is set. The ninth receive bit is buffered the same way as the receive

data. Reading the RCREG register will load bit RX9D with a new value, therefore, it is essential for the user to read the RCSTA register before reading RCREG in order not to lose the old RX9D information.

When setting up a Synchronous Master Reception:

- 1. Initialize the SPBRG register for the appropriate baud rate (Section 10.1 "USART Baud Rate Generator (BRG)").

- 2. Enable the synchronous master serial port by setting bits SYNC, SPEN and CSRC.

- 3. Ensure bits CREN and SREN are clear.

- 4. If interrupts are desired, then set enable bit RCIE.

- 5. If 9-bit reception is desired, then set bit RX9.

- 6. If a single reception is required, set bit SREN. For continuous reception, set bit CREN.

- Interrupt flag bit RCIF will be set when reception is complete and an interrupt will be generated if enable bit RCIE was set.

- 8. Read the RCSTA register to get the ninth bit (if enabled) and determine if any error occurred during reception.

- 9. Read the 8-bit received data by reading the RCREG register.

- 10. If any error occurred, clear the error by clearing bit CREN.

- 11. If using interrupts, ensure that GIE and PEIE (bits 7 and 6) of the INTCON register are set.

| ABEE 10-9. REGISTERS ASSOCIATED WITH STREAKONOOS MASTER RECEPTION |                                                           |                                                                                                     |                                                                                                          |                                                                                                                                                                                                  |                                                                                                                                                                                              |                                                                                                                                                                                                                                                             |                                                                                                                                                                                                                                                      |                                                                                                                                                                                                                                                                               |                                                                                                                                                                                                                                                                                                            |                                                                                                                                                                                                                                                                                                                                                                                                        |

|-------------------------------------------------------------------|-----------------------------------------------------------|-----------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Name                                                              | Bit 7                                                     | Bit 6                                                                                               | Bit 5                                                                                                    | Bit 4                                                                                                                                                                                            | Bit 3                                                                                                                                                                                        | Bit 2                                                                                                                                                                                                                                                       | Bit 1                                                                                                                                                                                                                                                | Bit 0                                                                                                                                                                                                                                                                         | Value on:<br>POR, BOR                                                                                                                                                                                                                                                                                      | Value on<br>all other<br>Resets                                                                                                                                                                                                                                                                                                                                                                        |

| INTCON                                                            | GIE                                                       | PEIE                                                                                                | TMR0IE                                                                                                   | INTE                                                                                                                                                                                             | RBIE                                                                                                                                                                                         | TMR0IF                                                                                                                                                                                                                                                      | INTF                                                                                                                                                                                                                                                 | R0IF                                                                                                                                                                                                                                                                          | 0000 000x                                                                                                                                                                                                                                                                                                  | 0000 000u                                                                                                                                                                                                                                                                                                                                                                                              |

| PIR1                                                              | PSPIF <sup>(1)</sup>                                      | ADIF                                                                                                | RCIF                                                                                                     | TXIF                                                                                                                                                                                             | SSPIF                                                                                                                                                                                        | CCP1IF                                                                                                                                                                                                                                                      | TMR2IF                                                                                                                                                                                                                                               | TMR1IF                                                                                                                                                                                                                                                                        | 0000 0000                                                                                                                                                                                                                                                                                                  | 0000 0000                                                                                                                                                                                                                                                                                                                                                                                              |

| RCSTA                                                             | SPEN                                                      | RX9                                                                                                 | SREN                                                                                                     | CREN                                                                                                                                                                                             |                                                                                                                                                                                              | FERR                                                                                                                                                                                                                                                        | OERR                                                                                                                                                                                                                                                 | RX9D                                                                                                                                                                                                                                                                          | 0000 -00x                                                                                                                                                                                                                                                                                                  | 0000 -00x                                                                                                                                                                                                                                                                                                                                                                                              |

| RCREG                                                             | USART Re                                                  | USART Receive Register                                                                              |                                                                                                          |                                                                                                                                                                                                  |                                                                                                                                                                                              |                                                                                                                                                                                                                                                             |                                                                                                                                                                                                                                                      |                                                                                                                                                                                                                                                                               | 0000 0000                                                                                                                                                                                                                                                                                                  | 0000 0000                                                                                                                                                                                                                                                                                                                                                                                              |

| PIE1                                                              | PSPIE <sup>(1)</sup>                                      | ADIE                                                                                                | RCIE                                                                                                     | TXIE                                                                                                                                                                                             | SSPIE                                                                                                                                                                                        | CCP1IE                                                                                                                                                                                                                                                      | TMR2IE                                                                                                                                                                                                                                               | TMR1IE                                                                                                                                                                                                                                                                        | 0000 0000                                                                                                                                                                                                                                                                                                  | 0000 0000                                                                                                                                                                                                                                                                                                                                                                                              |

| TXSTA                                                             | CSRC                                                      | TX9                                                                                                 | TXEN                                                                                                     | SYNC                                                                                                                                                                                             |                                                                                                                                                                                              | BRGH                                                                                                                                                                                                                                                        | TRMT                                                                                                                                                                                                                                                 | TX9D                                                                                                                                                                                                                                                                          | 0000 -010                                                                                                                                                                                                                                                                                                  | 0000 -010                                                                                                                                                                                                                                                                                                                                                                                              |

| SPBRG                                                             | Baud Rate                                                 | Generato                                                                                            | or Register                                                                                              | r                                                                                                                                                                                                |                                                                                                                                                                                              |                                                                                                                                                                                                                                                             |                                                                                                                                                                                                                                                      |                                                                                                                                                                                                                                                                               | 0000 0000                                                                                                                                                                                                                                                                                                  | 0000 0000                                                                                                                                                                                                                                                                                                                                                                                              |

|                                                                   | Name<br>INTCON<br>PIR1<br>RCSTA<br>RCREG<br>PIE1<br>TXSTA | NameBit 7INTCONGIEPIR1PSPIF <sup>(1)</sup> RCSTASPENRCREGUSART RePIE1PSPIE <sup>(1)</sup> TXSTACSRC | NameBit 7Bit 6INTCONGIEPEIEPIR1PSPIF(1)ADIFRCSTASPENRX9RCREGUSART Receive RePIE1PSPIE(1)ADIETXSTACSRCTX9 | NameBit 7Bit 6Bit 5INTCONGIEPEIETMR0IEPIR1PSPIF <sup>(1)</sup> ADIFRCIFRCSTASPENRX9SRENRCREGUSART Receive RegisterPIE1PSPIE <sup>(1)</sup> ADIEPIE1PSPIE <sup>(1)</sup> ADIERCIETXSTACSRCTX9TXEN | NameBit 7Bit 6Bit 5Bit 4INTCONGIEPEIETMROIEINTEPIR1PSPIF <sup>(1)</sup> ADIFRCIFTXIFRCSTASPENRX9SRENCRENRCREGUSART Receive RegisterFIE1PSPIE <sup>(1)</sup> ADIERCIETXIETXSTACSRCTX9TXENSYNC | NameBit 7Bit 6Bit 5Bit 4Bit 3INTCONGIEPEIETMROIEINTERBIEPIR1PSPIF <sup>(1)</sup> ADIFRCIFTXIFSSPIFRCSTASPENRX9SRENCREN—RCREGUSART Receive RegisterFIE1PSPIE <sup>(1)</sup> ADIERCIETXIESSPIEPIE1PSPIE <sup>(1)</sup> ADIERCIETXIESSPIETXSTACSRCTX9TXENSYNC— | NameBit 7Bit 6Bit 5Bit 4Bit 3Bit 2INTCONGIEPEIETMR0IEINTERBIETMR0IFPIR1PSPIF <sup>(1)</sup> ADIFRCIFTXIFSSPIFCCP1IFRCSTASPENRX9SRENCREN—FERRRCREGUSART Receive RegisterFFFFPIE1PSPIE <sup>(1)</sup> ADIERCIETXIESSPIECCP1IETXSTACSRCTX9TXENSYNC—BRGH | NameBit 7Bit 6Bit 5Bit 4Bit 3Bit 2Bit 1INTCONGIEPEIETMROIEINTERBIETMROIFINTFPIR1PSPIF <sup>(1)</sup> ADIFRCIFTXIFSSPIFCCP1IFTMR2IFRCSTASPENRX9SRENCREN—FERROERRRCREGUSART Receive RegisterFIE1PSPIE <sup>(1)</sup> ADIERCIETXIESSPIECCP1IETMR2IETXSTACSRCTX9TXENSYNC—BRGHTRMT | NameBit 7Bit 6Bit 5Bit 4Bit 3Bit 2Bit 1Bit 0INTCONGIEPEIETMROIEINTERBIETMROIFINTFROIFPIR1PSPIF <sup>(1)</sup> ADIFRCIFTXIFSSPIFCCP1IFTMR2IFTMR1IFRCSTASPENRX9SRENCREN—FERROERRRX9DRCREGUSART Receive RegisterFIE1PSPIE <sup>(1)</sup> ADIERCIETXIESSPIECCP1IETMR2IETMR1IETXSTACSRCTX9TXENSYNC—BRGHTRMTTX9D | NameBit 7Bit 6Bit 5Bit 4Bit 3Bit 2Bit 1Bit 0Value on:<br>POR, BORINTCONGIEPEIETMROIEINTERBIETMROIFINTFROIF0000000xPIR1PSPIF <sup>(1)</sup> ADIFRCIFTXIFSSPIFCCP1IFTMR2IFTMR1IF00000000RCSTASPENRX9SRENCREN—FERROERRRX9D0000-00xRCREGUSART Receive RegisterSYPIECCP1IETMR2IETMR1IE00000000PIE1PSPIE <sup>(1)</sup> ADIERCIETXIESSPIECCP1IETMR2IETMR1IE00000000TXSTACSRCTX9TXENSYNC—BRGHTRMTTX9D0000-011 |

#### TABLE 10-9: REGISTERS ASSOCIATED WITH SYNCHRONOUS MASTER RECEPTION

Legend: x = unknown, - = unimplemented, read as '0'. Shaded cells are not used for synchronous master reception. Note 1: Bits PSPIE and PSPIF are reserved on 28-pin devices; always maintain these bits clear.

# 16.0 DEVELOPMENT SUPPORT

The PIC<sup>®</sup> microcontrollers are supported with a full range of hardware and software development tools:

- Integrated Development Environment

- MPLAB<sup>®</sup> IDE Software

- Assemblers/Compilers/Linkers

- MPASM<sup>™</sup> Assembler

- MPLAB C17 and MPLAB C18 C Compilers

- MPLINK<sup>™</sup> Object Linker/

- MPLIB<sup>™</sup> Object Librarian

- MPLAB C30 C Compiler

- MPLAB ASM30 Assembler/Linker/Library

- Simulators

- MPLAB SIM Software Simulator

- MPLAB dsPIC30 Software Simulator

- Emulators

- MPLAB ICE 2000 In-Circuit Emulator

- MPLAB ICE 4000 In-Circuit Emulator

- In-Circuit Debugger

- MPLAB ICD 2

- Device Programmers

- PRO MATE<sup>®</sup> II Universal Device Programmer

- PICSTART<sup>®</sup> Plus Development Programmer

- Low Cost Demonstration Boards

- PICDEM<sup>™</sup> 1 Demonstration Board

- PICDEM.net<sup>™</sup> Demonstration Board

- PICDEM 2 Plus Demonstration Board

- PICDEM 3 Demonstration Board

- PICDEM 4 Demonstration Board

- PICDEM 17 Demonstration Board

- PICDEM 18R Demonstration Board

- PICDEM LIN Demonstration Board

- PICDEM USB Demonstration Board

- Evaluation Kits

- KEELOQ<sup>®</sup>

- PICDEM MSC

- microID<sup>®</sup>

- CAN

- PowerSmart<sup>®</sup>

- Analog

#### 16.1 MPLAB Integrated Development Environment Software

The MPLAB IDE software brings an ease of software development previously unseen in the 8/16-bit microcontroller market. The MPLAB IDE is a Windows<sup>®</sup> based application that contains:

- · An interface to debugging tools

- simulator

- programmer (sold separately)

- emulator (sold separately)

- in-circuit debugger (sold separately)

- · A full-featured editor with color coded context

- A multiple project manager

- Customizable data windows with direct edit of contents

- High level source code debugging

- Mouse over variable inspection

- Extensive on-line help

- The MPLAB IDE allows you to:

- Edit your source files (either assembly or C)

- One touch assemble (or compile) and download to PIC MCU emulator and simulator tools (automatically updates all project information)

- Debug using:

- source files (assembly or C)

- absolute listing file (mixed assembly and C)

- machine code

MPLAB IDE supports multiple debugging tools in a single development paradigm, from the cost effective simulators, through low cost in-circuit debuggers, to full-featured emulators. This eliminates the learning curve when upgrading to tools with increasing flexibility and power.

#### 16.2 MPASM Assembler

The MPASM assembler is a full-featured, universal macro assembler for all PIC MCUs.

The MPASM assembler generates relocatable object files for the MPLINK object linker, Intel<sup>®</sup> standard HEX files, MAP files to detail memory usage and symbol reference, absolute LST files that contain source lines and generated machine code and COFF files for debugging.

The MPASM assembler features include:

- Integration into MPLAB IDE projects

- · User defined macros to streamline assembly code

- Conditional assembly for multi-purpose source files

- Directives that allow complete control over the assembly process

## TABLE 17-1: COMPARATOR SPECIFICATIONS

| <b>Operating Conditions:</b> $3.0V < VDD < 5.5V$ , $-40^{\circ}C < TA < +85^{\circ}C$ (unless otherwise stated) $4.0V < VDD < 5.5V$ , $-40^{\circ}C < TA < +125^{\circ}C$ (unless otherwise stated) |        |                                            |     |       |            |          |                           |  |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|--------------------------------------------|-----|-------|------------|----------|---------------------------|--|

| Param<br>No.                                                                                                                                                                                        | Sym    | Characteristics                            | Min | Тур   | Мах        | Units    | Comments                  |  |

| D300                                                                                                                                                                                                | VIOFF  | Input Offset Voltage                       | _   | ± 5.0 | ± 10       | mV       |                           |  |

| D301                                                                                                                                                                                                | VICM   | Input Common Mode Voltage*                 | 0   | -     | Vdd - 1.5  | V        |                           |  |

| D302                                                                                                                                                                                                | CMRR   | Common Mode Rejection Ratio*               | 55  | -     | _          | dB       |                           |  |

| 300<br>300A                                                                                                                                                                                         | TRESP  | Response Time <sup>*(1)</sup>              | —   | 150   | 400<br>600 | ns<br>ns | PIC16F87XA<br>PIC16LF87XA |  |

| 301                                                                                                                                                                                                 | TMC20V | Comparator Mode Change to<br>Output Valid* | _   | —     | 10         | μS       |                           |  |

These parameters are characterized but not tested.

Note 1: Response time measured with one comparator input at (VDD - 1.5)/2 while the other input transitions from Vss to VDD.

# TABLE 17-2: VOLTAGE REFERENCE SPECIFICATIONS

| <b>Operating Conditions:</b> $3.0V < VDD < 5.5V$ , $-40^{\circ}C < TA < +85^{\circ}C$ (unless otherwise stated) $4.0V < VDD < 5.5V$ , $-40^{\circ}C < TA < +125^{\circ}C$ (unless otherwise stated) |      |                               |        |     |            |            |                                             |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|-------------------------------|--------|-----|------------|------------|---------------------------------------------|

| Spec<br>No.                                                                                                                                                                                         | Sym  | Characteristics               | Min    | Тур | Мах        | Units      | Comments                                    |

| D310                                                                                                                                                                                                | Vres | Resolution                    | Vdd/24 | —   | Vdd/32     | LSb        |                                             |

| D311                                                                                                                                                                                                | VRAA | Absolute Accuracy             | _      | _   | 1/2<br>1/2 | LSb<br>LSb | Low Range (VRR = 1)<br>High Range (VRR = 0) |