Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                     |

|----------------------------|----------------------------------------------------------------------------|

| Core Processor             | PIC                                                                        |

| Core Size                  | 8-Bit                                                                      |

| Speed                      | 10MHz                                                                      |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                          |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                      |

| Number of I/O              | 33                                                                         |

| Program Memory Size        | 7KB (4K x 14)                                                              |

| Program Memory Type        | FLASH                                                                      |

| EEPROM Size                | 128 x 8                                                                    |

| RAM Size                   | 192 x 8                                                                    |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 5.5V                                                                  |

| Data Converters            | A/D 8x10b                                                                  |

| Oscillator Type            | External                                                                   |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                          |

| Mounting Type              | Surface Mount                                                              |

| Package / Case             | 44-VQFN Exposed Pad                                                        |

| Supplier Device Package    | 44-QFN (8x8)                                                               |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16lf874a-i-ml |

|                            |                                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| TABLE 1-3:         PIC16F874A/877A PINOUT DESCRIPTION (CONTINUED) |              |          |              |                 |               |                       |                                                                 |

|-------------------------------------------------------------------|--------------|----------|--------------|-----------------|---------------|-----------------------|-----------------------------------------------------------------|

| Pin Name                                                          | PDII<br>Pin# |          | TQFP<br>Pin# | QFN<br>Pin#     | I/O/P<br>Type | Buffer<br>Type        | Description                                                     |

|                                                                   |              |          |              |                 |               |                       | PORTD is a bidirectional I/O port or Parallel Slave             |

|                                                                   |              |          |              |                 |               |                       | Port when interfacing to a microprocessor bus.                  |

| RD0/PSP0                                                          | 19           | 21       | 38           | 38              |               | ST/TTL <sup>(3)</sup> |                                                                 |

| RD0                                                               |              |          |              |                 | I/O           |                       | Digital I/O.                                                    |

| PSP0                                                              |              |          |              |                 | I/O           |                       | Parallel Slave Port data.                                       |

| RD1/PSP1                                                          | 20           | 22       | 39           | 39              |               | ST/TTL <sup>(3)</sup> |                                                                 |

| RD1                                                               |              |          |              |                 | I/O           |                       | Digital I/O.                                                    |

| PSP1                                                              |              |          |              |                 | I/O           | (2)                   | Parallel Slave Port data.                                       |

| RD2/PSP2                                                          | 21           | 23       | 40           | 40              |               | ST/TTL <sup>(3)</sup> |                                                                 |

| RD2<br>PSP2                                                       |              |          |              |                 | I/O<br>I/O    |                       | Digital I/O.<br>Parallel Slave Port data.                       |

| -                                                                 |              |          |              |                 | 1/0           | o = (=== (3)          | Parallel Slave Port data.                                       |

| RD3/PSP3                                                          | 22           | 24       | 41           | 41              | I/O           | ST/TTL <sup>(3)</sup> |                                                                 |

| RD3<br>PSP3                                                       |              |          |              |                 | 1/O<br>1/O    |                       | Digital I/O.<br>Parallel Slave Port data.                       |

|                                                                   | 07           | 20       | 0            | 0               | 1/0           | ST/TTL <sup>(3)</sup> |                                                                 |

| RD4/PSP4<br>RD4                                                   | 27           | 30       | 2            | 2               | I/O           | 51/11L*/              | Digital I/O.                                                    |

| PSP4                                                              |              |          |              |                 | 1/O           |                       | Parallel Slave Port data.                                       |

| RD5/PSP5                                                          | 28           | 31       | 3            | 3               |               | ST/TTL <sup>(3)</sup> |                                                                 |

| RD5                                                               | 20           | 51       | 5            | 5               | I/O           | 31/112.7              | Digital I/O.                                                    |

| PSP5                                                              |              |          |              |                 | I/O           |                       | Parallel Slave Port data.                                       |

| RD6/PSP6                                                          | 29           | 32       | 4            | 4               |               | ST/TTL <sup>(3)</sup> |                                                                 |

| RD6                                                               | 20           | 02       | -            | -               | I/O           | OWITE                 | Digital I/O.                                                    |

| PSP6                                                              |              |          |              |                 | I/O           |                       | Parallel Slave Port data.                                       |

| RD7/PSP7                                                          | 30           | 33       | 5            | 5               |               | ST/TTL <sup>(3)</sup> |                                                                 |

| RD7                                                               |              |          | Ũ            | Ŭ               | I/O           | 0.,                   | Digital I/O.                                                    |

| PSP7                                                              |              |          |              |                 | I/O           |                       | Parallel Slave Port data.                                       |

|                                                                   |              |          |              |                 |               |                       | PORTE is a bidirectional I/O port.                              |

| RE0/RD/AN5                                                        | 8            | 9        | 25           | 25              |               | ST/TTL(3)             |                                                                 |

| RE0                                                               | _            | _        | _            |                 | I/O           |                       | Digital I/O.                                                    |

| RD                                                                |              |          |              |                 | I             |                       | Read control for Parallel Slave Port.                           |

| AN5                                                               |              |          |              |                 | I             |                       | Analog input 5.                                                 |

| RE1/WR/AN6                                                        | 9            | 10       | 26           | 26              |               | ST/TTL <sup>(3)</sup> |                                                                 |

| RE1                                                               |              |          |              |                 | I/O           |                       | Digital I/O.                                                    |

| WR                                                                |              |          |              |                 |               |                       | Write control for Parallel Slave Port.                          |

| AN6                                                               |              |          |              |                 | I             | (2)                   | Analog input 6.                                                 |

| RE2/CS/AN7                                                        | 10           | 11       | 27           | 27              |               | ST/TTL <sup>(3)</sup> |                                                                 |

| RE2<br>CS                                                         |              |          |              |                 | I/O           |                       | Digital I/O.<br>Chip coloct control for Parallel Slove Part     |

| AN7                                                               |              |          |              |                 |               |                       | Chip select control for Parallel Slave Port.<br>Analog input 7. |

| Vss                                                               | 10.0         | 1 13, 34 | 6.20         | 6 20            | P             |                       |                                                                 |

| v                                                                 | 12, 3        | 1 13, 34 | 6, 29        | 6, 30,<br>31    |               |                       | Ground reference for logic and I/O pins.                        |

| Vdd                                                               | 11, 3        | 2 12, 35 | 7, 28        | 7, 8,<br>28, 29 | Р             | —                     | Positive supply for logic and I/O pins.                         |

| NC                                                                | <u> </u>     | 1, 17,   | 12,13,       | 13              |               | _                     | These pins are not internally connected. These pins             |

|                                                                   | 1            | 28, 40   | 33, 34       | -               |               |                       | should be left unconnected.                                     |

#### TARI E 1-3. PIC16E8744/8774 PINOLIT DESCRIPTION (CONTINUED)

= input I. — = Not used TTL = TTL input

I/O = input/output I ST = Schmitt Trigger input

Note 1: This buffer is a Schmitt Trigger input when configured as the external interrupt.2: This buffer is a Schmitt Trigger input when used in Serial Programming mode.

3: This buffer is a Schmitt Trigger input when configured in RC Oscillator mode and a CMOS input otherwise.

### 2.2.2.4 PIE1 Register

The PIE1 register contains the individual enable bits for the peripheral interrupts.

| Note: | Bit PEIE (INTCON<6>) must be set to |

|-------|-------------------------------------|

|       | enable any peripheral interrupt.    |

| <b>REGISTER 2-4:</b> | PIE1 REG                                                                                  | STER (AD     | DRESS 8       | Ch)                            |                              |            |              |            |  |  |

|----------------------|-------------------------------------------------------------------------------------------|--------------|---------------|--------------------------------|------------------------------|------------|--------------|------------|--|--|

|                      | R/W-0                                                                                     | R/W-0        | R/W-0         | R/W-0                          | R/W-0                        | R/W-0      | R/W-0        | R/W-0      |  |  |

|                      | PSPIE <sup>(1)</sup>                                                                      | ADIE         | RCIE          | TXIE                           | SSPIE                        | CCP1IE     | TMR2IE       | TMR1IE     |  |  |

|                      | bit 7                                                                                     |              |               |                                |                              |            |              | bit 0      |  |  |

|                      |                                                                                           |              |               |                                | . – (1)                      |            |              |            |  |  |

| bit 7                |                                                                                           |              |               |                                | pt Enable bit <sup>(1)</sup> |            |              |            |  |  |

|                      | 1 = Enables<br>0 = Disable                                                                |              |               |                                |                              |            |              |            |  |  |

|                      | Note 1:                                                                                   | PSPIE is re  | eserved on    | PIC16F873                      | A/876A devices               | ; always m | aintain this | bit clear. |  |  |

| bit 6                | ADIE: A/D                                                                                 | Converter Ir | nterrupt Ena  | able bit                       |                              |            |              |            |  |  |

|                      | 1 = Enable:<br>0 = Disable                                                                |              |               | •                              |                              |            |              |            |  |  |

| bit 5                | RCIE: USA                                                                                 | RT Receive   | Interrupt E   | nable bit                      |                              |            |              |            |  |  |

|                      | 1 = Enables the USART receive interrupt                                                   |              |               |                                |                              |            |              |            |  |  |

|                      | 0 = Disables the USART receive interrupt                                                  |              |               |                                |                              |            |              |            |  |  |

| bit 4                | TXIE: USA                                                                                 |              | •             |                                |                              |            |              |            |  |  |

|                      | 1 = Enables<br>0 = Disable                                                                |              |               |                                |                              |            |              |            |  |  |

| bit 3                | SSPIE: Syr                                                                                | nchronous S  | Serial Port I | nterrupt Ena                   | ıble bit                     |            |              |            |  |  |

|                      | <ul> <li>1 = Enables the SSP interrupt</li> <li>0 = Disables the SSP interrupt</li> </ul> |              |               |                                |                              |            |              |            |  |  |

| bit 2                | CCP1IE: C                                                                                 | CP1 Interru  | pt Enable b   | it                             |                              |            |              |            |  |  |

|                      | 1 = Enables                                                                               |              |               |                                |                              |            |              |            |  |  |

|                      | 0 = Disable                                                                               |              |               |                                |                              |            |              |            |  |  |

| bit 1                |                                                                                           |              |               | errupt Enabl                   |                              |            |              |            |  |  |

|                      |                                                                                           |              |               | tch interrupt<br>atch interrup |                              |            |              |            |  |  |

| bit 0                | TMR1IE: T                                                                                 | MR1 Overflo  | ow Interrupt  | t Enable bit                   |                              |            |              |            |  |  |

|                      | 1 = Enable:<br>0 = Disable                                                                |              |               |                                |                              |            |              |            |  |  |

|                      |                                                                                           |              |               |                                |                              |            |              |            |  |  |

| Legend:            |                  |                      |                    |

|--------------------|------------------|----------------------|--------------------|

| R = Readable bit   | W = Writable bit | U = Unimplemented    | bit, read as '0'   |

| - n = Value at POR | '1' = Bit is set | '0' = Bit is cleared | x = Bit is unknown |

#### 4.5 PORTE and TRISE Register

| Note: | PORTE and TRISE are not implemented |  |  |  |  |  |  |  |

|-------|-------------------------------------|--|--|--|--|--|--|--|

|       | on the 28-pin devices.              |  |  |  |  |  |  |  |

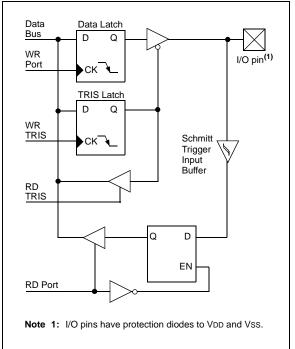

PORTE has three pins (RE0/RD/AN5, RE1/WR/AN6 and RE2/CS/AN7) which are individually configurable as inputs or outputs. These pins have Schmitt Trigger input buffers.

The PORTE pins become the I/O control inputs for the microprocessor port when bit PSPMODE (TRISE<4>) is set. In this mode, the user must make certain that the TRISE<2:0> bits are set and that the pins are configured as digital inputs. Also, ensure that ADCON1 is configured for digital I/O. In this mode, the input buffers are TTL.

Register 4-1 shows the TRISE register which also controls the Parallel Slave Port operation.

PORTE pins are multiplexed with analog inputs. When selected for analog input, these pins will read as '0's.

TRISE controls the direction of the RE pins, even when they are being used as analog inputs. The user must make sure to keep the pins configured as inputs when using them as analog inputs.

Note: On a Power-on Reset, these pins are configured as analog inputs and read as '0'.

#### TABLE 4-9: PORTE FUNCTIONS

#### FIGURE 4-9:

#### PORTE BLOCK DIAGRAM (IN I/O PORT MODE)

| Name       | Bit#  | Buffer Type           | Function                                                                                                                                                                                                                                   |

|------------|-------|-----------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| RE0/RD/AN5 | bit 0 | ST/TTL <sup>(1)</sup> | <ul> <li>I/O port pin or read control input in Parallel Slave Port mode or analog input:</li> <li>RD</li> <li>1 = Idle</li> <li>0 = Read operation. Contents of PORTD register are output to PORTD I/O pins (if chip selected).</li> </ul> |

| RE1/WR/AN6 | bit 1 | ST/TTL <sup>(1)</sup> | <ul> <li>I/O port pin or write control input in Parallel Slave Port mode or analog input:<br/>WR</li> <li>1 = Idle</li> <li>0 = Write operation. Value of PORTD I/O pins is latched into PORTD register (if chip selected).</li> </ul>     |

| RE2/CS/AN7 | bit 2 | ST/TTL <sup>(1)</sup> | <ul> <li>I/O port pin or chip select control input in Parallel Slave Port mode or analog input:</li> <li>CS</li> <li>1 = Device is not selected</li> <li>0 = Device is selected</li> </ul>                                                 |

Legend: ST = Schmitt Trigger input, TTL = TTL input

Note 1: Input buffers are Schmitt Triggers when in I/O mode and TTL buffers when in Parallel Slave Port mode.

NOTES:

### 6.4 Timer1 Operation in Asynchronous Counter Mode

If control bit  $\overline{T1SYNC}$  (T1CON<2>) is set, the external clock input is not synchronized. The timer continues to increment asynchronous to the internal phase clocks. The timer will continue to run during Sleep and can generate an interrupt-on-overflow which will wake-up the processor. However, special precautions in software are needed to read/write the timer.

In Asynchronous Counter mode, Timer1 cannot be used as a time base for capture or compare operations.

#### 6.4.1 READING AND WRITING TIMER1 IN ASYNCHRONOUS COUNTER MODE

Reading TMR1H or TMR1L while the timer is running from an external asynchronous clock will ensure a valid read (taken care of in hardware). However, the user should keep in mind that reading the 16-bit timer in two 8-bit values itself, poses certain problems, since the timer may overflow between the reads.

For writes, it is recommended that the user simply stop the timer and write the desired values. A write contention may occur by writing to the timer registers while the register is incrementing. This may produce an unpredictable value in the timer register.

Reading the 16-bit value requires some care. Examples 12-2 and 12-3 in the PIC<sup>®</sup> Mid-Range MCU Family Reference Manual (DS33023) show how to read and write Timer1 when it is running in Asynchronous mode.

# 6.5 Timer1 Oscillator

A crystal oscillator circuit is built-in between pins T1OSI (input) and T1OSO (amplifier output). It is enabled by setting control bit, T1OSCEN (T1CON<3>). The oscillator is a low-power oscillator, rated up to 200 kHz. It will continue to run during Sleep. It is primarily intended for use with a 32 kHz crystal. Table 6-1 shows the capacitor selection for the Timer1 oscillator.

The Timer1 oscillator is identical to the LP oscillator. The user must provide a software time delay to ensure proper oscillator start-up.

# TABLE 6-1:CAPACITOR SELECTION FOR<br/>THE TIMER1 OSCILLATOR

| Freq.                                      | C1                                                                                    | C2                                                                                                                                                                                                                    |  |  |  |  |

|--------------------------------------------|---------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| 32 kHz                                     | 33 pF                                                                                 | 33 pF                                                                                                                                                                                                                 |  |  |  |  |

| 100 kHz                                    | 15 pF                                                                                 | 15 pF                                                                                                                                                                                                                 |  |  |  |  |

| 200 kHz                                    | 15 pF                                                                                 | 15 pF                                                                                                                                                                                                                 |  |  |  |  |

| These values are for design guidance only. |                                                                                       |                                                                                                                                                                                                                       |  |  |  |  |

| Crystals                                   | Tested:                                                                               |                                                                                                                                                                                                                       |  |  |  |  |

| 32.768 kHz Epson C-001R32.768K-A ± 20 PPM  |                                                                                       |                                                                                                                                                                                                                       |  |  |  |  |

| Epson C-2 100.00 KC-P ± 20 PPM             |                                                                                       |                                                                                                                                                                                                                       |  |  |  |  |

| STD XTL 2                                  | STD XTL 200.000 kHz ± 20 PPM                                                          |                                                                                                                                                                                                                       |  |  |  |  |

|                                            | 32 kHz<br>100 kHz<br>200 kHz<br>Iues are for o<br>Crystals<br>Epson C-00<br>Epson C-2 | 32 kHz         33 pF           100 kHz         15 pF           200 kHz         15 pF           lues are for design guidate           Crystals Tested:           Epson C-001R32.768K-A           Epson C-2 100.00 KC-P |  |  |  |  |

**Note 1:** Higher capacitance increases the stability of oscillator but also increases the start-up time.

2: Since each resonator/crystal has its own characteristics, the user should consult the resonator/crystal manufacturer for appropriate values of external components.

### 6.6 Resetting Timer1 Using a CCP Trigger Output

If the CCP1 or CCP2 module is configured in Compare mode to generate a "special event trigger" (CCP1M3:CCP1M0 = 1011), this signal will reset Timer1.

| Note: | The special event triggers from the CCP1 |

|-------|------------------------------------------|

|       | and CCP2 modules will not set interrupt  |

|       | flag bit, TMR1IF (PIR1<0>).              |

Timer1 must be configured for either Timer or Synchronized Counter mode to take advantage of this feature. If Timer1 is running in Asynchronous Counter mode, this Reset operation may not work.

In the event that a write to Timer1 coincides with a special event trigger from CCP1 or CCP2, the write will take precedence.

In this mode of operation, the CCPRxH:CCPRxL register pair effectively becomes the period register for Timer1.

NOTES:

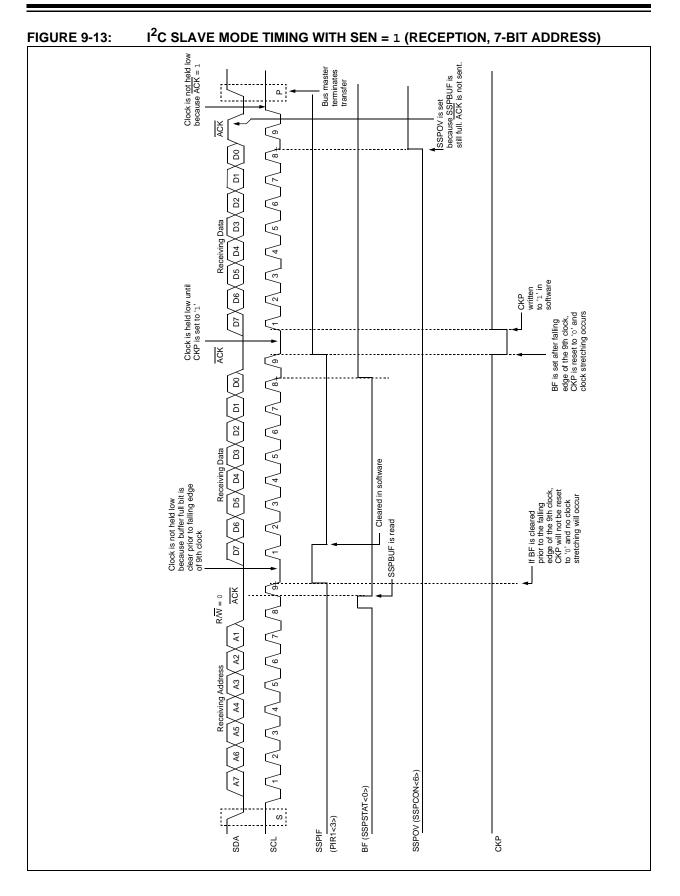

#### 9.4.10 I<sup>2</sup>C MASTER MODE TRANSMISSION

Transmission of a data byte, a 7-bit address or the other half of a 10-bit address is accomplished by simply writing a value to the SSPBUF register. This action will set the Buffer Full flag bit, BF, and allow the Baud Rate Generator to begin counting and start the next transmission. Each bit of address/data will be shifted out onto the SDA pin after the falling edge of SCL is asserted (see data hold time specification, parameter #106). SCL is held low for one Baud Rate Generator rollover count (TBRG). Data should be valid before SCL is released high (see data setup time specification, parameter #107). When the SCL pin is released high, it is held that way for TBRG. The data on the SDA pin must remain stable for that duration and some hold time after the next falling edge of SCL. After the eighth bit is shifted out (the falling edge of the eighth clock), the BF flag is cleared and the master releases SDA. This allows the slave device being addressed to respond with an ACK bit during the ninth bit time, if an address match occurred or if data was received properly. The status of ACK is written into the ACKDT bit on the falling edge of the ninth clock. If the master receives an Acknowledge, the Acknowledge Status bit, ACKSTAT, is cleared. If not, the bit is set. After the ninth clock, the SSPIF bit is set and the master clock (Baud Rate Generator) is suspended until the next data byte is loaded into the SSPBUF, leaving SCL low and SDA unchanged (Figure 9-21).

After the write to the SSPBUF, each bit of address will be shifted out on the falling edge of SCL, until all seven address bits and the R/W bit are completed. On the falling edge of the eighth clock, the master will deassert the SDA pin, allowing the slave to respond with an Acknowledge. On the falling edge of the ninth clock, the master will sample the SDA pin to see if the address was recognized by a slave. The status of the ACK bit is loaded into the ACKSTAT status bit (SSPCON2<6>). Following the falling edge of the ninth clock transmission of the address, the SSPIF is set, the BF flag is cleared and the Baud Rate Generator is turned off until another write to the SSPBUF takes place, holding SCL low and allowing SDA to float.

#### 9.4.10.1 BF Status Flag

In Transmit mode, the BF bit (SSPSTAT<0>) is set when the CPU writes to SSPBUF and is cleared when all eight bits are shifted out.

#### 9.4.10.2 WCOL Status Flag

If the user writes the SSPBUF when a transmit is already in progress (i.e., SSPSR is still shifting out a data byte), the WCOL is set and the contents of the buffer are unchanged (the write doesn't occur).

WCOL must be cleared in software.

### 9.4.10.3 ACKSTAT Status Flag

In Transmit mode, the ACKSTAT bit (SSPCON2<6>) is cleared when the slave has sent an Acknowledge  $(\overline{ACK} = 0)$  and is set when the slave does Not Acknowledge  $(\overline{ACK} = 1)$ . A slave sends an Acknowledge when it has recognized its address (including a general call) or when the slave has properly received its data.

### 9.4.11 I<sup>2</sup>C MASTER MODE RECEPTION

Master mode reception is enabled by programming the Receive Enable bit, RCEN (SSPCON2<3>).

Note: The MSSP module must be in an Idle state before the RCEN bit is set or the RCEN bit will be disregarded.

The Baud Rate Generator begins counting and on each rollover, the state of the SCL pin changes (high to low/ low to high) and data is shifted into the SSPSR. After the falling edge of the eighth clock, the receive enable flag is automatically cleared, the contents of the SSPSR are loaded into the SSPBUF, the BF flag bit is set, the SSPIF flag bit is set and the Baud Rate Generator is suspended from counting, holding SCL low. The MSSP is now in Idle state, awaiting the next command. When the buffer is read by the CPU, the BF flag bit is automatically cleared. The user can then send an Acknowledge bit at the end of reception by setting the Acknowledge Sequence Enable bit, ACKEN (SSPCON2<4>).

#### 9.4.11.1 BF Status Flag

In receive operation, the BF bit is set when an address or data byte is loaded into SSPBUF from SSPSR. It is cleared when the SSPBUF register is read.

#### 9.4.11.2 SSPOV Status Flag

In receive operation, the SSPOV bit is set when 8 bits are received into the SSPSR and the BF flag bit is already set from a previous reception.

#### 9.4.11.3 WCOL Status Flag

If the user writes the SSPBUF when a receive is already in progress (i.e., SSPSR is still shifting in a data byte), the WCOL bit is set and the contents of the buffer are unchanged (the write doesn't occur).

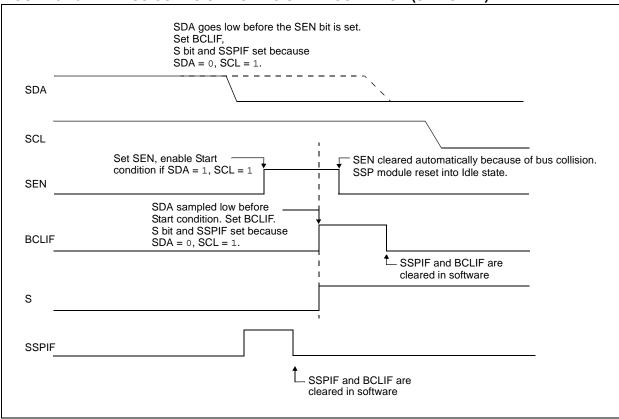

#### 9.4.17.1 Bus Collision During a Start Condition

During a Start condition, a bus collision occurs if:

- a) SDA or SCL are sampled low at the beginning of the Start condition (Figure 9-26).

- b) SCL is sampled low before SDA is asserted low (Figure 9-27).

During a Start condition, both the SDA and the SCL pins are monitored.

If the SDA pin is already low, or the SCL pin is already low, then all of the following occur:

- the Start condition is aborted,

- the BCLIF flag is set and

- the MSSP module is reset to its Idle state (Figure 9-26).

The Start condition begins with the SDA and SCL pins deasserted. When the SDA pin is sampled high, the Baud Rate Generator is loaded from SSPADD<6:0> and counts down to 0. If the SCL pin is sampled low while SDA is high, a bus collision occurs because it is assumed that another master is attempting to drive a data '1' during the Start condition.

If the SDA pin is sampled low during this count, the BRG is reset and the SDA line is asserted early (Figure 9-28). If, however, a '1' is sampled on the SDA pin, the SDA pin is asserted low at the end of the BRG count. The Baud Rate Generator is then reloaded and counts down to 0 and during this time, if the SCL pin is sampled as '0', a bus collision does not occur. At the end of the BRG count, the SCL pin is asserted low.

Note: The reason that bus collision is not a factor during a Start condition is that no two bus masters can assert a Start condition at the exact same time. Therefore, one master will always assert SDA before the other. This condition does not cause a bus collision because the two masters must be allowed to arbitrate the first address following the Start condition. If the address is the same, arbitration must be allowed to continue into the data portion, Repeated Start or Stop conditions.

#### FIGURE 9-26: BUS COLLISION DURING START CONDITION (SDA ONLY)

When setting up an Asynchronous Transmission, follow these steps:

- Initialize the SPBRG register for the appropriate baud rate. If a high-speed baud rate is desired, set bit BRGH (Section 10.1 "USART Baud Rate Generator (BRG)").

- 2. Enable the asynchronous serial port by clearing bit SYNC and setting bit SPEN.

- 3. If interrupts are desired, then set enable bit TXIE.

- 4. If 9-bit transmission is desired, then set transmit bit TX9.

- 5. Enable the transmission by setting bit TXEN, which will also set bit TXIF.

- 6. If 9-bit transmission is selected, the ninth bit should be loaded in bit TX9D.

- 7. Load data to the TXREG register (starts transmission).

- 8. If using interrupts, ensure that GIE and PEIE (bits 7 and 6) of the INTCON register are set.

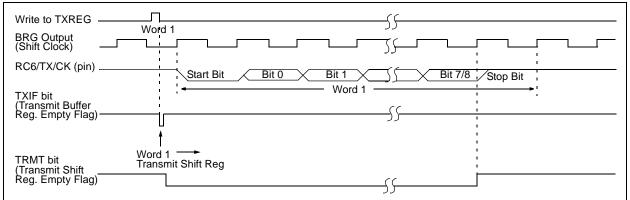

#### FIGURE 10-2: ASYNCHRONOUS MASTER TRANSMISSION

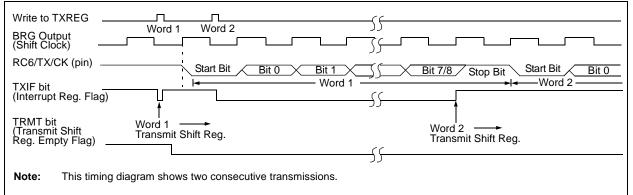

#### FIGURE 10-3: ASYNCHRONOUS MASTER TRANSMISSION (BACK TO BACK)

#### TABLE 10-5: REGISTERS ASSOCIATED WITH ASYNCHRONOUS TRANSMISSION

| Address                | Name   | Bit 7                              | Bit 6    | Bit 5  | Bit 4 | Bit 3    | Bit 2      | Bit 1       | Bit 0      | Value on:<br>POR, BOR | Value on<br>all other<br>Resets |

|------------------------|--------|------------------------------------|----------|--------|-------|----------|------------|-------------|------------|-----------------------|---------------------------------|

| 0Bh, 8Bh,<br>10Bh,18Bh | INTCON | GIE                                | PEIE     | TMR0IE | INTE  | RBIE     | TMR0IF     | INTF        | R0IF       | 0000 000x             | 0000 000u                       |

| 0Ch                    | PIR1   | PSPIF <sup>(1)</sup>               | ADIF     | RCIF   | TXIF  | SSPIF    | CCP1IF     | TMR2IF      | TMR1IF     | 0000 0000             | 0000 0000                       |

| 18h                    | RCSTA  | SPEN                               | RX9      | SREN   | CREN  |          | FERR       | OERR        | RX9D       | 0000 -00x             | 0000 -00x                       |

| 19h                    | TXREG  | USART Tra                          | nsmit Re | gister |       |          |            |             |            | 0000 0000             | 0000 0000                       |

| 8Ch                    | PIE1   | PSPIE <sup>(1)</sup>               | ADIE     | RCIE   | TXIE  | SSPIE    | CCP1IE     | TMR2IE      | TMR1IE     | 0000 0000             | 0000 0000                       |

| 98h                    | TXSTA  | CSRC                               | TX9      | TXEN   | SYNC  |          | BRGH       | TRMT        | TX9D       | 0000 -010             | 0000 -010                       |

| 99h                    | SPBRG  | SPBRG Baud Rate Generator Register |          |        |       |          |            |             |            | 0000 0000             | 0000 0000                       |

| Legend:                |        |                                    |          | 0      |       | s '0' Sh | adad calls | are not use | d for asym | chronous trans        |                                 |

Legend: x = unknown, - = unimplemented locations read as '0'. Shaded cells are not used for asynchronous transmission.

Note 1: Bits PSPIE and PSPIF are reserved on 28-pin devices; always maintain these bits clear.

### 10.3 USART Synchronous Master Mode

In Synchronous Master mode, the data is transmitted in a half-duplex manner (i.e., transmission and reception do not occur at the same time). When transmitting data, the reception is inhibited and vice versa. Synchronous mode is entered by setting bit, SYNC (TXSTA<4>). In addition, enable bit, SPEN (RCSTA<7>), is set in order to configure the RC6/TX/CK and RC7/RX/DT I/O pins to CK (clock) and DT (data) lines, respectively. The Master mode indicates that the processor transmits the master clock on the CK line. The Master mode is entered by setting bit, CSRC (TXSTA<7>).

#### 10.3.1 USART SYNCHRONOUS MASTER TRANSMISSION

The USART transmitter block diagram is shown in Figure 10-6. The heart of the transmitter is the Transmit (Serial) Shift Register (TSR). The shift register obtains its data from the Read/Write Transmit Buffer register, TXREG. The TXREG register is loaded with data in software. The TSR register is not loaded until the last bit has been transmitted from the previous load. As soon as the last bit is transmitted, the TSR is loaded with new data from the TXREG (if available). Once the TXREG register transfers the data to the TSR register (occurs in one TCYCLE), the TXREG is empty and interrupt bit, TXIF (PIR1<4>), is set. The interrupt can be enabled/disabled by setting/clearing enable bit TXIE (PIE1<4>). Flag bit TXIF will be set regardless of the state of enable bit TXIE and cannot be cleared in software. It will reset only when new data is loaded into the TXREG register. While flag bit TXIF indicates the status of the TXREG register, another bit, TRMT (TXSTA<1>), shows the status of the TSR register. TRMT is a readonly bit which is set when the TSR is empty. No interrupt logic is tied to this bit so the user has to poll this bit in order to determine if the TSR register is empty. The TSR is not mapped in data memory so it is not available to the user.

Transmission is enabled by setting enable bit, TXEN (TXSTA<5>). The actual transmission will not occur until the TXREG register has been loaded with data. The first data bit will be shifted out on the next available rising edge of the clock on the CK line. Data out is stable around the falling edge of the synchronous clock (Figure 10-9). The transmission can also be started by first loading the TXREG register and then setting bit TXEN (Figure 10-10). This is advantageous when slow baud rates are selected since the BRG is kept in Reset when bits TXEN, CREN and SREN are clear. Setting enable bit TXEN will start the BRG, creating a shift clock immediately. Normally, when transmission is first started, the TSR register is empty so a transfer to the TXREG register will result in an immediate transfer to TSR, resulting in an empty TXREG. Back-to-back transfers are possible.

Clearing enable bit TXEN during a transmission will cause the transmission to be aborted and will reset the transmitter. The DT and CK pins will revert to highimpedance. If either bit CREN or bit SREN is set during a transmission, the transmission is aborted and the DT pin reverts to a high-impedance state (for a reception). The CK pin will remain an output if bit CSRC is set (internal clock). The transmitter logic, however, is not reset, although it is disconnected from the pins. In order to reset the transmitter, the user has to clear bit TXEN. If bit SREN is set (to interrupt an on-going transmission and receive a single word), then after the single word is received, bit SREN will be cleared and the serial port will revert back to transmitting since bit TXEN is still set. The DT line will immediately switch from High-Impedance Receive mode to transmit and start driving. To avoid this, bit TXEN should be cleared.

In order to select 9-bit transmission, the TX9 (TXSTA<6>) bit should be set and the ninth bit should be written to bit TX9D (TXSTA<0>). The ninth bit must be written before writing the 8-bit data to the TXREG register. This is because a data write to the TXREG can result in an immediate transfer of the data to the TSR register (if the TSR is empty). If the TSR was empty and the TXREG was written before writing the "new" TX9D, the "present" value of bit TX9D is loaded.

Steps to follow when setting up a Synchronous Master Transmission:

- 1. Initialize the SPBRG register for the appropriate baud rate (Section 10.1 "USART Baud Rate Generator (BRG)").

- 2. Enable the synchronous master serial port by setting bits SYNC, SPEN and CSRC.

- 3. If interrupts are desired, set enable bit TXIE.

- 4. If 9-bit transmission is desired, set bit TX9.

- 5. Enable the transmission by setting bit TXEN.

- 6. If 9-bit transmission is selected, the ninth bit should be loaded in bit TX9D.

- 7. Start transmission by loading data to the TXREG register.

- 8. If using interrupts, ensure that GIE and PEIE (bits 7 and 6) of the INTCON register are set.

# 11.0 ANALOG-TO-DIGITAL CONVERTER (A/D) MODULE

The Analog-to-Digital (A/D) Converter module has five inputs for the 28-pin devices and eight for the 40/44-pin devices.

The conversion of an analog input signal results in a corresponding 10-bit digital number. The A/D module has high and low-voltage reference input that is software selectable to some combination of VDD, Vss, RA2 or RA3.

The A/D converter has a unique feature of being able to operate while the device is in Sleep mode. To operate in Sleep, the A/D clock must be derived from the A/D's internal RC oscillator. The A/D module has four registers. These registers are:

- A/D Result High Register (ADRESH)

- A/D Result Low Register (ADRESL)

- A/D Control Register 0 (ADCON0)

- A/D Control Register 1 (ADCON1)

The ADCON0 register, shown in Register 11-1, controls the operation of the A/D module. The ADCON1 register, shown in Register 11-2, configures the functions of the port pins. The port pins can be configured as analog inputs (RA3 can also be the voltage reference) or as digital I/O.

Additional information on using the A/D module can be found in the PIC<sup>®</sup> Mid-Range MCU Family Reference Manual (DS33023).

| REGISTER 11-1: | ADCON0 REGISTER (ADDRESS 1Fh |

|----------------|------------------------------|

|----------------|------------------------------|

| R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0   | U-0 | R/W-0 |

|-------|-------|-------|-------|-------|---------|-----|-------|

| ADCS1 | ADCS0 | CHS2  | CHS1  | CHS0  | GO/DONE | Ι   | ADON  |

| bit 7 |       |       |       |       |         |     | bit 0 |

bit 7-6 ADCS1:ADCS0: A/D Conversion Clock Select bits (ADCON0 bits in **bold**)

| ADCON1<br><adcs2></adcs2> | ADCON0<br><adcs1:adcs0></adcs1:adcs0> | Clock Conversion                                        |

|---------------------------|---------------------------------------|---------------------------------------------------------|

| 0                         | 00                                    | Fosc/2                                                  |

| 0                         | 01                                    | Fosc/8                                                  |

| 0                         | 10                                    | Fosc/32                                                 |

| 0                         | 11                                    | FRC (clock derived from the internal A/D RC oscillator) |

| 1                         | 00                                    | Fosc/4                                                  |

| 1                         | 01                                    | Fosc/16                                                 |

| 1                         | 10                                    | Fosc/64                                                 |

| 1                         | 11                                    | FRC (clock derived from the internal A/D RC oscillator) |

bit 5-3 CHS2:CHS0: Analog Channel Select bits

- 000 = Channel 0 (AN0)

- 001 = Channel 1 (AN1)

- 010 = Channel 2 (AN2)

- 011 = Channel 3 (AN3)

- 100 = Channel 4 (AN4)

- 101 = Channel 5 (AN5)

- 110 = Channel 6 (AN6)

- 111 = Channel 7 (AN7)

- **Note:** The PIC16F873A/876A devices only implement A/D channels 0 through 4; the unimplemented selections are reserved. Do not select any unimplemented channels with these devices.

bit 2 GO/DONE: A/D Conversion Status bit

<u>When ADON = 1:</u>

- 1 = A/D conversion in progress (setting this bit starts the A/D conversion which is automatically cleared by hardware when the A/D conversion is complete)

- 0 = A/D conversion not in progress

- bit 1 Unimplemented: Read as '0'

#### bit 0 ADON: A/D On bit

1 = A/D converter module is powered up

0 = A/D converter module is shut-off and consumes no operating current

# Legend:

| Legend:            |                  |                      |                    |

|--------------------|------------------|----------------------|--------------------|

| R = Readable bit   | W = Writable bit | U = Unimplemented    | l bit, read as '0' |

| - n = Value at POR | '1' = Bit is set | '0' = Bit is cleared | x = Bit is unknown |

| TABLE 15-2: PIC16 | F87XA INSTRUCTION SET |

|-------------------|-----------------------|

|-------------------|-----------------------|

| Mnem    | ionic, | Description                                    | Cycles        |       | 14-Bit | Status | Notos |          |       |  |

|---------|--------|------------------------------------------------|---------------|-------|--------|--------|-------|----------|-------|--|

| Oper    | ands   | Description                                    | Cycles        | MSb   |        |        | LSb   | Affected | Notes |  |

|         |        | BYTE-ORIENTED FILE                             | EREGISTER OPE | RATIC | NS     |        |       |          |       |  |

| ADDWF   | f, d   | Add W and f                                    | 1             | 00    | 0111   | dfff   | ffff  | C,DC,Z   | 1,2   |  |

| ANDWF   | f, d   | AND W with f                                   | 1             | 00    | 0101   | dfff   | ffff  | Z        | 1,2   |  |

| CLRF    | f      | Clear f                                        | 1             | 00    | 0001   | lfff   | ffff  | Z        | 2     |  |

| CLRW    | -      | Clear W                                        | 1             | 00    | 0001   | 0xxx   | xxxx  | Z        |       |  |

| COMF    | f, d   | Complement f                                   | 1             | 00    | 1001   | dfff   | ffff  | Z        | 1,2   |  |

| DECF    | f, d   | Decrement f                                    | 1             | 00    | 0011   | dfff   | ffff  | Z        | 1,2   |  |

| DECFSZ  | f, d   | Decrement f, Skip if 0                         | 1(2)          | 00    | 1011   | dfff   | ffff  |          | 1,2,3 |  |

| INCF    | f, d   | Increment f                                    | 1             | 00    | 1010   | dfff   | ffff  | Z        | 1,2   |  |

| INCFSZ  | f, d   | Increment f, Skip if 0                         | 1(2)          | 00    | 1111   | dfff   | ffff  |          | 1,2,3 |  |

| IORWF   | f, d   | Inclusive OR W with f                          | 1             | 00    | 0100   | dfff   | ffff  | Z        | 1,2   |  |

| MOVF    | f, d   | Move f                                         | 1             | 00    | 1000   | dfff   | ffff  | Z        | 1,2   |  |

| MOVWF   | f      | Move W to f                                    | 1             | 00    | 0000   | lfff   | ffff  |          |       |  |

| NOP     | -      | No Operation                                   | 1             | 00    | 0000   | 0xx0   | 0000  |          |       |  |

| RLF     | f, d   | Rotate Left f through Carry                    | 1             | 00    | 1101   | dfff   | ffff  | С        | 1,2   |  |

| RRF     | f, d   | Rotate Right f through Carry                   | 1             | 00    | 1100   | dfff   | ffff  | С        | 1,2   |  |

| SUBWF   | f, d   | Subtract W from f                              | 1             | 00    | 0010   | dfff   | ffff  | C,DC,Z   | 1,2   |  |

| SWAPF   | f, d   | Swap nibbles in f                              | 1             | 00    | 1110   | dfff   | ffff  |          | 1,2   |  |

| XORWF   | f, d   | Exclusive OR W with f                          | 1             | 00    | 0110   | dfff   | ffff  | Z        | 1,2   |  |

|         |        | BIT-ORIENTED FILE                              |               | ATIO  | NS     |        |       |          |       |  |

| BCF     | f, b   | Bit Clear f                                    | 1             | 01    | 00bb   | bfff   | ffff  |          | 1,2   |  |

| BSF     | f, b   | Bit Set f                                      | 1             | 01    |        | bfff   |       |          | 1,2   |  |

| BTFSC   | f, b   | Bit Test f, Skip if Clear                      | 1 (2)         | 01    | 10bb   | bfff   |       |          | 3     |  |

| BTFSS   | f, b   | Bit Test f, Skip if Set                        | 1 (2)         | 01    | 11bb   | bfff   | ffff  |          | 3     |  |

|         | ,      | LITERAL AND CO                                 | ( )           | IONS  |        |        |       |          |       |  |

| ADDLW   | k      | Add Literal and W                              | 1             | 11    | 111x   | kkkk   | kkkk  | C,DC,Z   |       |  |

| ANDLW   | k      | AND Literal with W                             | 1             | 11    | 1001   | kkkk   | kkkk  | Z        |       |  |

| CALL    | k      | Call Subroutine                                | 2             | 10    | 0kkk   | kkkk   | kkkk  |          |       |  |

| CLRWDT  | -      | Clear Watchdog Timer                           | 1             | 00    | 0000   | 0110   | 0100  | TO,PD    |       |  |

| GOTO    | k      | Go to Address                                  | 2             | 10    | 1kkk   | kkkk   | kkkk  | -        |       |  |

| IORLW   | k      | Inclusive OR Literal with W                    | 1             | 11    | 1000   | kkkk   | kkkk  | Z        |       |  |

| MOVLW   | k      | Move Literal to W                              | 1             | 11    | 00xx   | kkkk   | kkkk  |          |       |  |

| RETFIE  | -      | Return from Interrupt                          | 2             | 00    | 0000   | 0000   | 1001  |          |       |  |

| RETLW   | k      | Return with Literal in W                       | 2             | 11    | 01xx   | kkkk   |       |          |       |  |

| RETURN  | -      | Return from Subroutine                         | 2             | 00    | 0000   | 0000   | 1000  |          |       |  |

| SLEEP   | -      | Go into Standby mode                           | 1             | 00    | 0000   | 0110   | 0011  | TO,PD    |       |  |

| SUBLW   | k      | Subtract W from Literal                        | 1             | 11    |        | kkkk   |       | C,DC,Z   |       |  |

| XORLW   | k      | Exclusive OR Literal with W                    | 1             | 11    | 1010   | kkkk   |       | Z        |       |  |

| Note 1: |        | I/O register is modified as a function of itse |               |       |        |        |       |          |       |  |

Note 1: When an I/O register is modified as a function of itself (e.g., MOVF PORTE, 1), the value used will be that value present on the pins themselves. For example, if the data latch is '1' for a pin configured as input and is driven low by an external device, the data will be written back with a '0'.

2: If this instruction is executed on the TMR0 register (and where applicable, d = 1), the prescaler will be cleared if assigned to the Timer0 module.

3: If Program Counter (PC) is modified, or a conditional test is true, the instruction requires two cycles. The second cycle is executed as a NOP.

**Note:** Additional information on the mid-range instruction set is available in the PIC<sup>®</sup> Mid-Range MCU Family Reference Manual (DS33023).

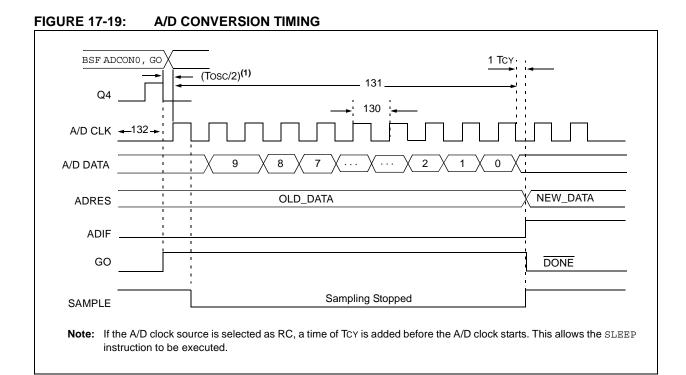

| TABLE 17-15: A/D CONVERSION REQUIREMENTS |

|------------------------------------------|

|------------------------------------------|

| Param<br>No. | Symbol | Characte                      | eristic             | Min      | Тур†     | Max | Units | Conditions                                                                                                                                                                                                                      |

|--------------|--------|-------------------------------|---------------------|----------|----------|-----|-------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 130          | TAD    | A/D Clock Period              | PIC16F87XA          | 1.6      | —        | _   | μs    | Tosc based, VREF $\geq$ 3.0V                                                                                                                                                                                                    |

|              |        |                               | PIC16LF87XA         | 3.0      | —        | _   | μS    | Tosc based, VREF $\ge 2.0V$                                                                                                                                                                                                     |

|              |        |                               | PIC16F87XA          | 2.0      | 4.0      | 6.0 | μS    | A/D RC mode                                                                                                                                                                                                                     |

|              |        |                               | PIC16LF87XA         | 3.0      | 6.0      | 9.0 | μS    | A/D RC mode                                                                                                                                                                                                                     |

| 131          | TCNV   | Conversion Time (not (Note 1) | including S/H time) |          | —        | 12  | TAD   |                                                                                                                                                                                                                                 |

| 132          | TACQ   | Acquisition Time              |                     | (Note 2) | 40       | _   | μS    |                                                                                                                                                                                                                                 |

|              |        |                               |                     | 10*      | _        |     | μs    | The minimum time is the<br>amplifier settling time. This may<br>be used if the "new" input volt-<br>age has not changed by more<br>than 1 LSb (i.e., 20.0 mV @<br>5.12V) from the last sampled<br>voltage (as stated on CHOLD). |

| 134          | TGO    | Q4 to A/D Clock Start         |                     |          | Tosc/2 § |     | _     | If the A/D clock source is<br>selected as RC, a time of TCY is<br>added before the A/D clock<br>starts. This allows the SLEEP<br>instruction to be executed.                                                                    |

\* These parameters are characterized but not tested.

† Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

§ This specification ensured by design.

- **Note 1:** ADRES register may be read on the following TCY cycle.

- 2: See Section 11.1 "A/D Acquisition Requirements" for minimum conditions.

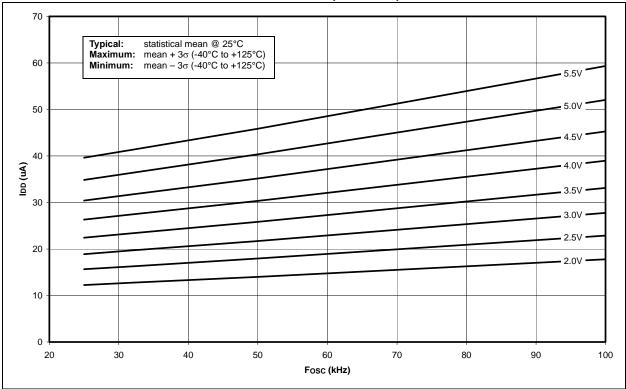

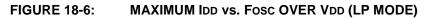

FIGURE 18-5: TYPICAL IDD vs. Fosc OVER VDD (LP MODE)

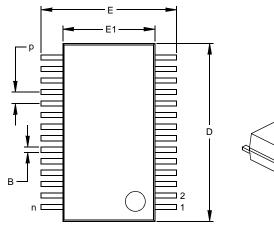

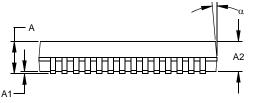

### 28-Lead Plastic Shrink Small Outline (SS) - 209 mil, 5.30 mm (SSOP)

Note: For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

|                          | Units    |      | INCHES |      | N     | <b>1ILLIMETERS</b> | )*     |

|--------------------------|----------|------|--------|------|-------|--------------------|--------|

| Dimension                | n Limits | MIN  | NOM    | MAX  | MIN   | NOM                | MAX    |

| Number of Pins           | n        |      | 28     |      |       | 28                 |        |

| Pitch                    | р        |      | .026   |      |       | 0.65               |        |

| Overall Height           | Α        | .068 | .073   | .078 | 1.73  | 1.85               | 1.98   |

| Molded Package Thickness | A2       | .064 | .068   | .072 | 1.63  | 1.73               | 1.83   |

| Standoff §               | A1       | .002 | .006   | .010 | 0.05  | 0.15               | 0.25   |

| Overall Width            | E        | .299 | .309   | .319 | 7.59  | 7.85               | 8.10   |

| Molded Package Width     | E1       | .201 | .207   | .212 | 5.11  | 5.25               | 5.38   |

| Overall Length           | D        | .396 | .402   | .407 | 10.06 | 10.20              | 10.34  |

| Foot Length              | L        | .022 | .030   | .037 | 0.56  | 0.75               | 0.94   |

| Lead Thickness           | С        | .004 | .007   | .010 | 0.10  | 0.18               | 0.25   |

| Foot Angle               | φ        | 0    | 4      | 8    | 0.00  | 101.60             | 203.20 |

| Lead Width               | В        | .010 | .013   | .015 | 0.25  | 0.32               | 0.38   |

| Mold Draft Angle Top     | α        | 0    | 5      | 10   | 0     | 5                  | 10     |

| Mold Draft Angle Bottom  | β        | 0    | 5      | 10   | 0     | 5                  | 10     |

\* Controlling Parameter § Significant Characteristic

Notes:

Dimensions D and E1 do not include mold flash or protrusions. Mold flash or protrusions shall not exceed .010" (0.254mm) per side. JEDEC Equivalent: MS-150

Drawing No. C04-073

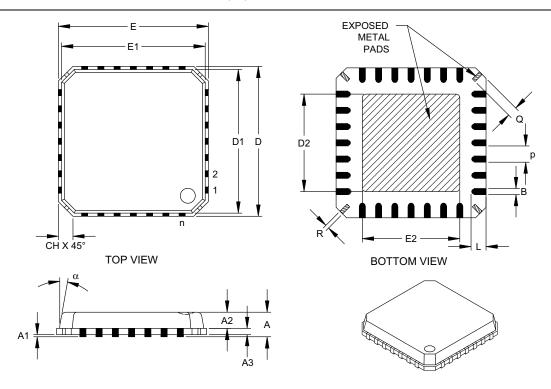

# 28-Lead Plastic Quad Flat No Lead Package (ML) 6x6 mm Body, Punch Singulated (QFN)

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

|                          | Units  |      | INCHES   |      | М    | ILLIMETERS | k .  |

|--------------------------|--------|------|----------|------|------|------------|------|

| Dimension                | Limits | MIN  | NOM      | MAX  | MIN  | NOM        | MAX  |

| Number of Pins           | n      |      | 28       |      |      | 28         |      |

| Pitch                    | р      |      | .026 BSC |      |      | 0.65 BSC   |      |

| Overall Height           | Α      |      | .033     | .039 |      | 0.85       | 1.00 |

| Molded Package Thickness | A2     |      | .026     | .031 |      | 0.65       | 0.80 |

| Standoff                 | A1     | .000 | .0004    | .002 | 0.00 | 0.01       | 0.05 |

| Base Thickness           | A3     |      | .008 REF |      |      | 0.20 REF   |      |

| Overall Width            | E      |      | .236 BSC |      |      | 6.00 BSC   |      |

| Molded Package Width     | E1     |      | .226 BSC |      |      | 5.75 BSC   |      |

| Exposed Pad Width        | E2     | .140 | .146     | .152 | 3.55 | 3.70       | 3.85 |

| Overall Length           | D      |      | .236 BSC |      |      | 6.00 BSC   |      |

| Molded Package Length    | D1     |      | .226 BSC |      |      | 5.75 BSC   |      |

| Exposed Pad Length       | D2     | .140 | .146     | .152 | 3.55 | 3.70       | 3.85 |

| Lead Width               | В      | .009 | .011     | .014 | 0.23 | 0.28       | 0.35 |

| Lead Length              | L      | .020 | .024     | .030 | 0.50 | 0.60       | 0.75 |

| Tie Bar Width            | R      | .005 | .007     | .010 | 0.13 | 0.17       | 0.23 |

| Tie Bar Length           | Q      | .012 | .016     | .026 | 0.30 | 0.40       | 0.65 |

| Chamfer                  | СН     | .009 | .017     | .024 | 0.24 | 0.42       | 0.60 |

| Mold Draft Angle Top     | α      |      |          | 12°  |      |            | 12°  |

\*Controlling Parameter

Notes:

Dimensions D and E1 do not include mold flash or protrusions. Mold flash or protrusions shall not exceed .010" (0.254mm) per side. JEDEC equivalent: mMO-220

Drawing No. C04-114

| MPLAB ICE 4000 High-Performance Universal    |

|----------------------------------------------|

| In-Circuit Emulator169                       |

| MPLAB Integrated Development                 |

| Environment Software167                      |

| MPLINK Object Linker/MPLIB Object Librarian  |

| MSSP71                                       |

| I <sup>2</sup> C Mode. See I <sup>2</sup> C. |

| SPI Mode71                                   |

| SPI Mode. See SPI.                           |

| MSSP Module                                  |

| Clock Stretching90                           |

| Clock Synchronization and the CKP Bit91      |

| Control Registers (General)71                |

| Operation84                                  |

| Overview71                                   |

| SPI Master Mode76                            |

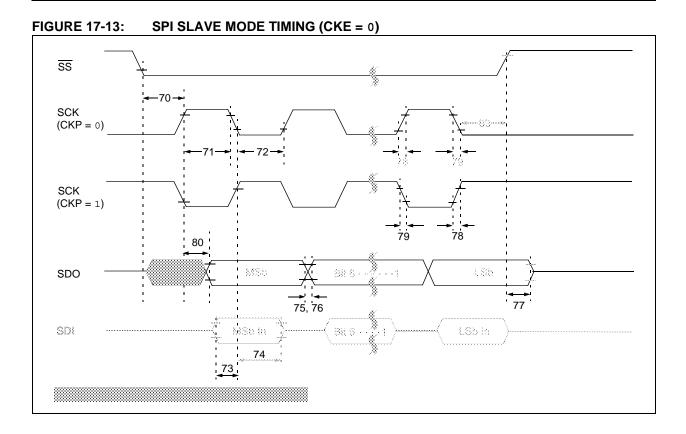

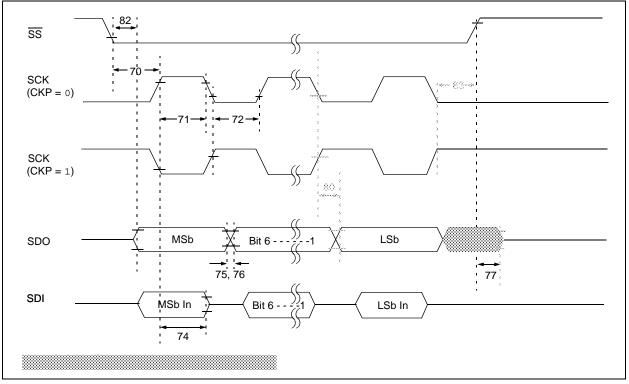

| SPI Slave Mode77                             |

| SSPBUF                                       |

| SSPSR76                                      |

| Multi-Master Mode105                         |

# 0

| Opcode Field Descriptions       |               |

|---------------------------------|---------------|

| OPTION_REG Register             |               |

| INTEDG Bit                      |               |

| PS2:PS0 Bits                    |               |

| PSA Bit                         |               |

| RBPU Bit                        |               |

| T0CS Bit                        |               |

| T0SE Bit                        |               |

| OSC1/CLKI Pin                   |               |

| OSC2/CLKO Pin                   |               |

| Oscillator Configuration        |               |

| HS                              |               |

| LP                              |               |

| RC                              | 145, 146, 149 |

| XT                              |               |

| Oscillator Selection            |               |

| Oscillator Start-up Timer (OST) |               |

| Oscillator, WDT                 |               |

| Oscillators                     |               |

| Capacitor Selection             |               |

| Ceramic Resonator Selection     |               |

| Crystal and Ceramic Resonators  |               |

| RC                              |               |

|                                 |               |

# Ρ

| Package Information                      |                 |

|------------------------------------------|-----------------|

| Marking                                  |                 |

| Packaging Information                    |                 |

| Paging, Program Memory                   |                 |

| Parallel Slave Port (PSP)                | 13, 48, 51      |

| Associated Registers                     |                 |

| RE0/RD/AN5 Pin                           |                 |

| RE1/WR/AN6 Pin                           | 49, 51          |

| RE2/CS/AN7 Pin                           |                 |

| Select (PSPMODE Bit)                     | .48, 49, 50, 51 |

| Parallel Slave Port Requirements         |                 |

| (PIC16F874A/ 877A Only)                  |                 |

| PCL Register                             |                 |

| PCLATH Register                          | 19, 20, 30      |

| PCON Register                            |                 |

| BOR Bit                                  |                 |

| POR Bit                                  | 29              |

| PIC16F87XA Product Identification System |                 |

| PICkit 1 Flash Starter Kit               | 171             |

| PICSTART Plus Development Programmer                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                               |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------|

| PIE1 Register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                               |

| PIE2 Register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 20, 27                                                                        |

| Pinout Descriptions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                               |

| PIC16F873A/PIC16F876A                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                               |

| PIR1 Register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                               |

| PIR2 Register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                               |