Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                     |

|----------------------------|----------------------------------------------------------------------------|

| Core Processor             | PIC                                                                        |

| Core Size                  | 8-Bit                                                                      |

| Speed                      | 10MHz                                                                      |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                          |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                      |

| Number of I/O              | 33                                                                         |

| Program Memory Size        | 7KB (4K x 14)                                                              |

| Program Memory Type        | FLASH                                                                      |

| EEPROM Size                | 128 x 8                                                                    |

| RAM Size                   | 192 x 8                                                                    |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 5.5V                                                                  |

| Data Converters            | A/D 8x10b                                                                  |

| Oscillator Type            | External                                                                   |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                          |

| Mounting Type              | Surface Mount                                                              |

| Package / Case             | 44-TQFP                                                                    |

| Supplier Device Package    | 44-TQFP (10x10)                                                            |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16lf874a-i-pt |

|                            |                                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## PIC16F87XA

NOTES:

## 2.0 MEMORY ORGANIZATION

There are three memory blocks in each of the PIC16F87XA devices. The program memory and data memory have separate buses so that concurrent access can occur and is detailed in this section. The EEPROM data memory block is detailed in **Section 3.0 "Data EEPROM and Flash Program Memory"**.

Additional information on device memory may be found in the PIC<sup>®</sup> Mid-Range MCU Family Reference Manual (DS33023).

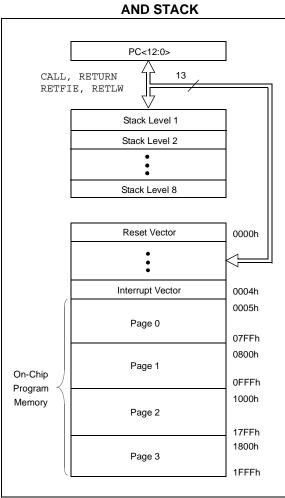

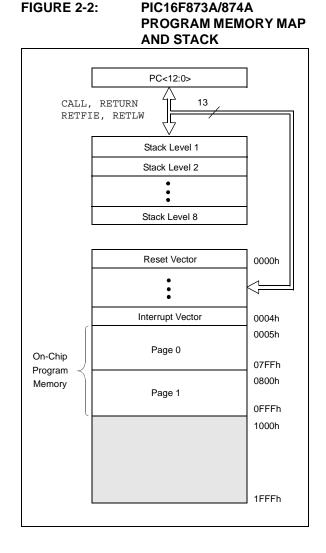

#### FIGURE 2-1: PIC16F876A/877A PROGRAM MEMORY MAP AND STACK

### 2.1 Program Memory Organization

The PIC16F87XA devices have a 13-bit program counter capable of addressing an 8K word x 14 bit program memory space. The PIC16F876A/877A devices have 8K words x 14 bits of Flash program memory, while PIC16F873A/874A devices have 4K words x 14 bits. Accessing a location above the physically implemented address will cause a wraparound.

The Reset vector is at 0000h and the interrupt vector is at 0004h.

## 2.2 Data Memory Organization

The data memory is partitioned into multiple banks which contain the General Purpose Registers and the Special Function Registers. Bits RP1 (Status<6>) and RP0 (Status<5>) are the bank select bits.

| RP1:RP0 | Bank |

|---------|------|

| 00      | 0    |

| 01      | 1    |

| 10      | 2    |

| 11      | 3    |

Each bank extends up to 7Fh (128 bytes). The lower locations of each bank are reserved for the Special Function Registers. Above the Special Function Registers are General Purpose Registers, implemented as static RAM. All implemented banks contain Special Function Registers. Some frequently used Special Function Registers from one bank may be mirrored in another bank for code reduction and quicker access.

| Note: | The EEPROM data memory description can |

|-------|----------------------------------------|

|       | be found in Section 3.0 "Data EEPROM   |

|       | and Flash Program Memory" of this data |

|       | sheet.                                 |

#### 2.2.1 GENERAL PURPOSE REGISTER FILE

The register file can be accessed either directly, or indirectly, through the File Select Register (FSR).

| Name                | Bit#  | Buffer | Function                                                                                             |

|---------------------|-------|--------|------------------------------------------------------------------------------------------------------|

| RA0/AN0             | bit 0 | TTL    | Input/output or analog input.                                                                        |

| RA1/AN1             | bit 1 | TTL    | Input/output or analog input.                                                                        |

| RA2/AN2/VREF-/CVREF | bit 2 | TTL    | Input/output or analog input or VREF- or CVREF.                                                      |

| RA3/AN3/VREF+       | bit 3 | TTL    | Input/output or analog input or VREF+.                                                               |

| RA4/T0CKI/C1OUT     | bit 4 | ST     | Input/output or external clock input for Timer0 or comparator output.<br>Output is open-drain type.  |

| RA5/AN4/SS/C2OUT    | bit 5 | TTL    | Input/output or analog input or slave select input for synchronous serial port or comparator output. |

#### TABLE 4-1: PORTA FUNCTIONS

Legend: TTL = TTL input, ST = Schmitt Trigger input

#### TABLE 4-2: SUMMARY OF REGISTERS ASSOCIATED WITH PORTA

| Address | Name   | Bit 7 | Bit 6 | Bit 5   | Bit 4      | Bit 3      | Bit 2 | Bit 1 | Bit 0 | Value on:<br>POR, BOR | Value on<br>all other<br>Resets |

|---------|--------|-------|-------|---------|------------|------------|-------|-------|-------|-----------------------|---------------------------------|

| 05h     | PORTA  | —     | —     | RA5     | RA4        | RA3        | RA2   | RA1   | RA0   | 0x 0000               | 0u 0000                         |

| 85h     | TRISA  | _     | _     | PORTA D | ata Direct | ion Regist | er    |       |       | 11 1111               | 11 1111                         |

| 9Ch     | CMCON  | C2OUT | C10UT | C2INV   | C1INV      | CIS        | CM2   | CM1   | CM0   | 0000 0111             | 0000 0111                       |

| 9Dh     | CVRCON | CVREN | CVROE | CVRR    | —          | CVR3       | CVR2  | CVR1  | CVR0  | 000- 0000             | 000- 0000                       |

| 9Fh     | ADCON1 | ADFM  | ADCS2 |         | _          | PCFG3      | PCFG2 | PCFG1 | PCFG0 | 00 0000               | 00 0000                         |

Legend: x = unknown, u = unchanged, - = unimplemented locations read as '0'. Shaded cells are not used by PORTA.

Note: When using the SSP module in SPI Slave mode and  $\overline{SS}$  enabled, the A/D converter must be set to one of the following modes, where PCFG3:PCFG0 = 0100, 0101, 011x, 1101, 1110, 1111.

#### 4.5 PORTE and TRISE Register

| Note: | PORTE and TRISE are not implemented |

|-------|-------------------------------------|

|       | on the 28-pin devices.              |

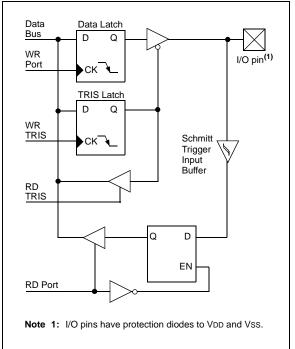

PORTE has three pins (RE0/RD/AN5, RE1/WR/AN6 and RE2/CS/AN7) which are individually configurable as inputs or outputs. These pins have Schmitt Trigger input buffers.

The PORTE pins become the I/O control inputs for the microprocessor port when bit PSPMODE (TRISE<4>) is set. In this mode, the user must make certain that the TRISE<2:0> bits are set and that the pins are configured as digital inputs. Also, ensure that ADCON1 is configured for digital I/O. In this mode, the input buffers are TTL.

Register 4-1 shows the TRISE register which also controls the Parallel Slave Port operation.

PORTE pins are multiplexed with analog inputs. When selected for analog input, these pins will read as '0's.

TRISE controls the direction of the RE pins, even when they are being used as analog inputs. The user must make sure to keep the pins configured as inputs when using them as analog inputs.

Note: On a Power-on Reset, these pins are configured as analog inputs and read as '0'.

#### TABLE 4-9: PORTE FUNCTIONS

#### FIGURE 4-9:

#### PORTE BLOCK DIAGRAM (IN I/O PORT MODE)

| Name       | Bit#  | Buffer Type           | Function                                                                                                                                                                                                                                   |

|------------|-------|-----------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| RE0/RD/AN5 | bit 0 | ST/TTL <sup>(1)</sup> | <ul> <li>I/O port pin or read control input in Parallel Slave Port mode or analog input:</li> <li>RD</li> <li>1 = Idle</li> <li>0 = Read operation. Contents of PORTD register are output to PORTD I/O pins (if chip selected).</li> </ul> |

| RE1/WR/AN6 | bit 1 | ST/TTL <sup>(1)</sup> | <ul> <li>I/O port pin or write control input in Parallel Slave Port mode or analog input:<br/>WR</li> <li>1 = Idle</li> <li>0 = Write operation. Value of PORTD I/O pins is latched into PORTD register (if chip selected).</li> </ul>     |

| RE2/CS/AN7 | bit 2 | ST/TTL <sup>(1)</sup> | <ul> <li>I/O port pin or chip select control input in Parallel Slave Port mode or analog input:</li> <li>CS</li> <li>1 = Device is not selected</li> <li>0 = Device is selected</li> </ul>                                                 |

Legend: ST = Schmitt Trigger input, TTL = TTL input

Note 1: Input buffers are Schmitt Triggers when in I/O mode and TTL buffers when in Parallel Slave Port mode.

## PIC16F87XA

| REGISTER 8-1: | CCP1CON REGISTER/CCP2CON REGISTER (ADDRESS 17h/1Dh)                                                                                    |                                                                                                                                    |                                                                                                                                   |                                                                                                    |                                                                                                         |                                              |               |            |  |  |

|---------------|----------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------|----------------------------------------------|---------------|------------|--|--|

|               | U-0                                                                                                                                    | U-0                                                                                                                                | R/W-0                                                                                                                             | R/W-0                                                                                              | R/W-0                                                                                                   | R/W-0                                        | R/W-0         | R/W-0      |  |  |

|               | —                                                                                                                                      | _                                                                                                                                  | CCPxX                                                                                                                             | CCPxY                                                                                              | CCPxM3                                                                                                  | CCPxM2                                       | CCPxM1        | CCPxM0     |  |  |

|               | bit 7                                                                                                                                  |                                                                                                                                    |                                                                                                                                   |                                                                                                    |                                                                                                         |                                              |               | bit 0      |  |  |

| bit 7-6       | Unimplem                                                                                                                               | ented: Rea                                                                                                                         | <b>d as</b> '0'                                                                                                                   |                                                                                                    |                                                                                                         |                                              |               |            |  |  |

| bit 5-4       | CCPxX:CC                                                                                                                               | PxY: PWM                                                                                                                           | Least Sign                                                                                                                        | ificant bits                                                                                       |                                                                                                         |                                              |               |            |  |  |

|               | <u>Capture mo</u><br>Unused.                                                                                                           | ode:                                                                                                                               |                                                                                                                                   |                                                                                                    |                                                                                                         |                                              |               |            |  |  |

|               | <u>Compare n</u><br>Unused.                                                                                                            | <u>node:</u>                                                                                                                       |                                                                                                                                   |                                                                                                    |                                                                                                         |                                              |               |            |  |  |

|               | <u>PWM mode</u><br>These bits                                                                                                          |                                                                                                                                    | LSbs of the                                                                                                                       | e PWM duty                                                                                         | cycle. The eig                                                                                          | jht MSbs ar                                  | e found in C  | CPRxL.     |  |  |

| bit 3-0       | CCPxM3:C                                                                                                                               | CPxM0: C                                                                                                                           | CPx Mode S                                                                                                                        | Select bits                                                                                        |                                                                                                         |                                              |               |            |  |  |

|               | 0100 = Ca<br>0101 = Ca<br>0110 = Ca<br>0111 = Ca<br>1000 = Co<br>1001 = Co<br>1010 = Co<br>una<br>1011 = Co<br>res<br>ena<br>11xx = PW | pture mode<br>pture mode<br>pture mode<br>mpare mode<br>mpare mode<br>mpare mode<br>affected)<br>mpare mode<br>ets TMR1;<br>abled) | , every fallir<br>, every risin<br>, every 4th r<br>, every 16th<br>e, set outpu<br>e, clear outp<br>e, generate<br>e, trigger sp | ng edge<br>g edge<br>rising edge<br>t on match (<br>out on match<br>software int<br>ecial event (f | ets CCPx mod<br>CCPxIF bit is<br>a (CCPxIF bit i<br>errupt on mat<br>CCPxIF bit is s<br>and starts an A | set)<br>is set)<br>ch (CCPxIF<br>set, CCPx p | in is unaffec | ted); CCP1 |  |  |

|               | Legend:                                                                                                                                |                                                                                                                                    |                                                                                                                                   |                                                                                                    |                                                                                                         |                                              |               |            |  |  |

|               | R = Reada                                                                                                                              | ble bit                                                                                                                            |                                                                                                                                   | Vritable bit                                                                                       | •                                                                                                       |                                              | oit, read as  | ʻ0'        |  |  |

|               | - n = Value                                                                                                                            | at POR                                                                                                                             | '1' = E                                                                                                                           | Bit is set                                                                                         | '0' = Bit is                                                                                            | cleared                                      | x = Bit is u  | nknown     |  |  |

#### 9.3.1 REGISTERS

The MSSP module has four registers for SPI mode operation. These are:

- MSSP Control Register (SSPCON)

- MSSP Status Register (SSPSTAT)

- Serial Receive/Transmit Buffer Register (SSPBUF)

- MSSP Shift Register (SSPSR) Not directly accessible

SSPCON and SSPSTAT are the control and status registers in SPI mode operation. The SSPCON register is readable and writable. The lower six bits of the SSPSTAT are read-only. The upper two bits of the SSPSTAT are read/write. SSPSR is the shift register used for shifting data in or out. SSPBUF is the buffer register to which data bytes are written to or read from.

In receive operations, SSPSR and SSPBUF together create a double-buffered receiver. When SSPSR receives a complete byte, it is transferred to SSPBUF and the SSPIF interrupt is set.

During transmission, the SSPBUF is not doublebuffered. A write to SSPBUF will write to both SSPBUF and SSPSR.

#### REGISTER 9-1: SSPSTAT: MSSP STATUS REGISTER (SPI MODE) (ADDRESS 94h)

|       | R/W-0                                | R/W-0                                                                         | R-0             | R-0          | R-0           | R-0           | R-0          | R-0           |  |  |

|-------|--------------------------------------|-------------------------------------------------------------------------------|-----------------|--------------|---------------|---------------|--------------|---------------|--|--|

|       | SMP                                  | CKE                                                                           | D/A             | Р            | S             | R/W           | UA           | BF            |  |  |

|       | bit 7                                |                                                                               |                 |              |               |               |              | bit 0         |  |  |

| bit 7 | SMP: Sam                             | ple bit                                                                       |                 |              |               |               |              |               |  |  |

|       | SPI Master                           |                                                                               |                 |              |               |               |              |               |  |  |

|       |                                      | ata sampled                                                                   |                 |              |               |               |              |               |  |  |

|       |                                      | 0 = Input data sampled at middle of data output time                          |                 |              |               |               |              |               |  |  |

|       |                                      | <u>SPI Slave mode:</u><br>SMP must be cleared when SPI is used in Slave mode. |                 |              |               |               |              |               |  |  |

| bit 6 |                                      | CKE: SPI Clock Select bit                                                     |                 |              |               |               |              |               |  |  |

|       | 1 = Transm                           | nit occurs on                                                                 | transition fr   | om active to | ldle clock s  | state         |              |               |  |  |

|       | 0 = Transm                           | nit occurs on                                                                 | transition fr   | om Idle to a | ctive clock s | state         |              |               |  |  |

|       | Note:                                | Polarity of o                                                                 | clock state is  | s set by the | CKP bit (SS   | PCON1<4>      | ).           |               |  |  |

| bit 5 | D/A: Data/                           | Address bit                                                                   |                 |              |               |               |              |               |  |  |

|       | Used in I <sup>2</sup> C             | c mode only.                                                                  |                 |              |               |               |              |               |  |  |

| bit 4 | P: Stop bit                          |                                                                               |                 |              |               |               |              |               |  |  |

|       | Used in I <sup>2</sup> C             | mode only.                                                                    | This bit is cle | ared when t  | he MSSP me    | odule is disa | bled, SSPEI  | N is cleared. |  |  |

| bit 3 | S: Start bit                         |                                                                               |                 |              |               |               |              |               |  |  |

|       | Used in I <sup>2</sup> C             | c mode only.                                                                  |                 |              |               |               |              |               |  |  |

| bit 2 | R/W: Read                            | I/Write bit inf                                                               | ormation        |              |               |               |              |               |  |  |

|       | Used in I <sup>2</sup> C             | c mode only.                                                                  |                 |              |               |               |              |               |  |  |

| bit 1 | UA: Update                           | e Address b                                                                   | it              |              |               |               |              |               |  |  |

|       | Used in I <sup>2</sup> C             | c mode only.                                                                  |                 |              |               |               |              |               |  |  |

| bit 0 | BF: Buffer                           | Full Status b                                                                 | oit (Receive    | mode only)   |               |               |              |               |  |  |

|       | 1 = Receive complete, SSPBUF is full |                                                                               |                 |              |               |               |              |               |  |  |

|       | 0 = Receiv                           | e not comple                                                                  | ete, SSPBU      | F is empty   |               |               |              |               |  |  |

|       | Legend:                              |                                                                               |                 |              |               |               |              |               |  |  |

|       | R = Reada                            | ble bit                                                                       | W = W           | ritable bit  | U = Unim      | plemented     | bit, read as | '0'           |  |  |

|       | - n = Value                          | at POR                                                                        | '1' = B         | it is set    | '0' = Bit i   | s cleared     | x = Bit is ι | Inknown       |  |  |

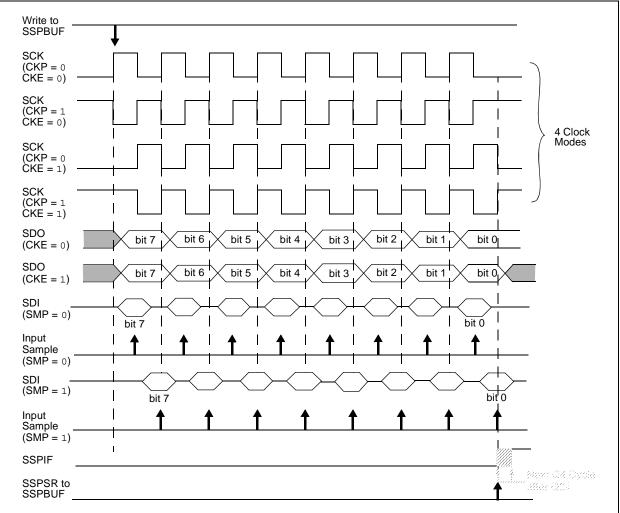

#### 9.3.5 MASTER MODE

The master can initiate the data transfer at any time because it controls the SCK. The master determines when the slave (Processor 2, Figure 9-2) is to broadcast data by the software protocol.

In Master mode, the data is transmitted/received as soon as the SSPBUF register is written to. If the SPI is only going to receive, the SDO output could be disabled (programmed as an input). The SSPSR register will continue to shift in the signal present on the SDI pin at the programmed clock rate. As each byte is received, it will be loaded into the SSPBUF register as if a normal received byte (interrupts and status bits appropriately set). This could be useful in receiver applications as a "Line Activity Monitor" mode.

The clock polarity is selected by appropriately programming the CKP bit (SSPCON<4>). This then, would give waveforms for SPI communication as shown in Figure 9-3, Figure 9-5 and Figure 9-6, where the MSB is transmitted first. In Master mode, the SPI clock rate (bit rate) is user programmable to be one of the following:

- Fosc/4 (or Tcy)

- Fosc/16 (or 4 Tcy)

- Fosc/64 (or 16 Tcy)

- Timer2 output/2

This allows a maximum data rate (at 40 MHz) of 10.00 Mbps.

Figure 9-3 shows the waveforms for Master mode. When the CKE bit is set, the SDO data is valid before there is a clock edge on SCK. The change of the input sample is shown based on the state of the SMP bit. The time when the SSPBUF is loaded with the received data is shown.

#### FIGURE 9-3: SPI MODE WAVEFORM (MASTER MODE)

|                                                                                                                                | R/W-0                                                                                                                                                                                              | R/W-0                               | R/W-0         | R/W-0         | R/W-0         | R/W-0       | R/W-0        | R/W-0      |  |

|--------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------|---------------|---------------|---------------|-------------|--------------|------------|--|

|                                                                                                                                | GCEN                                                                                                                                                                                               | ACKSTAT                             | ACKDT         | ACKEN         | RCEN          | PEN         | RSEN         | SEN        |  |

|                                                                                                                                | bit 7                                                                                                                                                                                              | 1                                   |               | I             |               | I           | I            | bit 0      |  |

| bit 7                                                                                                                          |                                                                                                                                                                                                    | eneral Call En                      |               | -             | -             |             |              |            |  |

|                                                                                                                                |                                                                                                                                                                                                    | e interrupt whe<br>ral call address |               | call address  | (0000h) is    | received in | the SSPSF    | 2          |  |

| bit 6                                                                                                                          | ACKSTA                                                                                                                                                                                             | <b>f:</b> Acknowledg                | e Status bit  | (Master Tran  | smit mode o   | only)       |              |            |  |

|                                                                                                                                |                                                                                                                                                                                                    | wledge was n<br>wledge was re       |               |               |               |             |              |            |  |

| bit 5                                                                                                                          | ACKDT: A                                                                                                                                                                                           | Acknowledge [                       | Data bit (Mas | ster Receive  | mode only)    |             |              |            |  |

|                                                                                                                                | 1 = Not A<br>0 = Ackno                                                                                                                                                                             | cknowledge<br>wledge                |               |               |               |             |              |            |  |

|                                                                                                                                | Note:                                                                                                                                                                                              | Value that w the end of a           |               | itted when th | e user initia | tes an Ackr | nowledge se  | equence at |  |

| bit 4                                                                                                                          | ACKEN:                                                                                                                                                                                             | Acknowledge                         | Sequence E    | nable bit (Ma | ster Receiv   | e mode on   | ly)          |            |  |

|                                                                                                                                | <ul> <li>1 = Initiate Acknowledge sequence on SDA and SCL pins and transmit ACKDT data bit.<br/>Automatically cleared by hardware.</li> <li>0 = Acknowledge sequence Idle</li> </ul>               |                                     |               |               |               |             |              |            |  |

| bit 3                                                                                                                          | RCEN: R                                                                                                                                                                                            | eceive Enable                       | bit (Master i | mode only)    |               |             |              |            |  |

|                                                                                                                                | <ul> <li>1 = Enables Receive mode for I<sup>2</sup>C</li> <li>0 = Receive Idle</li> </ul>                                                                                                          |                                     |               |               |               |             |              |            |  |

| bit 2                                                                                                                          | PEN: Stop Condition Enable bit (Master mode only)                                                                                                                                                  |                                     |               |               |               |             |              |            |  |

|                                                                                                                                | <ul> <li>1 = Initiate Stop condition on SDA and SCL pins. Automatically cleared by hardware.</li> <li>0 = Stop condition Idle</li> </ul>                                                           |                                     |               |               |               |             | re.          |            |  |

| bit 1                                                                                                                          | RSEN: Repeated Start Condition Enabled bit (Master mode only)                                                                                                                                      |                                     |               |               |               |             |              |            |  |

|                                                                                                                                | <ul> <li>1 = Initiate Repeated Start condition on SDA and SCL pins. Automatically cleared by hardware.</li> <li>0 = Repeated Start condition Idle</li> </ul>                                       |                                     |               |               |               |             |              |            |  |

| bit 0                                                                                                                          | SEN: Star                                                                                                                                                                                          | t Condition En                      | abled/Streto  | h Enabled bi  | t             |             |              |            |  |

| In Master mode:<br>1 = Initiate Start condition on SDA and SCL pins. Automatically cleared by harc<br>0 = Start condition Idle |                                                                                                                                                                                                    |                                     |               |               | by hardwa     | re.         |              |            |  |

|                                                                                                                                | In Slave mode:<br>1 = Clock stretching is enabled for both slave transmit and slave receive (stretch enabled)<br>0 = Clock stretching is enabled for slave transmit only (PIC16F87X compatibility) |                                     |               |               |               |             |              |            |  |

|                                                                                                                                | Legend:                                                                                                                                                                                            |                                     |               |               |               |             |              |            |  |

|                                                                                                                                | R = Read                                                                                                                                                                                           |                                     |               | itable bit    | -             |             | bit, read as |            |  |

|                                                                                                                                | - n = Valu                                                                                                                                                                                         | e at POR                            | '1' = Bit     | is set        | '0' = Bit is  | cleared     | x = Bit is ι | unknown    |  |

**Note:** For bits ACKEN, RCEN, PEN, RSEN, SEN: If the I<sup>2</sup>C module is not in the Idle mode, this bit may not be set (no spooling) and the SSPBUF may not be written (or writes to the SSPBUF are disabled).

### 10.2 USART Asynchronous Mode

In this mode, the USART uses standard Non-Returnto-Zero (NRZ) format (one Start bit, eight or nine data bits and one Stop bit). The most common data format is 8 bits. An on-chip, dedicated, 8-bit Baud Rate Generator can be used to derive standard baud rate frequencies from the oscillator. The USART transmits and receives the LSb first. The transmitter and receiver are functionally independent but use the same data format and baud rate. The baud rate generator produces a clock, either x16 or x64 of the bit shift rate, depending on bit BRGH (TXSTA<2>). Parity is not supported by the hardware but can be implemented in software (and stored as the ninth data bit). Asynchronous mode is stopped during Sleep.

Asynchronous mode is selected by clearing bit SYNC (TXSTA<4>).

The USART Asynchronous module consists of the following important elements:

- Baud Rate Generator

- Sampling Circuit

- Asynchronous Transmitter

- Asynchronous Receiver

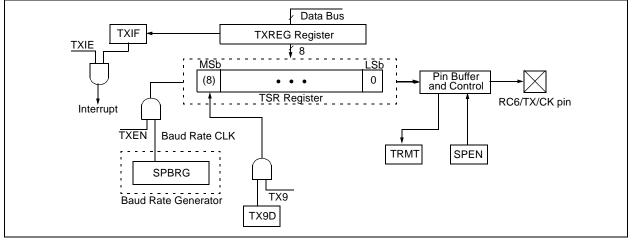

#### 10.2.1 USART ASYNCHRONOUS TRANSMITTER

The USART transmitter block diagram is shown in Figure 10-1. The heart of the transmitter is the Transmit (Serial) Shift Register (TSR). The shift register obtains its data from the Read/Write Transmit Buffer, TXREG. The TXREG register is loaded with data in software. The TSR register is not loaded until the Stop bit has been transmitted from the previous load. As soon as the Stop bit is transmitted, the TSR is loaded with new data from the TXREG register (if available). Once the TXREG register transfers the data to the TSR register (occurs in one TcY), the TXREG register is empty and flag bit, TXIF (PIR1<4>), is set. This interrupt can be

enabled/disabled by setting/clearing enable bit, TXIE (PIE1<4>). Flag bit TXIF will be set regardless of the state of enable bit TXIE and cannot be cleared in software. It will reset only when new data is loaded into the TXREG register. While flag bit TXIF indicates the status of the TXREG register, another bit, TRMT (TXSTA<1>), shows the status of the TSR register. Status bit TRMT is a read-only bit which is set when the TSR register is empty. No interrupt logic is tied to this bit so the user has to poll this bit in order to determine if the TSR register is empty.

- **Note 1:** The TSR register is not mapped in data memory so it is not available to the user.

- 2: Flag bit TXIF is set when enable bit TXEN is set. TXIF is cleared by loading TXREG.

Transmission is enabled by setting enable bit, TXEN (TXSTA<5>). The actual transmission will not occur until the TXREG register has been loaded with data and the Baud Rate Generator (BRG) has produced a shift clock (Figure 10-2). The transmission can also be started by first loading the TXREG register and then setting enable bit TXEN. Normally, when transmission is first started, the TSR register is empty. At that point, transfer to the TXREG register will result in an immediate transfer to TSR, resulting in an empty TXREG. A back-to-back transfer is thus possible (Figure 10-3). Clearing enable bit TXEN during a transmission will cause the transmission to be aborted and will reset the transmitter. As a result, the RC6/TX/CK pin will revert to high-impedance.

In order to select 9-bit transmission, transmit bit TX9 (TXSTA<6>) should be set and the ninth bit should be written to TX9D (TXSTA<0>). The ninth bit must be written before writing the 8-bit data to the TXREG register. This is because a data write to the TXREG register can result in an immediate transfer of the data to the TSR register (if the TSR is empty). In such a case, an incorrect ninth data bit may be loaded in the TSR register.

| SWAPF            | Swap Nibbles in f                                                                                                                                                      |

|------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [ label ] SWAPF f,d                                                                                                                                                    |

| Operands:        | $\begin{array}{l} 0\leq f\leq 127\\ d\in [0,1] \end{array}$                                                                                                            |

| Operation:       | $(f<3:0>) \rightarrow (destination<7:4>), (f<7:4>) \rightarrow (destination<3:0>)$                                                                                     |

| Status Affected: | None                                                                                                                                                                   |

| Description:     | The upper and lower nibbles of register 'f' are exchanged. If 'd' is '0', the result is placed in the W register. If 'd' is '1', the result is placed in register 'f'. |

| XORWF            | Exclusive OR W with f                                                                                                                                                           |

|------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [label] XORWF f,d                                                                                                                                                               |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ d  \in  [0,1] \end{array}$                                                                                                               |

| Operation:       | (W) .XOR. (f) $\rightarrow$ (destination)                                                                                                                                       |

| Status Affected: | Z                                                                                                                                                                               |

| Description:     | Exclusive OR the contents of the W register with register 'f'. If 'd' is '0', the result is stored in the W register. If 'd' is '1', the result is stored back in register 'f'. |

| XORLW            | Exclusive OR Literal with W                                                                                                |  |  |  |  |

|------------------|----------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| Syntax:          | [label] XORLW k                                                                                                            |  |  |  |  |

| Operands:        | $0 \leq k \leq 255$                                                                                                        |  |  |  |  |

| Operation:       | (W) .XOR. $k \rightarrow (W)$                                                                                              |  |  |  |  |

| Status Affected: | Z                                                                                                                          |  |  |  |  |

| Description:     | The contents of the W register<br>are XOR'ed with the eight-bit<br>literal 'k'. The result is placed in<br>the W register. |  |  |  |  |

## 16.9 MPLAB ICE 2000 High Performance Universal In-Circuit Emulator

The MPLAB ICE 2000 universal in-circuit emulator is intended to provide the product development engineer with a complete microcontroller design tool set for PIC microcontrollers. Software control of the MPLAB ICE 2000 in-circuit emulator is advanced by the MPLAB Integrated Development Environment, which allows editing, building, downloading and source debugging from a single environment.

The MPLAB ICE 2000 is a full-featured emulator system with enhanced trace, trigger and data monitoring features. Interchangeable processor modules allow the system to be easily reconfigured for emulation of different processors. The universal architecture of the MPLAB ICE in-circuit emulator allows expansion to support new PIC microcontrollers.

The MPLAB ICE 2000 in-circuit emulator system has been designed as a real-time emulation system with advanced features that are typically found on more expensive development tools. The PC platform and Microsoft<sup>®</sup> Windows 32-bit operating system were chosen to best make these features available in a simple, unified application.

## 16.10 MPLAB ICE 4000 High Performance Universal In-Circuit Emulator

The MPLAB ICE 4000 universal in-circuit emulator is intended to provide the product development engineer with a complete microcontroller design tool set for highend PIC microcontrollers. Software control of the MPLAB ICE in-circuit emulator is provided by the MPLAB Integrated Development Environment, which allows editing, building, downloading and source debugging from a single environment.

The MPLAB ICD 4000 is a premium emulator system, providing the features of MPLAB ICE 2000, but with increased emulation memory and high speed performance for dsPIC30F and PIC18XXXX devices. Its advanced emulator features include complex triggering and timing, up to 2 Mb of emulation memory, and the ability to view variables in real-time.

The MPLAB ICE 4000 in-circuit emulator system has been designed as a real-time emulation system with advanced features that are typically found on more expensive development tools. The PC platform and Microsoft Windows 32-bit operating system were chosen to best make these features available in a simple, unified application.

## 16.11 MPLAB ICD 2 In-Circuit Debugger

Microchip's In-Circuit Debugger, MPLAB ICD 2, is a powerful, low-cost, run-time development tool, connecting to the host PC via an RS-232 or high-speed USB interface. This tool is based on the Flash PIC MCUs and can be used to develop for these and other PIC microcontrollers. The MPLAB ICD 2 utilizes the incircuit debugging capability built into the Flash devices. This feature, along with Microchip's In-Circuit Serial Programming<sup>™</sup> (ICSP<sup>™</sup>) protocol, offers cost effective in-circuit Flash debugging from the graphical user interface of the MPLAB Integrated Development Environment. This enables a designer to develop and debug source code by setting breakpoints, singlestepping and watching variables, CPU status and peripheral registers. Running at full speed enables testing hardware and applications in real-time. MPLAB ICD 2 also serves as a development programmer for selected PIC devices.

## 16.12 PRO MATE II Universal Device Programmer

The PRO MATE II is a universal, CE compliant device programmer with programmable voltage verification at VDDMIN and VDDMAX for maximum reliability. It features an LCD display for instructions and error messages and a modular detachable socket assembly to support various package types. In Stand-Alone mode, the PRO MATE II device programmer can read, verify, and program PIC devices without a PC connection. It can also set code protection in this mode.

### 16.13 PICSTART Plus Development Programmer

The PICSTART Plus development programmer is an easy-to-use, low-cost, prototype programmer. It connects to the PC via a COM (RS-232) port. MPLAB Integrated Development Environment software makes using the programmer simple and efficient. The PICSTART Plus development programmer supports most PIC devices up to 40 pins. Larger pin count devices, such as the PIC16C92X and PIC17C76X, may be supported with an adapter socket. The PICSTART Plus development programmer is CE compliant.

| Param<br>No. | Sym     | Characte                      | eristic      | Min         | Max  | Units | Conditions                              |

|--------------|---------|-------------------------------|--------------|-------------|------|-------|-----------------------------------------|

| 100          | Тнідн   | Clock High Time               | 100 kHz mode | 4.0         | _    | μs    |                                         |

|              |         |                               | 400 kHz mode | 0.6         | _    | μs    |                                         |

|              |         |                               | SSP Module   | 0.5 TCY     | _    |       |                                         |

| 101          | TLOW    | Clock Low Time                | 100 kHz mode | 4.7         | _    | μs    |                                         |

|              |         |                               | 400 kHz mode | 1.3         | _    | μs    |                                         |

|              |         |                               | SSP Module   | 0.5 TCY     | _    |       |                                         |

| 102          | TR      | SDA and SCL Rise              | 100 kHz mode | —           | 1000 | ns    |                                         |

|              | Time    |                               | 400 kHz mode | 20 + 0.1 Св | 300  | ns    | Cb is specified to be from 10 to 400 pF |

| 103          | TF      | SDA and SCL Fall              | 100 kHz mode | —           | 300  | ns    |                                         |

|              |         | Time                          | 400 kHz mode | 20 + 0.1 Св | 300  | ns    | CB is specified to be from 10 to 400 pF |

| 90           | TSU:STA | Start Condition Setup<br>Time | 100 kHz mode | 4.7         | _    | μs    | Only relevant for Repeated Start        |

|              |         |                               | 400 kHz mode | 0.6         | _    | μs    | condition                               |

| 91           | THD:STA | Start Condition Hold<br>Time  | 100 kHz mode | 4.0         | _    | μs    | After this period, the first clock      |

|              |         |                               | 400 kHz mode | 0.6         | _    | μs    | pulse is generated                      |

| 106          | THD:DAT | Data Input Hold Time          | 100 kHz mode | 0           | _    | ns    |                                         |

|              |         |                               | 400 kHz mode | 0           | 0.9  | μs    |                                         |

| 107          | TSU:DAT | Data Input Setup Time         | 100 kHz mode | 250         | _    | ns    | (Note 2)                                |

|              |         |                               | 400 kHz mode | 100         |      | ns    |                                         |

| 92           | Tsu:sto | Stop Condition Setup<br>Time  | 100 kHz mode | 4.7         | _    | μs    |                                         |

|              |         |                               | 400 kHz mode | 0.6         | _    | μs    |                                         |

| 109          | ΤΑΑ     | Output Valid from<br>Clock    | 100 kHz mode | _           | 3500 | ns    | (Note 1)                                |

|              |         |                               | 400 kHz mode | —           | —    | ns    |                                         |

| 110          | TBUF    | Bus Free Time                 | 100 kHz mode | 4.7         | _    | μs    | Time the bus must be free before        |

|              |         |                               | 400 kHz mode | 1.3         | _    | μs    | a new transmission can start            |

|              | Св      | Bus Capacitive Loading        | _            | 400         | pF   |       |                                         |

## TABLE 17-11: I<sup>2</sup>C BUS DATA REQUIREMENTS

**Note 1:** As a transmitter, the device must provide this internal minimum delay time to bridge the undefined region (min. 300 ns) of the falling edge of SCL to avoid unintended generation of Start or Stop conditions.

2: A fast mode (400 kHz) I<sup>2</sup>C bus device can be used in a standard mode (100 kHz) I<sup>2</sup>C bus system, but the requirement that, TSU:DAT ≥ 250 ns, must then be met. This will automatically be the case if the device does not stretch the LOW period of the SCL signal. If such a device does stretch the LOW period of the SCL signal, it must output the next data bit to the SDA line, TR MAX. + TSU:DAT = 1000 + 250 = 1250 ns (according to the standard mode I<sup>2</sup>C bus specification), before the SCL line is released.

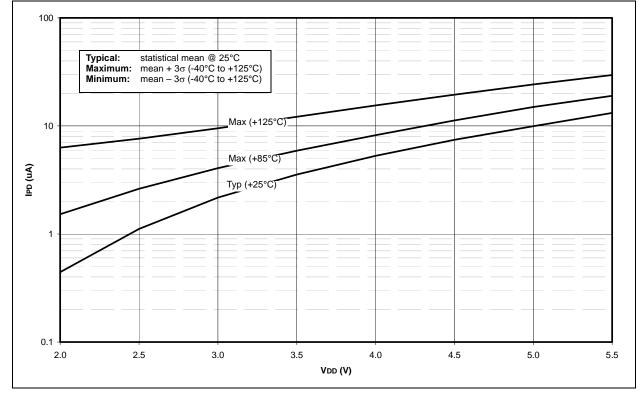

100 Max (125°C) 10 Max (85°C) 1 IPD (NA) 0.1 0.01 Тур (25°С) Typical: statistical mean @ 25°C Maximum: mean +  $3\sigma$  (-40°C to +125°C) Minimum: mean -  $3\sigma$  (-40°C to +125°C) 0.001 2.0 2.5 3.0 3.5 4.0 4.5 5.0 5.5 VDD (V)

# PIC16F87XA

## FIGURE 18-11: TYPICAL AND MAXIMUM $\triangle$ ITMR1 vs. VDD OVER TEMPERATURE (-10°C TO +70°C, TIMER1 WITH OSCILLATOR, XTAL = 32 kHz, C1 AND C2 = 47 pF)

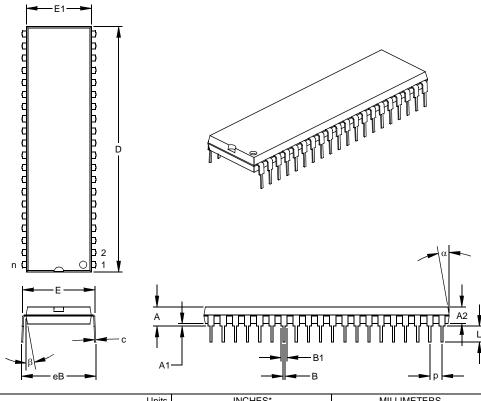

## 40-Lead Plastic Dual In-line (P) - 600 mil (PDIP)

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

|                            | Units    | INCHES* |       | MILLIMETERS |       |       |       |

|----------------------------|----------|---------|-------|-------------|-------|-------|-------|

| Dimensio                   | n Limits | MIN     | NOM   | MAX         | MIN   | NOM   | MAX   |

| Number of Pins             | n        |         | 40    |             |       | 40    |       |

| Pitch                      | р        |         | .100  |             |       | 2.54  |       |

| Top to Seating Plane       | А        | .160    | .175  | .190        | 4.06  | 4.45  | 4.83  |

| Molded Package Thickness   | A2       | .140    | .150  | .160        | 3.56  | 3.81  | 4.06  |

| Base to Seating Plane      | A1       | .015    |       |             | 0.38  |       |       |

| Shoulder to Shoulder Width | E        | .595    | .600  | .625        | 15.11 | 15.24 | 15.88 |

| Molded Package Width       | E1       | .530    | .545  | .560        | 13.46 | 13.84 | 14.22 |

| Overall Length             | D        | 2.045   | 2.058 | 2.065       | 51.94 | 52.26 | 52.45 |

| Tip to Seating Plane       | L        | .120    | .130  | .135        | 3.05  | 3.30  | 3.43  |

| Lead Thickness             | С        | .008    | .012  | .015        | 0.20  | 0.29  | 0.38  |

| Upper Lead Width           | B1       | .030    | .050  | .070        | 0.76  | 1.27  | 1.78  |

| Lower Lead Width           | В        | .014    | .018  | .022        | 0.36  | 0.46  | 0.56  |

| Overall Row Spacing §      | eB       | .620    | .650  | .680        | 15.75 | 16.51 | 17.27 |

| Mold Draft Angle Top       | α        | 5       | 10    | 15          | 5     | 10    | 15    |

| Mold Draft Angle Bottom    | β        | 5       | 10    | 15          | 5     | 10    | 15    |

\* Controlling Parameter § Significant Characteristic

Notes:

Dimensions D and E1 do not include mold flash or protrusions. Mold flash or protrusions shall not exceed

.010" (0.254mm) per side. JEDEC Equivalent: MO-011

Drawing No. C04-016

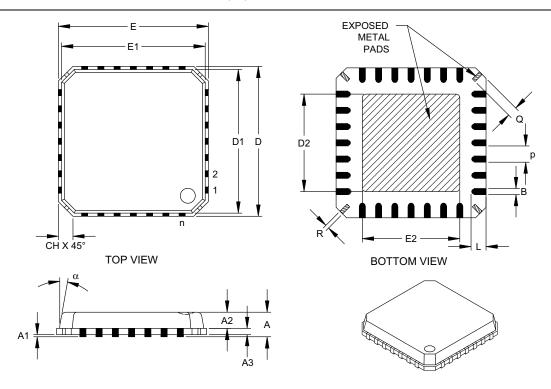

## 28-Lead Plastic Quad Flat No Lead Package (ML) 6x6 mm Body, Punch Singulated (QFN)

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

|                          | Units  | INCHES |          |      | MILLIMETERS* |          |      |

|--------------------------|--------|--------|----------|------|--------------|----------|------|

| Dimension                | Limits | MIN    | NOM      | MAX  | MIN          | NOM      | MAX  |

| Number of Pins           | n      |        | 28       |      |              | 28       |      |

| Pitch                    | р      |        | .026 BSC |      |              | 0.65 BSC |      |

| Overall Height           | Α      |        | .033     | .039 |              | 0.85     | 1.00 |

| Molded Package Thickness | A2     |        | .026     | .031 |              | 0.65     | 0.80 |

| Standoff                 | A1     | .000   | .0004    | .002 | 0.00         | 0.01     | 0.05 |

| Base Thickness           | A3     |        | .008 REF |      |              | 0.20 REF |      |

| Overall Width            | E      |        | .236 BSC |      |              | 6.00 BSC |      |

| Molded Package Width     | E1     |        | .226 BSC |      |              | 5.75 BSC |      |

| Exposed Pad Width        | E2     | .140   | .146     | .152 | 3.55         | 3.70     | 3.85 |

| Overall Length           | D      |        | .236 BSC |      |              | 6.00 BSC |      |

| Molded Package Length    | D1     |        | .226 BSC |      |              | 5.75 BSC |      |

| Exposed Pad Length       | D2     | .140   | .146     | .152 | 3.55         | 3.70     | 3.85 |

| Lead Width               | В      | .009   | .011     | .014 | 0.23         | 0.28     | 0.35 |

| Lead Length              | L      | .020   | .024     | .030 | 0.50         | 0.60     | 0.75 |

| Tie Bar Width            | R      | .005   | .007     | .010 | 0.13         | 0.17     | 0.23 |

| Tie Bar Length           | Q      | .012   | .016     | .026 | 0.30         | 0.40     | 0.65 |

| Chamfer                  | СН     | .009   | .017     | .024 | 0.24         | 0.42     | 0.60 |

| Mold Draft Angle Top     | α      |        |          | 12°  |              |          | 12°  |

\*Controlling Parameter

Notes:

Dimensions D and E1 do not include mold flash or protrusions. Mold flash or protrusions shall not exceed .010" (0.254mm) per side. JEDEC equivalent: mMO-220

Drawing No. C04-114

## INDEX

Α

| A/D                                            | 127     |

|------------------------------------------------|---------|

| Acquisition Requirements                       |         |

| ADCON0 Register                                |         |

| ADCON1 Register                                |         |

| ADIF Bit                                       |         |

| ADRESH Register                                |         |

| ADRESL Register                                |         |

| Analog Port Pins                               |         |

| Associated Registers and Bits                  |         |

| Calculating Acquisition Time                   |         |

| Configuring Analog Port Pins                   |         |

| Configuring the Interrupt                      |         |

| Configuring the Module                         |         |

| Conversion Clock                               |         |

| Conversions                                    |         |

| Converter Characteristics                      | 194     |

| Effects of a Reset                             |         |

| GO/DONE Bit                                    |         |

| Internal Sampling Switch (Rss) Impedance       |         |

| Operation During Sleep                         |         |

| Result Registers                               |         |

| Source Impedance                               |         |

| A/D Conversion Requirements                    |         |

| Absolute Maximum Ratings                       |         |

| ACKSTAT                                        |         |

| ADCON0 Register                                |         |

| ADCON1 Register                                |         |

| Addressable Universal Synchronous Asynchronous |         |

| Receiver Transmitter. See USART.               |         |

| ADRESH Register                                |         |

| ADRESL Register                                |         |

| Analog-to-Digital Converter. See A/D.          |         |

| Application Notes                              |         |

| AN552 (Implementing Wake-up                    |         |

| on Key Stroke)                                 | 44      |

| AN556 (Implementing a Table Read)              |         |

| Assembler                                      |         |

| MPASM Assembler                                | 167     |

| Asynchronous Reception                         |         |

| Associated Registers                           | 18, 120 |

| Asynchronous Transmission                      |         |

| Associated Registers                           | 116     |

| В                                              |         |

| -                                              | 10.00   |

| Banking, Data Memory                           |         |

| Baud Rate Generator                            |         |

| Associated Registers                           |         |

| BCLIF                                          |         |

| MSSP (SPI Mode)                                   |     |

|---------------------------------------------------|-----|

| On-Chip Reset Circuit 1                           | 47  |

| PIC16F873A/PIC16F876A Architecture                | . 6 |

| PIC16F874A/PIC16F877A Architecture                | . 7 |

| PORTC                                             |     |

| Peripheral Output Override                        |     |

| (RC2:0, RC7:5) Pins                               | 46  |

| Peripheral Output Override (RC4:3) Pins           | 46  |

| PORTD (in I/O Port Mode)                          |     |

| PORTD and PORTE (Parallel Slave Port)             |     |

| PORTE (In I/O Port Mode)                          |     |

| RA3:RA0 Pins                                      |     |

| RA4/T0CKI Pin                                     |     |

| RA5 Pin                                           |     |

| RB3:RB0 Pins                                      |     |

| RB7:RB4 Pins                                      |     |

| RC Oscillator Mode                                |     |

| Recommended MCLR Circuit                          | 10  |

| Simplified PWM Mode                               |     |

| Timer0/WDT Prescaler                              |     |

| Timero/WDT Prescaler                              |     |

|                                                   |     |

| Timer2                                            |     |

| USART Receive                                     |     |

| USART Transmit                                    |     |

| Watchdog Timer                                    | 55  |

| BOR. See Brown-out Reset.                         |     |

| BRG. See Baud Rate Generator.                     |     |

| BRGH Bit 1                                        |     |

| Brown-out Reset (BOR) 143, 147, 148, 149, 1       |     |

| BOR Status (BOR Bit)                              |     |

| Bus Collision During a Repeated Start Condition 1 |     |

| Bus Collision During a Start Condition 1          |     |

| Bus Collision During a Stop Condition 1           |     |

| Bus Collision Interrupt Flag bit, BCLIF           | 28  |

| С                                                 |     |

| -                                                 |     |

| C Compilers                                       |     |

| MPLAB C17 1                                       |     |

| MPLAB C18 1                                       |     |

| MPLAB C30 1                                       |     |

| Capture/Compare/PWM (CCP)                         | 63  |

| Associated Registers                              |     |

| Capture, Compare and Timer1                       |     |

| PWM and Timer2                                    | 69  |

| Capture Mode                                      | 65  |

| CCP1IF                                            | 65  |

| Prescaler                                         | 65  |

| CCP Timer Resources                               | 63  |

| Compare                                           |     |

| Special Event Trigger Output of CCP1              | 66  |

| Special Event Trigger Output of CCP2              |     |

| Compare Mode                                      |     |

| Software Interrupt Mode                           |     |

| Special Event Trigger                             |     |

|                                                   |     |

| Comparator I/O Operating Modes      |  |

|-------------------------------------|--|

| Comparator Output                   |  |

| Comparator Voltage Reference        |  |

| Compare Mode Operation              |  |

| Crystal/Ceramic Resonator Operation |  |

| (HS, XT or LP Osc Configuration) .  |  |

| External Clock Input Operation      |  |

| (HS, XT or LP Osc Configuration).   |  |

BF ......101

A/D129Analog Input Model130, 139Baud Rate Generator97Capture Mode Operation65

Block Diagrams