Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                            |

|----------------------------|----------------------------------------------------------------------------|

| Product Status             | Obsolete                                                                   |

| Core Processor             | PIC                                                                        |

| Core Size                  | 8-Bit                                                                      |

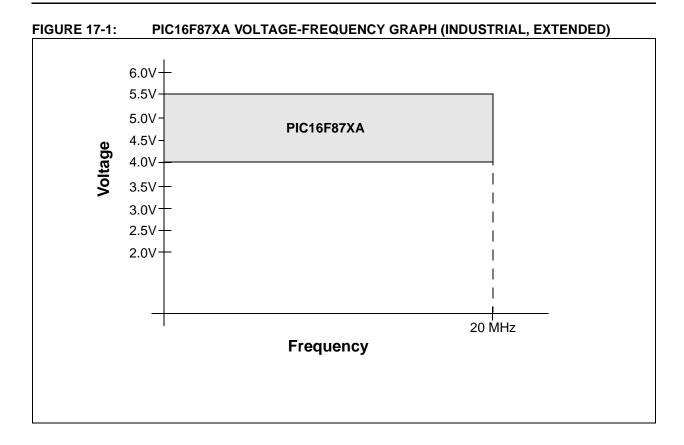

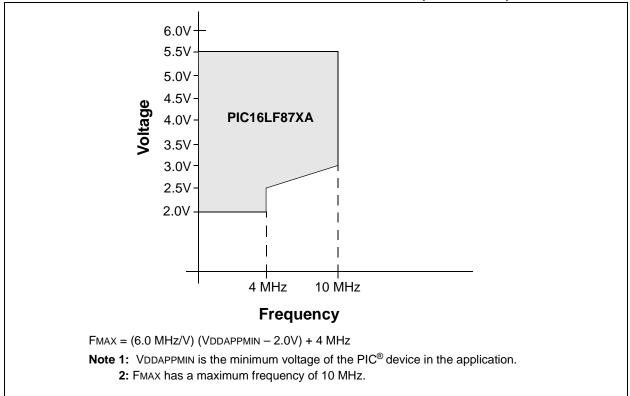

| Speed                      | 10MHz                                                                      |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                          |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                      |

| Number of I/O              | 33                                                                         |

| Program Memory Size        | 7KB (4K x 14)                                                              |

| Program Memory Type        | FLASH                                                                      |

| EEPROM Size                | 128 x 8                                                                    |

| RAM Size                   | 192 x 8                                                                    |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 5.5V                                                                  |

| Data Converters            | A/D 8x10b                                                                  |

| Oscillator Type            | External                                                                   |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                          |

| Mounting Type              | Surface Mount                                                              |

| Package / Case             | 44-LCC (J-Lead)                                                            |

| Supplier Device Package    | 44-PLCC (16.59x16.59)                                                      |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16lf874at-i-l |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| Pin Name                                                                                  | PDIP<br>Pin# | PLCC<br>Pin# | TQFP<br>Pin# | QFN<br>Pin# | I/O/P<br>Type | Buffer<br>Type        | Description                                          |

|-------------------------------------------------------------------------------------------|--------------|--------------|--------------|-------------|---------------|-----------------------|------------------------------------------------------|

|                                                                                           |              |              |              |             |               |                       | PORTB is a bidirectional I/O port. PORTB can be      |

|                                                                                           |              |              |              |             |               |                       | software programmed for internal weak pull-up on all |

|                                                                                           |              |              |              |             |               |                       | inputs.                                              |

| RB0/INT                                                                                   | 33           | 36           | 8            | 9           |               | TTL/ST <sup>(1)</sup> |                                                      |

| RB0                                                                                       |              |              |              |             | I/O           |                       | Digital I/O.                                         |

| INT                                                                                       |              |              |              |             | I             |                       | External interrupt.                                  |

| RB1                                                                                       | 34           | 37           | 9            | 10          | I/O           | TTL                   | Digital I/O.                                         |

| RB2                                                                                       | 35           | 38           | 10           | 11          | I/O           | TTL                   | Digital I/O.                                         |

| RB3/PGM                                                                                   | 36           | 39           | 11           | 12          |               | TTL                   |                                                      |

| RB3                                                                                       |              |              |              |             | I/O           |                       | Digital I/O.                                         |

| PGM                                                                                       |              |              |              |             | I             |                       | Low-voltage ICSP programming enable pin.             |

| RB4                                                                                       | 37           | 41           | 14           | 14          | I/O           | TTL                   | Digital I/O.                                         |

| RB5                                                                                       | 38           | 42           | 15           | 15          | I/O           | TTL                   | Digital I/O.                                         |

| RB6/PGC                                                                                   | 39           | 43           | 16           | 16          |               | TTL/ST <sup>(2)</sup> |                                                      |

| RB6                                                                                       |              |              |              |             | I/O           |                       | Digital I/O.                                         |

| PGC                                                                                       |              |              |              |             | I             |                       | In-circuit debugger and ICSP programming clock.      |

| RB7/PGD                                                                                   | 40           | 44           | 17           | 17          |               | TTL/ST <sup>(2)</sup> |                                                      |

| RB7                                                                                       |              |              |              |             | I/O           |                       | Digital I/O.                                         |

| PGD                                                                                       |              |              |              |             | I/O           |                       | In-circuit debugger and ICSP programming data.       |

| Legend:         I = input         O = output         I/O = input/output         P = power |              |              |              |             |               |                       |                                                      |

#### TABLE 1-3: PIC16F874A/877A PINOUT DESCRIPTION (CONTINUED)

Legend: I = input O = output — = Not used TTL = TTL input

ST = Schmitt Trigger input

Note 1: This buffer is a Schmitt Trigger input when configured as the external interrupt.

2: This buffer is a Schmitt Trigger input when used in Serial Programming mode.

3: This buffer is a Schmitt Trigger input when configured in RC Oscillator mode and a CMOS input otherwise.

NOTES:

#### 3.5 Reading Flash Program Memory

To read a program memory location, the user must write two bytes of the address to the EEADR and EEADRH registers, set the EEPGD control bit (EECON1<7>) and then set control bit RD (EECON1<0>). Once the read control bit is set, the program memory Flash controller will use the next two instruction cycles to read the data. This causes these two instructions immediately following the "BSF EECON1, RD" instruction to be ignored. The data is available in the very next cycle in the EEDATA and EEDATH registers; therefore, it can be read as two bytes in the following instructions. EEDATA and EEDATH registers will hold this value until another read or until it is written to by the user (during a write operation).

| EXAMPLE 3-3: | FLASH PROGRAM READ |

|--------------|--------------------|

|              |                    |

|                           | BSF   | STATUS, RP1     | i                                                    |  |

|---------------------------|-------|-----------------|------------------------------------------------------|--|

|                           | BCF   | STATUS, RPO     | ; Bank 2                                             |  |

|                           | MOVLW | MS PROG EE ADDR | i                                                    |  |

|                           | MOVWF | EEADRH          | ; MS Byte of Program Address to read                 |  |

|                           | MOVLW | LS_PROG_EE_ADDR | i                                                    |  |

|                           | MOVWF | EEADR           | ; LS Byte of Program Address to read                 |  |

|                           | BSF   | STATUS, RPO     | ; Bank 3                                             |  |

|                           | BSF   | EECON1, EEPGD   | ; Point to PROGRAM memory                            |  |

|                           | BSF   | EECON1, RD      | ; EE Read                                            |  |

| Required<br>Sequence<br>; |       |                 |                                                      |  |

| luer                      | NOP   |                 |                                                      |  |

| Seq                       | NOP   |                 | ; Any instructions here are ignored as program       |  |

|                           |       |                 | ; memory is read in second cycle after BSF EECON1,RD |  |

| ;                         |       |                 |                                                      |  |

|                           | BCF   | STATUS, RPO     | ; Bank 2                                             |  |

|                           | MOVF  | EEDATA, W       | ; W = LS Byte of Program EEDATA                      |  |

|                           | MOVWF | DATAL           | ;                                                    |  |

|                           | MOVF  | EEDATH, W       | ; W = MS Byte of Program EEDATA                      |  |

|                           | MOVWF | DATAH           | ;                                                    |  |

|                           |       |                 |                                                      |  |

| Address | Name   | Bit 7 | Bit 6 | Bit 5 | Bit 4   | Bit 3 | Bit 2   | Bit 1       | Bit 0     | Value on:<br>POR, BOR | Value on<br>all other<br>Resets |

|---------|--------|-------|-------|-------|---------|-------|---------|-------------|-----------|-----------------------|---------------------------------|

| 09h     | PORTE  | —     | —     | _     | —       |       | RE2     | RE1         | RE0       | xxx                   | uuu                             |

| 89h     | TRISE  | IBF   | OBF   | IBOV  | PSPMODE | —     | PORTE D | Data Direct | tion bits | 0000 -111             | 0000 -111                       |

| 9Fh     | ADCON1 | ADFM  | ADCS2 | _     | —       | PCFG3 | PCFG2   | PCFG1       | PCFG0     | 00 0000               | 00 0000                         |

#### **TABLE 4-10:** SUMMARY OF REGISTERS ASSOCIATED WITH PORTE

Legend: x = unknown, u = unchanged, - = unimplemented, read as '0'. Shaded cells are not used by PORTE.

#### **REGISTER 4-1: TRISE REGISTER (ADDRESS 89h)**

| R-0   | R-0 | R/W-0 | R/W-0   | U-0 | R/W-1 | R/W-1 | R/W-1 |

|-------|-----|-------|---------|-----|-------|-------|-------|

| IBF   | OBF | IBOV  | PSPMODE | —   | Bit 2 | Bit 1 | Bit 0 |

| bit 7 |     |       |         |     |       |       | bit 0 |

#### Parallel Slave Port Status/Control Bits:

| bit 7 | IBF: Input Buffer Full Stat          | tus bit                              |                      |                        |

|-------|--------------------------------------|--------------------------------------|----------------------|------------------------|

|       | 1 = A word has been rece             | eived and is waiting to              | be read by the CPU   |                        |

|       | 0 = No word has been re-             | ceived                               |                      |                        |

| bit 6 | <b>OBF</b> : Output Buffer Full      | Status bit                           |                      |                        |

|       | 1 = The output buffer still          | holds a previously wri               | tten word            |                        |

|       | 0 = The output buffer has            | been read                            |                      |                        |

| bit 5 | IBOV: Input Buffer Overf             | low Detect bit (in Micro             | processor mode)      |                        |

|       | 1 = A write occurred wh<br>software) | en a previously input                | word has not been re | ad (must be cleared in |

|       | 0 = No overflow occurred             | b                                    |                      |                        |

| bit 4 | PSPMODE: Parallel Slav               | e Port Mode Select bit               |                      |                        |

|       | 1 = PORTD functions in F             | Parallel Slave Port mo               | de                   |                        |

|       | 0 = PORTD functions in g             | general purpose I/O m                | ode                  |                        |

| bit 3 | Unimplemented: Read a                | <b>as</b> '0'                        |                      |                        |

|       | PORTE Data Direction E               | <u>Bits:</u>                         |                      |                        |

| bit 2 | Bit 2: Direction Control bi          | it for pin RE2/ $\overline{CS}$ /AN7 |                      |                        |

|       | 1 = Input                            |                                      |                      |                        |

|       | 0 = Output                           |                                      |                      |                        |

| bit 1 | Bit 1: Direction Control bi          | it for pin RE1/WR/AN6                |                      |                        |

|       | 1 = Input                            |                                      |                      |                        |

|       | 0 = Output                           |                                      |                      |                        |

| bit 0 | Bit 0: Direction Control bi          | it for pin RE0/RD/AN5                |                      |                        |

|       | 1 = Input                            |                                      |                      |                        |

|       | 0 = Output                           |                                      |                      |                        |

|       |                                      |                                      |                      |                        |

|       | Legend:                              |                                      |                      |                        |

|       | R = Readable bit                     | W = Writable bit                     | U = Unimplemented    | bit, read as '0'       |

|       | - n = Value at POR                   | '1' = Bit is set                     | '0' = Bit is cleared | x = Bit is unknown     |

|       | L                                    |                                      |                      |                        |

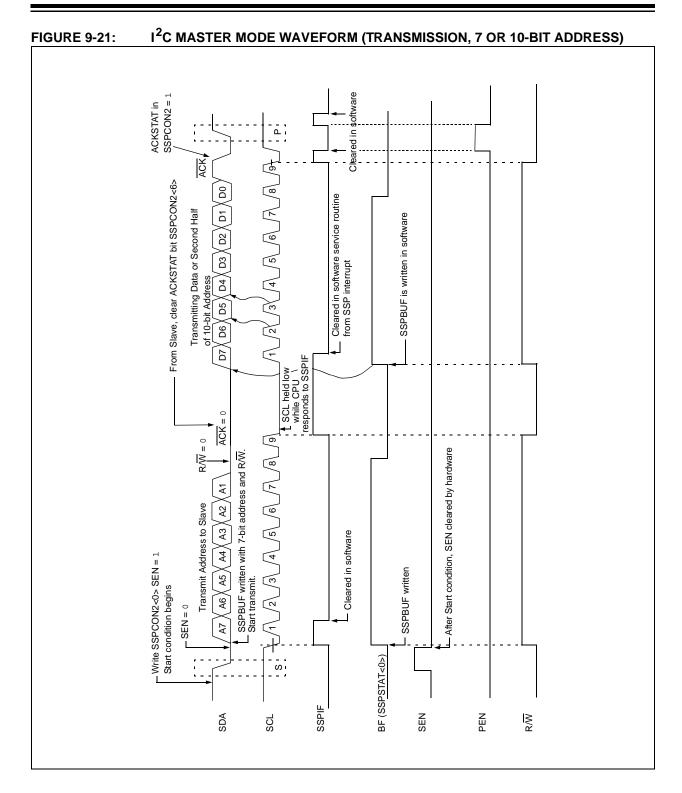

| <b>REGISTER 9-3:</b> | SSPSTAT:                                                                                                                                                                                                 | MSSP STA                        | TUS REG       | SISTER (I <sup>2</sup> | C MODE)                    | (ADDRESS      | 6 94h)         |         |  |

|----------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------|---------------|------------------------|----------------------------|---------------|----------------|---------|--|

|                      | R/W-0                                                                                                                                                                                                    | R/W-0                           | R-0           | R-0                    | R-0                        | R-0           | R-0            | R-0     |  |

|                      | SMP                                                                                                                                                                                                      | CKE                             | D/A           | Р                      | S                          | R/W           | UA             | BF      |  |

|                      | bit 7                                                                                                                                                                                                    |                                 |               |                        |                            |               |                | bit 0   |  |

| bit 7                | SMP: Slew                                                                                                                                                                                                | Rate Contro                     | l bit         |                        |                            |               |                |         |  |

|                      |                                                                                                                                                                                                          | or Slave mode                   |               |                        |                            |               |                |         |  |

|                      |                                                                                                                                                                                                          | ate control dis                 |               |                        |                            |               | 1 MHz)         |         |  |

| bit 6                |                                                                                                                                                                                                          | ate control en                  |               | gn-speed n             | 100e (400 K                | ΠΖ)           |                |         |  |

| bit 0                |                                                                                                                                                                                                          | or Slave mode                   | <i>.</i>      |                        |                            |               |                |         |  |

|                      | 1 = Enable                                                                                                                                                                                               | SMBus spec                      | ific inputs   |                        |                            |               |                |         |  |

|                      |                                                                                                                                                                                                          | e SMBus spe                     | cific inputs  |                        |                            |               |                |         |  |

| bit 5                |                                                                                                                                                                                                          | Address bit                     |               |                        |                            |               |                |         |  |

|                      | <u>In Master n</u><br>Reserved.                                                                                                                                                                          | node:                           |               |                        |                            |               |                |         |  |

|                      | In Slave me                                                                                                                                                                                              |                                 |               |                        |                            |               |                |         |  |

|                      |                                                                                                                                                                                                          | es that the las                 | -             |                        |                            |               |                |         |  |

| bit 4                | • = mulcate<br><b>P:</b> Stop bit                                                                                                                                                                        | es that the las                 | si byte rece  |                        | Smilleu was                | audiess       |                |         |  |

| 511 4                | •                                                                                                                                                                                                        | es that a Stop                  | bit has be    | en detected            | last                       |               |                |         |  |

|                      |                                                                                                                                                                                                          | t was not det                   |               |                        |                            |               |                |         |  |

|                      | Note:                                                                                                                                                                                                    | This bit is clo                 | eared on Re   | eset and wh            | nen SSPEN                  | is cleared.   |                |         |  |

| bit 3                | S: Start bit                                                                                                                                                                                             |                                 |               |                        |                            |               |                |         |  |

|                      |                                                                                                                                                                                                          | es that a Star<br>t was not det |               | en detectec            | llast                      |               |                |         |  |

|                      | Note:                                                                                                                                                                                                    | This bit is cl                  |               | eset and wh            | nen SSPEN                  | is cleared    |                |         |  |

| bit 2                | _                                                                                                                                                                                                        | Write bit info                  |               |                        |                            |               |                |         |  |

| 511 2                | In Slave me                                                                                                                                                                                              |                                 |               |                        | y)                         |               |                |         |  |

|                      | 1 = Read                                                                                                                                                                                                 |                                 |               |                        |                            |               |                |         |  |

|                      | 0 = Write                                                                                                                                                                                                |                                 |               |                        |                            |               |                | <b></b> |  |

|                      | Note:                                                                                                                                                                                                    | This bit hold<br>only valid fro |               |                        |                            |               |                |         |  |

|                      | In Master mode:                                                                                                                                                                                          |                                 |               |                        |                            |               |                |         |  |

|                      | 1 = Transmit is in progress<br>0 = Transmit is not in progress                                                                                                                                           |                                 |               |                        |                            |               |                |         |  |

|                      | <b>Note:</b> ORing this bit with SEN, RSEN, PEN, RCEN or ACKEN will indicate if the MSSP is                                                                                                              |                                 |               |                        |                            |               |                |         |  |

|                      |                                                                                                                                                                                                          | in Idle mode                    |               |                        |                            |               |                |         |  |

| bit 1                | UA: Update                                                                                                                                                                                               | e Address (10                   | D-bit Slave i | mode only)             |                            |               |                |         |  |

|                      |                                                                                                                                                                                                          | es that the us                  |               | •                      | address in                 | the SSPADE    | D register     |         |  |

|                      |                                                                                                                                                                                                          | s does not ne                   | •             | odated                 |                            |               |                |         |  |

| bit 0                | BF: Buffer Full Status bit                                                                                                                                                                               |                                 |               |                        |                            |               |                |         |  |

|                      | In Transmit mode:<br>1 = Receive complete, SSPBUF is full                                                                                                                                                |                                 |               |                        |                            |               |                |         |  |

|                      | 0 = Receive not complete, SSPBUF is empty                                                                                                                                                                |                                 |               |                        |                            |               |                |         |  |

|                      | In Receive                                                                                                                                                                                               |                                 | aroog (dog    | o not includ           | $a + b = \overline{A C K}$ | and Stop hits |                | o full  |  |

|                      | <ul> <li>1 = Data Transmit in progress (does not include the ACK and Stop bits), SSPBUF is full</li> <li>0 = Data Transmit complete (does not include the ACK and Stop bits), SSPBUF is empty</li> </ul> |                                 |               |                        |                            |               |                |         |  |

|                      | Legend:                                                                                                                                                                                                  |                                 |               |                        |                            |               |                |         |  |

|                      | R = Reada                                                                                                                                                                                                | ble bit                         | W = W         | ritable bit            | U = Unir                   | nplemented    | bit, read as ' | 0'      |  |

|                      | - n = Value                                                                                                                                                                                              |                                 | '1' = Bi      |                        |                            | is cleared    | x = Bit is u   |         |  |

|                      |                                                                                                                                                                                                          |                                 |               |                        |                            |               |                |         |  |

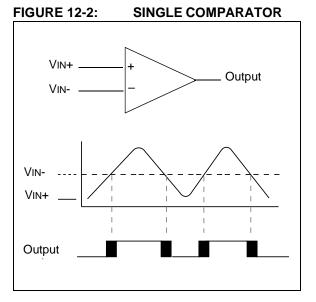

#### 12.2 Comparator Operation

A single comparator is shown in Figure 12-2 along with the relationship between the analog input levels and the digital output. When the analog input at VIN+ is less than the analog input VIN-, the output of the comparator is a digital low level. When the analog input at VIN+ is greater than the analog input VIN-, the output of the comparator is a digital high level. The shaded areas of the output of the comparator in Figure 12-2 represent the uncertainty due to input offsets and response time.

#### 12.3 Comparator Reference

An external or internal reference signal may be used depending on the comparator operating mode. The analog signal present at VIN- is compared to the signal at VIN+ and the digital output of the comparator is adjusted accordingly (Figure 12-2).

#### 12.3.1 EXTERNAL REFERENCE SIGNAL

When external voltage references are used, the comparator module can be configured to have the comparators operate from the same or different reference sources. However, threshold detector applications may require the same reference. The reference signal must be between VSS and VDD and can be applied to either pin of the comparator(s).

#### 12.3.2 INTERNAL REFERENCE SIGNAL

The comparator module also allows the selection of an internally generated voltage reference for the comparators. Section 13.0 "Comparator Voltage Reference Module" contains a detailed description of the Comparator Voltage Reference module that provides this signal. The internal reference signal is used when comparators are in mode, CM<2:0> = 110 (Figure 12-1). In this mode, the internal voltage reference is applied to the VIN+ pin of both comparators.

#### 12.4 Comparator Response Time

Response time is the minimum time, after selecting a new reference voltage or input source, before the comparator output has a valid level. If the internal reference is changed, the maximum delay of the internal voltage reference must be considered when using the comparator outputs. Otherwise, the maximum delay of the comparators should be used (Section 17.0 "Electrical Characteristics").

#### 12.5 Comparator Outputs

The comparator outputs are read through the CMCON register. These bits are read-only. The comparator outputs may also be directly output to the RA4 and RA5 I/O pins. When enabled, multiplexors in the output path of the RA4 and RA5 pins will switch and the output of each pin will be the unsynchronized output of the comparator. The uncertainty of each of the comparators is related to the input offset voltage and the response time given in the specifications. Figure 12-3 shows the comparator output block diagram.

The TRISA bits will still function as an output enable/ disable for the RA4 and RA5 pins while in this mode.

The polarity of the comparator outputs can be changed using the C2INV and C1INV bits (CMCON<4:5>).

- Note 1: When reading the Port register, all pins configured as analog inputs will read as a '0'. Pins configured as digital inputs will convert an analog input according to the Schmitt Trigger input specification.

- 2: Analog levels on any pin defined as a digital input may cause the input buffer to consume more current than is specified.

- **3:** RA4 is an open collector I/O pin. When used as an output, a pull-up resistor is required.

bit 0

### **13.0 COMPARATOR VOLTAGE REFERENCE MODULE**

The Comparator Voltage Reference Generator is a 16-tap resistor ladder network that provides a fixed voltage reference when the comparators are in mode '110'. A programmable register controls the function of the reference generator. Register 13-1 lists the bit functions of the CVRCON register.

As shown in Figure 13-1, the resistor ladder is segmented to provide two ranges of CVREF values and has a power-down function to conserve power when the reference is not being used. The comparator reference supply voltage (also referred to as CVRSRC) comes directly from VDD. It should be noted, however, that the voltage at the top of the ladder is CVRSRC - VSAT, where VSAT is the saturation voltage of the power switch transistor. This reference will only be as accurate as the values of CVRSRC and VSAT.

The output of the reference generator may be connected to the RA2/AN2/VREF-/CVREF pin. This can be used as a simple D/A function by the user if a very highimpedance load is used. The primary purpose of this function is to provide a test path for testing the reference generator function.

|       | R/W-0     | R/W-0        | R/W-0       | U-0         | R/W-0 | R/W-0 | R/W-0 | R/W-0 |

|-------|-----------|--------------|-------------|-------------|-------|-------|-------|-------|

|       | CVREN     | CVROE        | CVRR        | —           | CVR3  | CVR2  | CVR1  | CVR0  |

|       | bit 7     |              |             |             |       |       |       | bit ( |

|       |           |              |             |             |       |       |       |       |

| bit 7 | CVREN: C  | omparator V  | oltage Refe | rence Enabl | e bit |       |       |       |

|       | 1 = CVREF | circuit powe | ered on     |             |       |       |       |       |

#### REGISTER 13-1: CVRCON CONTROL REGISTER (ADDRESS 9Dh)

|         | CVREN. Comparator voltage Reference Enable bit                                                         |

|---------|--------------------------------------------------------------------------------------------------------|

|         | 1 = CVREF circuit powered on                                                                           |

|         | 0 = CVREF circuit powered down                                                                         |

| hit C   | · · · · · · · · · · · · · · · · · · ·                                                                  |

| bit 6   | CVROE: Comparator VREF Output Enable bit                                                               |

|         | 1 = CVREF voltage level is output on RA2/AN2/VREF-/CVREF pin                                           |

|         | 0 = CVREF voltage level is disconnected from RA2/AN2/VREF-/CVREF pin                                   |

| bit 5   | CVRR: Comparator VREF Range Selection bit                                                              |

|         | 1 = 0 to 0.75 CVRSRC, with CVRSRC/24 step size                                                         |

|         | 0 = 0.25 CVRSRC to 0.75 CVRSRC, with CVRSRC/32 step size                                               |

| L:1. A  |                                                                                                        |

| bit 4   | Unimplemented: Read as '0'                                                                             |

| bit 3-0 | <b>CVR3:CVR0:</b> Comparator VREF Value Selection bits $0 \le VR3:VR0 \le 15$                          |

|         | When $CVRR = 1$ :                                                                                      |

|         | $\overline{\text{CVREF}} = (\text{VR} < 3:0 > / 24) \bullet (\text{CVRSRC})$                           |

|         | When CVRR = 0:                                                                                         |

|         | $\overline{\text{CVREF}} = 1/4 \bullet (\text{CVRSRC}) + (\text{VR3:VR0/ 32}) \bullet (\text{CVRSRC})$ |

|         |                                                                                                        |

|         |                                                                                                        |

| Legend:           |                  |                      |                    |

|-------------------|------------------|----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented    | bit, read as '0'   |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared | x = Bit is unknown |

### TABLE 14-2:CAPACITOR SELECTION FOR<br/>CRYSTAL OSCILLATOR

| Osc Type | Crystal<br>Freq. | Cap. Range<br>C1 | Cap. Range<br>C2 |

|----------|------------------|------------------|------------------|

| LP       | 32 kHz           | 33 pF            | 33 pF            |

|          | 200 kHz          | 15 pF            | 15 pF            |

| XT       | 200 kHz          | 47-68 pF         | 47-68 pF         |

|          | 1 MHz            | 15 pF            | 15 pF            |

|          | 4 MHz            | 15 pF            | 15 pF            |

| HS       | 4 MHz            | 15 pF            | 15 pF            |

|          | 8 MHz            | 15-33 pF         | 15-33 pF         |

|          | 20 MHz           | 15-33 pF         | 15-33 pF         |

**These values are for design guidance only.** See notes following this table.

| Crystals Used |                        |          |  |  |  |  |

|---------------|------------------------|----------|--|--|--|--|

| 32 kHz        | Epson C-001R32.768K-A  | ± 20 PPM |  |  |  |  |

| 200 kHz       | STD XTL 200.000KHz     | ± 20 PPM |  |  |  |  |

| 1 MHz         | ECS ECS-10-13-1        | ± 50 PPM |  |  |  |  |

| 4 MHz         | ECS ECS-40-20-1        | ± 50 PPM |  |  |  |  |

| 8 MHz         | EPSON CA-301 8.000M-C  | ± 30 PPM |  |  |  |  |

| 20 MHz        | EPSON CA-301 20.000M-C | ± 30 PPM |  |  |  |  |

- Note 1: Higher capacitance increases the stability of oscillator but also increases the start-up time.

- 2: Since each resonator/crystal has its own characteristics, the user should consult the resonator/crystal manufacturer for appropriate values of external components.

- **3:** *R*<sub>s</sub> may be required in HS mode, as well as XT mode, to avoid overdriving crystals with low drive level specification.

- When migrating from other PIC<sup>®</sup> devices, oscillator performance should be verified.

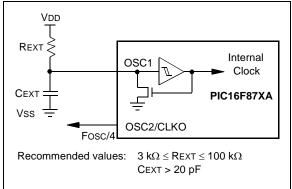

#### 14.2.3 RC OSCILLATOR

For timing insensitive applications, the "RC" device option offers additional cost savings. The RC oscillator frequency is a function of the supply voltage, the resistor (REXT) and capacitor (CEXT) values and the operating temperature. In addition to this, the oscillator frequency will vary from unit to unit due to normal process parameter variation. Furthermore, the difference in lead frame capacitance between package types will also affect the oscillation frequency, especially for low CEXT values. The user also needs to take into account variation due to tolerance of external R and C components used. Figure 14-3 shows how the R/C combination is connected to the PIC16F87XA.

#### 14.3 Reset

The PIC16F87XA differentiates between various kinds of Reset:

- Power-on Reset (POR)

- MCLR Reset during normal operation

- MCLR Reset during Sleep

- WDT Reset (during normal operation)

- WDT Wake-up (during Sleep)

- Brown-out Reset (BOR)

Some registers are not affected in any Reset condition. Their status is unknown on POR and unchanged in any other Reset. Most other registers are reset to a "Reset state" on Power-on Reset (POR), on the MCLR and WDT Reset, on MCLR Reset during Sleep and Brownout Reset (BOR). They are not affected by a WDT wake-up which is viewed as the resumption of normal operation. The TO and PD bits are set or cleared differently in different Reset situations as indicated in Table 14-4. These bits are used in software to determine the nature of the Reset. See Table 14-6 for a full description of Reset states of all registers.

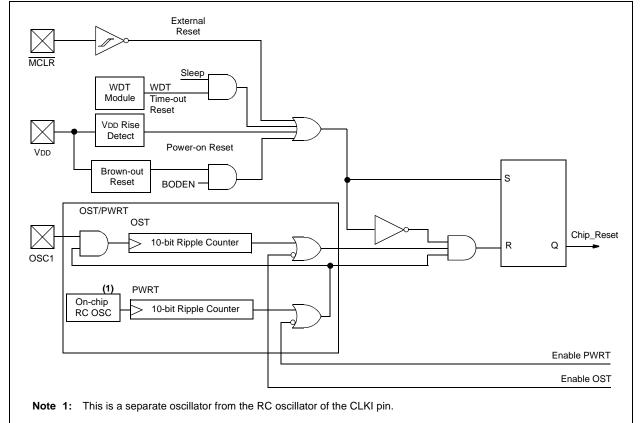

A simplified block diagram of the on-chip Reset circuit is shown in Figure 14-4.

#### FIGURE 14-4: SIMPLIFIED BLOCK DIAGRAM OF ON-CHIP RESET CIRCUIT

#### 14.10 Power Control/Status Register (PCON)

The Power Control/Status Register, PCON, has up to two bits depending upon the device.

Bit 0 is the Brown-out Reset Status bit, BOR. The BOR bit is unknown on a Power-on Reset. It must then be set by the user and checked on subsequent Resets to see if it has been cleared, indicating that a BOR has occurred.

When the Brown-out Reset is disabled, the state of the  $\overline{\text{BOR}}$  bit is unpredictable and is, therefore, not valid at any time.

Bit 1 is the Power-on Reset Status bit,  $\overline{\text{POR}}$ . It is cleared on a Power-on Reset and unaffected otherwise. The user must set this bit following a Power-on Reset.

| TABLE 14-3: | TIME-OUT IN VARIOUS SITUATIONS |

|-------------|--------------------------------|

|-------------|--------------------------------|

| Oscillator Configuration | Power             | -up              | Brown-out         | Wake-up from<br>Sleep |  |

|--------------------------|-------------------|------------------|-------------------|-----------------------|--|

| Oscillator Configuration | <b>PWRTE =</b> 0  | <b>PWRTE</b> = 1 | Brown-out         |                       |  |

| XT, HS, LP               | 72 ms + 1024 Tosc | 1024 Tosc        | 72 ms + 1024 Tosc | 1024 Tosc             |  |

| RC                       | 72 ms             |                  | 72 ms             | _                     |  |

#### TABLE 14-4: STATUS BITS AND THEIR SIGNIFICANCE

| POR | BOR | то | PD | Condition                                               |  |  |  |

|-----|-----|----|----|---------------------------------------------------------|--|--|--|

| 0   | x   | 1  | 1  | Power-on Reset                                          |  |  |  |

| 0   | x   | 0  | x  | llegal, TO is set on POR                                |  |  |  |

| 0   | x   | x  | 0  | llegal, PD is set on POR                                |  |  |  |

| 1   | 0   | 1  | 1  | Brown-out Reset                                         |  |  |  |

| 1   | 1   | 0  | 1  | VDT Reset                                               |  |  |  |

| 1   | 1   | 0  | 0  | WDT Wake-up                                             |  |  |  |

| 1   | 1   | u  | u  | MCLR Reset during normal operation                      |  |  |  |

| 1   | 1   | 1  | 0  | MCLR Reset during Sleep or Interrupt Wake-up from Sleep |  |  |  |

**Legend:** x = don't care, u = unchanged

#### TABLE 14-5: RESET CONDITIONS FOR SPECIAL REGISTERS

| Condition                          | Program<br>Counter    | Status<br>Register | PCON<br>Register |  |

|------------------------------------|-----------------------|--------------------|------------------|--|

| Power-on Reset                     | 000h                  | 0001 1xxx          | 0x               |  |

| MCLR Reset during normal operation | 000h                  | 000u uuuu          | uu               |  |

| MCLR Reset during Sleep            | 000h                  | 0001 0uuu          | uu               |  |

| WDT Reset                          | 000h                  | 0000 luuu          | uu               |  |

| WDT Wake-up                        | PC + 1                | uuu0 Ouuu          | uu               |  |

| Brown-out Reset                    | 000h                  | 0001 luuu          | u0               |  |

| Interrupt Wake-up from Sleep       | PC + 1 <sup>(1)</sup> | uuul Ouuu          | uu               |  |

Legend: u = unchanged, x = unknown, - = unimplemented bit, read as '0'

**Note 1:** When the wake-up is due to an interrupt and the GIE bit is set, the PC is loaded with the interrupt vector (0004h).

| TABLE 14-6: INITIALIZATION CONDITIONS FOR ALL REGISTERS (CONTINUED) |                  |     |                                    |                           |                                 | IED)      |           |

|---------------------------------------------------------------------|------------------|-----|------------------------------------|---------------------------|---------------------------------|-----------|-----------|

| Register                                                            | Register Devices |     | Power-on Reset,<br>Brown-out Reset | MCLR Resets,<br>WDT Reset | Wake-up via WDT or<br>Interrupt |           |           |

| TRISD                                                               | 73A              | 74A | 76A                                | 77A                       | 1111 1111                       | 1111 1111 | uuuu uuuu |

| TRISE                                                               | 73A              | 74A | 76A                                | 77A                       | 0000 -111                       | 0000 -111 | uuuu -uuu |

| PIE1                                                                | 73A              | 74A | 76A                                | 77A                       | r000 0000                       | r000 0000 | ruuu uuuu |

| FICI                                                                | 73A              | 74A | 76A                                | 77A                       | 0000 0000                       | 0000 0000 | սսսս սսսս |

| PIE2                                                                | 73A              | 74A | 76A                                | 77A                       | -0-0 00                         | -0-0 00   | -u-u uu   |

| PCON                                                                | 73A              | 74A | 76A                                | 77A                       | dd                              | uu        | uu        |

| SSPCON2                                                             | 73A              | 74A | 76A                                | 77A                       | 0000 0000                       | 0000 0000 | uuuu uuuu |

| PR2                                                                 | 73A              | 74A | 76A                                | 77A                       | 1111 1111                       | 1111 1111 | 1111 1111 |

| SSPADD                                                              | 73A              | 74A | 76A                                | 77A                       | 0000 0000                       | 0000 0000 | uuuu uuuu |

| SSPSTAT                                                             | 73A              | 74A | 76A                                | 77A                       | 00 0000                         | 00 0000   | uu uuuu   |

| TXSTA                                                               | 73A              | 74A | 76A                                | 77A                       | 0000 -010                       | 0000 -010 | uuuu -uuu |

| SPBRG                                                               | 73A              | 74A | 76A                                | 77A                       | 0000 0000                       | 0000 0000 | uuuu uuuu |

| CMCON                                                               | 73A              | 974 | 76A                                | 77A                       | 0000 0111                       | 0000 0111 | uuuu uuuu |

| CVRCON                                                              | 73A              | 74A | 76A                                | 77A                       | 000- 0000                       | 000- 0000 | uuu- uuuu |

| ADRESL                                                              | 73A              | 74A | 76A                                | 77A                       | XXXX XXXX                       | սսսս սսսս | uuuu uuuu |

| ADCON1                                                              | 73A              | 74A | 76A                                | 77A                       | 00 0000                         | 00 0000   | uu uuuu   |

| EEDATA                                                              | 73A              | 74A | 76A                                | 77A                       | XXXX XXXX                       | uuuu uuuu | uuuu uuuu |

| EEADR                                                               | 73A              | 74A | 76A                                | 77A                       | XXXX XXXX                       | uuuu uuuu | uuuu uuuu |

| EEDATH                                                              | 73A              | 74A | 76A                                | 77A                       | XXXX XXXX                       | սսսս սսսս | uuuu uuuu |

| EEADRH                                                              | 73A              | 74A | 76A                                | 77A                       | xxxx xxxx                       | սսսս սսսս | uuuu uuuu |

| EECON1                                                              | 73A              | 74A | 76A                                | 77A                       | x x000                          | u u000    | u uuuu    |

| EECON2                                                              | 73A              | 74A | 76A                                | 77A                       |                                 |           |           |

**Legend:** u = unchanged, x = unknown, - = unimplemented bit, read as '0', q = value depends on condition, r = reserved, maintain clear. Shaded cells indicate conditions do not apply for the designated device.

Note 1: One or more bits in INTCON, PIR1 and/or PIR2 will be affected (to cause wake-up).

**2:** When the wake-up is due to an interrupt and the GIE bit is set, the PC is loaded with the interrupt vector (0004h).

3: See Table 14-5 for Reset value for specific condition.

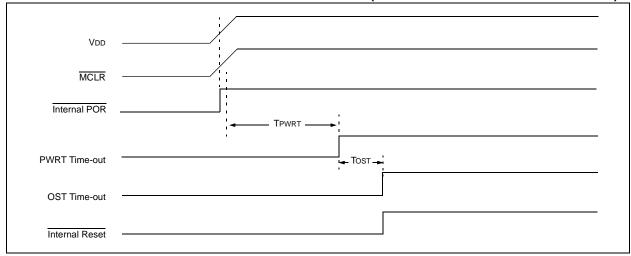

#### FIGURE 14-6: TIME-OUT SEQUENCE ON POWER-UP (MCLR TIED TO VDD VIA RC NETWORK)

© 2001-2013 Microchip Technology Inc.

### 17.3 Timing Parameter Symbology

The timing parameter symbols have been created following one of the following formats:

| 1. TppS2ppS           |                                               | 3. Tcc:st | (I <sup>2</sup> C specifications only) |  |  |  |  |

|-----------------------|-----------------------------------------------|-----------|----------------------------------------|--|--|--|--|

| 2. TppS               |                                               | 4. Ts     | (I <sup>2</sup> C specifications only) |  |  |  |  |

| Т                     |                                               |           |                                        |  |  |  |  |

| F                     | Frequency                                     | Т         | Time                                   |  |  |  |  |

| Lowerca               | se letters (pp) and their meanings:           |           |                                        |  |  |  |  |

| рр                    |                                               |           |                                        |  |  |  |  |

| CC                    | CCP1                                          | OSC       | OSC1                                   |  |  |  |  |

| ck                    | CLKO                                          | rd        | RD                                     |  |  |  |  |

| CS                    | CS                                            | rw        | RD or WR                               |  |  |  |  |

| di                    | SDI                                           | SC        | SCK                                    |  |  |  |  |

| do                    | SDO                                           | SS        | SS                                     |  |  |  |  |

| dt                    | Data in                                       | tO        | TOCKI                                  |  |  |  |  |

| io                    | I/O port                                      | t1        | T1CKI                                  |  |  |  |  |

| mc                    | MCLR                                          | wr        | WR                                     |  |  |  |  |

|                       | se letters and their meanings:                |           |                                        |  |  |  |  |

| S                     |                                               |           |                                        |  |  |  |  |

| F                     | Fall                                          | Р         | Period                                 |  |  |  |  |

| Н                     | High                                          | R         | Rise                                   |  |  |  |  |

| I                     | Invalid (High-impedance)                      | V         | Valid                                  |  |  |  |  |

| L                     | Low                                           | Z         | High-impedance                         |  |  |  |  |

| I <sup>2</sup> C only |                                               |           |                                        |  |  |  |  |

| AA                    | output access                                 | High      | High                                   |  |  |  |  |

| BUF                   | Bus free                                      | Low       | Low                                    |  |  |  |  |

| Tcc:st (I             | TCC:ST (I <sup>2</sup> C specifications only) |           |                                        |  |  |  |  |

| CC                    |                                               |           |                                        |  |  |  |  |

| HD                    | Hold                                          | SU        | Setup                                  |  |  |  |  |

| ST                    |                                               |           |                                        |  |  |  |  |

| DAT                   | Data input hold                               | STO       | Stop condition                         |  |  |  |  |

| STA                   | Start condition                               |           |                                        |  |  |  |  |

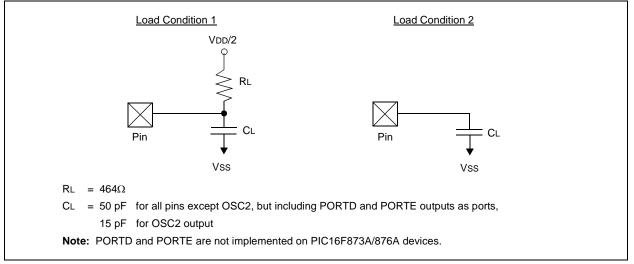

#### FIGURE 17-3: LOAD CONDITIONS

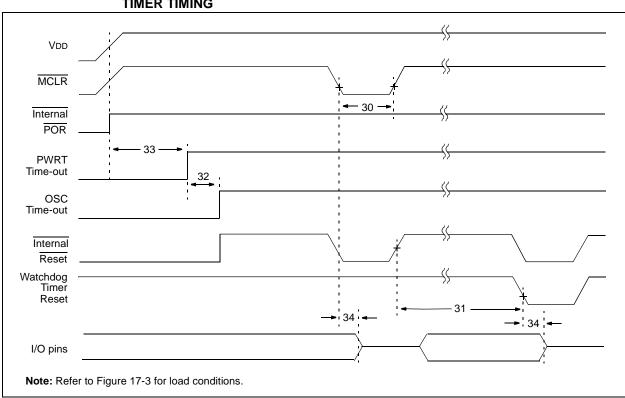

### FIGURE 17-6: RESET, WATCHDOG TIMER, OSCILLATOR START-UP TIMER AND POWER-UP TIMER TIMING

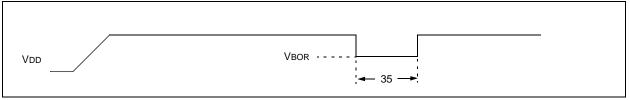

#### FIGURE 17-7: BROWN-OUT RESET TIMING

### TABLE 17-5:RESET, WATCHDOG TIMER, OSCILLATOR START-UP TIMER, POWER-UP TIMER<br/>AND BROWN-OUT RESET REQUIREMENTS

| Param<br>No. | Symbol | Characteristic                                           | Min | Тур†      | Max | Units | Conditions               |

|--------------|--------|----------------------------------------------------------|-----|-----------|-----|-------|--------------------------|

| 30           | TMCL   | MCLR Pulse Width (low)                                   | 2   | _         | -   | μS    | VDD = 5V, -40°C to +85°C |

| 31*          | Twdt   | Watchdog Timer Time-out Period<br>(no prescaler)         | 7   | 18        | 33  | ms    | VDD = 5V, -40°C to +85°C |

| 32           | Tost   | Oscillation Start-up Timer Period                        | —   | 1024 Tosc | _   | _     | Tosc = OSC1 period       |

| 33*          | TPWRT  | Power-up Timer Period                                    | 28  | 72        | 132 | ms    | VDD = 5V, -40°C to +85°C |

| 34           | Tıoz   | I/O High-Impedance from MCLR Low or Watchdog Timer Reset | —   | _         | 2.1 | μS    |                          |

| 35           | TBOR   | Brown-out Reset Pulse Width                              | 100 | —         | _   | μS    | $VDD \leq VBOR (D005)$   |

\* These parameters are characterized but not tested.

† Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

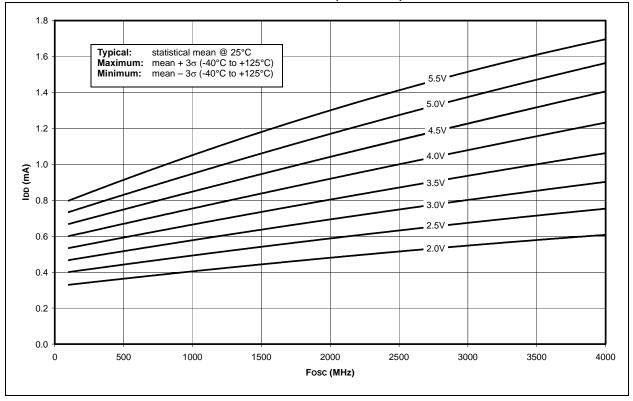

### FIGURE 18-11: TYPICAL AND MAXIMUM $\triangle$ ITMR1 vs. VDD OVER TEMPERATURE (-10°C TO +70°C, TIMER1 WITH OSCILLATOR, XTAL = 32 kHz, C1 AND C2 = 47 pF)

28-Lead QFN

28-Lead SSOP

Example

Example

28-Lead SOIC

Example

28-Lead PDIP (Skinny DIP)

Example

44-Lead QFN

$\mathbf{N}$

XXXXXXXXXXX

Package Marking Information (Cont'd)

NOTES:

### Worldwide Sales and Service

#### AMERICAS

Corporate Office 2355 West Chandler Blvd. Chandler, AZ 85224-6199 Tel: 480-792-7200 Fax: 480-792-7277 Technical Support: http://www.microchip.com/ support Web Address: www.microchip.com

Atlanta Duluth, GA Tel: 678-957-9614 Fax: 678-957-1455

Boston Westborough, MA Tel: 774-760-0087 Fax: 774-760-0088

Chicago Itasca, IL Tel: 630-285-0071 Fax: 630-285-0075

**Cleveland** Independence, OH Tel: 216-447-0464 Fax: 216-447-0643

**Dallas** Addison, TX Tel: 972-818-7423 Fax: 972-818-2924

Detroit Farmington Hills, MI Tel: 248-538-2250 Fax: 248-538-2260

Indianapolis Noblesville, IN Tel: 317-773-8323 Fax: 317-773-5453

Los Angeles Mission Viejo, CA Tel: 949-462-9523 Fax: 949-462-9608

Santa Clara Santa Clara, CA Tel: 408-961-6444 Fax: 408-961-6445

Toronto Mississauga, Ontario, Canada Tel: 905-673-0699 Fax: 905-673-6509

#### ASIA/PACIFIC

Asia Pacific Office Suites 3707-14, 37th Floor Tower 6, The Gateway Harbour City, Kowloon Hong Kong Tel: 852-2401-1200 Fax: 852-2401-3431 Australia - Sydney

Tel: 61-2-9868-6733 Fax: 61-2-9868-6755 China - Beijing

Tel: 86-10-8569-7000 Fax: 86-10-8528-2104

**China - Chengdu** Tel: 86-28-8665-5511 Fax: 86-28-8665-7889

**China - Chongqing** Tel: 86-23-8980-9588 Fax: 86-23-8980-9500

**China - Hangzhou** Tel: 86-571-2819-3187 Fax: 86-571-2819-3189

**China - Hong Kong SAR** Tel: 852-2943-5100 Fax: 852-2401-3431

**China - Nanjing** Tel: 86-25-8473-2460

Fax: 86-25-8473-2470 China - Qingdao Tel: 86-532-8502-7355 Fax: 86-532-8502-7205

**China - Shanghai** Tel: 86-21-5407-5533 Fax: 86-21-5407-5066

**China - Shenyang** Tel: 86-24-2334-2829 Fax: 86-24-2334-2393

**China - Shenzhen** Tel: 86-755-8864-2200 Fax: 86-755-8203-1760

**China - Wuhan** Tel: 86-27-5980-5300 Fax: 86-27-5980-5118

**China - Xian** Tel: 86-29-8833-7252 Fax: 86-29-8833-7256

**China - Xiamen** Tel: 86-592-2388138 Fax: 86-592-2388130

**China - Zhuhai** Tel: 86-756-3210040 Fax: 86-756-3210049

#### ASIA/PACIFIC

India - Bangalore Tel: 91-80-3090-4444 Fax: 91-80-3090-4123

India - New Delhi Tel: 91-11-4160-8631 Fax: 91-11-4160-8632

India - Pune Tel: 91-20-2566-1512 Fax: 91-20-2566-1513

**Japan - Osaka** Tel: 81-6-6152-7160 Fax: 81-6-6152-9310

**Japan - Tokyo** Tel: 81-3-6880- 3770 Fax: 81-3-6880-3771

**Korea - Daegu** Tel: 82-53-744-4301 Fax: 82-53-744-4302

Korea - Seoul Tel: 82-2-554-7200 Fax: 82-2-558-5932 or 82-2-558-5934

Malaysia - Kuala Lumpur Tel: 60-3-6201-9857 Fax: 60-3-6201-9859

**Malaysia - Penang** Tel: 60-4-227-8870 Fax: 60-4-227-4068

Philippines - Manila Tel: 63-2-634-9065 Fax: 63-2-634-9069

**Singapore** Tel: 65-6334-8870 Fax: 65-6334-8850

**Taiwan - Hsin Chu** Tel: 886-3-5778-366 Fax: 886-3-5770-955

Taiwan - Kaohsiung Tel: 886-7-213-7828 Fax: 886-7-330-9305

**Taiwan - Taipei** Tel: 886-2-2508-8600 Fax: 886-2-2508-0102

**Thailand - Bangkok** Tel: 66-2-694-1351 Fax: 66-2-694-1350

#### EUROPE

Austria - Wels Tel: 43-7242-2244-39 Fax: 43-7242-2244-393 Denmark - Copenhagen Tel: 45-4450-2828

France - Paris Tel: 33-1-69-53-63-20 Fax: 33-1-69-30-90-79

Fax: 45-4485-2829

**Germany - Munich** Tel: 49-89-627-144-0 Fax: 49-89-627-144-44

Italy - Milan Tel: 39-0331-742611 Fax: 39-0331-466781

Netherlands - Drunen Tel: 31-416-690399 Fax: 31-416-690340

**Spain - Madrid** Tel: 34-91-708-08-90 Fax: 34-91-708-08-91

**UK - Wokingham** Tel: 44-118-921-5869 Fax: 44-118-921-5820

11/29/12