Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Detuils                    |                                                                             |

|----------------------------|-----------------------------------------------------------------------------|

| Product Status             | Obsolete                                                                    |

| Core Processor             | PIC                                                                         |

| Core Size                  | 8-Bit                                                                       |

| Speed                      | 10MHz                                                                       |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                           |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                       |

| Number of I/O              | 33                                                                          |

| Program Memory Size        | 7KB (4K x 14)                                                               |

| Program Memory Type        | FLASH                                                                       |

| EEPROM Size                | 128 x 8                                                                     |

| RAM Size                   | 192 x 8                                                                     |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 5.5V                                                                   |

| Data Converters            | A/D 8x10b                                                                   |

| Oscillator Type            | External                                                                    |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                           |

| Mounting Type              | Surface Mount                                                               |

| Package / Case             | 44-VQFN Exposed Pad                                                         |

| Supplier Device Package    | 44-QFN (8x8)                                                                |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16lf874at-i-ml |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| Pin Name          | PDIP<br>Pin# | PLCC<br>Pin# | TQFP<br>Pin# | QFN<br>Pin# | I/O/P<br>Type | Buffer<br>Type        | Description                                          |

|-------------------|--------------|--------------|--------------|-------------|---------------|-----------------------|------------------------------------------------------|

|                   |              |              |              |             |               |                       | PORTB is a bidirectional I/O port. PORTB can be      |

|                   |              |              |              |             |               |                       | software programmed for internal weak pull-up on all |

|                   |              |              |              |             |               |                       | inputs.                                              |

| RB0/INT           | 33           | 36           | 8            | 9           |               | TTL/ST <sup>(1)</sup> |                                                      |

| RB0               |              |              |              |             | I/O           |                       | Digital I/O.                                         |

| INT               |              |              |              |             | I             |                       | External interrupt.                                  |

| RB1               | 34           | 37           | 9            | 10          | I/O           | TTL                   | Digital I/O.                                         |

| RB2               | 35           | 38           | 10           | 11          | I/O           | TTL                   | Digital I/O.                                         |

| RB3/PGM           | 36           | 39           | 11           | 12          |               | TTL                   |                                                      |

| RB3               |              |              |              |             | I/O           |                       | Digital I/O.                                         |

| PGM               |              |              |              |             | I             |                       | Low-voltage ICSP programming enable pin.             |

| RB4               | 37           | 41           | 14           | 14          | I/O           | TTL                   | Digital I/O.                                         |

| RB5               | 38           | 42           | 15           | 15          | I/O           | TTL                   | Digital I/O.                                         |

| RB6/PGC           | 39           | 43           | 16           | 16          |               | TTL/ST <sup>(2)</sup> |                                                      |

| RB6               |              |              |              |             | I/O           |                       | Digital I/O.                                         |

| PGC               |              |              |              |             | I             |                       | In-circuit debugger and ICSP programming clock.      |

| RB7/PGD           | 40           | 44           | 17           | 17          |               | TTL/ST <sup>(2)</sup> |                                                      |

| RB7               |              |              |              |             | I/O           |                       | Digital I/O.                                         |

| PGD               |              |              |              |             | I/O           |                       | In-circuit debugger and ICSP programming data.       |

| Legend: I = input | 0            | = outpu      | t            | I/O = i     | input/outp    | out F                 | p = power                                            |

#### TABLE 1-3: PIC16F874A/877A PINOUT DESCRIPTION (CONTINUED)

Legend: I = input O = output — = Not used TTL = TTL input

ST = Schmitt Trigger input

Note 1: This buffer is a Schmitt Trigger input when configured as the external interrupt.

2: This buffer is a Schmitt Trigger input when used in Serial Programming mode.

3: This buffer is a Schmitt Trigger input when configured in RC Oscillator mode and a CMOS input otherwise.

| TABLE 1-3:      |              |          | 1            |                 |               | `````````````````````````````````````` | ONTINUED)                                                       |

|-----------------|--------------|----------|--------------|-----------------|---------------|----------------------------------------|-----------------------------------------------------------------|

| Pin Name        | PDII<br>Pin# |          | TQFP<br>Pin# | QFN<br>Pin#     | I/O/P<br>Type | Buffer<br>Type                         | Description                                                     |

|                 |              |          |              |                 |               |                                        | PORTD is a bidirectional I/O port or Parallel Slave             |

|                 |              |          |              |                 |               |                                        | Port when interfacing to a microprocessor bus.                  |

| RD0/PSP0        | 19           | 21       | 38           | 38              |               | ST/TTL <sup>(3)</sup>                  |                                                                 |

| RD0             |              |          |              |                 | I/O           |                                        | Digital I/O.                                                    |

| PSP0            |              |          |              |                 | I/O           |                                        | Parallel Slave Port data.                                       |

| RD1/PSP1        | 20           | 22       | 39           | 39              |               | ST/TTL <sup>(3)</sup>                  |                                                                 |

| RD1             |              |          |              |                 | I/O           |                                        | Digital I/O.                                                    |

| PSP1            |              |          |              |                 | I/O           | (2)                                    | Parallel Slave Port data.                                       |

| RD2/PSP2        | 21           | 23       | 40           | 40              |               | ST/TTL <sup>(3)</sup>                  |                                                                 |

| RD2<br>PSP2     |              |          |              |                 | I/O<br>I/O    |                                        | Digital I/O.<br>Parallel Slave Port data.                       |

| -               |              |          |              |                 | 1/0           | o = (=== (3)                           | Parallel Slave Port data.                                       |

| RD3/PSP3        | 22           | 24       | 41           | 41              | I/O           | ST/TTL <sup>(3)</sup>                  |                                                                 |

| RD3<br>PSP3     |              |          |              |                 | 1/O<br>1/O    |                                        | Digital I/O.<br>Parallel Slave Port data.                       |

|                 | 07           | 20       | 0            | 0               | 1/0           | ST/TTL <sup>(3)</sup>                  |                                                                 |

| RD4/PSP4<br>RD4 | 27           | 30       | 2            | 2               | I/O           | 51/11L*/                               | Digital I/O.                                                    |

| PSP4            |              |          |              |                 | 1/O           |                                        | Parallel Slave Port data.                                       |

| RD5/PSP5        | 28           | 31       | 3            | 3               |               | ST/TTL <sup>(3)</sup>                  |                                                                 |

| RD5             | 20           | 51       | 5            | 5               | I/O           | 31/112.7                               | Digital I/O.                                                    |

| PSP5            |              |          |              |                 | I/O           |                                        | Parallel Slave Port data.                                       |

| RD6/PSP6        | 29           | 32       | 4            | 4               |               | ST/TTL <sup>(3)</sup>                  |                                                                 |

| RD6             | 20           | 02       | -            | -               | I/O           | OWITE                                  | Digital I/O.                                                    |

| PSP6            |              |          |              |                 | I/O           |                                        | Parallel Slave Port data.                                       |

| RD7/PSP7        | 30           | 33       | 5            | 5               |               | ST/TTL <sup>(3)</sup>                  |                                                                 |

| RD7             |              |          | Ũ            | Ŭ               | I/O           | 0.,                                    | Digital I/O.                                                    |

| PSP7            |              |          |              |                 | I/O           |                                        | Parallel Slave Port data.                                       |

|                 |              |          |              |                 |               |                                        | PORTE is a bidirectional I/O port.                              |

| RE0/RD/AN5      | 8            | 9        | 25           | 25              |               | ST/TTL(3)                              |                                                                 |

| RE0             | _            | _        | _            |                 | I/O           |                                        | Digital I/O.                                                    |

| RD              |              |          |              |                 | I             |                                        | Read control for Parallel Slave Port.                           |

| AN5             |              |          |              |                 | I             |                                        | Analog input 5.                                                 |

| RE1/WR/AN6      | 9            | 10       | 26           | 26              |               | ST/TTL <sup>(3)</sup>                  |                                                                 |

| RE1             |              |          |              |                 | I/O           |                                        | Digital I/O.                                                    |

| WR              |              |          |              |                 |               |                                        | Write control for Parallel Slave Port.                          |

| AN6             |              |          |              |                 | I             | (2)                                    | Analog input 6.                                                 |

| RE2/CS/AN7      | 10           | 11       | 27           | 27              |               | ST/TTL <sup>(3)</sup>                  |                                                                 |

| RE2<br>CS       |              |          |              |                 | I/O           |                                        | Digital I/O.<br>Chip coloct control for Parallel Slove Part     |

| AN7             |              |          |              |                 |               |                                        | Chip select control for Parallel Slave Port.<br>Analog input 7. |

| Vss             | 10.0         | 1 13, 34 | 6.20         | 6 20            | P             |                                        |                                                                 |

| v               | 12, 3        | 1 13, 34 | 6, 29        | 6, 30,<br>31    |               |                                        | Ground reference for logic and I/O pins.                        |

| Vdd             | 11, 3        | 2 12, 35 | 7, 28        | 7, 8,<br>28, 29 | Р             | —                                      | Positive supply for logic and I/O pins.                         |

| NC              | <u> </u>     | 1, 17,   | 12,13,       | 13              |               | _                                      | These pins are not internally connected. These pins             |

|                 | 1            | 28, 40   | 33, 34       | -               |               |                                        | should be left unconnected.                                     |

#### TARI E 1-3. PIC16E8744/8774 PINOLIT DESCRIPTION (CONTINUED)

= input I. — = Not used TTL = TTL input

I/O = input/output I ST = Schmitt Trigger input

Note 1: This buffer is a Schmitt Trigger input when configured as the external interrupt.2: This buffer is a Schmitt Trigger input when used in Serial Programming mode.

3: This buffer is a Schmitt Trigger input when configured in RC Oscillator mode and a CMOS input otherwise.

An example of the complete four-word write sequence is shown in Example 3-4. The initial address is loaded into the EEADRH:EEADR register pair; the four words of data are loaded using indirect addressing.

#### EXAMPLE 3-4: WRITING TO FLASH PROGRAM MEMORY

; This write routine assumes the following: ; 1. A valid starting address (the least significant bits = '00') is loaded in ADDRH:ADDRL ; 2. The 8 bytes of data are loaded, starting at the address in DATADDR ; 3. ADDRH, ADDRL and DATADDR are all located in shared data memory 0x70 - 0x7f ; BSF STATUS, RP1 ; ; Bank 2 BCF STATUS, RPO ; Load initial address MOVF ADDRH,W MOVWF EEADRH MOVF ADDRL,W ; MOVWF EEADR MOVF DATAADDR,W ; Load initial data address MOVWF FSR ; Load first data byte into lower LOOP MOVF INDF,W MOVWF EEDATA ; INCF FSR,F ; Next byte INDF,W MOVE ; Load second data byte into upper MOVWF EEDATH : INCF FSR,F ; ; Bank 3 STATUS, RPO BSF EECON1, EEPGD BSF ; Point to program memory ; Enable writes BSF EECON1,WREN BCF INTCON, GIE ; Disable interrupts (if using) MOVLW 55h ; Start of required write sequence: MOVWF EECON2 ; Write 55h MOVLW AAh ; Write AAh MOVWF EECON2 BSF EECON1,WR ; Set WR bit to begin write NOP ; Any instructions here are ignored as processor ; halts to begin write sequence NOP ; processor will stop here and wait for write complete ; after write processor continues with 3rd instruction EECON1,WREN BCF ; Disable writes INTCON, GIE ; Enable interrupts (if using) BSF BCF STATUS, RPO ; Bank 2 INCE EEADR, F ; Increment address ; Check if lower two bits of address are `00' MOVF EEADR,W ANDLW ; Indicates when four words have been programmed 0x03 XORLW 0x03 ; BTFSC STATUS,Z ; Exit if more than four words, GOTO ; Continue if less than four words LOOP

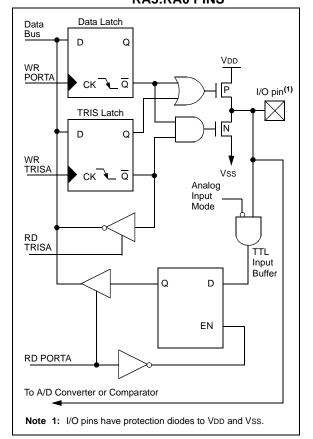

### 4.0 I/O PORTS

Some pins for these I/O ports are multiplexed with an alternate function for the peripheral features on the device. In general, when a peripheral is enabled, that pin may not be used as a general purpose I/O pin.

Additional information on I/O ports may be found in the PIC<sup>®</sup> Mid-Range Reference Manual (DS33023).

### 4.1 PORTA and the TRISA Register

PORTA is a 6-bit wide, bidirectional port. The corresponding data direction register is TRISA. Setting a TRISA bit (= 1) will make the corresponding PORTA pin an input (i.e., put the corresponding output driver in a High-Impedance mode). Clearing a TRISA bit (= 0) will make the corresponding PORTA pin an output (i.e., put the contents of the output latch on the selected pin).

Reading the PORTA register reads the status of the pins, whereas writing to it will write to the port latch. All write operations are read-modify-write operations. Therefore, a write to a port implies that the port pins are read, the value is modified and then written to the port data latch.

Pin RA4 is multiplexed with the Timer0 module clock input to become the RA4/T0CKI pin. The RA4/T0CKI pin is a Schmitt Trigger input and an open-drain output. All other PORTA pins have TTL input levels and full CMOS output drivers.

Other PORTA pins are multiplexed with analog inputs and the analog VREF input for both the A/D converters and the comparators. The operation of each pin is selected by clearing/setting the appropriate control bits in the ADCON1 and/or CMCON registers.

| Note: | On a Power-on Reset, these pins are con-  |  |  |  |  |  |  |  |

|-------|-------------------------------------------|--|--|--|--|--|--|--|

|       | figured as analog inputs and read as '0'. |  |  |  |  |  |  |  |

|       | The comparators are in the off (digital)  |  |  |  |  |  |  |  |

|       | state.                                    |  |  |  |  |  |  |  |

The TRISA register controls the direction of the port pins even when they are being used as analog inputs. The user must ensure the bits in the TRISA register are maintained set when using them as analog inputs.

#### EXAMPLE 4-1: INITIALIZING PORTA

| BCF   | STATUS, |     | ;                       |

|-------|---------|-----|-------------------------|

| BCF   | STATUS, | RP1 | ; Bank0                 |

| CLRF  | PORTA   |     | ; Initialize PORTA by   |

|       |         |     | ; clearing output       |

|       |         |     | ; data latches          |

| BSF   | STATUS, | RP0 | ; Select Bank 1         |

| MOVLW | 0x06    |     | ; Configure all pins    |

| MOVWF | ADCON1  |     | ; as digital inputs     |

| MOVLW | 0xCF    |     | ; Value used to         |

|       |         |     | ; initialize data       |

|       |         |     | ; direction             |

| MOVWF | TRISA   |     | ; Set RA<3:0> as inputs |

|       |         |     | ; RA<5:4> as outputs    |

|       |         |     | ; TRISA<7:6>are always  |

|       |         |     | ; read as '0'.          |

|       |         |     |                         |

BLOCK DIAGRAM OF RA3:RA0 PINS

| Name                   | Bit#  | Buffer                | Function                                                                                                                                          |

|------------------------|-------|-----------------------|---------------------------------------------------------------------------------------------------------------------------------------------------|

| RB0/INT                | bit 0 | TTL/ST <sup>(1)</sup> | Input/output pin or external interrupt input. Internal software programmable weak pull-up.                                                        |

| RB1                    | bit 1 | TTL                   | Input/output pin. Internal software programmable weak pull-up.                                                                                    |

| RB2                    | bit 2 | TTL                   | Input/output pin. Internal software programmable weak pull-up.                                                                                    |

| RB3/PGM <sup>(3)</sup> | bit 3 | TTL                   | Input/output pin or programming pin in LVP mode. Internal software programmable weak pull-up.                                                     |

| RB4                    | bit 4 | TTL                   | Input/output pin (with interrupt-on-change). Internal software programmable weak pull-up.                                                         |

| RB5                    | bit 5 | TTL                   | Input/output pin (with interrupt-on-change). Internal software programmable weak pull-up.                                                         |

| RB6/PGC                | bit 6 | TTL/ST <sup>(2)</sup> | Input/output pin (with interrupt-on-change) or in-circuit debugger pin.<br>Internal software programmable weak pull-up. Serial programming clock. |

| RB7/PGD                | bit 7 | TTL/ST <sup>(2)</sup> | Input/output pin (with interrupt-on-change) or in-circuit debugger pin.<br>Internal software programmable weak pull-up. Serial programming data.  |

#### TABLE 4-3:PORTB FUNCTIONS

**Legend:** TTL = TTL input, ST = Schmitt Trigger input

**Note 1:** This buffer is a Schmitt Trigger input when configured as the external interrupt.

2: This buffer is a Schmitt Trigger input when used in Serial Programming mode or in-circuit debugger.

**3:** Low-Voltage ICSP Programming (LVP) is enabled by default which disables the RB3 I/O function. LVP must be disabled to enable RB3 as an I/O pin and allow maximum compatibility to the other 28-pin and 40-pin mid-range devices.

| TABLE 4-4: S | SUMMARY OF REGISTERS ASSOCIATED WITH PORTB |

|--------------|--------------------------------------------|

|--------------|--------------------------------------------|

| Address   | Name       | Bit 7 | Bit 6                                                              | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 | Value<br>POR, I |      | Valu<br>all o<br>Res | ther |

|-----------|------------|-------|--------------------------------------------------------------------|-------|-------|-------|-------|-------|-------|-----------------|------|----------------------|------|

| 06h, 106h | PORTB      | RB7   | RB6                                                                | RB5   | RB4   | RB3   | RB2   | RB1   | RB0   | XXXX :          | xxxx | uuuu                 | uuuu |

| 86h, 186h | TRISB      | PORTB | PORTB Data Direction Register 1111 1111 1111 1111 1111 1111 1111 1 |       |       |       |       |       |       | 1111            |      |                      |      |

| 81h, 181h | OPTION_REG | RBPU  | INTEDG                                                             | TOCS  | T0SE  | PSA   | PS2   | PS1   | PS0   | 1111 1          | 1111 | 1111                 | 1111 |

|           |            |       |                                                                    |       |       |       |       |       |       |                 |      |                      |      |

**Legend:** x = unknown, u = unchanged. Shaded cells are not used by PORTB.

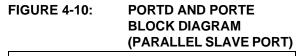

### 4.6 Parallel Slave Port

The Parallel Slave Port (PSP) is not implemented on the PIC16F873A or PIC16F876A.

PORTD operates as an 8-bit wide Parallel Slave Port, or microprocessor port, when control bit PSPMODE (TRISE<4>) is set. In Slave mode, it is asynchronously readable and writable by the external world through RD control input pin, RE0/RD/AN5, and WR control input pin, RE1/WR/AN6.

The PSP can directly interface to an 8-bit microprocessor data bus. The external microprocessor can read or write the PORTD latch as an 8-bit latch. Setting bit PSPMODE enables port pin RE0/RD/AN5 to be the RD input, RE1/WR/AN6 to be the WR input and RE2/CS/AN7 to be the CS (Chip Select) input. For this functionality, the corresponding data direction bits of the TRISE register (TRISE<2:0>) must be configured as inputs (set). The A/D port configuration bits, PCFG3:PCFG0 (ADCON1<3:0>), must be set to configure pins RE2:RE0 as digital I/O.

There are actually two 8-bit latches: one for data output and one for data input. The user writes 8-bit data to the PORTD data latch and reads data from the port pin latch (note that they have the same address). In this mode, the TRISD register is ignored since the external device is controlling the direction of data flow.

A write to the PSP occurs when both the  $\overline{CS}$  and  $\overline{WR}$ lines are first detected low. When either the  $\overline{CS}$  or  $\overline{WR}$ lines become high (level triggered), the Input Buffer Full (IBF) status flag bit (TRISE<7>) is set on the Q4 clock cycle, following the next Q2 cycle, to signal the write is complete (Figure 4-11). The interrupt flag bit, PSPIF (PIR1<7>), is also set on the same Q4 clock cycle. IBF can only be cleared by reading the PORTD input latch. The Input Buffer Overflow (IBOV) status flag bit (TRISE<5>) is set if a second write to the PSP is attempted when the previous byte has not been read out of the buffer.

A read from the PSP occurs when both the CS and RD lines are first detected low. The Output Buffer Full (OBF) status flag bit (TRISE<6>) is cleared immediately (Figure 4-12), indicating that the PORTD latch is waiting to be read by the external bus. When either the CS or RD pin becomes high (level triggered), the interrupt flag bit PSPIF is set on the Q4 clock cycle, following the next Q2 cycle, indicating that the read is complete. OBF remains low until data is written to PORTD by the user firmware. When not in PSP mode, the IBF and OBF bits are held clear. However, if flag bit IBOV was previously set, it must be cleared in firmware.

An interrupt is generated and latched into flag bit PSPIF when a read or write operation is completed. PSPIF must be cleared by the user in firmware and the interrupt can be disabled by clearing the interrupt enable bit PSPIE (PIE1<7>).

#### 9.3.8 SLEEP OPERATION

In Master mode, all module clocks are halted and the transmission/reception will remain in that state until the device wakes from Sleep. After the device returns to normal mode, the module will continue to transmit/ receive data.

In Slave mode, the SPI Transmit/Receive Shift register operates asynchronously to the device. This allows the device to be placed in Sleep mode and data to be shifted into the SPI Transmit/Receive Shift register. When all 8 bits have been received, the MSSP interrupt flag bit will be set and if enabled, will wake the device from Sleep.

#### 9.3.9 EFFECTS OF A RESET

A Reset disables the MSSP module and terminates the current transfer.

#### 9.3.10 BUS MODE COMPATIBILITY

Table 9-1 shows the compatibility between the standard SPI modes and the states of the CKP and CKE control bits.

#### TABLE 9-1: SPI BUS MODES

| Standard SPI Mode | Control Bits State |     |  |  |  |  |

|-------------------|--------------------|-----|--|--|--|--|

| Terminology       | СКР                | CKE |  |  |  |  |

| 0, 0              | 0                  | 1   |  |  |  |  |

| 0, 1              | 0                  | 0   |  |  |  |  |

| 1, 0              | 1                  | 1   |  |  |  |  |

| 1, 1              | 1                  | 0   |  |  |  |  |

There is also a SMP bit which controls when the data is sampled.

| Name    | Bit 7                | Bit 6                         | Bit 5      | Bit 4      | Bit 3       | Bit 2    | Bit 1  | Bit 0  | Valu<br>POR, | e on<br>BOR | Valu<br>all o<br>Res | ther |

|---------|----------------------|-------------------------------|------------|------------|-------------|----------|--------|--------|--------------|-------------|----------------------|------|

| INTCON  | GIE/<br>GIEH         | PEIE/<br>GIEL                 | TMR0IE     | INTOIE     | RBIE        | TMR0IF   | INTOIF | RBIF   | 0000         | 000x        | 0000                 | 000u |

| PIR1    | PSPIF <sup>(1)</sup> | ADIF                          | RCIF       | TXIF       | SSPIF       | CCP1IF   | TMR2IF | TMR1IF | 0000         | 0000        | 0000                 | 0000 |

| PIE1    | PSPIE <sup>(1)</sup> | ADIE                          | RCIE       | TXIE       | SSPIE       | CCP1IE   | TMR2IE | TMR1IE | 0000         | 0000        | 0000                 | 0000 |

| TRISC   | PORTC D              | ata Direc                     | tion Regis | ter        |             |          |        |        | 1111         | 1111        | 1111                 | 1111 |

| SSPBUF  | Synchron             | ous Seria                     | I Port Rec | eive Buffe | er/Transmit | Register |        |        | xxxx         | xxxx        | uuuu                 | uuuu |

| SSPCON  | WCOL                 | SSPOV                         | SSPEN      | CKP        | SSPM3       | SSPM2    | SSPM1  | SSPM0  | 0000         | 0000        | 0000                 | 0000 |

| TRISA   | —                    | PORTA Data Direction Register |            |            |             |          |        |        | 11           | 1111        | 11                   | 1111 |

| SSPSTAT | SMP                  | CKE                           | D/Ā        | Р          | S           | R/W      | UA     | BF     | 0000         | 0000        | 0000                 | 0000 |

#### TABLE 9-2: REGISTERS ASSOCIATED WITH SPI OPERATION

Legend: x = unknown, u = unchanged, - = unimplemented, read as '0'. Shaded cells are not used by the MSSP in SPI mode.

Note 1: The PSPIF, PSPIE and PSPIP bits are reserved on 28-pin devices; always maintain these bits clear.

| <b>REGISTER 9-3:</b> | SSPSTAT:                                                                                                                | MSSP STA                                                  | TUS REG       | SISTER (I <sup>2</sup> | C MODE)     | (ADDRESS     | 6 94h)         |           |  |  |

|----------------------|-------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------|---------------|------------------------|-------------|--------------|----------------|-----------|--|--|

|                      | R/W-0                                                                                                                   | R/W-0                                                     | R-0           | R-0                    | R-0         | R-0          | R-0            | R-0       |  |  |

|                      | SMP                                                                                                                     | CKE                                                       | D/A           | Р                      | S           | R/W          | UA             | BF        |  |  |

|                      | bit 7                                                                                                                   |                                                           |               |                        |             |              |                | bit 0     |  |  |

| bit 7                | SMP: Slew                                                                                                               | Rate Contro                                               | l bit         |                        |             |              |                |           |  |  |

|                      |                                                                                                                         | or Slave mode                                             |               |                        |             |              |                |           |  |  |

|                      |                                                                                                                         | ate control dis                                           |               |                        |             |              | 1 MHz)         |           |  |  |

| bit 6                |                                                                                                                         | ate control en                                            |               | gn-speed n             | 100e (400 K | ΠΖ)          |                |           |  |  |

| bit 0                |                                                                                                                         | or Slave mode                                             | <i>.</i>      |                        |             |              |                |           |  |  |

|                      | 1 = Enable                                                                                                              | SMBus spec                                                | ific inputs   |                        |             |              |                |           |  |  |

|                      |                                                                                                                         | e SMBus spe                                               | cific inputs  |                        |             |              |                |           |  |  |

| bit 5                |                                                                                                                         | Address bit                                               |               |                        |             |              |                |           |  |  |

|                      | <u>In Master n</u><br>Reserved.                                                                                         | node:                                                     |               |                        |             |              |                |           |  |  |

|                      | In Slave me                                                                                                             |                                                           |               |                        |             |              |                |           |  |  |

|                      |                                                                                                                         | es that the las                                           | -             |                        |             |              |                |           |  |  |

| bit 4                | • = mulcate<br><b>P:</b> Stop bit                                                                                       | es that the las                                           | si byte rece  |                        | Smilleu was | audiess      |                |           |  |  |

| 511 4                | •                                                                                                                       | es that a Stop                                            | bit has be    | en detected            | last        |              |                |           |  |  |

|                      |                                                                                                                         | t was not det                                             |               |                        |             |              |                |           |  |  |

|                      | Note:                                                                                                                   | This bit is clo                                           | eared on Re   | eset and wh            | nen SSPEN   | is cleared.  |                |           |  |  |

| bit 3                | S: Start bit                                                                                                            |                                                           |               |                        |             |              |                |           |  |  |

|                      |                                                                                                                         | es that a Star<br>t was not det                           |               | en detectec            | llast       |              |                |           |  |  |

|                      | Note:                                                                                                                   | This bit is cl                                            |               | eset and wh            | nen SSPEN   | is cleared   |                |           |  |  |

| bit 2                | _                                                                                                                       | Write bit info                                            |               |                        |             |              |                |           |  |  |

| 511 2                | In Slave me                                                                                                             |                                                           |               |                        | y)          |              |                |           |  |  |

|                      | 1 = Read                                                                                                                |                                                           |               |                        |             |              |                |           |  |  |

|                      | 0 = Write                                                                                                               |                                                           |               |                        |             |              |                | <b></b>   |  |  |

|                      | Note:                                                                                                                   | This bit hold<br>only valid fro                           |               |                        |             |              |                |           |  |  |

|                      | In Master n                                                                                                             |                                                           |               |                        |             |              |                |           |  |  |

|                      | <ul> <li>1 = Transmit is in progress</li> <li>0 = Transmit is not in progress</li> </ul>                                |                                                           |               |                        |             |              |                |           |  |  |

|                      | Note:                                                                                                                   | ORing this b                                              | -             | , RSEN, PE             | N, RCEN o   | r ACKEN will | indicate if th | e MSSP is |  |  |

|                      |                                                                                                                         | in Idle mode                                              |               |                        |             |              |                |           |  |  |

| bit 1                | UA: Update                                                                                                              | e Address (10                                             | D-bit Slave i | mode only)             |             |              |                |           |  |  |

|                      |                                                                                                                         | es that the us                                            |               | •                      | address in  | the SSPADE   | D register     |           |  |  |

|                      |                                                                                                                         | s does not ne                                             | •             | odated                 |             |              |                |           |  |  |

| bit 0                | BF: Buffer Full Status bit                                                                                              |                                                           |               |                        |             |              |                |           |  |  |

|                      |                                                                                                                         | In Transmit mode:<br>1 = Receive complete, SSPBUF is full |               |                        |             |              |                |           |  |  |

|                      | 0 = Receive not complete, SSPBUF is empty                                                                               |                                                           |               |                        |             |              |                |           |  |  |

|                      | In Receive mode:<br>1 = Data Transmit in progress (does not include the $\overline{ACK}$ and Stop bits), SSPBUF is full |                                                           |               |                        |             |              |                |           |  |  |

|                      |                                                                                                                         | ransmit in pro                                            |               |                        |             |              |                |           |  |  |

|                      | Legend:                                                                                                                 |                                                           |               |                        |             |              |                |           |  |  |

|                      | R = Reada                                                                                                               | ble bit                                                   | W = W         | ritable bit            | U = Unir    | nplemented   | bit, read as ' | 0'        |  |  |

|                      | - n = Value                                                                                                             |                                                           | '1' = Bi      |                        |             | is cleared   | x = Bit is u   |           |  |  |

|                      |                                                                                                                         |                                                           |               |                        |             |              |                |           |  |  |

#### 9.4.14 SLEEP OPERATION

While in Sleep mode, the  $I^2C$  module can receive addresses or data and when an address match or complete byte transfer occurs, wake the processor from Sleep (if the MSSP interrupt is enabled).

#### 9.4.15 EFFECT OF A RESET

A Reset disables the MSSP module and terminates the current transfer.

#### 9.4.16 MULTI-MASTER MODE

In Multi-Master mode, the interrupt generation on the detection of the Start and Stop conditions allows the determination of when the bus is free. The Stop (P) and Start (S) bits are cleared from a Reset or when the MSSP module is disabled. Control of the  $I^2C$  bus may be taken when the P bit (SSPSTAT<4>) is set, or the bus is Idle, with both the S and P bits clear. When the bus is busy, enabling the SSP interrupt will generate the interrupt when the Stop condition occurs.

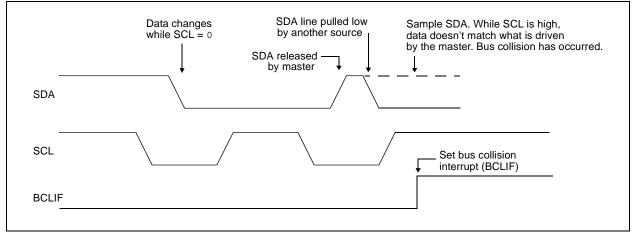

In multi-master operation, the SDA line must be monitored for arbitration to see if the signal level is at the expected output level. This check is performed in hardware with the result placed in the BCLIF bit.

The states where arbitration can be lost are:

- · Address Transfer

- Data Transfer

- A Start Condition

- A Repeated Start Condition

- An Acknowledge Condition

#### 9.4.17 MULTI -MASTER COMMUNICATION, BUS COLLISION AND BUS ARBITRATION

Multi-Master mode support is achieved by bus arbitration. When the master outputs address/data bits onto the SDA pin, arbitration takes place when the master outputs a '1' on SDA by letting SDA float high and another master asserts a '0'. When the SCL pin floats high, data should be stable. If the expected data on SDA is a '1' and the data sampled on the SDA pin = 0, then a bus collision has taken place. The master will set the Bus Collision Interrupt Flag, BCLIF, and reset the  $I^2C$  port to its Idle state (Figure 9-25).

If a transmit was in progress when the bus collision occurred, the transmission is halted, the BF flag is cleared, the SDA and SCL lines are deasserted and the SSPBUF can be written to. When the user services the bus collision Interrupt Service Routine and if the  $I^2C$  bus is free, the user can resume communication by asserting a Start condition.

If a Start, Repeated Start, Stop or Acknowledge condition was in progress when the bus collision occurred, the condition is aborted, the SDA and SCL lines are deasserted and the respective control bits in the SSPCON2 register are cleared. When the user services the bus collision Interrupt Service Routine and if the I<sup>2</sup>C bus is free, the user can resume communication by asserting a Start condition.

The Master will continue to monitor the SDA and SCL pins. If a Stop condition occurs, the SSPIF bit will be set.

A write to the SSPBUF will start the transmission of data at the first data bit regardless of where the transmitter left off when the bus collision occurred.

In Multi-Master mode, the interrupt generation on the detection of Start and Stop conditions allows the determination of when the bus is free. Control of the  $I^2C$  bus can be taken when the P bit is set in the SSPSTAT register or the bus is Idle and the S and P bits are cleared.

#### FIGURE 9-25: BUS COLLISION TIMING FOR TRANSMIT AND ACKNOWLEDGE

© 2001-2013 Microchip Technology Inc.

### 14.3 Reset

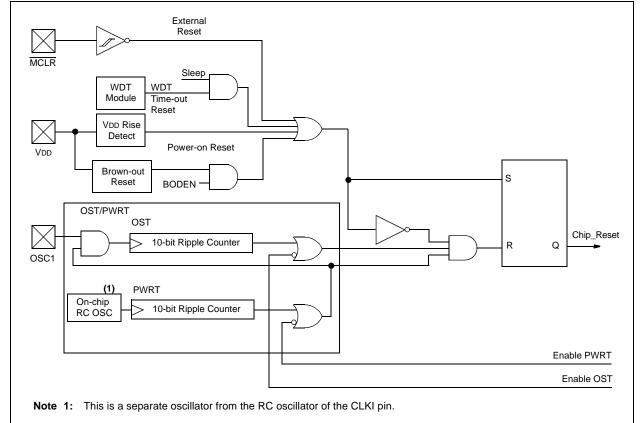

The PIC16F87XA differentiates between various kinds of Reset:

- Power-on Reset (POR)

- MCLR Reset during normal operation

- MCLR Reset during Sleep

- WDT Reset (during normal operation)

- WDT Wake-up (during Sleep)

- Brown-out Reset (BOR)

Some registers are not affected in any Reset condition. Their status is unknown on POR and unchanged in any other Reset. Most other registers are reset to a "Reset state" on Power-on Reset (POR), on the MCLR and WDT Reset, on MCLR Reset during Sleep and Brownout Reset (BOR). They are not affected by a WDT wake-up which is viewed as the resumption of normal operation. The TO and PD bits are set or cleared differently in different Reset situations as indicated in Table 14-4. These bits are used in software to determine the nature of the Reset. See Table 14-6 for a full description of Reset states of all registers.

A simplified block diagram of the on-chip Reset circuit is shown in Figure 14-4.

#### FIGURE 14-4: SIMPLIFIED BLOCK DIAGRAM OF ON-CHIP RESET CIRCUIT

| TABLE 15-2: PIC16 | F87XA INSTRUCTION SET |

|-------------------|-----------------------|

|-------------------|-----------------------|

| Mnemonic,<br>Operands                  |      | Description                                    | Cycles        | 14-Bit Opcode |      |      |      | Status   | Notos |

|----------------------------------------|------|------------------------------------------------|---------------|---------------|------|------|------|----------|-------|

|                                        |      | Description                                    | Cycles        | MSb           |      |      | LSb  | Affected | Notes |

| BYTE-ORIENTED FILE REGISTER OPERATIONS |      |                                                |               |               |      |      |      |          |       |

| ADDWF                                  | f, d | Add W and f                                    | 1             | 00            | 0111 | dfff | ffff | C,DC,Z   | 1,2   |

| ANDWF                                  | f, d | AND W with f                                   | 1             | 00            | 0101 | dfff | ffff | Z        | 1,2   |

| CLRF                                   | f    | Clear f                                        | 1             | 00            | 0001 | lfff | ffff | Z        | 2     |

| CLRW                                   | -    | Clear W                                        | 1             | 00            | 0001 | 0xxx | xxxx | Z        |       |

| COMF                                   | f, d | Complement f                                   | 1             | 00            | 1001 | dfff | ffff | Z        | 1,2   |

| DECF                                   | f, d | Decrement f                                    | 1             | 00            | 0011 | dfff | ffff | Z        | 1,2   |

| DECFSZ                                 | f, d | Decrement f, Skip if 0                         | 1(2)          | 00            | 1011 | dfff | ffff |          | 1,2,3 |

| INCF                                   | f, d | Increment f                                    | 1             | 00            | 1010 | dfff | ffff | Z        | 1,2   |

| INCFSZ                                 | f, d | Increment f, Skip if 0                         | 1(2)          | 00            | 1111 | dfff | ffff |          | 1,2,3 |

| IORWF                                  | f, d | Inclusive OR W with f                          | 1             | 00            | 0100 | dfff | ffff | Z        | 1,2   |

| MOVF                                   | f, d | Move f                                         | 1             | 00            | 1000 | dfff | ffff | Z        | 1,2   |

| MOVWF                                  | f    | Move W to f                                    | 1             | 00            | 0000 | lfff | ffff |          |       |

| NOP                                    | -    | No Operation                                   | 1             | 00            | 0000 | 0xx0 | 0000 |          |       |

| RLF                                    | f, d | Rotate Left f through Carry                    | 1             | 00            | 1101 | dfff | ffff | С        | 1,2   |

| RRF                                    | f, d | Rotate Right f through Carry                   | 1             | 00            | 1100 | dfff | ffff | С        | 1,2   |

| SUBWF                                  | f, d | Subtract W from f                              | 1             | 00            | 0010 | dfff | ffff | C,DC,Z   | 1,2   |

| SWAPF                                  | f, d | Swap nibbles in f                              | 1             | 00            | 1110 | dfff | ffff |          | 1,2   |

| XORWF                                  | f, d | Exclusive OR W with f                          | 1             | 00            | 0110 | dfff | ffff | Z        | 1,2   |

|                                        |      | BIT-ORIENTED FILE                              | REGISTER OPER | ATION         | ١S   |      |      |          |       |

| BCF                                    | f, b | Bit Clear f                                    | 1             | 01            | 00bb | bfff | ffff |          | 1,2   |

| BSF                                    | f, b | Bit Set f                                      | 1             | 01            | 01bb | bfff | ffff |          | 1,2   |

| BTFSC                                  | f, b | Bit Test f, Skip if Clear                      | 1 (2)         | 01            | 10bb | bfff | ffff |          | 3     |

| BTFSS                                  | f, b | Bit Test f, Skip if Set                        | 1 (2)         | 01            | 11bb | bfff | ffff |          | 3     |

|                                        |      | LITERAL AND CO                                 | NTROL OPERAT  | IONS          |      |      |      |          |       |

| ADDLW                                  | k    | Add Literal and W                              | 1             | 11            | 111x | kkkk | kkkk | C,DC,Z   |       |

| ANDLW                                  | k    | AND Literal with W                             | 1             | 11            | 1001 | kkkk | kkkk | Z        |       |

| CALL                                   | k    | Call Subroutine                                | 2             | 10            | 0kkk | kkkk | kkkk |          |       |

| CLRWDT                                 | -    | Clear Watchdog Timer                           | 1             | 00            | 0000 | 0110 | 0100 | TO,PD    |       |

| GOTO                                   | k    | Go to Address                                  | 2             | 10            | 1kkk | kkkk | kkkk | -        |       |

| IORLW                                  | k    | Inclusive OR Literal with W                    | 1             | 11            | 1000 | kkkk | kkkk | Z        |       |

| MOVLW                                  | k    | Move Literal to W                              | 1             | 11            | 00xx | kkkk | kkkk |          |       |

| RETFIE                                 | -    | Return from Interrupt                          | 2             | 00            | 0000 | 0000 | 1001 |          |       |

| RETLW                                  | k    | Return with Literal in W                       | 2             | 11            | 01xx | kkkk |      |          |       |

| RETURN                                 | -    | Return from Subroutine                         | 2             | 00            | 0000 | 0000 | 1000 |          |       |

| SLEEP                                  | -    | Go into Standby mode                           | 1             | 00            | 0000 | 0110 | 0011 | TO,PD    |       |

| SUBLW                                  | k    | Subtract W from Literal                        | 1             | 11            |      | kkkk |      | C,DC,Z   |       |

| XORLW                                  | k    | Exclusive OR Literal with W                    | 1             | 11            | 1010 | kkkk |      | Z        |       |

| Note 1:                                |      | I/O register is modified as a function of itse |               |               |      |      |      |          |       |

Note 1: When an I/O register is modified as a function of itself (e.g., MOVF PORTE, 1), the value used will be that value present on the pins themselves. For example, if the data latch is '1' for a pin configured as input and is driven low by an external device, the data will be written back with a '0'.

2: If this instruction is executed on the TMR0 register (and where applicable, d = 1), the prescaler will be cleared if assigned to the Timer0 module.

3: If Program Counter (PC) is modified, or a conditional test is true, the instruction requires two cycles. The second cycle is executed as a NOP.

**Note:** Additional information on the mid-range instruction set is available in the PIC<sup>®</sup> Mid-Range MCU Family Reference Manual (DS33023).

| DECFSZ           | Decrement f, Skip if 0                                                                                                                                                                                                                                                                                         |  |  |

|------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Syntax:          | [ <i>label</i> ] DECFSZ f,d                                                                                                                                                                                                                                                                                    |  |  |

| Operands:        | $\begin{array}{l} 0\leq f\leq 127\\ d\in [0,1] \end{array}$                                                                                                                                                                                                                                                    |  |  |

| Operation:       | (f) - 1 $\rightarrow$ (destination);<br>skip if result = 0                                                                                                                                                                                                                                                     |  |  |

| Status Affected: | None                                                                                                                                                                                                                                                                                                           |  |  |

| Description:     | The contents of register 'f' are decremented. If 'd' is '0', the result is placed in the W register. If 'd' is '1', the result is placed back in register 'f'.<br>If the result is '1', the next instruction is executed. If the result is '0', then a NOP is executed instead, making it a 2 TCY instruction. |  |  |

| INCFSZ           | Increment f, Skip if 0                                                                                                                                                                                                                                                                                                           |  |  |  |

|------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| Syntax:          | [label] INCFSZ f,d                                                                                                                                                                                                                                                                                                               |  |  |  |

| Operands:        | $\begin{array}{l} 0\leq f\leq 127\\ d\in [0,1] \end{array}$                                                                                                                                                                                                                                                                      |  |  |  |

| Operation:       | (f) + 1 $\rightarrow$ (destination),<br>skip if result = 0                                                                                                                                                                                                                                                                       |  |  |  |

| Status Affected: | None                                                                                                                                                                                                                                                                                                                             |  |  |  |

| Description:     | The contents of register 'f' are<br>incremented. If 'd' is '0', the result<br>is placed in the W register. If 'd' is<br>'1', the result is placed back in<br>register 'f'.<br>If the result is '1', the next instruc-<br>tion is executed. If the result is '0',<br>a NOP is executed instead, making<br>it a 2 TCY instruction. |  |  |  |

| GOTO             | Unconditional Branch                                                                                                                                                                             |  |  |  |

|------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| Syntax:          | [ <i>label</i> ] GOTO k                                                                                                                                                                          |  |  |  |

| Operands:        | $0 \le k \le 2047$                                                                                                                                                                               |  |  |  |

| Operation:       | $k \rightarrow PC<10:0>$<br>PCLATH<4:3> $\rightarrow$ PC<12:11>                                                                                                                                  |  |  |  |

| Status Affected: | None                                                                                                                                                                                             |  |  |  |

| Description:     | GOTO is an unconditional branch.<br>The eleven-bit immediate value is<br>loaded into PC bits <10:0>. The<br>upper bits of PC are loaded from<br>PCLATH<4:3>. GOTO is a<br>two-cycle instruction. |  |  |  |

| IORLW            | Inclusive OR Literal with W                                                                                               |  |  |

|------------------|---------------------------------------------------------------------------------------------------------------------------|--|--|

| Syntax:          | [ <i>label</i> ] IORLW k                                                                                                  |  |  |

| Operands:        | $0 \le k \le 255$                                                                                                         |  |  |

| Operation:       | (W) .OR. $k \rightarrow$ (W)                                                                                              |  |  |

| Status Affected: | Z                                                                                                                         |  |  |

| Description:     | The contents of the W register are<br>OR'ed with the eight-bit literal 'k'.<br>The result is placed in the W<br>register. |  |  |

| INCF             | Increment f                                                                                                                                                                | IORWF            | Inclusive OR W with f                                                                                                                                                       |

|------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [label] INCF f,d                                                                                                                                                           | Syntax:          | [ <i>label</i> ] IORWF f,d                                                                                                                                                  |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ d \in [0,1] \end{array}$                                                                                                            | Operands:        | $0 \le f \le 127$<br>$d \in [0,1]$                                                                                                                                          |

| Operation:       | (f) + 1 $\rightarrow$ (destination)                                                                                                                                        | Operation:       | (W) .OR. (f) $\rightarrow$ (destination)                                                                                                                                    |

| Status Affected: | Z                                                                                                                                                                          | Status Affected: | Z                                                                                                                                                                           |

| Description:     | The contents of register 'f' are<br>incremented. If 'd' is '0', the result<br>is placed in the W register. If 'd' is<br>'1', the result is placed back in<br>register 'f'. | Description:     | Inclusive OR the W register with<br>register 'f'. If 'd' is '0', the result is<br>placed in the W register. If 'd' is<br>'1', the result is placed back in<br>register 'f'. |

## FIGURE 18-11: TYPICAL AND MAXIMUM $\triangle$ ITMR1 vs. VDD OVER TEMPERATURE (-10°C TO +70°C, TIMER1 WITH OSCILLATOR, XTAL = 32 kHz, C1 AND C2 = 47 pF)

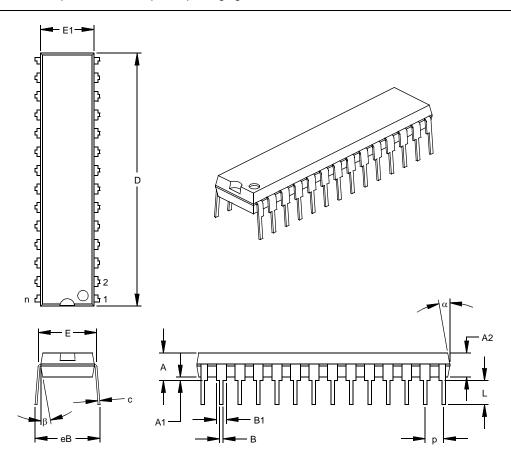

### 28-Lead Skinny Plastic Dual In-line (SP) – 300 mil (PDIP)

Note: For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

|                            | Units        |       | INCHES* |       | N     | IILLIMETERS |       |

|----------------------------|--------------|-------|---------|-------|-------|-------------|-------|

| Dimer                      | ision Limits | MIN   | NOM     | MAX   | MIN   | NOM         | MAX   |

| Number of Pins             | n            |       | 28      |       |       | 28          |       |

| Pitch                      | р            |       | .100    |       |       | 2.54        |       |

| Top to Seating Plane       | А            | .140  | .150    | .160  | 3.56  | 3.81        | 4.06  |

| Molded Package Thickness   | A2           | .125  | .130    | .135  | 3.18  | 3.30        | 3.43  |

| Base to Seating Plane      | A1           | .015  |         |       | 0.38  |             |       |

| Shoulder to Shoulder Width | E            | .300  | .310    | .325  | 7.62  | 7.87        | 8.26  |

| Molded Package Width       | E1           | .275  | .285    | .295  | 6.99  | 7.24        | 7.49  |

| Overall Length             | D            | 1.345 | 1.365   | 1.385 | 34.16 | 34.67       | 35.18 |

| Tip to Seating Plane       | L            | .125  | .130    | .135  | 3.18  | 3.30        | 3.43  |

| Lead Thickness             | С            | .008  | .012    | .015  | 0.20  | 0.29        | 0.38  |

| Upper Lead Width           | B1           | .040  | .053    | .065  | 1.02  | 1.33        | 1.65  |

| Lower Lead Width           | В            | .016  | .019    | .022  | 0.41  | 0.48        | 0.56  |

| Overall Row Spacing        | § eB         | .320  | .350    | .430  | 8.13  | 8.89        | 10.92 |

| Mold Draft Angle Top       | α            | 5     | 10      | 15    | 5     | 10          | 15    |

| Mold Draft Angle Bottom    | β            | 5     | 10      | 15    | 5     | 10          | 15    |

\* Controlling Parameter § Significant Characteristic

Notes:

Dimension D and E1 do not include mold flash or protrusions. Mold flash or protrusions shall not exceed

.010" (0.254mm) per side. JEDEC Equivalent: MO-095

Drawing No. C04-070

| Special Function Registers<br>Special Function Registers (SFRs) |     |

|-----------------------------------------------------------------|-----|

| Speed, Operating                                                |     |

| SPI Mode                                                        |     |

| Associated Registers                                            | 79  |

| Bus Mode Compatibility                                          |     |

| Effects of a Reset                                              |     |

| Enabling SPI I/O                                                | 75  |

| Master Mode                                                     |     |

| Master/Slave Connection                                         |     |

| Serial Clock                                                    |     |

| Serial Data In                                                  |     |

| Serial Data Out                                                 |     |

| Slave Select                                                    |     |

| Slave Select Synchronization                                    |     |

| Sleep Operation                                                 |     |

| SPI Clock                                                       |     |

| Typical Connection                                              |     |

| SPI Mode Requirements                                           |     |

| SS                                                              | 71  |

| SSP                                                             |     |

| SPI Master/Slave Connection                                     |     |

| SSPADD Register                                                 |     |

| SSPBUF Register                                                 |     |

| SSPCON Register                                                 |     |

| SSPCON2 Register<br>SSPIF                                       |     |

|                                                                 | -   |

| SSPOV                                                           |     |

| SSPSTAT Register                                                |     |

| R/W Bit                                                         |     |

| Overflows                                                       |     |

| Underflow                                                       |     |

| Status Register                                                 |     |

| C Bit                                                           | 22  |

| DC Bit                                                          |     |

| IRP Bit                                                         |     |

| PD Bit                                                          |     |

| RP1:RP0 Bits                                                    | ,   |

| TO Bit                                                          |     |

| Z Bit                                                           |     |

| Synchronous Master Reception                                    |     |

| Associated Registers                                            | 123 |

| Synchronous Master Transmission                                 |     |

| Associated Registers                                            | 122 |

| Synchronous Serial Port Interrupt                               |     |

| Synchronous Slave Reception                                     |     |

| Associated Registers                                            | 125 |

| Synchronous Slave Transmission                                  |     |

| Associated Registers                                            | 125 |

| -                                                               |     |

| T                                                               |     |

| T1CKPS0 Bit                                                     |     |

| T1CKPS1 Bit                                                     | -   |

| T1CON Register                                                  |     |

| T1OSCEN Bit                                                     |     |

| T1SYNC Bit                                                      |     |

| T2CKPS0 Bit                                                     |     |

| T2CKPS1 Bit                                                     | 61  |

T2CON Register

19

TAD

131

Time-out Sequence

148

| Timer0                                        | 53  |

|-----------------------------------------------|-----|

| Associated Registers                          | 55  |

| Clock Source Edge Select (T0SE Bit)           | 23  |

| Clock Source Select (T0CS Bit)                | 23  |

| External Clock                                | 54  |

| Interrupt                                     |     |

| Overflow Enable (TMR0IE Bit)                  |     |

| Overflow Flag (TMR0IF Bit)                    |     |

| Overflow Interrupt                            |     |

| Prescaler                                     |     |

| Т0СКІ                                         |     |

| Timer0 and Timer1 External Clock Requirements |     |

| Timer1                                        |     |

| Associated Registers                          |     |

| Asynchronous Counter Mode                     |     |

| Reading and Writing to                        |     |

| Counter Operation                             |     |

| Operation in Timer Mode                       |     |

| Oscillator<br>Capacitor Selection             |     |

|                                               |     |

| Prescaler<br>Resetting of Timer1 Registers    |     |

| Resetting Timer1 Using a CCP Trigger Output . |     |

| Synchronized Counter Mode                     |     |

| TMR1H                                         |     |

| TMR1L                                         |     |

| Timer2                                        |     |

| Associated Registers                          |     |

| Output                                        |     |

| Postscaler                                    |     |

| Prescaler                                     |     |

| Prescaler and Postscaler                      |     |

| Timing Diagrams                               |     |

| A/D Conversion                                | 195 |

| Acknowledge Sequence                          |     |