Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                     |

|----------------------------|----------------------------------------------------------------------------|

| Core Processor             | PIC                                                                        |

| Core Size                  | 8-Bit                                                                      |

| Speed                      | 10MHz                                                                      |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                          |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                      |

| Number of I/O              | 22                                                                         |

| Program Memory Size        | 14KB (8K x 14)                                                             |

| Program Memory Type        | FLASH                                                                      |

| EEPROM Size                | 256 x 8                                                                    |

| RAM Size                   | 368 x 8                                                                    |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 5.5V                                                                  |

| Data Converters            | A/D 5x10b                                                                  |

| Oscillator Type            | External                                                                   |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                          |

| Mounting Type              | Surface Mount                                                              |

| Package / Case             | 28-VQFN Exposed Pad                                                        |

| Supplier Device Package    | 28-QFN (6x6)                                                               |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16lf876a-i-ml |

|                            |                                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

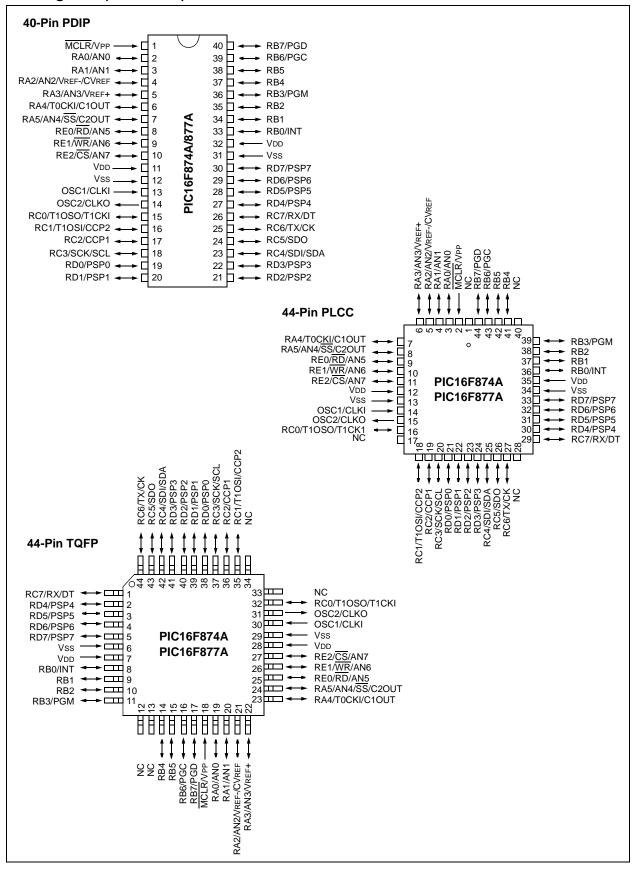

## **Pin Diagrams (Continued)**

# PIC16F87XA

|                                                     | PDIP | PLCC | TQFP | QFN  | I/O/P              | Buffer                 |                                                                                                                                                                     |

|-----------------------------------------------------|------|------|------|------|--------------------|------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Pin Name                                            | Pin# | Pin# | Pin# | Pin# | Туре               | Туре                   | Description                                                                                                                                                         |

| OSC1/CLKI<br>OSC1                                   | 13   | 14   | 30   | 32   | I                  | ST/CMOS <sup>(4)</sup> | Oscillator crystal or external clock input.<br>Oscillator crystal input or external clock source<br>input. ST buffer when configured in RC mode;<br>otherwise CMOS. |

| CLKI                                                |      |      |      |      | Ι                  |                        | External clock source input. Always associated<br>with pin function OSC1 (see OSC1/CLKI,<br>OSC2/CLKO pins).                                                        |

| OSC2/CLKO<br>OSC2                                   | 14   | 15   | 31   | 33   | 0                  | _                      | Oscillator crystal or clock output.<br>Oscillator crystal output.<br>Connects to crystal or resonator in Crystal<br>Oscillator mode.                                |

| CLKO                                                |      |      |      |      | 0                  |                        | In RC mode, OSC2 pin outputs CLKO, which<br>has 1/4 the frequency of OSC1 and denotes the<br>instruction cycle rate.                                                |

| MCLR/VPP<br>MCLR                                    | 1    | 2    | 18   | 18   | I                  | ST                     | Master Clear (input) or programming voltage (output)<br>Master Clear (Reset) input. This pin is an active<br>low Reset to the device.                               |

| Vpp                                                 |      |      |      |      | Р                  |                        | Programming voltage input.                                                                                                                                          |

|                                                     |      |      | 10   | 10   |                    |                        | PORTA is a bidirectional I/O port.                                                                                                                                  |

| RA0/AN0<br>RA0<br>AN0                               | 2    | 3    | 19   | 19   | I/O<br>I           | TTL                    | Digital I/O.<br>Analog input 0.                                                                                                                                     |

| RA1/AN1<br>RA1<br>AN1                               | 3    | 4    | 20   | 20   | I/O<br>I           | TTL                    | Digital I/O.<br>Analog input 1.                                                                                                                                     |

| RA2/AN2/VREF-/CVREF<br>RA2<br>AN2<br>VREF-<br>CVREF | 4    | 5    | 21   | 21   | I/O<br>I<br>I<br>O | TTL                    | Digital I/O.<br>Analog input 2.<br>A/D reference voltage (Low) input.<br>Comparator VREF output.                                                                    |

| RA3/AN3/Vref+<br>RA3<br>AN3<br>Vref+                | 5    | 6    | 22   | 22   | I/O<br>I<br>I      | TTL                    | Digital I/O.<br>Analog input 3.<br>A/D reference voltage (High) input.                                                                                              |

| RA4/T0CKI/C1OUT<br>RA4                              | 6    | 7    | 23   | 23   | I/O                | ST                     | Digital I/O – Open-drain when configured as output.                                                                                                                 |

| T0CKI<br>C1OUT                                      |      |      |      |      | I<br>O             |                        | Timer0 external clock input.<br>Comparator 1 output.                                                                                                                |

| RA5/AN4/SS/C2OUT<br>RA5<br>AN4<br>SS<br>C2OUT       | 7    | 8    | 24   | 24   | I/O<br>I<br>0      | TTL                    | Digital I/O.<br>Analog input 4.<br>SPI slave select input.<br>Comparator 2 output.                                                                                  |

## TABLE 1-3: PIC16F874A/877A PINOUT DESCRIPTION

— = Not used TTL = TTL input ST = Schmitt Trigger input

Note 1: This buffer is a Schmitt Trigger input when configured as the external interrupt.

This buffer is a Schmitt Trigger input when used in Serial Programming mode.

3: This buffer is a Schmitt Trigger input when configured in RC Oscillator mode and a CMOS input otherwise.

#### 2.2.2.6 **PIE2** Register

The PIE2 register contains the individual enable bits for the CCP2 peripheral interrupt, the SSP bus collision interrupt, EEPROM write operation interrupt and the comparator interrupt.

- n = Value at POR

| REGISTER 2-6: | PIE2 REG                                                                                    | ISTER (AD                     | DRESS 8         | Dh)          |         |     |     |        |  |  |

|---------------|---------------------------------------------------------------------------------------------|-------------------------------|-----------------|--------------|---------|-----|-----|--------|--|--|

|               | U-0                                                                                         | R/W-0                         | U-0             | R/W-0        | R/W-0   | U-0 | U-0 | R/W-0  |  |  |

|               |                                                                                             | CMIE                          |                 | EEIE         | BCLIE   | _   | _   | CCP2IE |  |  |

|               | bit 7                                                                                       |                               |                 |              |         |     |     | bit 0  |  |  |

|               |                                                                                             |                               |                 |              |         |     |     |        |  |  |

| bit 7         | Unimplem                                                                                    | ented: Read                   | <b>d as</b> '0' |              |         |     |     |        |  |  |

| bit 6         | CMIE: Con                                                                                   | nparator Inte                 | rrupt Enabl     | le bit       |         |     |     |        |  |  |

|               |                                                                                             | s the compa<br>the compar     |                 | -            |         |     |     |        |  |  |

| bit 5         | Unimplem                                                                                    | Unimplemented: Read as '0'    |                 |              |         |     |     |        |  |  |

| bit 4         | EEIE: EEP                                                                                   | ROM Write                     | Operation I     | nterrupt Ena | ble bit |     |     |        |  |  |

|               |                                                                                             | EEPROM v<br>EEPROM v          |                 |              |         |     |     |        |  |  |

| bit 3         | BCLIE: Bu                                                                                   | s Collision Ir                | nterrupt Ena    | able bit     |         |     |     |        |  |  |

|               |                                                                                             | bus collision<br>bus collisio | •               |              |         |     |     |        |  |  |

| bit 2-1       | Unimplem                                                                                    | ented: Read                   | <b>d as</b> '0' |              |         |     |     |        |  |  |

| bit 0         | CCP2IE: C                                                                                   | CP2 Interru                   | ot Enable b     | it           |         |     |     |        |  |  |

|               | <ul> <li>1 = Enables the CCP2 interrupt</li> <li>0 = Disables the CCP2 interrupt</li> </ul> |                               |                 |              |         |     |     |        |  |  |

|               |                                                                                             |                               |                 |              |         |     |     |        |  |  |

|               | Legend:                                                                                     |                               |                 |              |         |     |     |        |  |  |

|               | $R = Readable bit \qquad W = Writable bit \qquad U = Unimplemented bit, read as '0'$        |                               |                 |              |         |     |     |        |  |  |

'1' = Bit is set

'0' = Bit is cleared

#### Note: Bit PEIE (INTCON<6>) must be set to enable any peripheral interrupt.

x = Bit is unknown

## PIC16F87XA

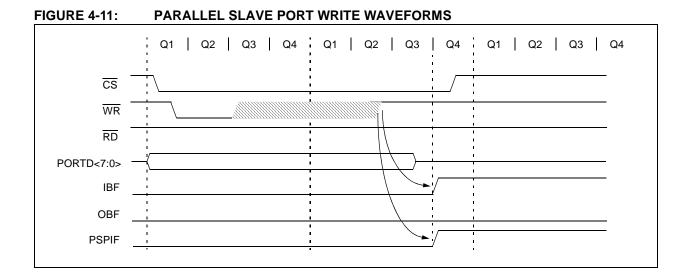

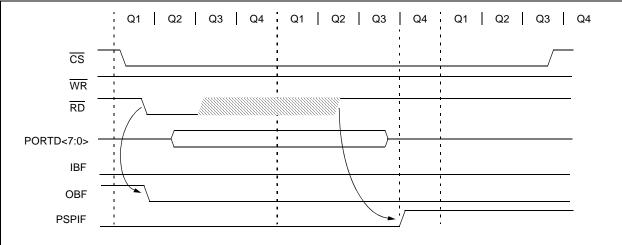

## FIGURE 4-12: PARALLEL SLAVE PORT READ WAVEFORMS

### TABLE 4-11: REGISTERS ASSOCIATED WITH PARALLEL SLAVE PORT

| Address | Name   | Bit 7                | Bit 6    | Bit 5                            | Bit 4   | Bit 3 | Bit 2   | Bit 1       | Bit 0   | Value on:<br>POR, BOR | Value on<br>all other<br>Resets |

|---------|--------|----------------------|----------|----------------------------------|---------|-------|---------|-------------|---------|-----------------------|---------------------------------|

| 08h     | PORTD  | Port Data            | Latch wh | nen written; Port pins when read |         |       |         |             |         | xxxx xxxx             | uuuu uuuu                       |

| 09h     | PORTE  | _                    | _        | _                                | _       | —     | RE2     | RE1         | RE0     | xxx                   | uuu                             |

| 89h     | TRISE  | IBF                  | OBF      | IBOV                             | PSPMODE | _     | PORTE D | ata Directi | on bits | 0000 -111             | 0000 -111                       |

| 0Ch     | PIR1   | PSPIF <sup>(1)</sup> | ADIF     | RCIF                             | TXIF    | SSPIF | CCP1IF  | TMR2IF      | TMR1IF  | 0000 0000             | 0000 0000                       |

| 8Ch     | PIE1   | PSPIE <sup>(1)</sup> | ADIE     | RCIE                             | TXIE    | SSPIE | CCP1IE  | TMR2IE      | TMR1IE  | 0000 0000             | 0000 0000                       |

| 9Fh     | ADCON1 | ADFM                 | ADCS2    | _                                | —       | PCFG3 | PCFG2   | PCFG1       | PCFG0   | 00 0000               | 00 0000                         |

**Legend:** x = unknown, u = unchanged, - = unimplemented, read as '0'. Shaded cells are not used by the Parallel Slave Port. **Note 1:** Bits PSPIE and PSPIF are reserved on the PIC16F873A/876A; always maintain these bits clear.

## PIC16F87XA

NOTES:

## 7.1 Timer2 Prescaler and Postscaler

The prescaler and postscaler counters are cleared when any of the following occurs:

- a write to the TMR2 register

- a write to the T2CON register

- any device Reset (POR, MCLR Reset, WDT Reset or BOR)

TMR2 is not cleared when T2CON is written.

## 7.2 Output of TMR2

The output of TMR2 (before the postscaler) is fed to the SSP module, which optionally uses it to generate the shift clock.

| TABLE 7-1:       | REGISTERS ASSOCIATED WITH TIMER2 AS A TIMER/COUNTER |

|------------------|-----------------------------------------------------|

| $IADEE I^{-1}$ . |                                                     |

| Address                 | Name   | Bit 7                | Bit 6       | Bit 5   | Bit 4   | Bit 3   | Bit 2  | Bit 1   | Bit 0   | Value<br>POR, |      |      | e on<br>other<br>sets |

|-------------------------|--------|----------------------|-------------|---------|---------|---------|--------|---------|---------|---------------|------|------|-----------------------|

| 0Bh, 8Bh,<br>10Bh, 18Bh | INTCON | GIE                  | PEIE        | TMR0IE  | INTE    | RBIE    | TMR0IF | INTF    | RBIF    | 0000          | 000x | 0000 | 000u                  |

| 0Ch                     | PIR1   | PSPIF <sup>(1)</sup> | ADIF        | RCIF    | TXIF    | SSPIF   | CCP1IF | TMR2IF  | TMR1IF  | 0000          | 0000 | 0000 | 0000                  |

| 8Ch                     | PIE1   | PSPIE <sup>(1)</sup> | ADIE        | RCIE    | TXIE    | SSPIE   | CCP1IE | TMR2IE  | TMR1IE  | 0000          | 0000 | 0000 | 0000                  |

| 11h                     | TMR2   | Timer2 M             | lodule's Re | gister  |         |         |        |         |         | 0000          | 0000 | 0000 | 0000                  |

| 12h                     | T2CON  | —                    | TOUTPS3     | TOUTPS2 | TOUTPS1 | TOUTPS0 | TMR2ON | T2CKPS1 | T2CKPS0 | -000          | 0000 | -000 | 0000                  |

| 92h                     | PR2    | Timer2 P             | eriod Regis | ter     |         |         |        |         |         | 1111          | 1111 | 1111 | 1111                  |

Legend: x = unknown, u = unchanged, - = unimplemented, read as '0'. Shaded cells are not used by the Timer2 module.

Note 1: Bits PSPIE and PSPIF are reserved on 28-pin devices; always maintain these bits clear.

## 8.0 CAPTURE/COMPARE/PWM MODULES

Each Capture/Compare/PWM (CCP) module contains a 16-bit register which can operate as a:

- 16-bit Capture register

- 16-bit Compare register

- PWM Master/Slave Duty Cycle register

Both the CCP1 and CCP2 modules are identical in operation, with the exception being the operation of the special event trigger. Table 8-1 and Table 8-2 show the resources and interactions of the CCP module(s). In the following sections, the operation of a CCP module is described with respect to CCP1. CCP2 operates the same as CCP1 except where noted.

#### CCP1 Module:

Capture/Compare/PWM Register 1 (CCPR1) is comprised of two 8-bit registers: CCPR1L (low byte) and CCPR1H (high byte). The CCP1CON register controls the operation of CCP1. The special event trigger is generated by a compare match and will reset Timer1.

### CCP2 Module:

Capture/Compare/PWM Register 2 (CCPR2) is comprised of two 8-bit registers: CCPR2L (low byte) and CCPR2H (high byte). The CCP2CON register controls the operation of CCP2. The special event trigger is generated by a compare match and will reset Timer1 and start an A/D conversion (if the A/D module is enabled).

Additional information on CCP modules is available in the PIC<sup>®</sup> Mid-Range MCU Family Reference Manual (DS33023) and in application note *AN594, "Using the CCP Module*(s)" (DS00594).

## TABLE 8-1: CCP MODE – TIMER RESOURCES REQUIRED

| CCP Mode | Timer Resource |

|----------|----------------|

| Capture  | Timer1         |

| Compare  | Timer1         |

| PWM      | Timer2         |

TABLE 8-2:INTERACTION OF TWO CCP MODULES

| CCPx Mode | CCPy Mode | Interaction                                                                         |

|-----------|-----------|-------------------------------------------------------------------------------------|

| Capture   | Capture   | Same TMR1 time base                                                                 |

| Capture   | Compare   | The compare should be configured for the special event trigger which clears TMR1    |

| Compare   | Compare   | The compare(s) should be configured for the special event trigger which clears TMR1 |

| PWM       | PWM       | The PWMs will have the same frequency and update rate (TMR2 interrupt)              |

| PWM       | Capture   | None                                                                                |

| PWM       | Compare   | None                                                                                |

## 9.0 MASTER SYNCHRONOUS SERIAL PORT (MSSP) MODULE

## 9.1 Master SSP (MSSP) Module Overview

The Master Synchronous Serial Port (MSSP) module is a serial interface, useful for communicating with other peripheral or microcontroller devices. These peripheral devices may be serial EEPROMs, shift registers, display drivers, A/D converters, etc. The MSSP module can operate in one of two modes:

- Serial Peripheral Interface (SPI)

- Inter-Integrated Circuit (I<sup>2</sup>C)

- Full Master mode

- Slave mode (with general address call)

The I<sup>2</sup>C interface supports the following modes in hardware:

- Master mode

- Multi-Master mode

- Slave mode

## 9.2 Control Registers

The MSSP module has three associated registers. These include a status register (SSPSTAT) and two control registers (SSPCON and SSPCON2). The use of these registers and their individual configuration bits differ significantly, depending on whether the MSSP module is operated in SPI or  $I^2C$  mode.

Additional details are provided under the individual sections.

## 9.3 SPI Mode

The SPI mode allows 8 bits of data to be synchronously transmitted and received simultaneously. All four modes of SPI are supported. To accomplish communication, typically three pins are used:

- Serial Data Out (SDO) RC5/SDO

- Serial Data In (SDI) RC4/SDI/SDA

- Serial Clock (SCK) RC3/SCK/SCL

Additionally, a fourth pin may be used when in a Slave mode of operation:

Slave Select (SS) – RA5/AN4/SS/C2OUT

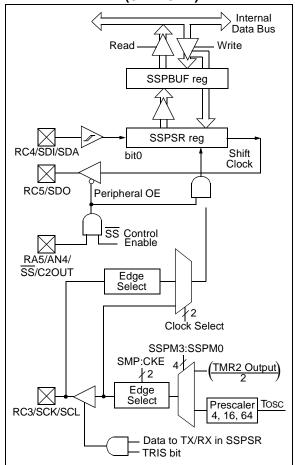

Figure 9-1 shows the block diagram of the MSSP module when operating in SPI mode.

#### FIGURE 9-1:

#### MSSP BLOCK DIAGRAM (SPI MODE)

| Note: | When the SPI is in Slave mode with $\overline{SS}$ pin<br>control enabled (SSPCON<3:0> = 0100),<br>the state of the SS pin can affect the state<br>read back from the TRISC<5> bit. The<br>Peripheral OE signal from the SSP mod-<br>ule in PORTC controls the state that is<br>read back from the TRISC<5> bit (see<br>Section 4.3 "PORTC and the TRISC<br>Register" for information on PORTC). If<br>Read-Modify-Write instructions, such as<br>BSF, are performed on the TRISC register<br>while the SS pin is high, this will cause the<br>TRISC of the table part though displayed by |

|-------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|       | while the SS pin is high, this will cause the TRISC<5> bit to be set, thus disabling the SDO output.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

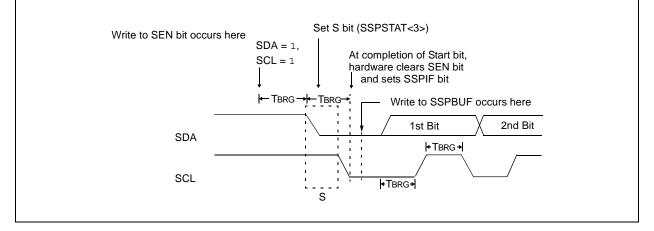

## 9.4.8 I<sup>2</sup>C MASTER MODE START CONDITION TIMING

To initiate a Start condition, the user sets the Start condition enable bit, SEN (SSPCON2<0>). If the SDA and SCL pins are sampled high, the Baud Rate Generator is reloaded with the contents of SSPADD<6:0> and starts its count. If SCL and SDA are both sampled high when the Baud Rate Generator times out (TBRG), the SDA pin is driven low. The action of the SDA being driven low, while SCL is high, is the Start condition and causes the S bit (SSPSTAT<3>) to be set. Following this, the Baud Rate Generator is reloaded with the contents of SSPADD<6:0> and resumes its count. When the Baud Rate Generator times out (TBRG), the SEN bit (SSPCON2<0>) will be automatically cleared by hardware, the Baud Rate Generator is suspended, leaving the SDA line held low and the Start condition is complete.

**Note:** If at the beginning of the Start condition, the SDA and SCL pins are already sampled low, or if during the Start condition, the SCL line is sampled low before the SDA line is driven low, a bus collision occurs, the Bus Collision Interrupt Flag (BCLIF) is set, the Start condition is aborted and the I<sup>2</sup>C module is reset into its Idle state.

## 9.4.8.1 WCOL Status Flag

If the user writes the SSPBUF when a Start sequence is in progress, the WCOL is set and the contents of the buffer are unchanged (the write doesn't occur).

Note: Because queueing of events is not allowed, writing to the lower 5 bits of SSPCON2 is disabled until the Start condition is complete.

## FIGURE 9-19: FIRST START BIT TIMING

#### 9.4.14 SLEEP OPERATION

While in Sleep mode, the  $I^2C$  module can receive addresses or data and when an address match or complete byte transfer occurs, wake the processor from Sleep (if the MSSP interrupt is enabled).

## 9.4.15 EFFECT OF A RESET

A Reset disables the MSSP module and terminates the current transfer.

#### 9.4.16 MULTI-MASTER MODE

In Multi-Master mode, the interrupt generation on the detection of the Start and Stop conditions allows the determination of when the bus is free. The Stop (P) and Start (S) bits are cleared from a Reset or when the MSSP module is disabled. Control of the  $I^2C$  bus may be taken when the P bit (SSPSTAT<4>) is set, or the bus is Idle, with both the S and P bits clear. When the bus is busy, enabling the SSP interrupt will generate the interrupt when the Stop condition occurs.

In multi-master operation, the SDA line must be monitored for arbitration to see if the signal level is at the expected output level. This check is performed in hardware with the result placed in the BCLIF bit.

The states where arbitration can be lost are:

- · Address Transfer

- Data Transfer

- A Start Condition

- A Repeated Start Condition

- An Acknowledge Condition

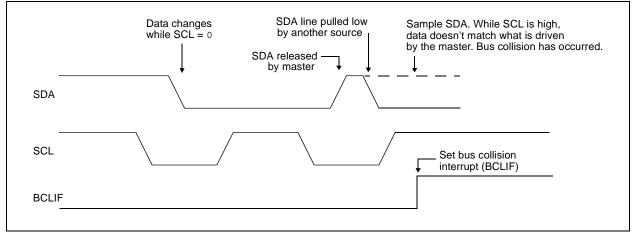

#### 9.4.17 MULTI -MASTER COMMUNICATION, BUS COLLISION AND BUS ARBITRATION

Multi-Master mode support is achieved by bus arbitration. When the master outputs address/data bits onto the SDA pin, arbitration takes place when the master outputs a '1' on SDA by letting SDA float high and another master asserts a '0'. When the SCL pin floats high, data should be stable. If the expected data on SDA is a '1' and the data sampled on the SDA pin = 0, then a bus collision has taken place. The master will set the Bus Collision Interrupt Flag, BCLIF, and reset the  $I^2C$  port to its Idle state (Figure 9-25).

If a transmit was in progress when the bus collision occurred, the transmission is halted, the BF flag is cleared, the SDA and SCL lines are deasserted and the SSPBUF can be written to. When the user services the bus collision Interrupt Service Routine and if the  $I^2C$  bus is free, the user can resume communication by asserting a Start condition.

If a Start, Repeated Start, Stop or Acknowledge condition was in progress when the bus collision occurred, the condition is aborted, the SDA and SCL lines are deasserted and the respective control bits in the SSPCON2 register are cleared. When the user services the bus collision Interrupt Service Routine and if the I<sup>2</sup>C bus is free, the user can resume communication by asserting a Start condition.

The Master will continue to monitor the SDA and SCL pins. If a Stop condition occurs, the SSPIF bit will be set.

A write to the SSPBUF will start the transmission of data at the first data bit regardless of where the transmitter left off when the bus collision occurred.

In Multi-Master mode, the interrupt generation on the detection of Start and Stop conditions allows the determination of when the bus is free. Control of the  $I^2C$  bus can be taken when the P bit is set in the SSPSTAT register or the bus is Idle and the S and P bits are cleared.

#### FIGURE 9-25: BUS COLLISION TIMING FOR TRANSMIT AND ACKNOWLEDGE

© 2001-2013 Microchip Technology Inc.

| BAUD        | F       | osc = 20 M | IHz                         | F       | osc = 16 N | IHz                         | Fosc = 10 MHz |            |                             |

|-------------|---------|------------|-----------------------------|---------|------------|-----------------------------|---------------|------------|-----------------------------|

| RATE<br>(K) | KBAUD   | %<br>ERROR | SPBRG<br>value<br>(decimal) | KBAUD   | %<br>ERROR | SPBRG<br>value<br>(decimal) | KBAUD         | %<br>ERROR | SPBRG<br>value<br>(decimal) |

| 0.3         | -       | -          | -                           | -       | -          | -                           | -             | -          | -                           |

| 1.2         | 1.221   | 1.75       | 255                         | 1.202   | 0.17       | 207                         | 1.202         | 0.17       | 129                         |

| 2.4         | 2.404   | 0.17       | 129                         | 2.404   | 0.17       | 103                         | 2.404         | 0.17       | 64                          |

| 9.6         | 9.766   | 1.73       | 31                          | 9.615   | 0.16       | 25                          | 9.766         | 1.73       | 15                          |

| 19.2        | 19.531  | 1.72       | 15                          | 19.231  | 0.16       | 12                          | 19.531        | 1.72       | 7                           |

| 28.8        | 31.250  | 8.51       | 9                           | 27.778  | 3.55       | 8                           | 31.250        | 8.51       | 4                           |

| 33.6        | 34.722  | 3.34       | 8                           | 35.714  | 6.29       | 6                           | 31.250        | 6.99       | 4                           |

| 57.6        | 62.500  | 8.51       | 4                           | 62.500  | 8.51       | 3                           | 52.083        | 9.58       | 2                           |

| HIGH        | 1.221   | -          | 255                         | 0.977   | -          | 255                         | 0.610         | -          | 255                         |

| LOW         | 312.500 | -          | 0                           | 250.000 | -          | 0                           | 156.250       | -          | 0                           |

## TABLE 10-3: BAUD RATES FOR ASYNCHRONOUS MODE (BRGH = 0)

| BAUD        |        | Fosc = 4 M | Hz                          | Fosc = 3.6864 MHz |            |                             |  |  |

|-------------|--------|------------|-----------------------------|-------------------|------------|-----------------------------|--|--|

| RATE<br>(K) | KBAUD  | %<br>ERROR | SPBRG<br>value<br>(decimal) | KBAUD             | %<br>ERROR | SPBRG<br>value<br>(decimal) |  |  |

| 0.3         | 0.300  | 0          | 207                         | 0.3               | 0          | 191                         |  |  |

| 1.2         | 1.202  | 0.17       | 51                          | 1.2               | 0          | 47                          |  |  |

| 2.4         | 2.404  | 0.17       | 25                          | 2.4               | 0          | 23                          |  |  |

| 9.6         | 8.929  | 6.99       | 6                           | 9.6               | 0          | 5                           |  |  |

| 19.2        | 20.833 | 8.51       | 2                           | 19.2              | 0          | 2                           |  |  |

| 28.8        | 31.250 | 8.51       | 1                           | 28.8              | 0          | 1                           |  |  |

| 33.6        | -      | -          | -                           | -                 | -          | -                           |  |  |

| 57.6        | 62.500 | 8.51       | 0                           | 57.6              | 0          | 0                           |  |  |

| HIGH        | 0.244  | -          | 255                         | 0.225             | -          | 255                         |  |  |

| LOW         | 62.500 | -          | 0                           | 57.6              | -          | 0                           |  |  |

## TABLE 10-4: BAUD RATES FOR ASYNCHRONOUS MODE (BRGH = 1)

| BAUD        | F        | osc = 20 M | Hz                          | F        | osc = 16 M | Hz                          | Fosc = 10 MHz |            |                             |

|-------------|----------|------------|-----------------------------|----------|------------|-----------------------------|---------------|------------|-----------------------------|

| RATE<br>(K) | ATE      | %<br>ERROR | SPBRG<br>value<br>(decimal) | KBAUD    | %<br>ERROR | SPBRG<br>value<br>(decimal) | KBAUD         | %<br>ERROR | SPBRG<br>value<br>(decimal) |

| 0.3         | -        | -          | -                           | -        | -          | -                           | -             | -          | -                           |

| 1.2         | -        | -          | -                           | -        | -          | -                           | -             | -          | -                           |

| 2.4         | -        | -          | -                           | -        | -          | -                           | 2.441         | 1.71       | 255                         |

| 9.6         | 9.615    | 0.16       | 129                         | 9.615    | 0.16       | 103                         | 9.615         | 0.16       | 64                          |

| 19.2        | 19.231   | 0.16       | 64                          | 19.231   | 0.16       | 51                          | 19.531        | 1.72       | 31                          |

| 28.8        | 29.070   | 0.94       | 42                          | 29.412   | 2.13       | 33                          | 28.409        | 1.36       | 21                          |

| 33.6        | 33.784   | 0.55       | 36                          | 33.333   | 0.79       | 29                          | 32.895        | 2.10       | 18                          |

| 57.6        | 59.524   | 3.34       | 20                          | 58.824   | 2.13       | 16                          | 56.818        | 1.36       | 10                          |

| HIGH        | 4.883    | -          | 255                         | 3.906    | -          | 255                         | 2.441         | -          | 255                         |

| LOW         | 1250.000 | -          | 0                           | 1000.000 |            | 0                           | 625.000       | -          | 0                           |

| BAUD        | F       | osc = 4 MH | łz                          | Fos   | c = 3.6864 | MHz                         |

|-------------|---------|------------|-----------------------------|-------|------------|-----------------------------|

| RATE<br>(K) | KBAUD   | %<br>ERROR | SPBRG<br>value<br>(decimal) | KBAUD | %<br>ERROR | SPBRG<br>value<br>(decimal) |

| 0.3         | -       | -          | -                           | -     | -          | -                           |

| 1.2         | 1.202   | 0.17       | 207                         | 1.2   | 0          | 191                         |

| 2.4         | 2.404   | 0.17       | 103                         | 2.4   | 0          | 95                          |

| 9.6         | 9.615   | 0.16       | 25                          | 9.6   | 0          | 23                          |

| 19.2        | 19.231  | 0.16       | 12                          | 19.2  | 0          | 11                          |

| 28.8        | 27.798  | 3.55       | 8                           | 28.8  | 0          | 7                           |

| 33.6        | 35.714  | 6.29       | 6                           | 32.9  | 2.04       | 6                           |

| 57.6        | 62.500  | 8.51       | 3                           | 57.6  | 0          | 3                           |

| HIGH        | 0.977   | -          | 255                         | 0.9   | -          | 255                         |

| LOW         | 250.000 | -          | 0                           | 230.4 | -          | 0                           |

## 10.2 USART Asynchronous Mode

In this mode, the USART uses standard Non-Returnto-Zero (NRZ) format (one Start bit, eight or nine data bits and one Stop bit). The most common data format is 8 bits. An on-chip, dedicated, 8-bit Baud Rate Generator can be used to derive standard baud rate frequencies from the oscillator. The USART transmits and receives the LSb first. The transmitter and receiver are functionally independent but use the same data format and baud rate. The baud rate generator produces a clock, either x16 or x64 of the bit shift rate, depending on bit BRGH (TXSTA<2>). Parity is not supported by the hardware but can be implemented in software (and stored as the ninth data bit). Asynchronous mode is stopped during Sleep.

Asynchronous mode is selected by clearing bit SYNC (TXSTA<4>).

The USART Asynchronous module consists of the following important elements:

- Baud Rate Generator

- Sampling Circuit

- Asynchronous Transmitter

- Asynchronous Receiver

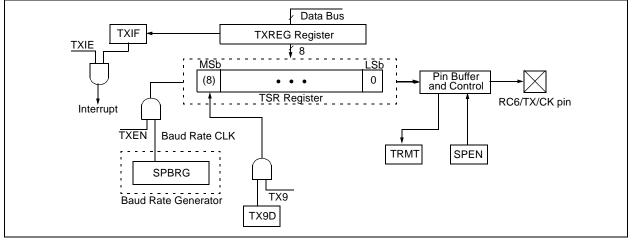

## 10.2.1 USART ASYNCHRONOUS TRANSMITTER

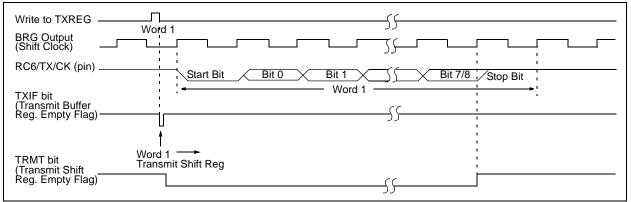

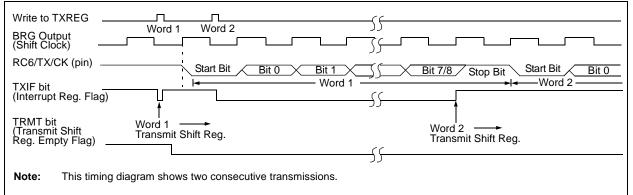

The USART transmitter block diagram is shown in Figure 10-1. The heart of the transmitter is the Transmit (Serial) Shift Register (TSR). The shift register obtains its data from the Read/Write Transmit Buffer, TXREG. The TXREG register is loaded with data in software. The TSR register is not loaded until the Stop bit has been transmitted from the previous load. As soon as the Stop bit is transmitted, the TSR is loaded with new data from the TXREG register (if available). Once the TXREG register transfers the data to the TSR register (occurs in one TcY), the TXREG register is empty and flag bit, TXIF (PIR1<4>), is set. This interrupt can be

enabled/disabled by setting/clearing enable bit, TXIE (PIE1<4>). Flag bit TXIF will be set regardless of the state of enable bit TXIE and cannot be cleared in software. It will reset only when new data is loaded into the TXREG register. While flag bit TXIF indicates the status of the TXREG register, another bit, TRMT (TXSTA<1>), shows the status of the TSR register. Status bit TRMT is a read-only bit which is set when the TSR register is empty. No interrupt logic is tied to this bit so the user has to poll this bit in order to determine if the TSR register is empty.

- **Note 1:** The TSR register is not mapped in data memory so it is not available to the user.

- 2: Flag bit TXIF is set when enable bit TXEN is set. TXIF is cleared by loading TXREG.

Transmission is enabled by setting enable bit, TXEN (TXSTA<5>). The actual transmission will not occur until the TXREG register has been loaded with data and the Baud Rate Generator (BRG) has produced a shift clock (Figure 10-2). The transmission can also be started by first loading the TXREG register and then setting enable bit TXEN. Normally, when transmission is first started, the TSR register is empty. At that point, transfer to the TXREG register will result in an immediate transfer to TSR, resulting in an empty TXREG. A back-to-back transfer is thus possible (Figure 10-3). Clearing enable bit TXEN during a transmission will cause the transmission to be aborted and will reset the transmitter. As a result, the RC6/TX/CK pin will revert to high-impedance.

In order to select 9-bit transmission, transmit bit TX9 (TXSTA<6>) should be set and the ninth bit should be written to TX9D (TXSTA<0>). The ninth bit must be written before writing the 8-bit data to the TXREG register. This is because a data write to the TXREG register can result in an immediate transfer of the data to the TSR register (if the TSR is empty). In such a case, an incorrect ninth data bit may be loaded in the TSR register.

When setting up an Asynchronous Transmission, follow these steps:

- Initialize the SPBRG register for the appropriate baud rate. If a high-speed baud rate is desired, set bit BRGH (Section 10.1 "USART Baud Rate Generator (BRG)").

- 2. Enable the asynchronous serial port by clearing bit SYNC and setting bit SPEN.

- 3. If interrupts are desired, then set enable bit TXIE.

- 4. If 9-bit transmission is desired, then set transmit bit TX9.

- 5. Enable the transmission by setting bit TXEN, which will also set bit TXIF.

- 6. If 9-bit transmission is selected, the ninth bit should be loaded in bit TX9D.

- 7. Load data to the TXREG register (starts transmission).

- 8. If using interrupts, ensure that GIE and PEIE (bits 7 and 6) of the INTCON register are set.

## FIGURE 10-2: ASYNCHRONOUS MASTER TRANSMISSION

#### FIGURE 10-3: ASYNCHRONOUS MASTER TRANSMISSION (BACK TO BACK)

#### TABLE 10-5: REGISTERS ASSOCIATED WITH ASYNCHRONOUS TRANSMISSION

| Name                               | Bit 7                                             | Bit 6                                                                                                               | Bit 5                                                                                                                                              | Bit 4                                                                                                                                   | Bit 3                                                                                                                                       | Bit 2                                                                                                                                                          | Bit 1                                                                                                                                                                                  | Bit 0                                                                                                                                                                                                                                   | Value on:<br>POR, BOR                                                                                                                                                                                                                                          | Value on<br>all other<br>Resets                                                                                                                                                                                                                                                                                                                                                            |

|------------------------------------|---------------------------------------------------|---------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| INTCON                             | GIE                                               | PEIE                                                                                                                | TMR0IE                                                                                                                                             | INTE                                                                                                                                    | RBIE                                                                                                                                        | TMR0IF                                                                                                                                                         | INTF                                                                                                                                                                                   | R0IF                                                                                                                                                                                                                                    | 0000 000x                                                                                                                                                                                                                                                      | 0000 000u                                                                                                                                                                                                                                                                                                                                                                                  |

| PIR1                               | PSPIF <sup>(1)</sup>                              | ADIF                                                                                                                | RCIF                                                                                                                                               | TXIF                                                                                                                                    | SSPIF                                                                                                                                       | CCP1IF                                                                                                                                                         | TMR2IF                                                                                                                                                                                 | TMR1IF                                                                                                                                                                                                                                  | 0000 0000                                                                                                                                                                                                                                                      | 0000 0000                                                                                                                                                                                                                                                                                                                                                                                  |

| RCSTA                              | SPEN                                              | RX9                                                                                                                 | SREN                                                                                                                                               | CREN                                                                                                                                    | _                                                                                                                                           | FERR                                                                                                                                                           | OERR                                                                                                                                                                                   | RX9D                                                                                                                                                                                                                                    | 0000 -00x                                                                                                                                                                                                                                                      | 0000 -00x                                                                                                                                                                                                                                                                                                                                                                                  |

| TXREG                              | USART Tra                                         | nsmit Re                                                                                                            | gister                                                                                                                                             |                                                                                                                                         |                                                                                                                                             |                                                                                                                                                                |                                                                                                                                                                                        |                                                                                                                                                                                                                                         | 0000 0000                                                                                                                                                                                                                                                      | 0000 0000                                                                                                                                                                                                                                                                                                                                                                                  |

| PIE1                               | PSPIE <sup>(1)</sup>                              | ADIE                                                                                                                | RCIE                                                                                                                                               | TXIE                                                                                                                                    | SSPIE                                                                                                                                       | CCP1IE                                                                                                                                                         | TMR2IE                                                                                                                                                                                 | TMR1IE                                                                                                                                                                                                                                  | 0000 0000                                                                                                                                                                                                                                                      | 0000 0000                                                                                                                                                                                                                                                                                                                                                                                  |

| TXSTA                              | CSRC                                              | TX9                                                                                                                 | TXEN                                                                                                                                               | SYNC                                                                                                                                    |                                                                                                                                             | BRGH                                                                                                                                                           | TRMT                                                                                                                                                                                   | TX9D                                                                                                                                                                                                                                    | 0000 -010                                                                                                                                                                                                                                                      | 0000 -010                                                                                                                                                                                                                                                                                                                                                                                  |

| SPBRG Baud Rate Generator Register |                                                   |                                                                                                                     |                                                                                                                                                    |                                                                                                                                         |                                                                                                                                             |                                                                                                                                                                |                                                                                                                                                                                        |                                                                                                                                                                                                                                         | 0000 0000                                                                                                                                                                                                                                                      | 0000 0000                                                                                                                                                                                                                                                                                                                                                                                  |

|                                    | INTCON<br>PIR1<br>RCSTA<br>TXREG<br>PIE1<br>TXSTA | INTCON GIE<br>PIR1 PSPIF <sup>(1)</sup><br>RCSTA SPEN<br>TXREG USART Tra<br>PIE1 PSPIE <sup>(1)</sup><br>TXSTA CSRC | INTCON GIE PEIE<br>PIR1 PSPIF <sup>(1)</sup> ADIF<br>RCSTA SPEN RX9<br>TXREG USART Transmit Re<br>PIE1 PSPIE <sup>(1)</sup> ADIE<br>TXSTA CSRC TX9 | INTCONGIEPEIETMR0IEPIR1PSPIF(1)ADIFRCIFRCSTASPENRX9SRENTXREGUSART Transmit RegisterPIE1PSPIE(1)ADIEPIE1PSPIE(1)ADIERCIETXSTACSRCTX9TXEN | INTCONGIEPEIETMR0IEINTEPIR1PSPIF(1)ADIFRCIFTXIFRCSTASPENRX9SRENCRENTXREGUSART Transmit RegisterFIE1PSPIE(1)ADIERCIETXIETXSTACSRCTX9TXENSYNC | INTCONGIEPEIETMR0IEINTERBIEPIR1PSPIF(1)ADIFRCIFTXIFSSPIFRCSTASPENRX9SRENCREN—TXREGUSART Transmit Register———PIE1PSPIE(1)ADIERCIETXIESSPIETXSTACSRCTX9TXENSYNC— | INTCONGIEPEIETMROIEINTERBIETMROIFPIR1PSPIF(1)ADIFRCIFTXIFSSPIFCCP1IFRCSTASPENRX9SRENCREN—FERRTXREGUSART Traverist RegisterFIE1PSPIE(1)ADIERCIETXIESSPIECCP1IETXSTACSRCTX9TXENSYNC—BRGH | INTCONGIEPEIETMR0IEINTERBIETMR0IFINTFPIR1PSPIF <sup>(1)</sup> ADIFRCIFTXIFSSPIFCCP1IFTMR2IFRCSTASPENRX9SRENCREN—FERROERRTXREGUSART Transmit RegisterPIE1PSPIE <sup>(1)</sup> ADIERCIETXIESSPIECCP1IETMR2IETXSTACSRCTX9TXENSYNC—BRGHTRMT | INTCONGIEPEIETMROIEINTERBIETMROIFINTFROIFPIR1PSPIF <sup>(1)</sup> ADIFRCIFTXIFSSPIFCCP1IFTMR2IFTMR1IFRCSTASPENRX9SRENCREN—FERROERRRX9DTXREGUSART Trasmit ResisterPIE1PSPIE <sup>(1)</sup> ADIERCIETXIESSPIECCP1IETMR2IETMR1IETXSTACSRCTX9TXENSYNC—BRGHTRMTTX9D | NameBit 7Bit 6Bit 5Bit 4Bit 3Bit 2Bit 1Bit 0POR, BORINTCONGIEPEIETMROIEINTERBIETMROIFINTFROIF00000000PIR1PSPIF <sup>(1)</sup> ADIFRCIFTXIFSSPIFCCP1IFTMR2IFTMR1IF00000000RCSTASPENRX9SRENCREN—FERROERRRX9D0000-0000TXREGUSART Travent Register5SPIECCP1IETMR2IETMR1IE00000000PIE1PSPIE <sup>(1)</sup> ADIERCIETXIESSPIECCP1IETMR2IETMR1IE00000000TXSTACSRCTX9TXENSYNC—BRGHTRMTTX9D0000-010 |

Legend: x = unknown, - = unimplemented locations read as '0'. Shaded cells are not used for asynchronous transmission.

Note 1: Bits PSPIE and PSPIF are reserved on 28-pin devices; always maintain these bits clear.

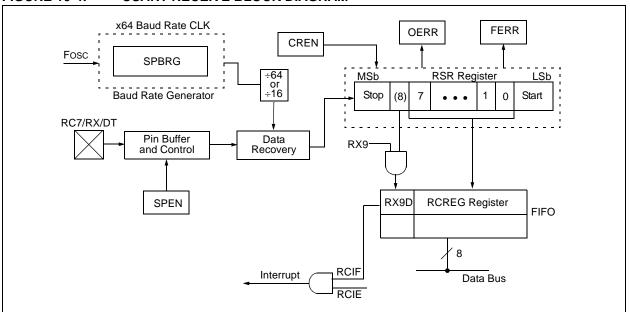

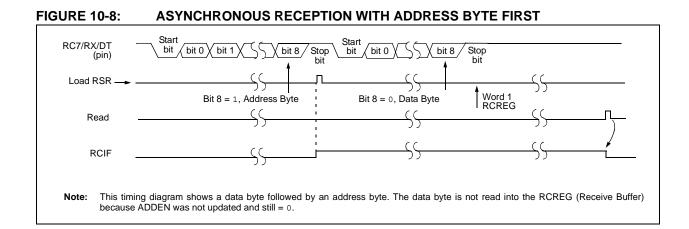

### 10.2.2 USART ASYNCHRONOUS RECEIVER

The receiver block diagram is shown in Figure 10-4. The data is received on the RC7/RX/DT pin and drives the data recovery block. The data recovery block is actually a high-speed shifter, operating at x16 times the baud rate; whereas the main receive serial shifter operates at the bit rate or at Fosc.

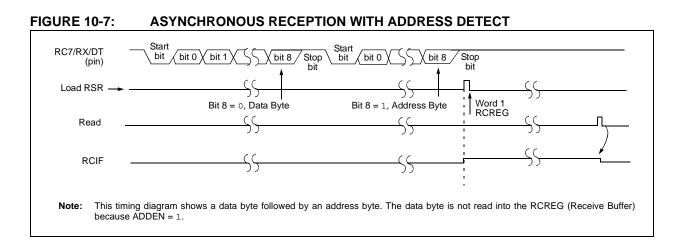

Once Asynchronous mode is selected, reception is enabled by setting bit CREN (RCSTA<4>).

The heart of the receiver is the Receive (Serial) Shift Register (RSR). After sampling the Stop bit, the received data in the RSR is transferred to the RCREG register (if it is empty). If the transfer is complete, flag bit, RCIF (PIR1<5>), is set. The actual interrupt can be enabled/disabled by setting/clearing enable bit, RCIE (PIE1<5>). Flag bit RCIF is a read-only bit which is cleared by the hardware. It is cleared when the RCREG register has been read and is empty. The RCREG is a double-buffered register (i.e., it is a two-deep FIFO). It is possible for two bytes of data to be received and transferred to the RCREG FIFO and a third byte to begin shifting to the RSR register. On the detection of the Stop bit of the third byte, if the RCREG register is still full, the Overrun Error bit, OERR (RCSTA<1>), will be set. The word in the RSR will be lost. The RCREG register can be read twice to retrieve the two bytes in the FIFO. Overrun bit OERR has to be cleared in software. This is done by resetting the receive logic (CREN is cleared and then set). If bit OERR is set, transfers from the RSR register to the RCREG register are inhibited and no further data will be received. It is, therefore, essential to clear error bit OERR if it is set. Framing error bit, FERR (RCSTA<2>), is set if a Stop bit is detected as clear. Bit FERR and the 9th receive bit are buffered the same way as the receive data. Reading the RCREG will load bits RX9D and FERR with new values, therefore, it is essential for the user to read the RCSTA register before reading the RCREG register in order not to lose the old FERR and RX9D information.

FIGURE 10-4: USART RECEIVE BLOCK DIAGRAM

# PIC16F87XA

| Address                | Name   | Bit 7                           | Bit 6     | Bit 5  | Bit 4 | Bit 3 | Bit 2  | Bit 1  | Bit 0     | Value on:<br>POR, BOR | Value on<br>all other<br>Resets |

|------------------------|--------|---------------------------------|-----------|--------|-------|-------|--------|--------|-----------|-----------------------|---------------------------------|

| 0Bh, 8Bh,<br>10Bh,18Bh | INTCON | GIE                             | PEIE      | TMR0IE | INTE  | RBIE  | TMR0IF | INTF   | R0IF      | 0000 000x             | 0000 000u                       |

| 0Ch                    | PIR1   | PSPIF <sup>(1)</sup>            | ADIF      | RCIF   | TXIF  | SSPIF | CCP1IF | TMR2IF | TMR1IF    | 0000 0000             | 0000 0000                       |

| 18h                    | RCSTA  | SPEN                            | RX9       | SREN   | CREN  | ADDEN | FERR   | OERR   | RX9D      | 0000 000x             | 0000 000x                       |

| 1Ah                    | RCREG  | USART Red                       | ceive Reg | gister |       |       |        |        |           | 0000 0000             | 0000 0000                       |

| 8Ch                    | PIE1   | PSPIE <sup>(1)</sup>            | ADIE      | RCIE   | TXIE  | SSPIE | CCP1IE | TMR2IE | TMR1IE    | 0000 0000             | 0000 0000                       |

| 98h                    | TXSTA  | CSRC                            | TX9       | TXEN   | SYNC  | —     | BRGH   | TRMT   | TX9D      | 0000 -010             | 0000 -010                       |

| 99h                    | SPBRG  | RG Baud Rate Generator Register |           |        |       |       |        |        | 0000 0000 | 0000 0000             |                                 |

Legend: x = unknown, - = unimplemented locations read as '0'. Shaded cells are not used for asynchronous reception.

Note 1: Bits PSPIE and PSPIF are reserved on 28-pin devices; always maintain these bits clear.

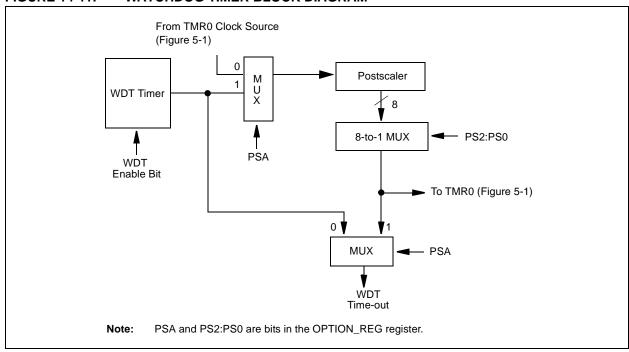

## 14.13 Watchdog Timer (WDT)

The Watchdog Timer is a free running, on-chip RC oscillator which does not require any external components. This RC oscillator is separate from the RC oscillator of the OSC1/CLKI pin. That means that the WDT will run even if the clock on the OSC1/CLKI and OSC2/CLKO pins of the device has been stopped, for example, by execution of a SLEEP instruction.

During normal operation, a WDT time-out generates a device Reset (Watchdog Timer Reset). If the device is in Sleep mode, a WDT time-out causes the device to wake-up and continue with normal operation (Watchdog Timer Wake-up). The TO bit in the Status register will be cleared upon a Watchdog Timer time-out.

The WDT can be permanently disabled by clearing configuration bit, WDTE (Section 14.1 "Configuration Bits").

WDT time-out period values may be found in **Section 17.0** "**Electrical Characteristics**" under parameter #31. Values for the WDT prescaler (actually a postscaler but shared with the Timer0 prescaler) may be assigned using the OPTION\_REG register.

- **Note 1:** The CLRWDT and SLEEP instructions clear the WDT and the postscaler, if assigned to the WDT and prevent it from timing out and generating a device Reset condition.

- 2: When a CLRWDT instruction is executed and the prescaler is assigned to the WDT, the prescaler count will be cleared but the prescaler assignment is not changed.

## FIGURE 14-11: WATCHDOG TIMER BLOCK DIAGRAM

#### TABLE 14-7: SUMMARY OF WATCHDOG TIMER REGISTERS

| Address   | Name         | Bit 7 | Bit 6                | Bit 5 | Bit 4 | Bit 3                | Bit 2 | Bit 1 | Bit 0 |

|-----------|--------------|-------|----------------------|-------|-------|----------------------|-------|-------|-------|

| 2007h     | Config. bits | (1)   | BODEN <sup>(1)</sup> | CP1   | CP0   | PWRTE <sup>(1)</sup> | WDTE  | Fosc1 | Fosc0 |

| 81h, 181h | OPTION_REG   | RBPU  | INTEDG               | TOCS  | TOSE  | PSA                  | PS2   | PS1   | PS0   |

Legend: Shaded cells are not used by the Watchdog Timer.

Note 1: See Register 14-1 for operation of these bits.

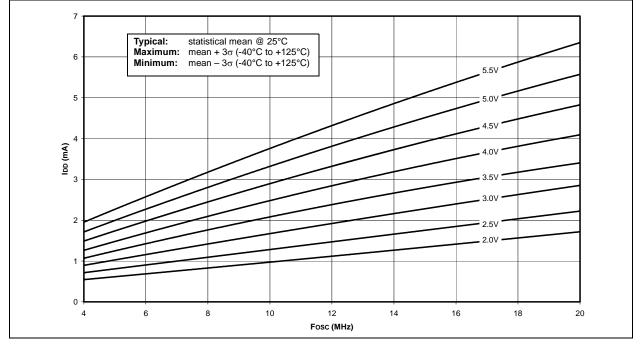

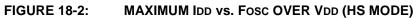

## 17.1 DC Characteristics: PIC16F873A/874A/876A/877A (Industrial, Extended) PIC16LF873A/874A/876A/877A (Industrial) (Continued)

|                                                     | PIC16LF873A/874A/876A/877A<br>(Industrial) |                                           |     |                                                                                                                                                                                         | Standard Operating Conditions (unless otherwise stated)Operating temperature $-40^{\circ}C \le TA \le +85^{\circ}C$ for industrial |          |                                                                                                        |  |  |  |  |  |

|-----------------------------------------------------|--------------------------------------------|-------------------------------------------|-----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------|----------|--------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| PIC16F873A/874A/876A/877A<br>(Industrial, Extended) |                                            |                                           |     | Standard Operating Conditions (unless otherwise stated)Operating temperature $-40^{\circ}C \le TA \le +85^{\circ}C$ for industrial $-40^{\circ}C \le TA \le +125^{\circ}C$ for extended |                                                                                                                                    |          |                                                                                                        |  |  |  |  |  |

| Param<br>No. Symbol Characteristic/<br>Device       |                                            |                                           | Min | Тур†                                                                                                                                                                                    | Max                                                                                                                                | Units    | Conditions                                                                                             |  |  |  |  |  |

|                                                     | IPD                                        | Power-down Current <sup>(3,5)</sup>       |     |                                                                                                                                                                                         |                                                                                                                                    |          |                                                                                                        |  |  |  |  |  |

| D020                                                |                                            | 16LF87XA                                  |     | 7.5                                                                                                                                                                                     | 30                                                                                                                                 | μΑ       | VDD = 3.0V, WDT enabled,<br>-40°C to +85°C                                                             |  |  |  |  |  |

| D020                                                |                                            | 16F87XA                                   | _   | 10.5                                                                                                                                                                                    | 42<br>60                                                                                                                           | μΑ<br>μΑ | VDD = 4.0V, WDT enabled,<br>-40°C to +85°C<br>VDD = 4.0V, WDT enabled,<br>-40°C to +125°C (extended)   |  |  |  |  |  |

| D021                                                |                                            | 16LF87XA                                  |     | 0.9                                                                                                                                                                                     | 5                                                                                                                                  | μΑ       | VDD = 3.0V, WDT disabled,<br>0°C to +70°C                                                              |  |  |  |  |  |

| D021                                                |                                            | 16F87XA                                   | _   | 1.5                                                                                                                                                                                     | 16<br>20                                                                                                                           | μΑ<br>μΑ | VDD = 4.0V, WDT disabled,<br>-40°C to +85°C<br>VDD = 4.0V, WDT disabled,<br>-40°C to +125°C (extended) |  |  |  |  |  |

| D021A                                               |                                            | 16LF87XA                                  |     | 0.9                                                                                                                                                                                     | 5                                                                                                                                  | μA       | VDD = 3.0V, WDT disabled,<br>-40°C to +85°C                                                            |  |  |  |  |  |

| D021A                                               |                                            | 16F87XA                                   |     | 1.5                                                                                                                                                                                     | 19                                                                                                                                 | μA       | VDD = 4.0V, WDT disabled,<br>-40°C to +85°C                                                            |  |  |  |  |  |

| D023                                                | $\Delta$ IBOR                              | Brown-out<br>Reset Current <sup>(6)</sup> |     | 85                                                                                                                                                                                      | 200                                                                                                                                | μΑ       | BOR enabled, VDD = 5.0V                                                                                |  |  |  |  |  |

Legend: Rows with standard voltage device data only are shaded for improved readability.

- † Data in "Typ" column is at 5V, 25°C, unless otherwise stated. These parameters are for design guidance only and are not tested.

- Note 1: This is the limit to which VDD can be lowered without losing RAM data.

- **2:** The supply current is mainly a function of the operating voltage and frequency. Other factors, such as I/O pin loading, switching rate, oscillator type, internal code execution pattern and temperature, also have an impact on the current consumption.

- The test conditions for all IDD measurements in active operation mode are:

- OSC1 = external square wave, from rail-to-rail; all I/O pins tri-stated, pulled to VDD; MCLR = VDD; WDT enabled/disabled as specified.

- **3:** The power-down current in Sleep mode does not depend on the oscillator type. Power-down current is measured with the part in Sleep mode, with all I/O pins in high-impedance state and tied to VDD and Vss.

- **4:** For RC osc configuration, current through REXT is not included. The current through the resistor can be estimated by the formula Ir = VDD/2REXT (mA) with REXT in kΩ.

- **5:** Timer1 oscillator (when enabled) adds approximately 20 μA to the specification. This value is from characterization and is for design guidance only. This is not tested.

- 6: The ∆ current is the additional current consumed when this peripheral is enabled. This current should be added to the base IDD or IPD measurement.

- 7: When BOR is enabled, the device will operate correctly until the VBOR voltage trip point is reached.

## 17.3 Timing Parameter Symbology

The timing parameter symbols have been created following one of the following formats:

| 1. TppS2pp            | bS                                  | 3. Tcc:st | (I <sup>2</sup> C specifications only) |

|-----------------------|-------------------------------------|-----------|----------------------------------------|

| 2. TppS               |                                     | 4. Ts     | (I <sup>2</sup> C specifications only) |

| Т                     |                                     |           |                                        |

| F                     | Frequency                           | Т         | Time                                   |

| Lowerca               | se letters (pp) and their meanings: |           |                                        |

| рр                    |                                     |           |                                        |

| CC                    | CCP1                                | OSC       | OSC1                                   |

| ck                    | CLKO                                | rd        | RD                                     |

| CS                    | CS                                  | rw        | RD or WR                               |

| di                    | SDI                                 | SC        | SCK                                    |

| do                    | SDO                                 | SS        | SS                                     |

| dt                    | Data in                             | tO        | TOCKI                                  |

| io                    | I/O port                            | t1        | T1CKI                                  |

| mc                    | MCLR                                | wr        | WR                                     |

|                       | se letters and their meanings:      |           |                                        |

| S                     |                                     |           |                                        |

| F                     | Fall                                | Р         | Period                                 |

| Н                     | High                                | R         | Rise                                   |

| I                     | Invalid (High-impedance)            | V         | Valid                                  |

| L                     | Low                                 | Z         | High-impedance                         |

| I <sup>2</sup> C only |                                     |           |                                        |

| AA                    | output access                       | High      | High                                   |

| BUF                   | Bus free                            | Low       | Low                                    |