#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                            |

|----------------------------|----------------------------------------------------------------------------|

| Product Status             | Active                                                                     |

| Core Processor             | PIC                                                                        |

| Core Size                  | 8-Bit                                                                      |

| Speed                      | 10MHz                                                                      |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                          |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                      |

| Number of I/O              | 22                                                                         |

| Program Memory Size        | 14KB (8K x 14)                                                             |

| Program Memory Type        | FLASH                                                                      |

| EEPROM Size                | 256 x 8                                                                    |

| RAM Size                   | 368 x 8                                                                    |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 5.5V                                                                  |

| Data Converters            | A/D 5x10b                                                                  |

| Oscillator Type            | External                                                                   |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                          |

| Mounting Type              | Through Hole                                                               |

| Package / Case             | 28-DIP (0.300", 7.62mm)                                                    |

| Supplier Device Package    | 28-SPDIP                                                                   |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16lf876a-i-sp |

|                            |                                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

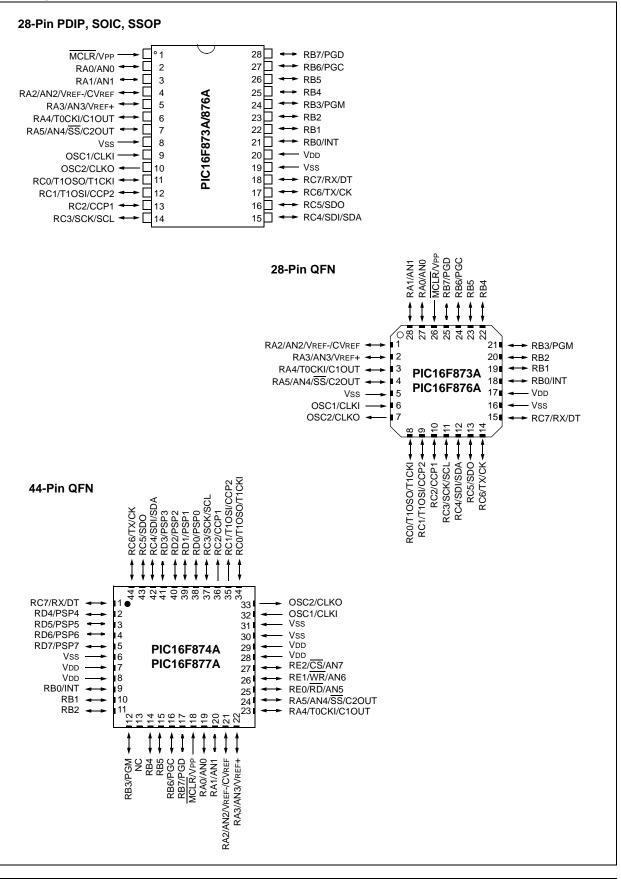

#### **Pin Diagrams**

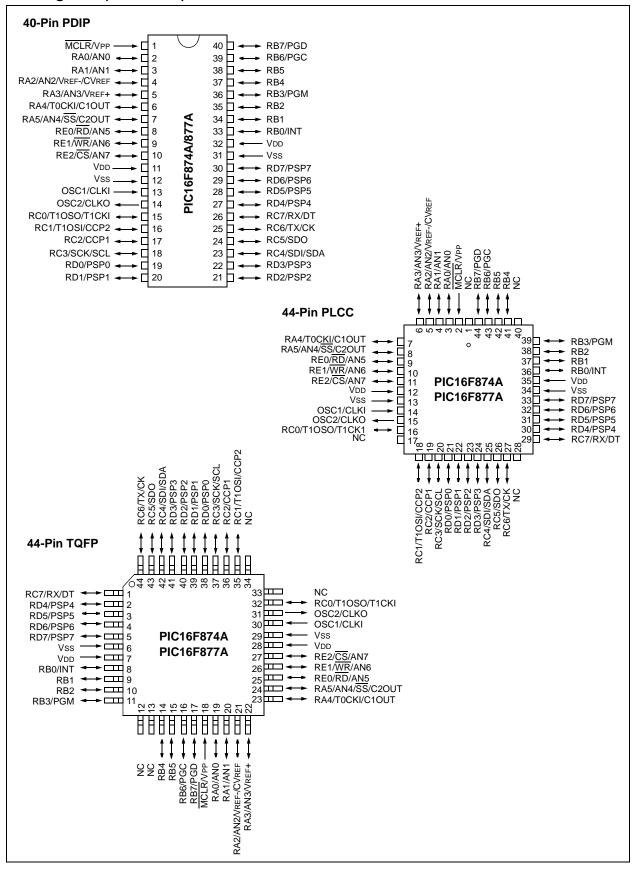

#### **Pin Diagrams (Continued)**

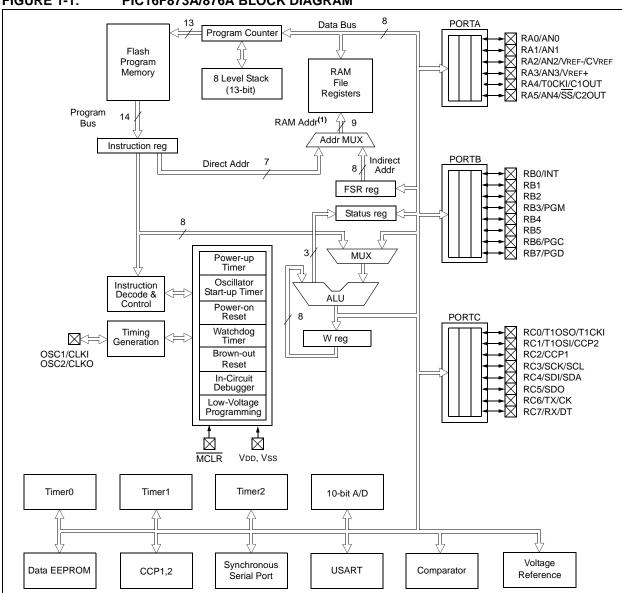

| Device     | e Program Flash Data Memory |           | Data EEPROM |

|------------|-----------------------------|-----------|-------------|

| PIC16F873A | 4K words                    | 192 Bytes | 128 Bytes   |

| PIC16F876A | 8K words                    | 368 Bytes | 256 Bytes   |

Note 1: Higher order bits are from the Status register.

| Pin Name                                                | PDIP, SOIC,<br>SSOP Pin# | QFN<br>Pin# | I/O/P<br>Type      | Buffer<br>Type         | Description                                                                                                                                                                                                                 |

|---------------------------------------------------------|--------------------------|-------------|--------------------|------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| OSC1/CLKI<br>OSC1<br>CLKI                               | 9                        | 6           |                    | ST/CMOS <sup>(3)</sup> | Oscillator crystal or external clock input.<br>Oscillator crystal input or external clock source input. ST<br>buffer when configured in RC mode; otherwise CMOS.<br>External clock source input. Always associated with pin |

| 0EI II                                                  |                          |             |                    |                        | function OSC1 (see OSC1/CLKI, OSC2/CLKO pins).                                                                                                                                                                              |

| OSC2/CLKO<br>OSC2                                       | 10                       | 7           | Ο                  | _                      | Oscillator crystal or clock output.<br>Oscillator crystal output. Connects to crystal or resonator<br>in Crystal Oscillator mode.                                                                                           |

| CLKO                                                    |                          |             | 0                  |                        | In RC mode, OSC2 pin outputs CLKO, which has 1/4 the<br>frequency of OSC1 and denotes the instruction cycle rate                                                                                                            |

| MCLR/VPP<br>MCLR                                        | 1                        | 26          | I                  | ST                     | Master Clear (input) or programming voltage (output).<br>Master Clear (Reset) input. This pin is an active low Reset<br>to the device.                                                                                      |

| VPP                                                     |                          |             | Р                  |                        | Programming voltage input.                                                                                                                                                                                                  |

|                                                         |                          |             |                    |                        | PORTA is a bidirectional I/O port.                                                                                                                                                                                          |

| RA0/AN0<br>RA0<br>AN0                                   | 2                        | 27          | I/O<br>I           | TTL                    | Digital I/O.<br>Analog input 0.                                                                                                                                                                                             |

| RA1/AN1<br>RA1<br>AN1                                   | 3                        | 28          | I/O<br>I           | TTL                    | Digital I/O.<br>Analog input 1.                                                                                                                                                                                             |

| RA2/AN2/VREF-/<br>CVREF<br>RA2<br>AN2<br>VREF-<br>CVREF | 4                        | 1           | I/O<br>I<br>I<br>O | TTL                    | Digital I/O.<br>Analog input 2.<br>A/D reference voltage (Low) input.<br>Comparator VREF output.                                                                                                                            |

| RA3/AN3/VREF+<br>RA3<br>AN3<br>VREF+                    | 5                        | 2           | I/O<br>I<br>I      | TTL                    | Digital I/O.<br>Analog input 3.<br>A/D reference voltage (High) input.                                                                                                                                                      |

| RA4/T0CKI/C1OUT<br>RA4<br>T0CKI<br>C1OUT                | 6                        | 3           | I/O<br>I<br>O      | ST                     | Digital I/O – Open-drain when configured as output.<br>Timer0 external clock input.<br>Comparator 1 output.                                                                                                                 |

| RA5/AN4/SS/C2OUT<br>RA5<br>AN4<br>SS<br>C2OUT           | 7<br>O = ou              | 4           | I/O<br>I<br>I<br>O | TTL                    | Digital I/O.<br>Analog input 4.<br>SPI slave select input.<br>Comparator 2 output.                                                                                                                                          |

#### TABLE 1-2:PIC16F873A/876A PINOUT DESCRIPTION

— = Not used TTL = TTL input ST = Schmitt Trigger input

**Note 1:** This buffer is a Schmitt Trigger input when configured as the external interrupt.

2: This buffer is a Schmitt Trigger input when used in Serial Programming mode.

3: This buffer is a Schmitt Trigger input when configured in RC Oscillator mode and a CMOS input otherwise.

NOTES:

#### 2.2.2.3 INTCON Register

The INTCON register is a readable and writable register, which contains various enable and flag bits for the TMR0 register overflow, RB port change and external RB0/INT pin interrupts. Note: Interrupt flag bits are set when an interrupt condition occurs regardless of the state of its corresponding enable bit or the global enable bit, GIE (INTCON<7>). User software should ensure the appropriate interrupt flag bits are clear prior to enabling an interrupt.

#### REGISTER 2-3: INTCON REGISTER (ADDRESS 0Bh, 8Bh, 10Bh, 18Bh)

| R/W-0      | R/W-0                         | R/W-0                                    | R/W-0        | R/W-0        | R/W-0         | R/W-0        | R/W-x |

|------------|-------------------------------|------------------------------------------|--------------|--------------|---------------|--------------|-------|

| GIE        | PEIE                          | TMR0IE                                   | INTE         | RBIE         | TMR0IF        | INTF         | RBIF  |

| bit 7      |                               |                                          |              |              |               |              | bit 0 |

|            | al Interrupt E                |                                          |              |              |               |              |       |

|            | s all unmas<br>es all interru | ked interrupt<br>pts                     | ts           |              |               |              |       |

| PEIE: Peri | oheral Interr                 | upt Enable b                             | oit          |              |               |              |       |

|            |                               | ked peripher<br>eral interrup            | •            |              |               |              |       |

| TMR0IE: T  | MR0 Overfl                    | ow Interrupt                             | Enable bit   |              |               |              |       |

|            | s the TMR0                    |                                          |              |              |               |              |       |

|            | es the TMR                    | •                                        |              |              |               |              |       |

|            |                               | al Interrupt E                           |              |              |               |              |       |

|            |                               | NT external                              | •            |              |               |              |       |

|            |                               | NT external                              |              |              |               |              |       |

|            | •                             | e Interrupt Ei<br>rt change in           |              |              |               |              |       |

|            | •                             | ort change in                            | •            |              |               |              |       |

|            | •                             | ow Interrupt                             | •            |              |               |              |       |

| 1 = TMR0   | register has                  | overflowed                               | (must be cle | ared in soft | ware)         |              |       |

|            |                               | al Interrupt F                           |              |              |               |              |       |

| 1 = The RE | B0/INT exter                  | nal interrupt                            | occurred (n  |              | red in softwa | are)         |       |

| RBIF: RB I | Port Change                   | Interrupt Fl                             | ag bit       |              |               |              |       |

| the bit    | . Reading F                   | RB7:RB4 p<br>ORTB will e<br>n software). |              |              |               |              |       |

| 0 = None   | of the RB7:F                  | RB4 pins hav                             | ve changed   | state        |               |              |       |

| Legend:    |                               |                                          |              |              |               |              |       |

| R = Reada  | ble bit                       | W = W                                    | /ritable bit | U = Unin     | nplemented    | bit. read as | '0'   |

| R = Readable bit W = Writable bit |                  | U = Unimplemented bit, read as '0'     |  |  |  |  |

|-----------------------------------|------------------|----------------------------------------|--|--|--|--|

| - n = Value at POR                | '1' = Bit is set | 0' = Bit is cleared x = Bit is unknown |  |  |  |  |

#### 2.2.2.6 **PIE2** Register

The PIE2 register contains the individual enable bits for the CCP2 peripheral interrupt, the SSP bus collision interrupt, EEPROM write operation interrupt and the comparator interrupt.

- n = Value at POR

| REGISTER 2-6: | PIE2 REG                                                                                    | ISTER (AD                                                                                              | DRESS 8         | Dh)          |             |            |               |        |  |  |

|---------------|---------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------|-----------------|--------------|-------------|------------|---------------|--------|--|--|

|               | U-0                                                                                         | R/W-0                                                                                                  | U-0             | R/W-0        | R/W-0       | U-0        | U-0           | R/W-0  |  |  |

|               |                                                                                             | CMIE                                                                                                   |                 | EEIE         | BCLIE       | _          | _             | CCP2IE |  |  |

|               | bit 7                                                                                       |                                                                                                        |                 |              |             |            |               | bit 0  |  |  |

|               |                                                                                             |                                                                                                        |                 |              |             |            |               |        |  |  |

| bit 7         | Unimplem                                                                                    | ented: Read                                                                                            | <b>d as</b> '0' |              |             |            |               |        |  |  |

| bit 6         | CMIE: Con                                                                                   | nparator Inte                                                                                          | rrupt Enabl     | le bit       |             |            |               |        |  |  |

|               |                                                                                             | <ul> <li>1 = Enables the comparator interrupt</li> <li>0 = Disable the comparator interrupt</li> </ul> |                 |              |             |            |               |        |  |  |

| bit 5         | Unimplem                                                                                    | ented: Read                                                                                            | <b>d as</b> '0' |              |             |            |               |        |  |  |

| bit 4         | EEIE: EEP                                                                                   | ROM Write                                                                                              | Operation I     | nterrupt Ena | ble bit     |            |               |        |  |  |

|               |                                                                                             | EEPROM v<br>EEPROM v                                                                                   |                 |              |             |            |               |        |  |  |

| bit 3         | BCLIE: Bu                                                                                   | s Collision Ir                                                                                         | nterrupt Ena    | able bit     |             |            |               |        |  |  |

|               |                                                                                             | bus collision<br>bus collisio                                                                          | •               |              |             |            |               |        |  |  |

| bit 2-1       | Unimplem                                                                                    | ented: Read                                                                                            | <b>d as</b> '0' |              |             |            |               |        |  |  |

| bit 0         | CCP2IE: C                                                                                   | CP2 Interru                                                                                            | ot Enable b     | it           |             |            |               |        |  |  |

|               | <ul> <li>1 = Enables the CCP2 interrupt</li> <li>0 = Disables the CCP2 interrupt</li> </ul> |                                                                                                        |                 |              |             |            |               |        |  |  |

|               |                                                                                             |                                                                                                        |                 |              |             |            |               |        |  |  |

|               | Legend:                                                                                     |                                                                                                        |                 |              |             |            |               |        |  |  |

|               | R = Reada                                                                                   | ble bit                                                                                                | VV = V          | Vritable bit | U = Unimple | emented bi | it, read as ' | D'     |  |  |

'1' = Bit is set

'0' = Bit is cleared

#### Note: Bit PEIE (INTCON<6>) must be set to enable any peripheral interrupt.

x = Bit is unknown

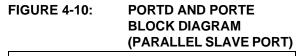

#### 4.5 PORTE and TRISE Register

| Note: | PORTE and TRISE are not implemented |  |  |  |  |  |  |

|-------|-------------------------------------|--|--|--|--|--|--|

|       | on the 28-pin devices.              |  |  |  |  |  |  |

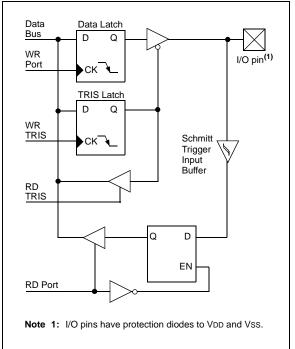

PORTE has three pins (RE0/RD/AN5, RE1/WR/AN6 and RE2/CS/AN7) which are individually configurable as inputs or outputs. These pins have Schmitt Trigger input buffers.

The PORTE pins become the I/O control inputs for the microprocessor port when bit PSPMODE (TRISE<4>) is set. In this mode, the user must make certain that the TRISE<2:0> bits are set and that the pins are configured as digital inputs. Also, ensure that ADCON1 is configured for digital I/O. In this mode, the input buffers are TTL.

Register 4-1 shows the TRISE register which also controls the Parallel Slave Port operation.

PORTE pins are multiplexed with analog inputs. When selected for analog input, these pins will read as '0's.

TRISE controls the direction of the RE pins, even when they are being used as analog inputs. The user must make sure to keep the pins configured as inputs when using them as analog inputs.

Note: On a Power-on Reset, these pins are configured as analog inputs and read as '0'.

#### TABLE 4-9: PORTE FUNCTIONS

#### FIGURE 4-9:

#### PORTE BLOCK DIAGRAM (IN I/O PORT MODE)

| Name       | Bit#  | Buffer Type           | Function                                                                                                                                                                                                                                   |

|------------|-------|-----------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| RE0/RD/AN5 | bit 0 | ST/TTL <sup>(1)</sup> | <ul> <li>I/O port pin or read control input in Parallel Slave Port mode or analog input:</li> <li>RD</li> <li>1 = Idle</li> <li>0 = Read operation. Contents of PORTD register are output to PORTD I/O pins (if chip selected).</li> </ul> |

| RE1/WR/AN6 | bit 1 | ST/TTL <sup>(1)</sup> | <ul> <li>I/O port pin or write control input in Parallel Slave Port mode or analog input:<br/>WR</li> <li>1 = Idle</li> <li>0 = Write operation. Value of PORTD I/O pins is latched into PORTD register (if chip selected).</li> </ul>     |

| RE2/CS/AN7 | bit 2 | ST/TTL <sup>(1)</sup> | <ul> <li>I/O port pin or chip select control input in Parallel Slave Port mode or analog input:</li> <li>CS</li> <li>1 = Device is not selected</li> <li>0 = Device is selected</li> </ul>                                                 |

Legend: ST = Schmitt Trigger input, TTL = TTL input

Note 1: Input buffers are Schmitt Triggers when in I/O mode and TTL buffers when in Parallel Slave Port mode.

#### 4.6 Parallel Slave Port

The Parallel Slave Port (PSP) is not implemented on the PIC16F873A or PIC16F876A.

PORTD operates as an 8-bit wide Parallel Slave Port, or microprocessor port, when control bit PSPMODE (TRISE<4>) is set. In Slave mode, it is asynchronously readable and writable by the external world through RD control input pin, RE0/RD/AN5, and WR control input pin, RE1/WR/AN6.

The PSP can directly interface to an 8-bit microprocessor data bus. The external microprocessor can read or write the PORTD latch as an 8-bit latch. Setting bit PSPMODE enables port pin RE0/RD/AN5 to be the RD input, RE1/WR/AN6 to be the WR input and RE2/CS/AN7 to be the CS (Chip Select) input. For this functionality, the corresponding data direction bits of the TRISE register (TRISE<2:0>) must be configured as inputs (set). The A/D port configuration bits, PCFG3:PCFG0 (ADCON1<3:0>), must be set to configure pins RE2:RE0 as digital I/O.

There are actually two 8-bit latches: one for data output and one for data input. The user writes 8-bit data to the PORTD data latch and reads data from the port pin latch (note that they have the same address). In this mode, the TRISD register is ignored since the external device is controlling the direction of data flow.

A write to the PSP occurs when both the  $\overline{CS}$  and  $\overline{WR}$ lines are first detected low. When either the  $\overline{CS}$  or  $\overline{WR}$ lines become high (level triggered), the Input Buffer Full (IBF) status flag bit (TRISE<7>) is set on the Q4 clock cycle, following the next Q2 cycle, to signal the write is complete (Figure 4-11). The interrupt flag bit, PSPIF (PIR1<7>), is also set on the same Q4 clock cycle. IBF can only be cleared by reading the PORTD input latch. The Input Buffer Overflow (IBOV) status flag bit (TRISE<5>) is set if a second write to the PSP is attempted when the previous byte has not been read out of the buffer.

A read from the PSP occurs when both the CS and RD lines are first detected low. The Output Buffer Full (OBF) status flag bit (TRISE<6>) is cleared immediately (Figure 4-12), indicating that the PORTD latch is waiting to be read by the external bus. When either the CS or RD pin becomes high (level triggered), the interrupt flag bit PSPIF is set on the Q4 clock cycle, following the next Q2 cycle, indicating that the read is complete. OBF remains low until data is written to PORTD by the user firmware. When not in PSP mode, the IBF and OBF bits are held clear. However, if flag bit IBOV was previously set, it must be cleared in firmware.

An interrupt is generated and latched into flag bit PSPIF when a read or write operation is completed. PSPIF must be cleared by the user in firmware and the interrupt can be disabled by clearing the interrupt enable bit PSPIE (PIE1<7>).

| <b>REGISTER 9-3:</b> | SSPSTAT:                                                                                                                                                                                              | MSSP STA                                                                                                                                                        | TUS REG       | SISTER (I <sup>2</sup> | C MODE)     | (ADDRESS    | 6 94h)         |         |  |

|----------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------|------------------------|-------------|-------------|----------------|---------|--|

|                      | R/W-0                                                                                                                                                                                                 | R/W-0                                                                                                                                                           | R-0           | R-0                    | R-0         | R-0         | R-0            | R-0     |  |

|                      | SMP                                                                                                                                                                                                   | CKE                                                                                                                                                             | D/A           | Р                      | S           | R/W         | UA             | BF      |  |

|                      | bit 7                                                                                                                                                                                                 |                                                                                                                                                                 |               |                        |             |             |                | bit 0   |  |

| bit 7                | SMP: Slew                                                                                                                                                                                             | Rate Contro                                                                                                                                                     | l bit         |                        |             |             |                |         |  |

|                      |                                                                                                                                                                                                       | or Slave mode                                                                                                                                                   |               |                        |             |             |                |         |  |

|                      |                                                                                                                                                                                                       | ate control dis                                                                                                                                                 |               |                        |             |             | 1 MHz)         |         |  |

| bit 6                |                                                                                                                                                                                                       | ate control en                                                                                                                                                  |               | gn-speed n             | 100e (400 K | ΠΖ)         |                |         |  |

| bit 0                |                                                                                                                                                                                                       | or Slave mode                                                                                                                                                   | <i>.</i>      |                        |             |             |                |         |  |

|                      | 1 = Enable                                                                                                                                                                                            | SMBus spec                                                                                                                                                      | ific inputs   |                        |             |             |                |         |  |

|                      |                                                                                                                                                                                                       | e SMBus spe                                                                                                                                                     | cific inputs  |                        |             |             |                |         |  |

| bit 5                |                                                                                                                                                                                                       | Address bit                                                                                                                                                     |               |                        |             |             |                |         |  |

|                      | <u>In Master n</u><br>Reserved.                                                                                                                                                                       | node:                                                                                                                                                           |               |                        |             |             |                |         |  |

|                      | In Slave me                                                                                                                                                                                           |                                                                                                                                                                 |               |                        |             |             |                |         |  |

|                      |                                                                                                                                                                                                       | es that the las                                                                                                                                                 | -             |                        |             |             |                |         |  |

| bit 4                | • = mulcate<br><b>P:</b> Stop bit                                                                                                                                                                     | es that the las                                                                                                                                                 | si byte rece  |                        | Smilleu was | audiess     |                |         |  |

| 511 4                | •                                                                                                                                                                                                     | es that a Stor                                                                                                                                                  | bit has be    | en detected            | last        |             |                |         |  |

|                      | <ul> <li>1 = Indicates that a Stop bit has been detected last</li> <li>0 = Stop bit was not detected last</li> </ul>                                                                                  |                                                                                                                                                                 |               |                        |             |             |                |         |  |

|                      | Note:                                                                                                                                                                                                 | This bit is clo                                                                                                                                                 | eared on Re   | eset and wh            | nen SSPEN   | is cleared. |                |         |  |

| bit 3                | S: Start bit                                                                                                                                                                                          |                                                                                                                                                                 |               |                        |             |             |                |         |  |

|                      |                                                                                                                                                                                                       | es that a Star<br>t was not det                                                                                                                                 |               | en detectec            | llast       |             |                |         |  |

|                      | Note:                                                                                                                                                                                                 |                                                                                                                                                                 |               | eset and wh            | nen SSPEN   | is cleared  |                |         |  |

| bit 2                | _                                                                                                                                                                                                     | <b>Note:</b> This bit is cleared on Reset and when SSPEN is cleared.<br>$\overline{W}$ : Read/ $\overline{W}$ rite bit information (I <sup>2</sup> C mode only) |               |                        |             |             |                |         |  |

| 511 2                | In Slave me                                                                                                                                                                                           |                                                                                                                                                                 |               |                        | y)          |             |                |         |  |

|                      | 1 = Read                                                                                                                                                                                              |                                                                                                                                                                 |               |                        |             |             |                |         |  |

|                      | 0 = Write                                                                                                                                                                                             |                                                                                                                                                                 |               |                        |             |             |                | <b></b> |  |

|                      | Note:                                                                                                                                                                                                 | This bit hold<br>only valid fro                                                                                                                                 |               |                        |             |             |                |         |  |

|                      | In Master mode:                                                                                                                                                                                       |                                                                                                                                                                 |               |                        |             |             |                |         |  |

|                      | <ul> <li>1 = Transmit is in progress</li> <li>0 = Transmit is not in progress</li> </ul>                                                                                                              |                                                                                                                                                                 |               |                        |             |             |                |         |  |

|                      | <b>Note:</b> ORing this bit with SEN, RSEN, PEN, RCEN or ACKEN will indicate if the MSSP is                                                                                                           |                                                                                                                                                                 |               |                        |             |             |                |         |  |

|                      |                                                                                                                                                                                                       | in Idle mode                                                                                                                                                    |               |                        |             |             |                |         |  |

| bit 1                | UA: Update                                                                                                                                                                                            | e Address (10                                                                                                                                                   | D-bit Slave i | mode only)             |             |             |                |         |  |

|                      |                                                                                                                                                                                                       | es that the us                                                                                                                                                  |               | •                      | address in  | the SSPADE  | D register     |         |  |

|                      |                                                                                                                                                                                                       | s does not ne                                                                                                                                                   | •             | odated                 |             |             |                |         |  |

| bit 0                | BF: Buffer Full Status bit                                                                                                                                                                            |                                                                                                                                                                 |               |                        |             |             |                |         |  |

|                      | In Transmit mode:<br>1 = Receive complete, SSPBUF is full                                                                                                                                             |                                                                                                                                                                 |               |                        |             |             |                |         |  |

|                      | 0 = Receive not complete, SSPBUF is empty                                                                                                                                                             |                                                                                                                                                                 |               |                        |             |             |                |         |  |

|                      | In Receive mode:                                                                                                                                                                                      |                                                                                                                                                                 |               |                        |             |             |                |         |  |

|                      | 1 = Data Transmit in progress (does not include the $\overline{ACK}$ and Stop bits), SSPBUF is full 0 = Data Transmit complete (does not include the $\overline{ACK}$ and Stop bits), SSPBUF is empty |                                                                                                                                                                 |               |                        |             |             |                |         |  |

|                      | Legend:                                                                                                                                                                                               |                                                                                                                                                                 |               |                        |             |             |                |         |  |

|                      | R = Reada                                                                                                                                                                                             | ble bit                                                                                                                                                         | W = W         | ritable bit            | U = Unir    | nplemented  | bit, read as ' | 0'      |  |

|                      | - n = Value                                                                                                                                                                                           |                                                                                                                                                                 | '1' = Bi      |                        |             | is cleared  | x = Bit is u   |         |  |

|                      |                                                                                                                                                                                                       |                                                                                                                                                                 |               |                        |             |             |                |         |  |

| REGISTER 9-4: SSPCON1: MSSP CONTROL REGISTER 1 (I <sup>2</sup> C MODE) (ADDRESS 14h)                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                                                         |                                          |                        |                |                |               |               |               |  |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------|------------------------|----------------|----------------|---------------|---------------|---------------|--|

|                                                                                                                                                                                                                                                                                                                                                                                                                                                          | R/W-0                                                                                                                                                   | R/W-0                                    | R/W-0                  | R/W-0          | R/W-0          | R/W-0         | R/W-0         | R/W-0         |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                          | WCOL                                                                                                                                                    | SSPOV                                    | SSPEN                  | CKP            | SSPM3          | SSPM2         | SSPM1         | SSPM0         |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                          | bit 7                                                                                                                                                   |                                          |                        |                |                |               |               | bit 0         |  |

| bit 7                                                                                                                                                                                                                                                                                                                                                                                                                                                    | WCOL: Wr                                                                                                                                                | rite Collision                           | Detect bit             |                |                |               |               |               |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                         | Fransmit moo                             |                        |                |                |               |               |               |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                         | e to the SSP<br>smission to t<br>Ilision |                        |                |                |               | itions were   | not valid for |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                          | In Slave Transmit mode:<br>1 = The SSPBUF register is written while it is still transmitting the previous wor<br>cleared in software.)                  |                                          |                        |                |                |               |               |               |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 0 = No col<br>In Receive                                                                                                                                | mode (Masi                               | ter or Slave           | modes):        |                |               |               |               |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                         | lon't care" bi                           |                        |                |                |               |               |               |  |

| bit 6                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                                                         | eceive Over                              | flow Indicato          | r bit          |                |               |               |               |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                          | In Receive mode:<br>1 = A byte is received while the SSPBUF register is still holding the previous byte. (N<br>cleared in software.)<br>0 = No overflow |                                          |                        |                |                |               |               | e. (Must be   |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                          | <u>In Transmi</u><br>This is a "d                                                                                                                       | <u>t mode:</u><br>Ion't care" bi         | t in Transmit          | mode.          |                |               |               |               |  |

| bit 5                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                                                         | ynchronous                               |                        |                |                |               |               |               |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                         | es the serial pes the serial             |                        |                |                |               | ne serial por | t pins        |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                          | Note:                                                                                                                                                   | When enab                                | led, the SDA           | and SCL pi     | ns must be p   | roperly confi | gured as inp  | ut or output. |  |

| bit 4                                                                                                                                                                                                                                                                                                                                                                                                                                                    | CKP: SCK                                                                                                                                                | Release Co                               | ontrol bit             |                |                |               |               |               |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                          | In Slave m<br>1 = Releas<br>0 = Holds o                                                                                                                 |                                          | ock stretch).          | (Used to er    | nsure data s   | etup time.)   |               |               |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                          | <u>In Master r</u><br>Unused in                                                                                                                         |                                          |                        |                |                |               |               |               |  |

| bit 3-0                                                                                                                                                                                                                                                                                                                                                                                                                                                  | SSPM3:SS                                                                                                                                                | SPM0: Synch                              | nronous Ser            | ial Port Moc   | le Select bits | 5             |               |               |  |

| 1111 = I <sup>2</sup> C Slave mode, 10-bit address with Start and Stop bit interrupts enabled<br>1110 = I <sup>2</sup> C Slave mode, 7-bit address with Start and Stop bit interrupts enabled<br>1011 = I <sup>2</sup> C Firmware Controlled Master mode (Slave Idle)<br>1000 = I <sup>2</sup> C Master mode, clock = Fosc/(4 * (SSPADD + 1))<br>0111 = I <sup>2</sup> C Slave mode, 10-bit address<br>0110 = I <sup>2</sup> C Slave mode, 7-bit address |                                                                                                                                                         |                                          |                        |                |                |               |               |               |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                          | Note:                                                                                                                                                   | Bit combina<br>SPI mode o                | ations not sp<br>only. | ecifically lis | ted here are   | e either rese | rved or imp   | emented in    |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                          | Legend:                                                                                                                                                 |                                          |                        |                |                |               |               | ]             |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                          | R = Reada                                                                                                                                               | ble bit                                  | W = W                  | ritable bit    | U = Unim       | plemented     | bit, read as  | '0'           |  |

|                |     |                  |                      | ,                  |

|----------------|-----|------------------|----------------------|--------------------|

| - n = Value at | POR | '1' = Bit is set | '0' = Bit is cleared | x = Bit is unknown |

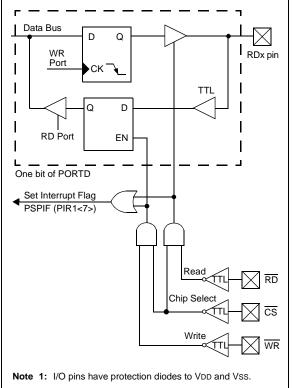

#### 9.4.6 MASTER MODE

Master mode is enabled by setting and clearing the appropriate SSPM bits in SSPCON and by setting the SSPEN bit. In Master mode, the SCL and SDA lines are manipulated by the MSSP hardware.

Master mode of operation is supported by interrupt generation on the detection of the Start and Stop conditions. The Stop (P) and Start (S) bits are cleared from a Reset or when the MSSP module is disabled. Control of the  $I^2C$  bus may be taken when the P bit is set or the bus is Idle, with both the S and P bits clear.

In Firmware Controlled Master mode, user code conducts all  $I^2C$  bus operations based on Start and Stop bit conditions.

Once Master mode is enabled, the user has six options.

- 1. Assert a Start condition on SDA and SCL.

- 2. Assert a Repeated Start condition on SDA and SCL.

- 3. Write to the SSPBUF register, initiating transmission of data/address.

- 4. Configure the I<sup>2</sup>C port to receive data.

- 5. Generate an Acknowledge condition at the end of a received byte of data.

- 6. Generate a Stop condition on SDA and SCL.

**Note:** The MSSP module, when configured in I<sup>2</sup>C Master mode, does not allow queueing of events. For instance, the user is not allowed to initiate a Start condition and immediately write the SSPBUF register to initiate transmission before the Start condition is complete. In this case, the SSPBUF will not be written to and the WCOL bit will be set, indicating that a write to the SSPBUF did not occur.

The following events will cause SSP Interrupt Flag bit, SSPIF, to be set (SSP interrupt if enabled):

- · Start condition

- Stop condition

- Data transfer byte transmitted/received

- Acknowledge transmit

- Repeated Start

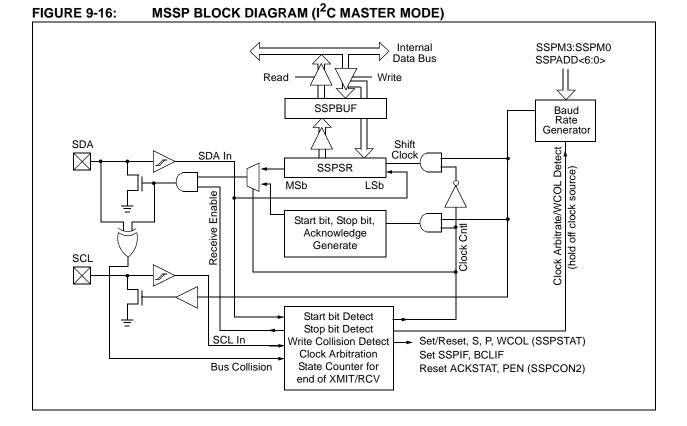

#### 9.4.12 ACKNOWLEDGE SEQUENCE TIMING

An Acknowledge sequence is enabled by setting the Acknowledge Sequence Enable bit. ACKEN (SSPCON2<4>). When this bit is set, the SCL pin is pulled low and the contents of the Acknowledge data bit are presented on the SDA pin. If the user wishes to generate an Acknowledge, then the ACKDT bit should be cleared. If not, the user should set the ACKDT bit before starting an Acknowledge sequence. The Baud Rate Generator then counts for one rollover period (TBRG) and the SCL pin is deasserted (pulled high). When the SCL pin is sampled high (clock arbitration), the Baud Rate Generator counts for TBRG. The SCL pin is then pulled low. Following this, the ACKEN bit is automatically cleared, the baud rate generator is turned off and the MSSP module then goes into Idle mode (Figure 9-23).

#### 9.4.12.1 WCOL Status Flag

If the user writes the SSPBUF when an Acknowledge sequence is in progress, then WCOL is set and the contents of the buffer are unchanged (the write doesn't occur).

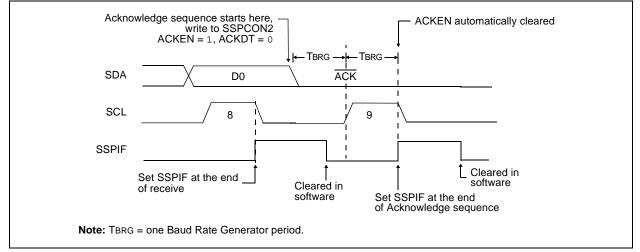

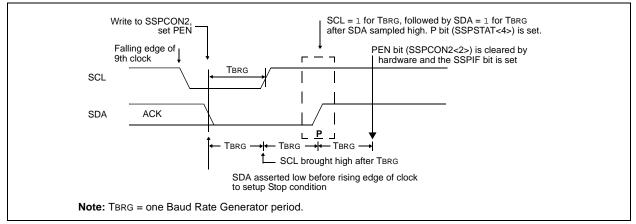

#### 9.4.13 STOP CONDITION TIMING

A Stop bit is asserted on the SDA pin at the end of a receive/transmit by setting the Stop Sequence Enable bit, PEN (SSPCON2<2>). At the end of a receive/ transmit, the SCL line is held low after the falling edge of the ninth clock. When the PEN bit is set, the master will assert the SDA line low. When the SDA line is sampled low, the Baud Rate Generator is reloaded and counts down to 0. When the Baud Rate Generator times out, the SCL pin will be brought high and one TBRG (Baud Rate Generator rollover count) later, the SDA pin will be deasserted. When the SDA pin is sampled high while SCL is high, the P bit (SSPSTAT<4>) is set. A TBRG later, the PEN bit is cleared and the SSPIF bit is set (Figure 9-24).

#### 9.4.13.1 WCOL Status Flag

If the user writes the SSPBUF when a Stop sequence is in progress, then the WCOL bit is set and the contents of the buffer are unchanged (the write doesn't occur).

#### FIGURE 9-23: ACKNOWLEDGE SEQUENCE WAVEFORM

#### FIGURE 9-24: STOP CONDITION RECEIVE OR TRANSMIT MODE

#### 16.3 MPLAB C17 and MPLAB C18 C Compilers

The MPLAB C17 and MPLAB C18 Code Development Systems are complete ANSI C compilers for Microchip's PIC17CXXX and PIC18CXXX family of microcontrollers. These compilers provide powerful integration capabilities, superior code optimization and ease of use not found with other compilers.

For easy source level debugging, the compilers provide symbol information that is optimized to the MPLAB IDE debugger.

#### 16.4 MPLINK Object Linker/ MPLIB Object Librarian

The MPLINK object linker combines relocatable objects created by the MPASM assembler and the MPLAB C17 and MPLAB C18 C compilers. It can link relocatable objects from precompiled libraries, using directives from a linker script.

The MPLIB object librarian manages the creation and modification of library files of pre-compiled code. When a routine from a library is called from a source file, only the modules that contain that routine will be linked in with the application. This allows large libraries to be used efficiently in many different applications.

The object linker/library features include:

- Efficient linking of single libraries instead of many smaller files

- Enhanced code maintainability by grouping related modules together

- Flexible creation of libraries with easy module listing, replacement, deletion and extraction

### 16.5 MPLAB C30 C Compiler

The MPLAB C30 C compiler is a full-featured, ANSI compliant, optimizing compiler that translates standard ANSI C programs into dsPIC30F assembly language source. The compiler also supports many command-line options and language extensions to take full advantage of the dsPIC30F device hardware capabilities, and afford fine control of the compiler code generator.

MPLAB C30 is distributed with a complete ANSI C standard library. All library functions have been validated and conform to the ANSI C library standard. The library includes functions for string manipulation, dynamic memory allocation, data conversion, time-keeping, and math functions (trigonometric, exponential and hyperbolic). The compiler provides symbolic information for high level source debugging with the MPLAB IDE.

## 16.6 MPLAB ASM30 Assembler, Linker, and Librarian

MPLAB ASM30 assembler produces relocatable machine code from symbolic assembly language for dsPIC30F devices. MPLAB C30 compiler uses the assembler to produce it's object file. The assembler generates relocatable object files that can then be archived or linked with other relocatable object files and archives to create an executable file. Notable features of the assembler include:

- Support for the entire dsPIC30F instruction set

- · Support for fixed-point and floating-point data

- Command line interface

- Rich directive set

- Flexible macro language

- MPLAB IDE compatibility

#### 16.7 MPLAB SIM Software Simulator

The MPLAB SIM software simulator allows code development in a PC hosted environment by simulating the PIC series microcontrollers on an instruction level. On any given instruction, the data areas can be examined or modified and stimuli can be applied from a file, or user defined key press, to any pin. The execution can be performed in Single-Step, Execute Until Break, or Trace mode.

The MPLAB SIM simulator fully supports symbolic debugging using the MPLAB C17 and MPLAB C18 C Compilers, as well as the MPASM assembler. The software simulator offers the flexibility to develop and debug code outside of the laboratory environment, making it an excellent, economical software development tool.

### 16.8 MPLAB SIM30 Software Simulator

The MPLAB SIM30 software simulator allows code development in a PC hosted environment by simulating the dsPIC30F series microcontrollers on an instruction level. On any given instruction, the data areas can be examined or modified and stimuli can be applied from a file, or user defined key press, to any of the pins.

The MPLAB SIM30 simulator fully supports symbolic debugging using the MPLAB C30 C Compiler and MPLAB ASM30 assembler. The simulator runs in either a Command Line mode for automated tasks, or from MPLAB IDE. This high speed simulator is designed to debug, analyze and optimize time intensive DSP routines.

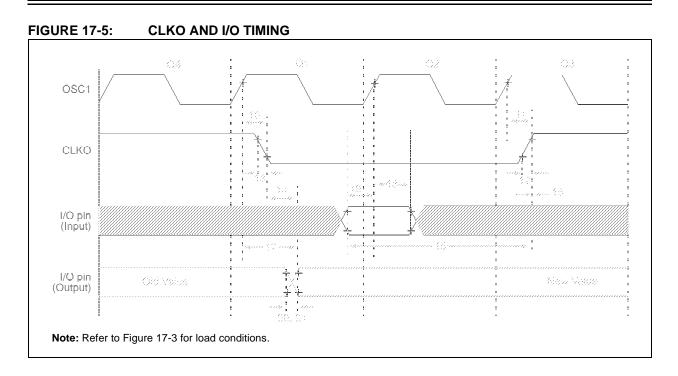

| Param<br>No. | Symbol   | Characteristic                      | Min           | Тур† | Мах          | Units | Conditions |          |

|--------------|----------|-------------------------------------|---------------|------|--------------|-------|------------|----------|

| 10*          | TosH2ckL | OSC1 ↑ to CLKO $↓$                  | _             | 75   | 200          | ns    | (Note 1)   |          |

| 11*          | TosH2ckH | OSC1 ↑ to CLKO ↑                    |               | —    | 75           | 200   | ns         | (Note 1) |

| 12*          | TCKR     | CLKO Rise Time                      | —             | 35   | 100          | ns    | (Note 1)   |          |

| 13*          | ТскF     | CLKO Fall Time                      | —             | 35   | 100          | ns    | (Note 1)   |          |

| 14*          | TCKL2IOV | CLKO ↓ to Port Out Valid            | —             |      | 0.5 TCY + 20 | ns    | (Note 1)   |          |

| 15*          | ТюV2скН  | Port In Valid before CLKO ↑         | Tosc + 200    | —    | _            | ns    | (Note 1)   |          |

| 16*          | TCKH2IOI | Port In Hold after CLKO ↑           | 0             | —    | _            | ns    | (Note 1)   |          |

| 17*          | TosH2IoV | OSC1 ↑ (Q1 cycle) to Port Out Va    | —             | 100  | 255          | ns    |            |          |

| 18*          | TosH2ıol | =    =                              | Standard (F)  | 100  | —            | —     | ns         |          |

|              |          |                                     | Extended (LF) | 200  | —            | _     | ns         |          |

| 19*          | TIOV20sH | Port Input Valid to OSC1 ↑ (I/O in  | 0             |      | —            | ns    |            |          |

| 20*          | TIOR     | Port Output Rise Time               | Standard (F)  | —    | 10           | 40    | ns         |          |

|              |          |                                     | Extended (LF) | —    |              | 145   | ns         |          |

| 21*          | TIOF     | Port Output Fall Time               | Standard (F)  | —    | 10           | 40    | ns         |          |

|              |          |                                     | Extended (LF) | —    |              | 145   | ns         |          |

| 22††*        | TINP     | INT pin High or Low Time            |               | Тсү  | —            | _     | ns         |          |

| 23††*        | Trbp     | RB7:RB4 Change INT High or Low Time |               | Тсү  | —            | _     | ns         |          |

These parameters are characterized but not tested.

† Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

†† These parameters are asynchronous events not related to any internal clock edges.

**Note 1:** Measurements are taken in RC mode where CLKO output is 4 x Tosc.

\*

NOTES:

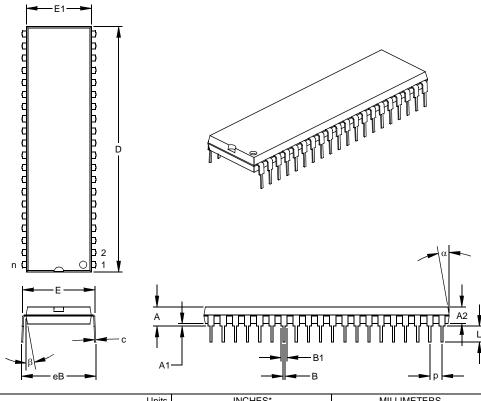

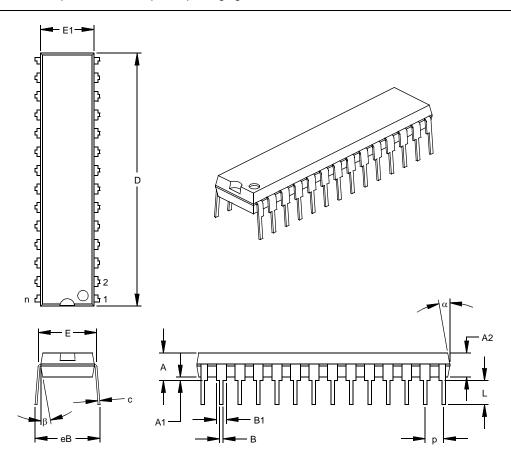

## 40-Lead Plastic Dual In-line (P) - 600 mil (PDIP)

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

|                            | Units | INCHES* |       |       | MILLIMETERS |       |       |  |