Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

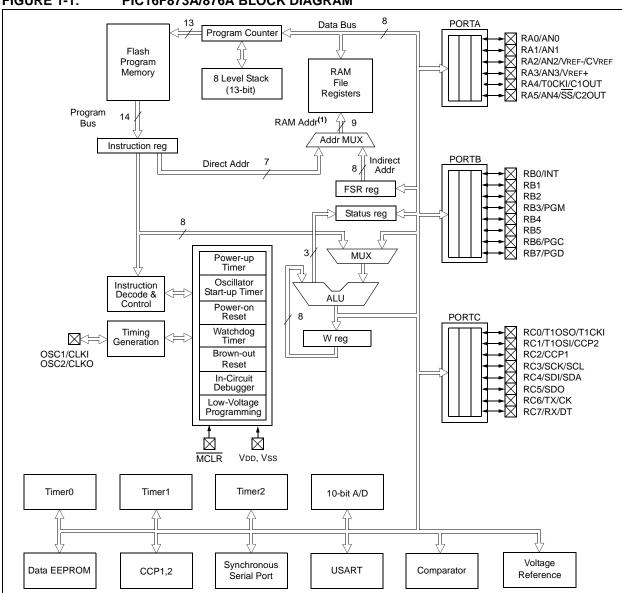

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                             |

|----------------------------|-----------------------------------------------------------------------------|

| Product Status             | Active                                                                      |

| Core Processor             | PIC                                                                         |

| Core Size                  | 8-Bit                                                                       |

| Speed                      | 10MHz                                                                       |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                           |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                       |

| Number of I/O              | 22                                                                          |

| Program Memory Size        | 14KB (8K x 14)                                                              |

| Program Memory Type        | FLASH                                                                       |

| EEPROM Size                | 256 x 8                                                                     |

| RAM Size                   | 368 x 8                                                                     |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 5.5V                                                                   |

| Data Converters            | A/D 5x10b                                                                   |

| Oscillator Type            | External                                                                    |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                           |

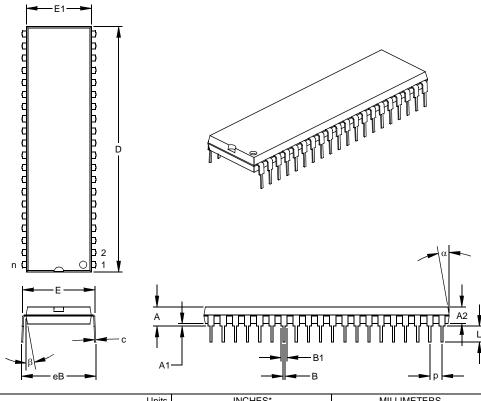

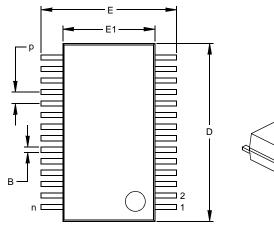

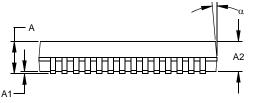

| Mounting Type              | Surface Mount                                                               |

| Package / Case             | 28-SSOP (0.209", 5.30mm Width)                                              |

| Supplier Device Package    | 28-SSOP                                                                     |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16lf876at-i-ss |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| Device     | evice Program Flash Data Memory |           | Data EEPROM |

|------------|---------------------------------|-----------|-------------|

| PIC16F873A | 4K words                        | 192 Bytes | 128 Bytes   |

| PIC16F876A | 8K words                        | 368 Bytes | 256 Bytes   |

Note 1: Higher order bits are from the Status register.

|                      | File<br>Address               | <i>I</i>                                                              | File<br>Address |                   |       | File<br>Addres          |      |

|----------------------|-------------------------------|-----------------------------------------------------------------------|-----------------|-------------------|-------|-------------------------|------|

| ndirect addr.(       | *) 00h                        | Indirect addr.(*)                                                     | 80h             | Indirect addr.(*) | 100h  | Indirect addr.(*)       | 180h |

| TMR0                 | 01h                           | OPTION_REG                                                            | 81h             | TMR0              | 101h  | OPTION_REG              | 181h |

| PCL                  | 02h                           | PCL                                                                   | 82h             | PCL               | 102h  | PCL                     | 182h |

| STATUS               | 03h                           | STATUS                                                                | 83h             | STATUS            | 103h  | STATUS                  | 183h |

| FSR                  | 04h                           | FSR                                                                   | 84h             | FSR               | 104h  | FSR                     | 184h |

| PORTA                | 05h                           | TRISA                                                                 | 85h             |                   | 105h  |                         | 185h |

| PORTB                | 06h                           | TRISB                                                                 | 86h             | PORTB             | 106h  | TRISB                   | 186h |

| PORTC                | 07h                           | TRISC                                                                 | 87h             |                   | 107h  |                         | 187h |

| PORTD <sup>(1)</sup> | 08h                           | TRISD <sup>(1)</sup>                                                  | 88h             |                   | 108h  |                         | 188h |

| PORTE <sup>(1)</sup> | 09h                           | TRISE <sup>(1)</sup>                                                  | 89h             |                   | 109h  |                         | 189h |

| PCLATH               | 0Ah                           | PCLATH                                                                | 8Ah             | PCLATH            | 10Ah  | PCLATH                  | 18Ah |

| INTCON               | 0Bh                           | INTCON                                                                | 8Bh             | INTCON            | 10Bh  | INTCON                  | 18Bh |

| PIR1                 | 0Ch                           | PIE1                                                                  | 8Ch             | EEDATA            | 10Ch  | EECON1                  | 18Ch |

| PIR2                 | 0Dh                           | PIE2                                                                  | 8Dh             | EEADR             | 10Dh  | EECON2                  | 18Dh |

| TMR1L                | 0Eh                           | PCON                                                                  | 8Eh             | EEDATH            | 10Eh  | Reserved <sup>(2)</sup> | 18Eh |

| TMR1H                | 0Fh                           |                                                                       | 8Fh             | EEADRH            | 10Fh  | Reserved <sup>(2)</sup> | 18Fh |

| T1CON                | 10h                           |                                                                       | 90h             |                   | 110h  |                         | 190h |

| TMR2                 | 11h                           | SSPCON2                                                               | 91h             |                   |       |                         |      |

| T2CON                | 12h                           | PR2                                                                   | 92h             |                   |       |                         |      |

| SSPBUF               | 13h                           | SSPADD                                                                | 93h             |                   |       |                         |      |

| SSPCON               | 14h                           | SSPSTAT                                                               | 94h             |                   |       |                         |      |

| CCPR1L               | 15h                           |                                                                       | 95h             |                   |       |                         |      |

| CCPR1H               | 16h                           |                                                                       | 96h             |                   |       |                         |      |

| CCP1CON              | 17h                           |                                                                       | 97h             |                   |       |                         |      |

| RCSTA                | 18h                           | TXSTA                                                                 | 98h             |                   |       |                         |      |

| TXREG                | 19h                           | SPBRG                                                                 | 99h             |                   |       |                         |      |

| RCREG                | 1Ah                           |                                                                       | 9Ah             |                   |       |                         |      |

| CCPR2L               | 1Bh                           |                                                                       | 9Bh             |                   |       |                         |      |

| CCPR2H               | 1Ch                           | CMCON                                                                 | 9Ch             |                   |       |                         |      |

| CCP2CON              | 1Dh                           | CVRCON                                                                | 9Dh             |                   |       |                         |      |

| ADRESH               | 1Eh                           | ADRESL                                                                | 9Eh             |                   |       |                         |      |

| ADCON0               | 1Fh                           | ADCON1                                                                | 9Fh             |                   | 120h  |                         | 1A0h |

| General              | 20h                           | General                                                               | A0h             |                   | 12011 |                         |      |

| Purpose              |                               | Purpose                                                               |                 | accesses          |       | accesses                |      |

| Register             |                               | Register                                                              |                 | 20h-7Fh           |       | A0h - FFh               |      |

| 96 Bytes             |                               | 96 Bytes                                                              |                 |                   | 16Fh  |                         | 1EFh |

|                      |                               | -                                                                     |                 |                   | 170h  |                         | 1F0h |

|                      |                               |                                                                       |                 |                   |       |                         |      |

| <b>D</b> 1 2         | 7Fh                           |                                                                       | FFh             | David C           | 17Fh  | Dersta 0                | 1FFh |

| Bank 0               |                               | Bank 1                                                                |                 | Bank 2            |       | Bank 3                  |      |

| * Not<br>ote 1: The  | a physical re<br>se registers | data memory loca<br>egister.<br>are not implemen<br>are reserved; mai | ted on the      | PIC16F873A.       |       |                         |      |

#### 2.2.2.6 **PIE2** Register

The PIE2 register contains the individual enable bits for the CCP2 peripheral interrupt, the SSP bus collision interrupt, EEPROM write operation interrupt and the comparator interrupt.

- n = Value at POR

| REGISTER 2-6: | PIE2 REG                                                                                    | ISTER (AD                                                                                              | DRESS 8         | Dh)          |             |            |               |        |  |  |  |

|---------------|---------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------|-----------------|--------------|-------------|------------|---------------|--------|--|--|--|

|               | U-0                                                                                         | R/W-0                                                                                                  | U-0             | R/W-0        | R/W-0       | U-0        | U-0           | R/W-0  |  |  |  |

|               |                                                                                             | CMIE                                                                                                   |                 | EEIE         | BCLIE       | _          | _             | CCP2IE |  |  |  |

|               | bit 7                                                                                       |                                                                                                        |                 |              |             |            |               | bit 0  |  |  |  |

|               |                                                                                             |                                                                                                        |                 |              |             |            |               |        |  |  |  |

| bit 7         | Unimplem                                                                                    | ented: Read                                                                                            | <b>d as</b> '0' |              |             |            |               |        |  |  |  |

| bit 6         | CMIE: Con                                                                                   | nparator Inte                                                                                          | rrupt Enabl     | le bit       |             |            |               |        |  |  |  |

|               |                                                                                             | <ul> <li>1 = Enables the comparator interrupt</li> <li>0 = Disable the comparator interrupt</li> </ul> |                 |              |             |            |               |        |  |  |  |

| bit 5         | Unimplem                                                                                    | ented: Read                                                                                            | <b>d as</b> '0' |              |             |            |               |        |  |  |  |

| bit 4         | EEIE: EEP                                                                                   | ROM Write                                                                                              | Operation I     | nterrupt Ena | ble bit     |            |               |        |  |  |  |

|               |                                                                                             | <ul> <li>1 = Enable EEPROM write interrupt</li> <li>0 = Disable EEPROM write interrupt</li> </ul>      |                 |              |             |            |               |        |  |  |  |

| bit 3         | BCLIE: Bu                                                                                   | s Collision Ir                                                                                         | nterrupt Ena    | able bit     |             |            |               |        |  |  |  |

|               |                                                                                             | <ul> <li>1 = Enable bus collision interrupt</li> <li>0 = Disable bus collision interrupt</li> </ul>    |                 |              |             |            |               |        |  |  |  |

| bit 2-1       | Unimplem                                                                                    | ented: Read                                                                                            | <b>d as</b> '0' |              |             |            |               |        |  |  |  |

| bit 0         | CCP2IE: C                                                                                   | CP2 Interru                                                                                            | ot Enable b     | it           |             |            |               |        |  |  |  |

|               | <ul> <li>1 = Enables the CCP2 interrupt</li> <li>0 = Disables the CCP2 interrupt</li> </ul> |                                                                                                        |                 |              |             |            |               |        |  |  |  |

|               |                                                                                             |                                                                                                        |                 |              |             |            |               |        |  |  |  |

|               | Legend:                                                                                     |                                                                                                        |                 |              |             |            |               |        |  |  |  |

|               | R = Reada                                                                                   | ble bit                                                                                                | VV = V          | Vritable bit | U = Unimple | emented bi | it, read as ' | D'     |  |  |  |

'1' = Bit is set

'0' = Bit is cleared

#### Note: Bit PEIE (INTCON<6>) must be set to enable any peripheral interrupt.

x = Bit is unknown

NOTES:

### 6.4 Timer1 Operation in Asynchronous Counter Mode

If control bit  $\overline{T1SYNC}$  (T1CON<2>) is set, the external clock input is not synchronized. The timer continues to increment asynchronous to the internal phase clocks. The timer will continue to run during Sleep and can generate an interrupt-on-overflow which will wake-up the processor. However, special precautions in software are needed to read/write the timer.

In Asynchronous Counter mode, Timer1 cannot be used as a time base for capture or compare operations.

#### 6.4.1 READING AND WRITING TIMER1 IN ASYNCHRONOUS COUNTER MODE

Reading TMR1H or TMR1L while the timer is running from an external asynchronous clock will ensure a valid read (taken care of in hardware). However, the user should keep in mind that reading the 16-bit timer in two 8-bit values itself, poses certain problems, since the timer may overflow between the reads.

For writes, it is recommended that the user simply stop the timer and write the desired values. A write contention may occur by writing to the timer registers while the register is incrementing. This may produce an unpredictable value in the timer register.

Reading the 16-bit value requires some care. Examples 12-2 and 12-3 in the PIC<sup>®</sup> Mid-Range MCU Family Reference Manual (DS33023) show how to read and write Timer1 when it is running in Asynchronous mode.

### 6.5 Timer1 Oscillator

A crystal oscillator circuit is built-in between pins T1OSI (input) and T1OSO (amplifier output). It is enabled by setting control bit, T1OSCEN (T1CON<3>). The oscillator is a low-power oscillator, rated up to 200 kHz. It will continue to run during Sleep. It is primarily intended for use with a 32 kHz crystal. Table 6-1 shows the capacitor selection for the Timer1 oscillator.

The Timer1 oscillator is identical to the LP oscillator. The user must provide a software time delay to ensure proper oscillator start-up.

## TABLE 6-1:CAPACITOR SELECTION FOR<br/>THE TIMER1 OSCILLATOR

| Freq.                                  | C1                                                                                    | C2                                                                                                                                                   |  |  |  |

|----------------------------------------|---------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| 32 kHz                                 | 33 pF                                                                                 | 33 pF                                                                                                                                                |  |  |  |

| 100 kHz                                | 15 pF                                                                                 |                                                                                                                                                      |  |  |  |

| 200 kHz 15 p                           |                                                                                       |                                                                                                                                                      |  |  |  |

| lues are for o                         | design guida                                                                          | nce only.                                                                                                                                            |  |  |  |

| Crystals                               | Tested:                                                                               |                                                                                                                                                      |  |  |  |

| Epson C-00                             | 1R32.768K-A                                                                           | ± 20 PPM                                                                                                                                             |  |  |  |

| 100 kHz Epson C-2 100.00 KC-P ± 20 PPM |                                                                                       |                                                                                                                                                      |  |  |  |

| STD XTL 2                              | 200.000 kHz                                                                           | ± 20 PPM                                                                                                                                             |  |  |  |

|                                        | 32 kHz<br>100 kHz<br>200 kHz<br>Iues are for o<br>Crystals<br>Epson C-00<br>Epson C-2 | 32 kHz     33 pF       100 kHz     15 pF       200 kHz     15 pF       lues are for design guidat       Crystals Tested:       Epson C-001R32.768K-A |  |  |  |

**Note 1:** Higher capacitance increases the stability of oscillator but also increases the start-up time.

2: Since each resonator/crystal has its own characteristics, the user should consult the resonator/crystal manufacturer for appropriate values of external components.

### 6.6 Resetting Timer1 Using a CCP Trigger Output

If the CCP1 or CCP2 module is configured in Compare mode to generate a "special event trigger" (CCP1M3:CCP1M0 = 1011), this signal will reset Timer1.

| Note: | The special event triggers from the CCP1 |

|-------|------------------------------------------|

|       | and CCP2 modules will not set interrupt  |

|       | flag bit, TMR1IF (PIR1<0>).              |

Timer1 must be configured for either Timer or Synchronized Counter mode to take advantage of this feature. If Timer1 is running in Asynchronous Counter mode, this Reset operation may not work.

In the event that a write to Timer1 coincides with a special event trigger from CCP1 or CCP2, the write will take precedence.

In this mode of operation, the CCPRxH:CCPRxL register pair effectively becomes the period register for Timer1.

#### 8.3.3 SETUP FOR PWM OPERATION

The following steps should be taken when configuring the CCP module for PWM operation:

- 1. Set the PWM period by writing to the PR2 register.

- 2. Set the PWM duty cycle by writing to the CCPR1L register and CCP1CON<5:4> bits.

- 3. Make the CCP1 pin an output by clearing the TRISC<2> bit.

- 4. Set the TMR2 prescale value and enable Timer2 by writing to T2CON.

- 5. Configure the CCP1 module for PWM operation.

| PWM Frequency              | 1.22 kHz | 4.88 kHz | 19.53 kHz | 78.12kHz | 156.3 kHz | 208.3 kHz |

|----------------------------|----------|----------|-----------|----------|-----------|-----------|

| Timer Prescaler (1, 4, 16) | 16       | 4        | 1         | 1        | 1         | 1         |

| PR2 Value                  | 0xFFh    | 0xFFh    | 0xFFh     | 0x3Fh    | 0x1Fh     | 0x17h     |

| Maximum Resolution (bits)  | 10       | 10       | 10        | 8        | 7         | 5.5       |

| TABLE 8-4: | <b>REGISTERS ASSOCIATED WITH CAPTURE, COMPARE AND TIMER1</b> |

|------------|--------------------------------------------------------------|

|------------|--------------------------------------------------------------|

| Address                | Name    | Bit 7                | Bit 6                                | Bit 5        | Bit 4         | Bit 3          | Bit 2      | Bit 1      | Bit 0  | Value on:<br>POR, BOR | Value on<br>all other<br>Resets |

|------------------------|---------|----------------------|--------------------------------------|--------------|---------------|----------------|------------|------------|--------|-----------------------|---------------------------------|

| 0Bh,8Bh,<br>10Bh, 18Bh | INTCON  | GIE                  | PEIE                                 | TMR0IE       | INTE          | RBIE           | TMR0IF     | INTF       | RBIF   | 0000 000x             | 0000 000u                       |

| 0Ch                    | PIR1    | PSPIF <sup>(1)</sup> | ADIF                                 | RCIF         | TXIF          | SSPIF          | CCP1IF     | TMR2IF     | TMR1IF | 0000 0000             | 0000 0000                       |

| 0Dh                    | PIR2    | —                    | —                                    | _            | _             | —              | —          | _          | CCP2IF | 0                     | 0                               |

| 8Ch                    | PIE1    | PSPIE <sup>(1)</sup> | ADIE                                 | RCIE         | TXIE          | SSPIE          | CCP1IE     | TMR2IE     | TMR1IE | 0000 0000             | 0000 0000                       |

| 8Dh                    | PIE2    | —                    | —                                    | _            | _             | —              | —          | _          | CCP2IE | 0                     | 0                               |

| 87h                    | TRISC   | PORTC D              | ata Direc                            | tion Registe | er            |                |            |            |        | 1111 1111             | 1111 1111                       |

| 0Eh                    | TMR1L   | Holding R            | egister fo                           | r the Least  | Significant I | Byte of the 1  | 6-bit TMR' | 1 Register |        | xxxx xxxx             | uuuu uuuu                       |

| 0Fh                    | TMR1H   | Holding R            | egister fo                           | r the Most S | Significant E | Byte of the 10 | 6-bit TMR1 | Register   |        | xxxx xxxx             | uuuu uuuu                       |

| 10h                    | T1CON   | —                    | —                                    | T1CKPS1      | T1CKPS0       | T1OSCEN        | T1SYNC     | TMR1CS     | TMR10N | 00 0000               | uu uuuu                         |

| 15h                    | CCPR1L  | Capture/C            | Compare/F                            | PWM Regis    | ter 1 (LSB)   |                |            |            |        | xxxx xxxx             | uuuu uuuu                       |

| 16h                    | CCPR1H  | Capture/C            | Compare/F                            | PWM Regis    | ter 1 (MSB)   | )              |            |            |        | xxxx xxxx             | uuuu uuuu                       |

| 17h                    | CCP1CON | _                    | _                                    | CCP1X        | CCP1Y         | CCP1M3         | CCP1M2     | CCP1M1     | CCP1M0 | 00 0000               | 00 0000                         |

| 1Bh                    | CCPR2L  | Capture/C            | Capture/Compare/PWM Register 2 (LSB) |              |               |                |            |            |        |                       | uuuu uuuu                       |

| 1Ch                    | CCPR2H  | Capture/C            | Compare/F                            | PWM Regis    | ter 2 (MSB)   | )              |            |            |        | xxxx xxxx             | uuuu uuuu                       |

| 1Dh                    | CCP2CON | _                    |                                      | CCP2X        | CCP2Y         | CCP2M3         | CCP2M2     | CCP2M1     | CCP2M0 | 00 0000               | 00 0000                         |

Legend: x = unknown, u = unchanged, - = unimplemented, read as '0'. Shaded cells are not used by Capture and Timer1.

Note 1: The PSP is not implemented on 28-pin devices; always maintain these bits clear.

#### 9.3.1 REGISTERS

The MSSP module has four registers for SPI mode operation. These are:

- MSSP Control Register (SSPCON)

- MSSP Status Register (SSPSTAT)

- Serial Receive/Transmit Buffer Register (SSPBUF)

- MSSP Shift Register (SSPSR) Not directly accessible

SSPCON and SSPSTAT are the control and status registers in SPI mode operation. The SSPCON register is readable and writable. The lower six bits of the SSPSTAT are read-only. The upper two bits of the SSPSTAT are read/write. SSPSR is the shift register used for shifting data in or out. SSPBUF is the buffer register to which data bytes are written to or read from.

In receive operations, SSPSR and SSPBUF together create a double-buffered receiver. When SSPSR receives a complete byte, it is transferred to SSPBUF and the SSPIF interrupt is set.

During transmission, the SSPBUF is not doublebuffered. A write to SSPBUF will write to both SSPBUF and SSPSR.

#### REGISTER 9-1: SSPSTAT: MSSP STATUS REGISTER (SPI MODE) (ADDRESS 94h)

|       | R/W-0                                                             | R/W-0                                                                                                                               | R-0             | R-0          | R-0          | R-0           | R-0          | R-0           |  |  |  |

|-------|-------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------|-----------------|--------------|--------------|---------------|--------------|---------------|--|--|--|

|       | SMP                                                               | CKE                                                                                                                                 | D/A             | Р            | S            | R/W           | UA           | BF            |  |  |  |

|       | bit 7                                                             |                                                                                                                                     |                 |              |              |               |              | bit 0         |  |  |  |

| bit 7 | SMP: Sam                                                          | ple bit                                                                                                                             |                 |              |              |               |              |               |  |  |  |

|       | SPI Master mode:                                                  |                                                                                                                                     |                 |              |              |               |              |               |  |  |  |

|       |                                                                   | <ul> <li>1 = Input data sampled at end of data output time</li> <li>0 = Input data sampled at middle of data output time</li> </ul> |                 |              |              |               |              |               |  |  |  |

|       |                                                                   |                                                                                                                                     | at middle o     | r data outpu | tume         |               |              |               |  |  |  |

|       | SMP must                                                          | be cleared v                                                                                                                        | when SPI is     | used in Slav | ve mode      |               |              |               |  |  |  |

| bit 6 |                                                                   | Clock Select                                                                                                                        |                 |              | o modo.      |               |              |               |  |  |  |

|       | 1 = Transm                                                        | nit occurs on                                                                                                                       | transition fr   | om active to | ldle clock s | state         |              |               |  |  |  |

|       | 0 = Transmit occurs on transition from Idle to active clock state |                                                                                                                                     |                 |              |              |               |              |               |  |  |  |

|       | Note:                                                             | Polarity of o                                                                                                                       | clock state is  | s set by the | CKP bit (SS  | PCON1<4>      | ).           |               |  |  |  |

| bit 5 | D/A: Data/                                                        | Address bit                                                                                                                         |                 |              |              |               |              |               |  |  |  |

|       | Used in I <sup>2</sup> C                                          | c mode only.                                                                                                                        |                 |              |              |               |              |               |  |  |  |

| bit 4 | P: Stop bit                                                       |                                                                                                                                     |                 |              |              |               |              |               |  |  |  |

|       | Used in I <sup>2</sup> C                                          | mode only.                                                                                                                          | This bit is cle | ared when t  | he MSSP me   | odule is disa | bled, SSPEI  | N is cleared. |  |  |  |

| bit 3 | S: Start bit                                                      |                                                                                                                                     |                 |              |              |               |              |               |  |  |  |

|       | Used in I <sup>2</sup> C                                          | c mode only.                                                                                                                        |                 |              |              |               |              |               |  |  |  |

| bit 2 | R/W: Read                                                         | I/Write bit inf                                                                                                                     | ormation        |              |              |               |              |               |  |  |  |

|       | Used in I <sup>2</sup> C                                          | c mode only.                                                                                                                        |                 |              |              |               |              |               |  |  |  |

| bit 1 | UA: Update                                                        | e Address b                                                                                                                         | it              |              |              |               |              |               |  |  |  |

|       | Used in I <sup>2</sup> C                                          | c mode only.                                                                                                                        |                 |              |              |               |              |               |  |  |  |

| bit 0 | BF: Buffer                                                        | Full Status b                                                                                                                       | oit (Receive    | mode only)   |              |               |              |               |  |  |  |

|       | 1 = Receiv                                                        | e complete,                                                                                                                         | SSPBUF is       | full         |              |               |              |               |  |  |  |

|       | 0 = Receiv                                                        | e not comple                                                                                                                        | ete, SSPBU      | F is empty   |              |               |              |               |  |  |  |

|       | Legend:                                                           |                                                                                                                                     |                 |              |              |               |              |               |  |  |  |

|       | R = Reada                                                         | ble bit                                                                                                                             | W = W           | ritable bit  | U = Unim     | plemented     | bit, read as | '0'           |  |  |  |

|       | - n = Value                                                       | at POR                                                                                                                              | '1' = B         | it is set    | '0' = Bit i  | s cleared     | x = Bit is ι | Inknown       |  |  |  |

#### 9.3.3 ENABLING SPI I/O

To enable the serial port, SSP Enable bit, SSPEN (SSPCON<5>), must be set. To reset or reconfigure SPI mode, clear the SSPEN bit, re-initialize the SSPCON registers and then set the SSPEN bit. This configures the SDI, SDO, SCK and SS pins as serial port pins. For the pins to behave as the serial port function, some must have their data direction bits (in the TRIS register) appropriately programmed. That is:

- SDI is automatically controlled by the SPI module

- SDO must have TRISC<5> bit cleared

- SCK (Master mode) must have TRISC<3> bit cleared

- SCK (Slave mode) must have TRISC<3> bit set

- SS must have TRISC<4> bit set

Any serial port function that is not desired may be overridden by programming the corresponding data direction (TRIS) register to the opposite value.

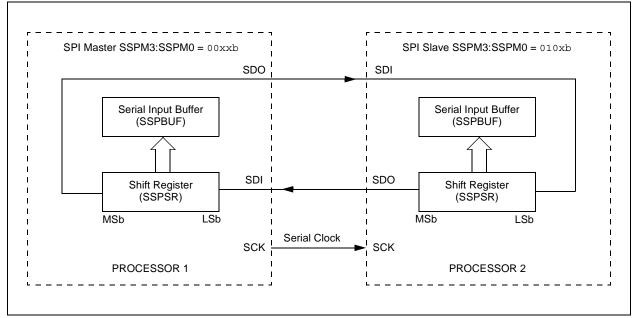

#### 9.3.4 TYPICAL CONNECTION

Figure 9-2 shows a typical connection between two microcontrollers. The master controller (Processor 1) initiates the data transfer by sending the SCK signal. Data is shifted out of both shift registers on their programmed clock edge and latched on the opposite edge of the clock. Both processors should be programmed to the same Clock Polarity (CKP), then both controllers would send and receive data at the same time. Whether the data is meaningful (or dummy data) depends on the application software. This leads to three scenarios for data transmission:

- Master sends data Slave sends dummy data

- Master sends data Slave sends data

- Master sends dummy data Slave sends data

#### FIGURE 9-2: SPI MASTER/SLAVE CONNECTION

| REGISTER 9-4: | SSPCON1: MSSP CONTROL REGISTER 1 (I <sup>2</sup> C MODE) (ADDRESS 14h)                                                                                                                                                                                                                                                                                                                       |                                                                                                                                                    |               |              |                |           |              |       |  |  |  |  |

|---------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------|---------------|--------------|----------------|-----------|--------------|-------|--|--|--|--|

|               | R/W-0                                                                                                                                                                                                                                                                                                                                                                                        | R/W-0                                                                                                                                              | R/W-0         | R/W-0        | R/W-0          | R/W-0     | R/W-0        | R/W-0 |  |  |  |  |

|               | WCOL                                                                                                                                                                                                                                                                                                                                                                                         | SSPOV                                                                                                                                              | SSPEN         | CKP          | SSPM3          | SSPM2     | SSPM1        | SSPM0 |  |  |  |  |

|               | bit 7                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                                    |               |              |                |           |              | bit 0 |  |  |  |  |

| bit 7         | WCOL: Wr                                                                                                                                                                                                                                                                                                                                                                                     | rite Collision                                                                                                                                     | Detect bit    |              |                |           |              |       |  |  |  |  |

|               | In Master Transmit mode:                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                                                    |               |              |                |           |              |       |  |  |  |  |

|               | <ul> <li>1 = A write to the SSPBUF register was attempted while the I<sup>2</sup>C conditions were not valid for<br/>a transmission to be started. (Must be cleared in software.)</li> <li>0 = No collision</li> </ul>                                                                                                                                                                       |                                                                                                                                                    |               |              |                |           |              |       |  |  |  |  |

|               | <u>In Slave Transmit mode:</u><br>1 = The SSPBUF register is written while it is still transmitting the previous word. (Must be<br>cleared in software.)                                                                                                                                                                                                                                     |                                                                                                                                                    |               |              |                |           |              |       |  |  |  |  |

|               | 0 = No col<br>In Receive                                                                                                                                                                                                                                                                                                                                                                     | mode (Masi                                                                                                                                         | ter or Slave  | modes):      |                |           |              |       |  |  |  |  |

|               |                                                                                                                                                                                                                                                                                                                                                                                              | lon't care" bi                                                                                                                                     |               |              |                |           |              |       |  |  |  |  |

| bit 6         |                                                                                                                                                                                                                                                                                                                                                                                              | eceive Over                                                                                                                                        | flow Indicato | r bit        |                |           |              |       |  |  |  |  |

|               | <ul> <li>In Receive mode:</li> <li>1 = A byte is received while the SSPBUF register is still holding the previous byte. (Must be cleared in software.)</li> <li>0 = No overflow</li> </ul>                                                                                                                                                                                                   |                                                                                                                                                    |               |              |                |           |              |       |  |  |  |  |

|               | <u>In Transmit mode:</u><br>This is a "don't care" bit in Transmit mode.                                                                                                                                                                                                                                                                                                                     |                                                                                                                                                    |               |              |                |           |              |       |  |  |  |  |

| bit 5         | SSPEN: Synchronous Serial Port Enable bit                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                                                    |               |              |                |           |              |       |  |  |  |  |

|               |                                                                                                                                                                                                                                                                                                                                                                                              | ables the serial port and configures the SDA and SCL pins as the serial port pins ables the serial port and configures these pins as I/O port pins |               |              |                |           |              |       |  |  |  |  |

|               | Note: When enabled, the SDA and SCL pins must be properly configured as input or output.                                                                                                                                                                                                                                                                                                     |                                                                                                                                                    |               |              |                |           |              |       |  |  |  |  |

| bit 4         | CKP: SCK                                                                                                                                                                                                                                                                                                                                                                                     | Release Co                                                                                                                                         | ontrol bit    |              |                |           |              |       |  |  |  |  |

|               | In Slave mode:<br>1 = Release clock<br>0 = Holds clock low (clock stretch). (Used to ensure data setup time.)                                                                                                                                                                                                                                                                                |                                                                                                                                                    |               |              |                |           |              |       |  |  |  |  |

|               | In Master mode:<br>Unused in this mode.                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                                                    |               |              |                |           |              |       |  |  |  |  |

| bit 3-0       | SSPM3:SS                                                                                                                                                                                                                                                                                                                                                                                     | SPM0: Synch                                                                                                                                        | nronous Ser   | ial Port Moc | le Select bits | 5         |              |       |  |  |  |  |

|               | 1111 = $I^2C$ Slave mode, 10-bit address with Start and Stop bit interrupts enabled<br>1110 = $I^2C$ Slave mode, 7-bit address with Start and Stop bit interrupts enabled<br>1011 = $I^2C$ Firmware Controlled Master mode (Slave Idle)<br>1000 = $I^2C$ Master mode, clock = Fosc/(4 * (SSPADD + 1))<br>0111 = $I^2C$ Slave mode, 10-bit address<br>0110 = $I^2C$ Slave mode, 7-bit address |                                                                                                                                                    |               |              |                |           |              |       |  |  |  |  |

|               | <b>Note:</b> Bit combinations not specifically listed here are either reserved or implemented in SPI mode only.                                                                                                                                                                                                                                                                              |                                                                                                                                                    |               |              |                |           |              |       |  |  |  |  |

|               | Legend:                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                                                    |               |              |                |           |              | ]     |  |  |  |  |

|               | R = Reada                                                                                                                                                                                                                                                                                                                                                                                    | ble bit                                                                                                                                            | W = W         | ritable bit  | U = Unim       | plemented | bit, read as | '0'   |  |  |  |  |

|                |     |                  |                      | ,                  |

|----------------|-----|------------------|----------------------|--------------------|

| - n = Value at | POR | '1' = Bit is set | '0' = Bit is cleared | x = Bit is unknown |

|       | R/W-0                                                                                                                                                                                              | R/W-0                                                                                                                                                                          | R/W-0                    | R/W-0          | R/W-0        | R/W-0        | R/W-0        | R/W-0     |  |  |  |  |

|-------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------|----------------|--------------|--------------|--------------|-----------|--|--|--|--|

|       | GCEN                                                                                                                                                                                               | ACKSTAT                                                                                                                                                                        | ACKDT                    | ACKEN          | RCEN         | PEN          | RSEN         | SEN       |  |  |  |  |

|       | bit 7                                                                                                                                                                                              | 1                                                                                                                                                                              |                          | I              |              | I            | I            | bit 0     |  |  |  |  |

| bit 7 |                                                                                                                                                                                                    | eneral Call En                                                                                                                                                                 |                          | -              | -            |              |              |           |  |  |  |  |

|       |                                                                                                                                                                                                    | e interrupt whe<br>ral call address                                                                                                                                            |                          | call address   | (0000h) is   | received in  | the SSPSF    | 2         |  |  |  |  |

| bit 6 | ACKSTA                                                                                                                                                                                             | <b>f:</b> Acknowledg                                                                                                                                                           | e Status bit             | (Master Tran   | smit mode o  | only)        |              |           |  |  |  |  |

|       |                                                                                                                                                                                                    | <ol> <li>1 = Acknowledge was not received from slave</li> <li>0 = Acknowledge was received from slave</li> </ol>                                                               |                          |                |              |              |              |           |  |  |  |  |

| bit 5 | bit 5 ACKDT: Acknowledge Data bit (Master Receive mode only)                                                                                                                                       |                                                                                                                                                                                |                          |                |              |              |              |           |  |  |  |  |

|       |                                                                                                                                                                                                    | 1 = Not Acknowledge<br>0 = Acknowledge                                                                                                                                         |                          |                |              |              |              |           |  |  |  |  |

|       | <b>Note:</b> Value that will be transmitted when the user initiates an Acknowledge sequer the end of a receive.                                                                                    |                                                                                                                                                                                |                          |                |              |              |              |           |  |  |  |  |

| bit 4 | ACKEN:                                                                                                                                                                                             | Acknowledge                                                                                                                                                                    | Sequence E               | nable bit (Ma  | ster Receiv  | e mode on    | ly)          |           |  |  |  |  |

|       | 1 = Initiat<br>Autor                                                                                                                                                                               | <ul> <li>1 = Initiate Acknowledge sequence on SDA and SCL pins and transmit ACKDT data by Automatically cleared by hardware.</li> <li>0 = Acknowledge sequence Idle</li> </ul> |                          |                |              |              |              |           |  |  |  |  |

| bit 3 | RCEN: R                                                                                                                                                                                            | eceive Enable                                                                                                                                                                  | bit (Master i            | mode only)     |              |              |              |           |  |  |  |  |

|       | 1 = Enabl<br>0 = Recei                                                                                                                                                                             | es Receive mo<br>ve Idle                                                                                                                                                       | ode for I <sup>2</sup> C |                |              |              |              |           |  |  |  |  |

| bit 2 | PEN: Stop                                                                                                                                                                                          | o Condition En                                                                                                                                                                 | able bit (Ma             | ster mode or   | nly)         |              |              |           |  |  |  |  |

|       |                                                                                                                                                                                                    | e Stop conditio                                                                                                                                                                | n on SDA a               | nd SCL pins.   | Automatica   | ally cleared | by hardwa    | re.       |  |  |  |  |

| bit 1 | RSEN: Re                                                                                                                                                                                           | epeated Start (                                                                                                                                                                | Condition Er             | nabled bit (Ma | aster mode   | only)        |              |           |  |  |  |  |

|       |                                                                                                                                                                                                    | e Repeated Sta<br>ated Start cond                                                                                                                                              |                          | on SDA and S   | SCL pins. A  | utomatically | y cleared by | hardware. |  |  |  |  |

| bit 0 | SEN: Star                                                                                                                                                                                          | t Condition En                                                                                                                                                                 | abled/Streto             | h Enabled bi   | t            |              |              |           |  |  |  |  |

|       |                                                                                                                                                                                                    | <u>mode:</u><br>e Start conditic<br>condition Idle                                                                                                                             | on on SDA a              | nd SCL pins.   | Automatica   | ally cleared | by hardwa    | re.       |  |  |  |  |

|       | In Slave mode:<br>1 = Clock stretching is enabled for both slave transmit and slave receive (stretch enabled)<br>0 = Clock stretching is enabled for slave transmit only (PIC16F87X compatibility) |                                                                                                                                                                                |                          |                |              |              |              |           |  |  |  |  |

|       | Legend:                                                                                                                                                                                            | -                                                                                                                                                                              |                          |                |              |              |              |           |  |  |  |  |

|       | R = Read                                                                                                                                                                                           |                                                                                                                                                                                |                          | itable bit     | -            |              | bit, read as |           |  |  |  |  |

|       | - n = Valu                                                                                                                                                                                         | e at POR                                                                                                                                                                       | '1' = Bit                | is set         | '0' = Bit is | cleared      | x = Bit is ι | unknown   |  |  |  |  |

**Note:** For bits ACKEN, RCEN, PEN, RSEN, SEN: If the I<sup>2</sup>C module is not in the Idle mode, this bit may not be set (no spooling) and the SSPBUF may not be written (or writes to the SSPBUF are disabled).

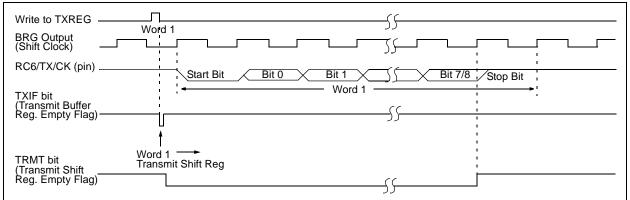

When setting up an Asynchronous Transmission, follow these steps:

- Initialize the SPBRG register for the appropriate baud rate. If a high-speed baud rate is desired, set bit BRGH (Section 10.1 "USART Baud Rate Generator (BRG)").

- 2. Enable the asynchronous serial port by clearing bit SYNC and setting bit SPEN.

- 3. If interrupts are desired, then set enable bit TXIE.

- 4. If 9-bit transmission is desired, then set transmit bit TX9.

- 5. Enable the transmission by setting bit TXEN, which will also set bit TXIF.

- 6. If 9-bit transmission is selected, the ninth bit should be loaded in bit TX9D.

- 7. Load data to the TXREG register (starts transmission).

- 8. If using interrupts, ensure that GIE and PEIE (bits 7 and 6) of the INTCON register are set.

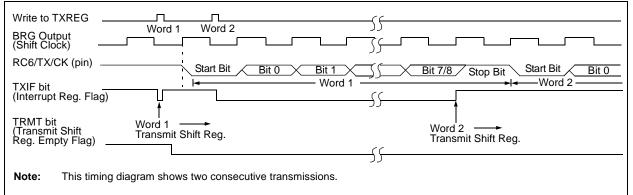

#### FIGURE 10-2: ASYNCHRONOUS MASTER TRANSMISSION

#### FIGURE 10-3: ASYNCHRONOUS MASTER TRANSMISSION (BACK TO BACK)

#### TABLE 10-5: REGISTERS ASSOCIATED WITH ASYNCHRONOUS TRANSMISSION

| Address                | Name   | Bit 7                              | Bit 6    | Bit 5  | Bit 4 | Bit 3    | Bit 2      | Bit 1       | Bit 0      | Value on:<br>POR, BOR | Value on<br>all other<br>Resets |

|------------------------|--------|------------------------------------|----------|--------|-------|----------|------------|-------------|------------|-----------------------|---------------------------------|

| 0Bh, 8Bh,<br>10Bh,18Bh | INTCON | GIE                                | PEIE     | TMR0IE | INTE  | RBIE     | TMR0IF     | INTF        | R0IF       | 0000 000x             | 0000 000u                       |

| 0Ch                    | PIR1   | PSPIF <sup>(1)</sup>               | ADIF     | RCIF   | TXIF  | SSPIF    | CCP1IF     | TMR2IF      | TMR1IF     | 0000 0000             | 0000 0000                       |

| 18h                    | RCSTA  | SPEN                               | RX9      | SREN   | CREN  |          | FERR       | OERR        | RX9D       | 0000 -00x             | 0000 -00x                       |

| 19h                    | TXREG  | USART Tra                          | nsmit Re | gister |       |          |            |             |            | 0000 0000             | 0000 0000                       |

| 8Ch                    | PIE1   | PSPIE <sup>(1)</sup>               | ADIE     | RCIE   | TXIE  | SSPIE    | CCP1IE     | TMR2IE      | TMR1IE     | 0000 0000             | 0000 0000                       |

| 98h                    | TXSTA  | CSRC                               | TX9      | TXEN   | SYNC  |          | BRGH       | TRMT        | TX9D       | 0000 -010             | 0000 -010                       |

| 99h                    | SPBRG  | SPBRG Baud Rate Generator Register |          |        |       |          |            |             |            |                       | 0000 0000                       |

| Legend:                |        |                                    |          | 0      |       | s '0' Sh | adad calls | are not use | d for asym | 0000 0000             |                                 |

Legend: x = unknown, - = unimplemented locations read as '0'. Shaded cells are not used for asynchronous transmission.

Note 1: Bits PSPIE and PSPIF are reserved on 28-pin devices; always maintain these bits clear.

### 14.10 Power Control/Status Register (PCON)

The Power Control/Status Register, PCON, has up to two bits depending upon the device.

Bit 0 is the Brown-out Reset Status bit, BOR. The BOR bit is unknown on a Power-on Reset. It must then be set by the user and checked on subsequent Resets to see if it has been cleared, indicating that a BOR has occurred.

When the Brown-out Reset is disabled, the state of the BOR bit is unpredictable and is, therefore, not valid at any time.

Bit 1 is the Power-on Reset Status bit,  $\overline{\text{POR}}$ . It is cleared on a Power-on Reset and unaffected otherwise. The user must set this bit following a Power-on Reset.

### TABLE 14-3: TIME-OUT IN VARIOUS SITUATIONS

| Oscillator Configuration | Power                                | -up | Brown-out         | Wake-up from |  |

|--------------------------|--------------------------------------|-----|-------------------|--------------|--|

|                          | <b>PWRTE = 0 PWRTE = </b> 2          |     | Brown-out         | Sleep        |  |

| XT, HS, LP               | ; HS, LP 72 ms + 1024 Tosc 1024 Tosc |     | 72 ms + 1024 Tosc | 1024 Tosc    |  |

| RC                       | 72 ms                                | —   | 72 ms             | —            |  |

#### TABLE 14-4: STATUS BITS AND THEIR SIGNIFICANCE

| POR | BOR | то | PD | Condition                                               |

|-----|-----|----|----|---------------------------------------------------------|

| 0   | x   | 1  | 1  | Power-on Reset                                          |

| 0   | x   | 0  | x  | Illegal, TO is set on POR                               |

| 0   | x   | x  | 0  | Illegal, PD is set on POR                               |

| 1   | 0   | 1  | 1  | Brown-out Reset                                         |

| 1   | 1   | 0  | 1  | WDT Reset                                               |

| 1   | 1   | 0  | 0  | WDT Wake-up                                             |

| 1   | 1   | u  | u  | MCLR Reset during normal operation                      |

| 1   | 1   | 1  | 0  | MCLR Reset during Sleep or Interrupt Wake-up from Sleep |

**Legend:** x = don't care, u = unchanged

#### TABLE 14-5: RESET CONDITIONS FOR SPECIAL REGISTERS

| Condition                          | Program<br>Counter    | Status<br>Register | PCON<br>Register |

|------------------------------------|-----------------------|--------------------|------------------|

| Power-on Reset                     | 000h                  | 0001 1xxx          | 0x               |

| MCLR Reset during normal operation | 000h                  | 000u uuuu          | uu               |

| MCLR Reset during Sleep            | 000h                  | 0001 0uuu          | uu               |

| WDT Reset                          | 000h                  | 0000 luuu          | uu               |

| WDT Wake-up                        | PC + 1                | uuu0 0uuu          | uu               |

| Brown-out Reset                    | 000h                  | 0001 luuu          | u0               |

| Interrupt Wake-up from Sleep       | PC + 1 <sup>(1)</sup> | uuul Ouuu          | uu               |

Legend: u = unchanged, x = unknown, - = unimplemented bit, read as '0'