Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                                           |

|----------------------------|---------------------------------------------------------------------------|

| Product Status             | Active                                                                    |

| Core Processor             | PIC                                                                       |

| Core Size                  | 8-Bit                                                                     |

| Speed                      | 10MHz                                                                     |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                         |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                     |

| Number of I/O              | 33                                                                        |

| Program Memory Size        | 14KB (8K x 14)                                                            |

| Program Memory Type        | FLASH                                                                     |

| EEPROM Size                | 256 x 8                                                                   |

| RAM Size                   | 368 x 8                                                                   |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 5.5V                                                                 |

| Data Converters            | A/D 8x10b                                                                 |

| Oscillator Type            | External                                                                  |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                         |

| Mounting Type              | Surface Mount                                                             |

| Package / Case             | 44-LCC (J-Lead)                                                           |

| Supplier Device Package    | 44-PLCC (16.59x16.59)                                                     |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16lf877a-i-l |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

PIC16F873A/876A PINOUT DESCRIPTION **TABLE 1-2:**

| Pin Name                                                | PDIP, SOIC,<br>SSOP Pin# | QFN<br>Pin# | I/O/P<br>Type               | Buffer<br>Type         | Description                                                                                                                                                                                                                                                         |

|---------------------------------------------------------|--------------------------|-------------|-----------------------------|------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| OSC1/CLKI<br>OSC1<br>CLKI                               | 9                        | 6           | 1                           | ST/CMOS <sup>(3)</sup> | Oscillator crystal or external clock input.  Oscillator crystal input or external clock source input. ST buffer when configured in RC mode; otherwise CMOS.  External clock source input. Always associated with pin function OSC1 (see OSC1/CLKI, OSC2/CLKO pins). |

| OSC2/CLKO<br>OSC2<br>CLKO                               | 10                       | 7           | 0                           | _                      | Oscillator crystal or clock output. Oscillator crystal output. Connects to crystal or resonator in Crystal Oscillator mode. In RC mode, OSC2 pin outputs CLKO, which has 1/4 the frequency of OSC1 and denotes the instruction cycle rate.                          |

| MCLR/VPP<br>MCLR<br>VPP                                 | 1                        | 26          | I<br>P                      | ST                     | Master Clear (input) or programming voltage (output).  Master Clear (Reset) input. This pin is an active low Reset to the device.  Programming voltage input.                                                                                                       |

| RA0/AN0<br>RA0<br>AN0                                   | 2                        | 27          | I/O<br>I                    | TTL                    | PORTA is a bidirectional I/O port.  Digital I/O.  Analog input 0.                                                                                                                                                                                                   |

| RA1/AN1<br>RA1<br>AN1                                   | 3                        | 28          | I/O<br>I                    | TTL                    | Digital I/O.<br>Analog input 1.                                                                                                                                                                                                                                     |

| RA2/AN2/VREF-/<br>CVREF<br>RA2<br>AN2<br>VREF-<br>CVREF | 4                        | 1           | I/O<br>I<br>I<br>O          | TTL                    | Digital I/O. Analog input 2. A/D reference voltage (Low) input. Comparator VREF output.                                                                                                                                                                             |

| RA3/AN3/VREF+<br>RA3<br>AN3<br>VREF+                    | 5                        | 2           | I/O<br> <br>                | TTL                    | Digital I/O.<br>Analog input 3.<br>A/D reference voltage (High) input.                                                                                                                                                                                              |

| RA4/T0CKI/C1OUT<br>RA4<br>T0CKI<br>C1OUT                | 6                        | 3           | I/O<br>I<br>O               | ST                     | Digital I/O – Open-drain when configured as output.<br>Timer0 external clock input.<br>Comparator 1 output.                                                                                                                                                         |

| RA5/AN4/SS/C2OUT<br>RA5<br>AN4<br>SS<br>C2OUT           | 7                        | 4           | I/O<br> <br> <br> <br> <br> | TTL                    | Digital I/O. Analog input 4. SPI slave select input. Comparator 2 output.                                                                                                                                                                                           |

**Legend:** I = input

O = output

I/O = input/output

P = power

— = Not used

TTL = TTL input

ST = Schmitt Trigger input

Note 1: This buffer is a Schmitt Trigger input when configured as the external interrupt.

2: This buffer is a Schmitt Trigger input when used in Serial Programming mode.

3: This buffer is a Schmitt Trigger input when configured in RC Oscillator mode and a CMOS input otherwise.

**TABLE 1-3:** PIC16F874A/877A PINOUT DESCRIPTION (CONTINUED)

| Pin Name                                 | PDIP<br>Pin# | PLCC<br>Pin# | TQFP<br>Pin# | QFN<br>Pin# | I/O/P<br>Type   | Buffer<br>Type | Description                                                                         |

|------------------------------------------|--------------|--------------|--------------|-------------|-----------------|----------------|-------------------------------------------------------------------------------------|

|                                          |              |              |              |             |                 |                | PORTC is a bidirectional I/O port.                                                  |

| RC0/T1OSO/T1CKI<br>RC0<br>T1OSO<br>T1CKI | 15           | 16           | 32           | 34          | I/O<br>O<br>I   | ST             | Digital I/O.<br>Timer1 oscillator output.<br>Timer1 external clock input.           |

| RC1/T1OSI/CCP2<br>RC1<br>T1OSI<br>CCP2   | 16           | 18           | 35           | 35          | I/O<br>I<br>I/O | ST             | Digital I/O. Timer1 oscillator input. Capture2 input, Compare2 output, PWM2 output. |

| RC2/CCP1<br>RC2<br>CCP1                  | 17           | 19           | 36           | 36          | I/O<br>I/O      | ST             | Digital I/O. Capture1 input, Compare1 output, PWM1 output.                          |

| RC3/SCK/SCL<br>RC3<br>SCK                | 18           | 20           | 37           | 37          | I/O<br>I/O      | ST             | Digital I/O. Synchronous serial clock input/output for SPI mode.                    |

| SCL                                      |              |              |              |             | I/O             |                | Synchronous serial clock input/output for I <sup>2</sup> C mode.                    |

| RC4/SDI/SDA<br>RC4<br>SDI<br>SDA         | 23           | 25           | 42           | 42          | I/O<br>I<br>I/O | ST             | Digital I/O.<br>SPI data in.<br>I <sup>2</sup> C data I/O.                          |

| RC5/SDO<br>RC5<br>SDO                    | 24           | 26           | 43           | 43          | I/O<br>O        | ST             | Digital I/O.<br>SPI data out.                                                       |

| RC6/TX/CK<br>RC6<br>TX<br>CK             | 25           | 27           | 44           | 44          | I/O<br>O<br>I/O | ST             | Digital I/O. USART asynchronous transmit. USART1 synchronous clock.                 |

| RC7/RX/DT<br>RC7<br>RX<br>DT             | 26           | 29           | 1            | 1           | I/O<br>I<br>I/O | ST             | Digital I/O. USART asynchronous receive. USART synchronous data.                    |

Legend:

I = input

O = output

I/O = input/output

P = power

— = Not used

TTL = TTL input ST = Schmitt Trigger input

Note 1: This buffer is a Schmitt Trigger input when configured as the external interrupt.

This buffer is a Schmitt Trigger input when used in Serial Programming mode.

This buffer is a Schmitt Trigger input when configured in RC Oscillator mode and a CMOS input otherwise.

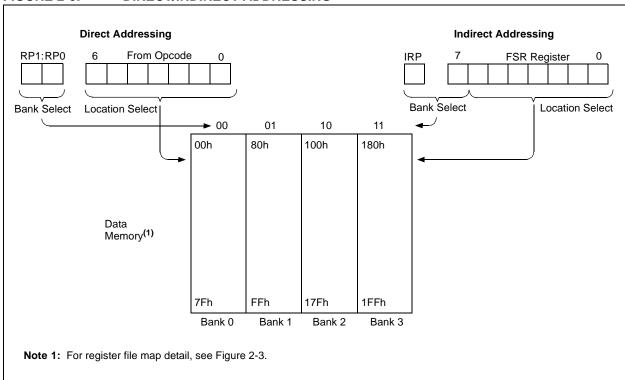

# 2.5 Indirect Addressing, INDF and FSR Registers

The INDF register is not a physical register. Addressing the INDF register will cause indirect addressing.

Indirect addressing is possible by using the INDF register. Any instruction using the INDF register actually accesses the register pointed to by the File Select Register, FSR. Reading the INDF register itself, indirectly (FSR = 0) will read 00h. Writing to the INDF register indirectly results in a no operation (although status bits may be affected). An effective 9-bit address is obtained by concatenating the 8-bit FSR register and the IRP bit (Status<7>) as shown in Figure 2-6.

A simple program to clear RAM locations 20h-2Fh using indirect addressing is shown in Example 2-2.

#### **EXAMPLE 2-2: INDIRECT ADDRESSING**

|          | MOVLW | 0x20  | ;initialize pointer  |

|----------|-------|-------|----------------------|

|          | MOVWF | FSR   | ;to RAM              |

| NEXT     | CLRF  | INDF  | clear INDF register; |

|          | INCF  | FSR,F | ;inc pointer         |

|          | BTFSS | FSR,4 | ;all done?           |

|          | GOTO  | NEXT  | ;no clear next       |

| CONTINUE |       |       |                      |

|          | :     |       | ;yes continue        |

FIGURE 2-6: DIRECT/INDIRECT ADDRESSING

## 5.2 Using Timer0 with an External Clock

When no prescaler is used, the external clock input is the same as the prescaler output. The synchronization of T0CKI with the internal phase clocks is accomplished by sampling the prescaler output on the Q2 and Q4 cycles of the internal phase clocks. Therefore, it is necessary for T0CKI to be high for at least 2 Tosc (and a small RC delay of 20 ns) and low for at least 2 Tosc (and a small RC delay of 20 ns). Refer to the electrical specification of the desired device.

#### 5.3 Prescaler

There is only one prescaler available which is mutually exclusively shared between the Timer0 module and the Watchdog Timer. A prescaler assignment for the

Timer0 module means that there is no prescaler for the Watchdog Timer and vice versa. This prescaler is not readable or writable (see Figure 5-1).

The PSA and PS2:PS0 bits (OPTION\_REG<3:0>) determine the prescaler assignment and prescale ratio.

When assigned to the Timer0 module, all instructions writing to the TMR0 register (e.g., CLRF1, MOVWF1, BSF1, x....etc.) will clear the prescaler. When assigned to WDT, a CLRWDT instruction will clear the prescaler along with the Watchdog Timer. The prescaler is not readable or writable.

**Note:** Writing to TMR0 when the prescaler is assigned to Timer0 will clear the prescaler count, but will not change the prescaler assignment.

#### REGISTER 5-1: OPTION REG REGISTER

| R/W-1 | R/W-1  | R/W-1 | R/W-1 | R/W-1 | R/W-1 | R/W-1 | R/W-1 |

|-------|--------|-------|-------|-------|-------|-------|-------|

| RBPU  | INTEDG | T0CS  | T0SE  | PSA   | PS2   | PS1   | PS0   |

| bit 7 |        |       |       |       |       |       | bit 0 |

bit 7 RBPU

bit 6 INTEDG

bit 5 TOCS: TMR0 Clock Source Select bit

1 = Transition on T0CKI pin

0 = Internal instruction cycle clock (CLKO)

bit 4 T0SE: TMR0 Source Edge Select bit

1 = Increment on high-to-low transition on TOCKI pin

0 = Increment on low-to-high transition on T0CKI pin

bit 3 **PSA**: Prescaler Assignment bit

1 = Prescaler is assigned to the WDT

0 = Prescaler is assigned to the Timer0 module

bit 2-0 **PS2:PS0**: Prescaler Rate Select bits

| Bit Value | TMR0 Rate | WDT Rate |

|-----------|-----------|----------|

| 000       | 1:2       | 1:1      |

| 001       | 1:4       | 1:2      |

| 010       | 1:8       | 1:4      |

| 011       | 1 : 16    | 1:8      |

| 100       | 1:32      | 1:16     |

| 101       | 1:64      | 1:32     |

| 110       | 1 : 128   | 1:64     |

| 111       | 1:256     | 1:128    |

|           |           |          |

### Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0' - n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

**Note:** To avoid an unintended device Reset, the instruction sequence shown in the PIC<sup>®</sup> Mid-Range MCU Family Reference Manual (DS33023) must be executed when changing the prescaler assignment from Timer0 to the WDT. This sequence must be followed even if the WDT is disabled.

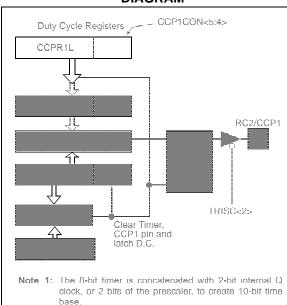

#### 8.3 PWM Mode (PWM)

In Pulse Width Modulation mode, the CCPx pin produces up to a 10-bit resolution PWM output. Since the CCP1 pin is multiplexed with the PORTC data latch, the TRISC<2> bit must be cleared to make the CCP1 pin an output.

Note: Clearing the CCP1CON register will force the CCP1 PWM output latch to the default low level. This is not the PORTC I/O data latch.

Figure 8-3 shows a simplified block diagram of the CCP module in PWM mode.

For a step-by-step procedure on how to set up the CCP module for PWM operation, see **Section 8.3.3 "Setup for PWM Operation"**.

### FIGURE 8-3: SIMPLIFIED PWM BLOCK DIAGRAM

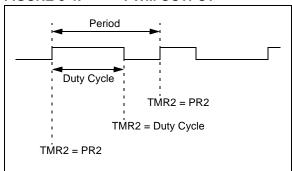

A PWM output (Figure 8-4) has a time base (period) and a time that the output stays high (duty cycle). The frequency of the PWM is the inverse of the period (1/period).

FIGURE 8-4: PWM OUTPUT

#### 8.3.1 PWM PERIOD

The PWM period is specified by writing to the PR2 register. The PWM period can be calculated using the following formula:

PWM frequency is defined as 1/[PWM period].

When TMR2 is equal to PR2, the following three events occur on the next increment cycle:

- TMR2 is cleared

- The CCP1 pin is set (exception: if PWM duty cycle = 0%, the CCP1 pin will not be set)

- The PWM duty cycle is latched from CCPR1L into CCPR1H

Note: The Timer2 postscaler (see Section 7.1 "Timer2 Prescaler and Postscaler") is not used in the determination of the PWM frequency. The postscaler could be used to have a servo update rate at a different frequency than the PWM output.

#### 8.3.2 PWM DUTY CYCLE

The PWM duty cycle is specified by writing to the CCPR1L register and to the CCP1CON<5:4> bits. Up to 10-bit resolution is available. The CCPR1L contains the eight MSbs and the CCP1CON<5:4> contains the two LSbs. This 10-bit value is represented by CCPR1L:CCP1CON<5:4>. The following equation is used to calculate the PWM duty cycle in time:

CCPR1L and CCP1CON<5:4> can be written to at any time, but the duty cycle value is not latched into CCPR1H until after a match between PR2 and TMR2 occurs (i.e., the period is complete). In PWM mode, CCPR1H is a read-only register.

The CCPR1H register and a 2-bit internal latch are used to double-buffer the PWM duty cycle. This double-buffering is essential for glitch-free PWM operation.

When the CCPR1H and 2-bit latch match TMR2, concatenated with an internal 2-bit Q clock or 2 bits of the TMR2 prescaler, the CCP1 pin is cleared.

The maximum PWM resolution (bits) for a given PWM frequency is given by the following formula.

#### **EQUATION 8-1:**

Resolution =

$$\frac{\log(\frac{Fosc}{FPWM})}{\log(2)}$$

bits

**Note:** If the PWM duty cycle value is longer than the PWM period, the CCP1 pin will not be cleared.

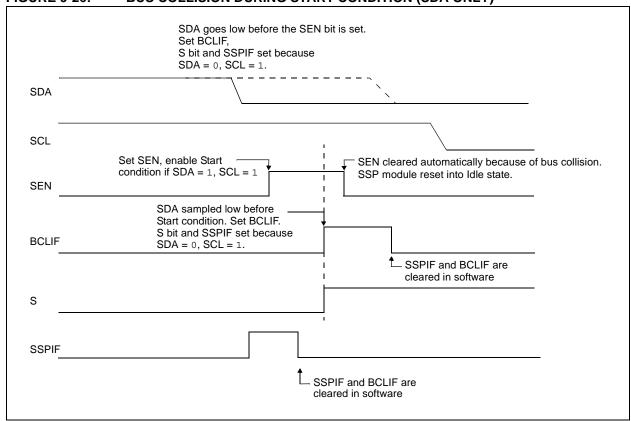

### 9.4.17.1 Bus Collision During a Start Condition

During a Start condition, a bus collision occurs if:

- a) SDA or SCL are sampled low at the beginning of the Start condition (Figure 9-26).

- b) SCL is sampled low before SDA is asserted low (Figure 9-27).

During a Start condition, both the SDA and the SCL pins are monitored.

If the SDA pin is already low, or the SCL pin is already low, then all of the following occur:

- the Start condition is aborted,

- · the BCLIF flag is set and

- the MSSP module is reset to its Idle state (Figure 9-26).

The Start condition begins with the SDA and SCL pins deasserted. When the SDA pin is sampled high, the Baud Rate Generator is loaded from SSPADD<6:0> and counts down to 0. If the SCL pin is sampled low while SDA is high, a bus collision occurs because it is assumed that another master is attempting to drive a data '1' during the Start condition.

If the SDA pin is sampled low during this count, the BRG is reset and the SDA line is asserted early (Figure 9-28). If, however, a '1' is sampled on the SDA pin, the SDA pin is asserted low at the end of the BRG count. The Baud Rate Generator is then reloaded and counts down to 0 and during this time, if the SCL pin is sampled as '0', a bus collision does not occur. At the end of the BRG count, the SCL pin is asserted low.

The reason that bus collision is not a factor during a Start condition is that no two bus masters can assert a Start condition at the exact same time. Therefore, one master will always assert SDA before the other. This condition does not cause a bus collision because the two masters must be allowed to arbitrate the first address following the Start condition. If the address is the same, arbitration must be allowed to continue into the data portion, Repeated Start or Stop conditions.

FIGURE 9-26: BUS COLLISION DURING START CONDITION (SDA ONLY)

**NOTES:**

TABLE 12-1: REGISTERS ASSOCIATED WITH COMPARATOR MODULE

| Address                | Name   | Bit 7        | Bit 6         | Bit 5   | Bit 4     | Bit 3      | Bit 2  | Bit 1  | Bit 0  | Value on POR | Value on<br>all other<br>Resets |

|------------------------|--------|--------------|---------------|---------|-----------|------------|--------|--------|--------|--------------|---------------------------------|

| 9Ch                    | CMCON  | C2OUT        | C1OUT         | C2INV   | C1INV     | CIS        | CM2    | CM1    | CM0    | 0000 0111    | 0000 0111                       |

| 9Dh                    | CVRCON | CVREN        | CVROE         | CVRR    | _         | CVR3       | CVR2   | CVR1   | CVR0   | 000- 0000    | 000- 0000                       |

| 0Bh, 8Bh,<br>10Bh,18Bh | INTCON | GIE/<br>GIEH | PEIE/<br>GIEL | TMR0IE  | INTIE     | RBIE       | TMR0IF | INTIF  | RBIF   | 0000 000x    | 0000 000u                       |

| 0Dh                    | PIR2   | _            | CMIF          | _       | _         | BCLIF      | LVDIF  | TMR3IF | CCP2IF | -0 0000      | -0 0000                         |

| 8Dh                    | PIE2   | _            | CMIE          | _       | _         | BCLIE      | LVDIE  | TMR3IE | CCP2IE | -0 0000      | -0 0000                         |

| 05h                    | PORTA  | _            | _             | RA5     | RA4       | RA3        | RA2    | RA1    | RA0    | 0x 0000      | 0u 0000                         |

| 85h                    | TRISA  | _            | _             | PORTA D | ata Direc | tion Regis | ster   |        |        | 11 1111      | 11 1111                         |

**Legend:** x = unknown, u = unchanged, - = unimplemented, read as '0'. Shaded cells are unused by the comparator module.

#### **RLF Rotate Left f through Carry** Syntax: [label] RLF f,d Operands: $0 \le f \le 127$ $d \in \left[0,1\right]$ Operation: See description below Status Affected: Description: The contents of register 'f' are rotated one bit to the left through the Carry flag. If 'd' is '0', the result is placed in the W register. If 'd' is '1', the result is stored back in register 'f'. Register f

#### **SLEEP** [label] SLEEP Syntax: Operands: None Operation: $00h \rightarrow WDT$ , $0 \rightarrow \underline{WDT}$ prescaler, $1 \rightarrow \overline{TO}$ $0 \rightarrow \overline{PD}$ TO. PD Status Affected: The power-down status bit, PD, Description: is cleared. Time-out status bit, TO, is set. Watchdog Timer and its prescaler are cleared. The processor is put into Sleep

| RETURN           | Return from Subroutine                                                                                                                         |

|------------------|------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [ label ] RETURN                                                                                                                               |

| Operands:        | None                                                                                                                                           |

| Operation:       | $TOS \rightarrow PC$                                                                                                                           |

| Status Affected: | None                                                                                                                                           |

| Description:     | Return from subroutine. The stack is POPed and the top of the stack (TOS) is loaded into the program counter. This is a two-cycle instruction. |

| RRF              | Rotate Right f through Carry                                                                                                                                                                           |

|------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [ label ] RRF f,d                                                                                                                                                                                      |

| Operands:        | $0 \le f \le 127$<br>$d \in [0,1]$                                                                                                                                                                     |

| Operation:       | See description below                                                                                                                                                                                  |

| Status Affected: | С                                                                                                                                                                                                      |

| Description:     | The contents of register 'f' are rotated one bit to the right through the Carry flag. If 'd' is '0', the result is placed in the W register. If 'd' is '1', the result is placed back in register 'f'. |

| sult is placed in the W register. |

|-----------------------------------|

| 'd' is '1', the result is placed  |

| ack in register 'f'.              |

| C Register f                      |

|                                   |

| SUBLW            | Subtract W from Literal                                                                                                      |

|------------------|------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [label] SUBLW k                                                                                                              |

| Operands:        | $0 \leq k \leq 255$                                                                                                          |

| Operation:       | $k - (W) \rightarrow (W)$                                                                                                    |

| Status Affected: | C, DC, Z                                                                                                                     |

| Description:     | The W register is subtracted (2's complement method) from the eight-bit literal 'k'. The result is placed in the W register. |

mode with the oscillator stopped.

| SUBWF               | Subtract W from f                                                                                                                                                               |

|---------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:             | [ label ] SUBWF f,d                                                                                                                                                             |

| Operands:           | $0 \le f \le 127$<br>$d \in [0,1]$                                                                                                                                              |

| Operation:          | (f) - (W) $\rightarrow$ (destination)                                                                                                                                           |

| Status<br>Affected: | C, DC, Z                                                                                                                                                                        |

| Description:        | Subtract (2's complement method) W register from register 'f'. If 'd' is '0', the result is stored in the W register. If 'd' is '1', the result is stored back in register 'f'. |

# 17.1 DC Characteristics: PIC16F873A/874A/876A/877A (Industrial, Extended) PIC16LF873A/874A/876A/877A (Industrial) (Continued)

| PIC16LF873A/874A/876A/877A<br>(Industrial)          |               |                                           |     | Standard Operating Conditions (unless otherwise stated)  Operating temperature -40°C ≤ TA ≤ +85°C for industrial                                                                                                                    |          |          |                                                                                                        |  |  |

|-----------------------------------------------------|---------------|-------------------------------------------|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|----------|--------------------------------------------------------------------------------------------------------|--|--|

| PIC16F873A/874A/876A/877A<br>(Industrial, Extended) |               |                                           |     | Standard Operating Conditions (unless otherwise stated)  Operating temperature $-40^{\circ}\text{C} \le \text{TA} \le +85^{\circ}\text{C}$ for industrial $-40^{\circ}\text{C} \le \text{TA} \le +125^{\circ}\text{C}$ for extended |          |          |                                                                                                        |  |  |

| Param<br>No.                                        | Symbol        | Characteristic/<br>Device                 | Min | Тур†                                                                                                                                                                                                                                | Max      | Units    | Conditions                                                                                             |  |  |

|                                                     | IPD           | Power-down Current <sup>(3,5)</sup>       |     |                                                                                                                                                                                                                                     |          |          |                                                                                                        |  |  |

| D020                                                |               | 16LF87XA                                  | _   | 7.5                                                                                                                                                                                                                                 | 30       | μА       | VDD = 3.0V, WDT enabled,<br>-40°C to +85°C                                                             |  |  |

| D020                                                |               | 16F87XA                                   | _   | 10.5                                                                                                                                                                                                                                | 42<br>60 | μΑ<br>μΑ | VDD = 4.0V, WDT enabled,<br>-40°C to +85°C<br>VDD = 4.0V, WDT enabled,<br>-40°C to +125°C (extended)   |  |  |

| D021                                                |               | 16LF87XA                                  | _   | 0.9                                                                                                                                                                                                                                 | 5        | μА       | VDD = 3.0V, WDT disabled,<br>0°C to +70°C                                                              |  |  |

| D021                                                |               | 16F87XA                                   | _   | 1.5                                                                                                                                                                                                                                 | 16<br>20 | μΑ<br>μΑ | VDD = 4.0V, WDT disabled,<br>-40°C to +85°C<br>VDD = 4.0V, WDT disabled,<br>-40°C to +125°C (extended) |  |  |

| D021A                                               |               | 16LF87XA                                  |     | 0.9                                                                                                                                                                                                                                 | 5        | μА       | VDD = 3.0V, WDT disabled,<br>-40°C to +85°C                                                            |  |  |

| D021A                                               |               | 16F87XA                                   |     | 1.5                                                                                                                                                                                                                                 | 19       | μА       | VDD = 4.0V, WDT disabled,<br>-40°C to +85°C                                                            |  |  |

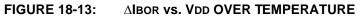

| D023                                                | $\Delta IBOR$ | Brown-out<br>Reset Current <sup>(6)</sup> | _   | 85                                                                                                                                                                                                                                  | 200      | μА       | BOR enabled, VDD = 5.0V                                                                                |  |  |

Legend: Rows with standard voltage device data only are shaded for improved readability.

- † Data in "Typ" column is at 5V, 25°C, unless otherwise stated. These parameters are for design guidance only and are not tested.

- **Note 1:** This is the limit to which VDD can be lowered without losing RAM data.

- 2: The supply current is mainly a function of the operating voltage and frequency. Other factors, such as I/O pin loading, switching rate, oscillator type, internal code execution pattern and temperature, also have an impact on the current consumption.

The test conditions for all IDD measurements in active operation mode are:

OSC1 = external square wave, from rail-to-rail; all I/O pins tri-stated, pulled to VDD; MCLR = VDD; WDT enabled/disabled as specified.

- 3: The power-down current in Sleep mode does not depend on the oscillator type. Power-down current is measured with the part in Sleep mode, with all I/O pins in high-impedance state and tied to VDD and Vss.

- **4:** For RC osc configuration, current through REXT is not included. The current through the resistor can be estimated by the formula Ir = VDD/2REXT (mA) with REXT in kΩ.

- 5: Timer1 oscillator (when enabled) adds approximately 20 μA to the specification. This value is from characterization and is for design guidance only. This is not tested.

- **6:** The  $\Delta$  current is the additional current consumed when this peripheral is enabled. This current should be added to the base IDD or IPD measurement.

- 7: When BOR is enabled, the device will operate correctly until the VBOR voltage trip point is reached.

**TABLE 17-9: SPI MODE REQUIREMENTS**

| Param<br>No. | Symbol                | Characteristic                                              | Min                                           | Тур†         | Max      | Units     | Conditions |  |

|--------------|-----------------------|-------------------------------------------------------------|-----------------------------------------------|--------------|----------|-----------|------------|--|

| 70*          | TssL2scH,<br>TssL2scL | SS ↓ to SCK ↓ or SCK ↑ Input                                | Tcy                                           |              | _        | ns        |            |  |

| 71*          | TscH                  | SCK Input High Time (Slave mode)                            |                                               | Tcy + 20     | _        | _         | ns         |  |

| 72*          | TscL                  | SCK Input Low Time (Slave mode)                             |                                               | Tcy + 20     | _        | _         | ns         |  |

| 73*          | TDIV2SCH,<br>TDIV2SCL | Setup Time of SDI Data Input to SCI                         | 100                                           | _            | _        | ns        |            |  |

| 74*          | TscH2DIL,<br>TscL2DIL | Hold Time of SDI Data Input to SCK                          | 100                                           | _            | _        | ns        |            |  |

| 75*          | TDOR                  | SDO Data Output Rise Time                                   | Standard( <b>F</b> )<br>Extended( <b>LF</b> ) | _<br>_       | 10<br>25 | 25<br>50  | ns<br>ns   |  |

| 76*          | TDOF                  | SDO Data Output Fall Time                                   | •                                             | _            | 10       | 25        | ns         |  |

| 77*          | TssH2DoZ              | SS ↑ to SDO Output High-Impedance                           | e                                             | 10           | _        | 50        | ns         |  |

| 78*          | TscR                  | SCK Output Rise Time Standard(F) (Master mode) Standard(LF) |                                               | _            | 10<br>25 | 25<br>50  | ns<br>ns   |  |

| 79*          | TscF                  | SCK Output Fall Time (Master mode                           | )                                             | _            | 10       | 25        | ns         |  |

| 80*          | TscH2DoV,<br>TscL2DoV | SDO Data Output Valid after<br>SCK Edge                     | Standard( <b>F</b> )<br>Extended( <b>LF</b> ) | _            |          | 50<br>145 | ns         |  |

| 81*          | TDOV2SCH,<br>TDOV2SCL | SDO Data Output Setup to SCK Edge                           |                                               | Tcy          | _        | _         | ns         |  |

| 82*          | TssL2DoV              | SDO Data Output Valid after SS ↓ Edge                       |                                               | _            | _        | 50        | ns         |  |

| 83*          | TscH2ssH,<br>TscL2ssH | SS ↑ after SCK Edge                                         |                                               | 1.5 Tcy + 40 | _        | _         | ns         |  |

These parameters are characterized but not tested.

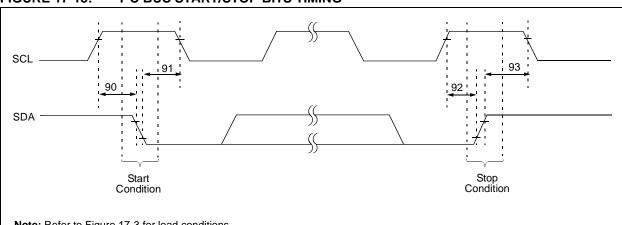

FIGURE 17-15: I<sup>2</sup>C BUS START/STOP BITS TIMING

Note: Refer to Figure 17-3 for load conditions.

Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

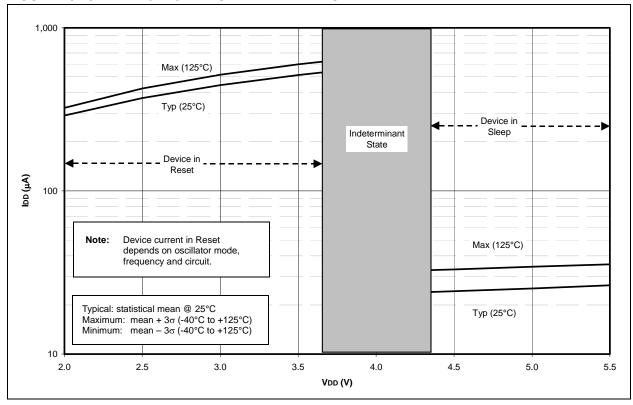

FIGURE 18-14: TYPICAL, MINIMUM AND MAXIMUM WDT PERIOD vs. VDD (-40°C TO +125°C)

#### 19.0 PACKAGING INFORMATION

### 19.1 Package Marking Information

#### 40-Lead PDIP

#### Example

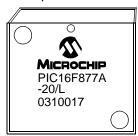

44-Lead TQFP

#### Example

#### 44-Lead PLCC

#### Example

**Legend:** XX...X Customer-specific information

Y Year code (last digit of calendar year)

YY Year code (last 2 digits of calendar year)

WW Week code (week of January 1 is week '01')

NNN Alphanumeric traceability code

(e3) Pb-free JEDEC designator for Matte Tin (Sn)

This package is Pb-free. The Pb-free JEDEC designator (@3)

can be found on the outer packaging for this package.

**Note**: In the event the full Microchip part number cannot be marked on one line, it will be carried over to the next line, thus limiting the number of available characters for customer-specific information.

### Package Marking Information (Cont'd)

44-Lead QFN

Example

28-Lead PDIP (Skinny DIP)

Example

28-Lead SOIC

Example

28-Lead SSOP

Example

28-Lead QFN

Example

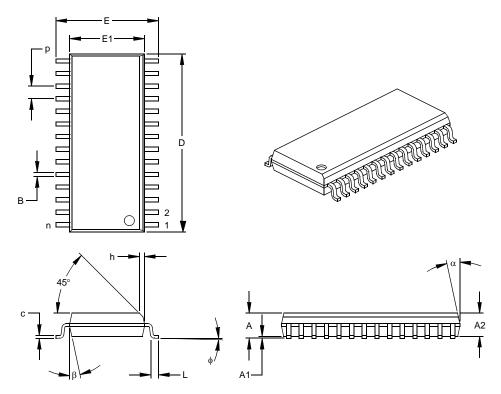

### 28-Lead Plastic Small Outline (SO) - Wide, 300 mil (SOIC)

Note: For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

|                          |    | INCHES* |      | MILLIMETERS |       |       |       |

|--------------------------|----|---------|------|-------------|-------|-------|-------|

| Dimension Limits         |    | MIN     | NOM  | MAX         | MIN   | NOM   | MAX   |

| Number of Pins           | n  |         | 28   |             |       | 28    |       |

| Pitch                    | р  |         | .050 |             |       | 1.27  |       |

| Overall Height           | Α  | .093    | .099 | .104        | 2.36  | 2.50  | 2.64  |

| Molded Package Thickness | A2 | .088    | .091 | .094        | 2.24  | 2.31  | 2.39  |

| Standoff §               | A1 | .004    | .008 | .012        | 0.10  | 0.20  | 0.30  |

| Overall Width            | Е  | .394    | .407 | .420        | 10.01 | 10.34 | 10.67 |

| Molded Package Width     | E1 | .288    | .295 | .299        | 7.32  | 7.49  | 7.59  |

| Overall Length           | D  | .695    | .704 | .712        | 17.65 | 17.87 | 18.08 |

| Chamfer Distance         | h  | .010    | .020 | .029        | 0.25  | 0.50  | 0.74  |

| Foot Length              | L  | .016    | .033 | .050        | 0.41  | 0.84  | 1.27  |

| Foot Angle Top           | ф  | 0       | 4    | 8           | 0     | 4     | 8     |

| Lead Thickness           | С  | .009    | .011 | .013        | 0.23  | 0.28  | 0.33  |

| Lead Width               | В  | .014    | .017 | .020        | 0.36  | 0.42  | 0.51  |

| Mold Draft Angle Top     | α  | 0       | 12   | 15          | 0     | 12    | 15    |

| Mold Draft Angle Bottom  | β  | 0       | 12   | 15          | 0     | 12    | 15    |

Dimensions D and E1 do not include mold flash or protrusions. Mold flash or protrusions shall not exceed .010" (0.254mm) per side.

JEDEC Equivalent: MS-013

Drawing No. C04-052

<sup>\*</sup> Controlling Parameter § Significant Characteristic

| Capture/Compare/PWM Requirements           |            | Data EEPROM Memory                                       |          |

|--------------------------------------------|------------|----------------------------------------------------------|----------|

| (CCP1 and CCP2)                            | 186        | Associated Registers                                     | 39       |

| CCP. See Capture/Compare/PWM.              |            | EEADR Register                                           | 33       |

| CCP1CON Register                           | 19         | EEADRH Register                                          | 33       |

| CCP2CON Register                           |            | EECON1 Register                                          |          |

| CCPR1H Register                            |            | EECON2 Register                                          |          |

| CCPR1L Register                            |            | Operation During Code-Protect                            |          |

| CCPR2H Register                            |            | Protection Against Spurious Writes                       |          |

| CCPR2L Register                            |            | Reading                                                  |          |

| CCPxM0 Bit                                 |            | Write Complete Flag Bit (EEIF)                           |          |

| CCPxM1 Bit                                 |            | Writing                                                  |          |

| CCPxM2 Bit                                 |            | · · · · · · · · · · · · · · · · · · ·                    |          |

| CCPxM3 Bit                                 |            | Data Memory                                              |          |

|                                            |            | Bank Select (RP1:RP0 Bits)                               |          |

| CCPxX Bit                                  |            | General Purpose Registers                                |          |

| CCPxY Bit                                  |            | Register File Map                                        |          |

| CLKO and I/O Timing Requirements           |            | Special Function Registers                               |          |

| CMCON Register                             | 20         | DC and AC Characteristics Graphs and Tables              |          |

| Code Examples                              |            | DC Characteristics1                                      | 75–179   |

| Call of a Subroutine in Page 1 from Page 0 |            | Demonstration Boards                                     |          |

| Indirect Addressing                        |            | PICDEM 1                                                 |          |

| Initializing PORTA                         |            | PICDEM 17                                                |          |

| Loading the SSPBUF (SSPSR) Register        |            | PICDEM 18R PIC18C601/801                                 |          |

| Reading Data EEPROM                        | 35         | PICDEM 2 Plus                                            | 170      |

| Reading Flash Program Memory               | 36         | PICDEM 3 PIC16C92X                                       | 170      |

| Saving Status, W and PCLATH Registers      |            | PICDEM 4                                                 | 170      |

| in RAM                                     | 154        | PICDEM LIN PIC16C43X                                     | 171      |

| Writing to Data EEPROM                     | 35         | PICDEM USB PIC16C7X5                                     | 171      |

| Writing to Flash Program Memory            |            | PICDEM.net Internet/Ethernet                             | 170      |

| Code Protection                            | . 143, 157 | Development Support                                      | 167      |

| Comparator Module                          | 135        | Device Differences                                       |          |

| Analog Input Connection                    |            | Device Overview                                          | 5        |

| Considerations                             | 139        | Direct Addressing                                        | 31       |

| Associated Registers                       |            | _                                                        |          |

| Configuration                              |            | E                                                        |          |

| Effects of a Reset                         |            | EEADR Register                                           | 21, 33   |

| Interrupts                                 |            | EEADRH Register                                          | 21. 33   |

| Operation                                  |            | EECON1 Register                                          |          |

| Operation During Sleep                     |            | EECON2 Register                                          |          |

| Outputs                                    |            | EEDATA Register                                          |          |

| Reference                                  |            | EEDATH Register                                          |          |

| Response Time                              |            | Electrical Characteristics                               |          |

| Comparator Specifications                  |            | Errata                                                   |          |

| Comparator Voltage Reference               |            | Evaluation and Programming Tools                         |          |

| Associated Registers                       |            | External Clock Timing Requirements                       |          |

| Computed GOTO                              |            | External Interrupt Input (RB0/INT). See Interrupt Source |          |

| •                                          |            | External Reference Signal                                |          |

| Configuration Bits                         |            | External Neterence Signal                                | 137      |

| Configuration Word                         |            | F                                                        |          |

| Conversion Considerations                  |            | Firmware Instructions                                    | 150      |

| CVRCON Register                            | 20         | Flash Program Memory                                     | 100      |

| D                                          |            | Associated Registers                                     | 30       |

|                                            |            | EECON1 Register                                          |          |

| Data EEPROM and Flash Program Memory       | 22         |                                                          |          |

| EEADR Register                             |            | EECON2 Register                                          |          |

| EEADRH Register                            |            | Reading                                                  |          |

| EECON1 Register                            |            | Writing                                                  |          |

| EECON2 Register                            |            | FSR Register19                                           | , ∠∪, 31 |

| EEDATA Register                            |            | G                                                        |          |

| EEDATH Register                            | 33         |                                                          |          |

|                                            |            | General Call Address Support                             | 94       |

### W

| Wake-up from Sleep               | 143, 156      |

|----------------------------------|---------------|

| Interrupts                       | 149, 150      |

| MCLR Reset                       |               |

| WDT Reset                        | 150           |

| Wake-up Using Interrupts         | 156           |

| Watchdog Timer                   |               |

| Register Summary                 | 155           |

| Watchdog Timer (WDT)             |               |

| Enable (WDTE Bit)                | 155           |

| Postscaler. See Postscaler, WDT. |               |

| Programming Considerations       |               |

| RC Oscillator                    | 155           |

| Time-out Period                  | 155           |

| WDT Reset, Normal Operation      | 147, 149, 150 |

| WDT Reset, Sleep                 | 147, 149, 150 |

| WCOL                             | 99, 101, 104  |

| WCOL Status Flag                 | 99            |

| WWW, On-Line Support             | 4             |

| P | IC1 | 6 | F۵ | 7) | ζΔ           |

|---|-----|---|----|----|--------------|

|   |     |   |    |    | $\mathbf{I}$ |