Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                                           |

|----------------------------|---------------------------------------------------------------------------|

| Product Status             | Active                                                                    |

| Core Processor             | PIC                                                                       |

| Core Size                  | 8-Bit                                                                     |

| Speed                      | 10MHz                                                                     |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                         |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                     |

| Number of I/O              | 33                                                                        |

| Program Memory Size        | 14KB (8K x 14)                                                            |

| Program Memory Type        | FLASH                                                                     |

| EEPROM Size                | 256 x 8                                                                   |

| RAM Size                   | 368 x 8                                                                   |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 5.5V                                                                 |

| Data Converters            | A/D 8x10b                                                                 |

| Oscillator Type            | External                                                                  |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                         |

| Mounting Type              | Through Hole                                                              |

| Package / Case             | 40-DIP (0.600", 15.24mm)                                                  |

| Supplier Device Package    | 40-PDIP                                                                   |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16lf877a-i-p |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

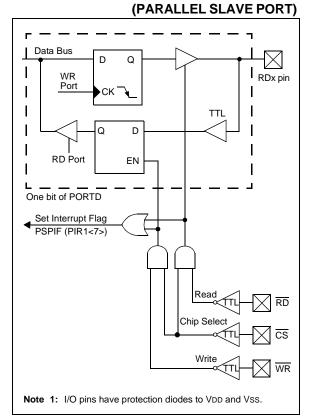

### 4.6 Parallel Slave Port

The Parallel Slave Port (PSP) is not implemented on the PIC16F873A or PIC16F876A.

PORTD operates as an 8-bit wide Parallel Slave Port, or microprocessor port, when control bit PSPMODE (TRISE<4>) is set. In Slave mode, it is asynchronously readable and writable by the external world through RD control input pin, RE0/RD/AN5, and WR control input pin, RE1/WR/AN6.

The PSP can directly interface to an 8-bit microprocessor data bus. The external microprocessor can read or write the PORTD latch as an 8-bit latch. Setting bit PSPMODE enables port pin RE0/RD/AN5 to be the RD input, RE1/WR/AN6 to be the WR input and RE2/CS/AN7 to be the CS (Chip Select) input. For this functionality, the corresponding data direction bits of the TRISE register (TRISE<2:0>) must be configured as inputs (set). The A/D port configuration bits, PCFG3:PCFG0 (ADCON1<3:0>), must be set to configure pins RE2:RE0 as digital I/O.

There are actually two 8-bit latches: one for data output and one for data input. The user writes 8-bit data to the PORTD data latch and reads data from the port pin latch (note that they have the same address). In this mode, the TRISD register is ignored since the external device is controlling the direction of data flow.

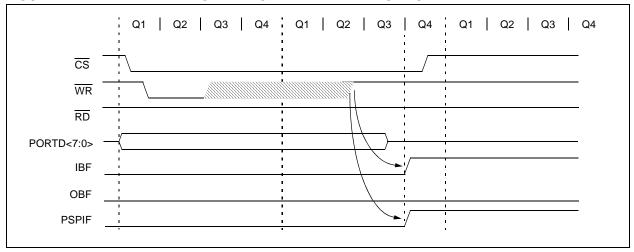

A write to the PSP occurs when both the  $\overline{\text{CS}}$  and  $\overline{\text{WR}}$  lines are first detected low. When either the  $\overline{\text{CS}}$  or  $\overline{\text{WR}}$  lines become high (level triggered), the Input Buffer Full (IBF) status flag bit (TRISE<7>) is set on the Q4 clock cycle, following the next Q2 cycle, to signal the write is complete (Figure 4-11). The interrupt flag bit, PSPIF (PIR1<7>), is also set on the same Q4 clock cycle. IBF can only be cleared by reading the PORTD input latch. The Input Buffer Overflow (IBOV) status flag bit (TRISE<5>) is set if a second write to the PSP is attempted when the previous byte has not been read out of the buffer.

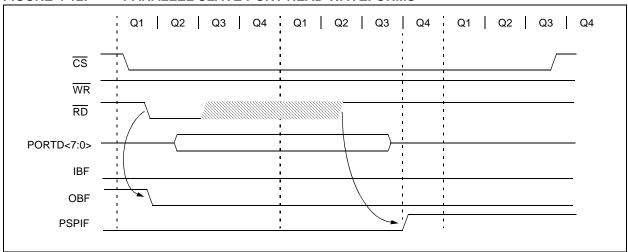

A read from the PSP occurs when both the  $\overline{\text{CS}}$  and  $\overline{\text{RD}}$  lines are first detected low. The Output Buffer Full (OBF) status flag bit (TRISE<6>) is cleared immediately (Figure 4-12), indicating that the PORTD latch is waiting to be read by the external bus. When either the  $\overline{\text{CS}}$  or  $\overline{\text{RD}}$  pin becomes high (level triggered), the interrupt flag bit PSPIF is set on the Q4 clock cycle, following the next Q2 cycle, indicating that the read is complete. OBF remains low until data is written to PORTD by the user firmware.

When not in PSP mode, the IBF and OBF bits are held clear. However, if flag bit IBOV was previously set, it must be cleared in firmware.

An interrupt is generated and latched into flag bit PSPIF when a read or write operation is completed. PSPIF must be cleared by the user in firmware and the interrupt can be disabled by clearing the interrupt enable bit PSPIE (PIE1<7>).

FIGURE 4-10: PORTD AND PORTE

BLOCK DIAGRAM

FIGURE 4-11: PARALLEL SLAVE PORT WRITE WAVEFORMS

FIGURE 4-12: PARALLEL SLAVE PORT READ WAVEFORMS

TABLE 4-11: REGISTERS ASSOCIATED WITH PARALLEL SLAVE PORT

| Address | Name   | Bit 7                | Bit 6                                             | Bit 5 | Bit 4   | Bit 3 | Bit 2   | Bit 1       | Bit 0   | Value on:<br>POR, BOR | Value on<br>all other<br>Resets |

|---------|--------|----------------------|---------------------------------------------------|-------|---------|-------|---------|-------------|---------|-----------------------|---------------------------------|

| 08h     | PORTD  | Port Data            | Port Data Latch when written; Port pins when read |       |         |       |         |             |         | xxxx xxxx             | uuuu uuuu                       |

| 09h     | PORTE  | _                    | _                                                 | _     | _       | _     | RE2     | RE1         | RE0     | xxx                   | uuu                             |

| 89h     | TRISE  | IBF                  | OBF                                               | IBOV  | PSPMODE | _     | PORTE D | ata Directi | on bits | 0000 -111             | 0000 -111                       |

| 0Ch     | PIR1   | PSPIF <sup>(1)</sup> | ADIF                                              | RCIF  | TXIF    | SSPIF | CCP1IF  | TMR2IF      | TMR1IF  | 0000 0000             | 0000 0000                       |

| 8Ch     | PIE1   | PSPIE <sup>(1)</sup> | ADIE                                              | RCIE  | TXIE    | SSPIE | CCP1IE  | TMR2IE      | TMR1IE  | 0000 0000             | 0000 0000                       |

| 9Fh     | ADCON1 | ADFM                 | ADCS2                                             |       | _       | PCFG3 | PCFG2   | PCFG1       | PCFG0   | 00 0000               | 00 0000                         |

**Legend:** x = unknown, u = unchanged, - = unimplemented, read as '0'. Shaded cells are not used by the Parallel Slave Port.

Note 1: Bits PSPIE and PSPIF are reserved on the PIC16F873A/876A; always maintain these bits clear.

### 6.0 TIMER1 MODULE

The Timer1 module is a 16-bit timer/counter consisting of two 8-bit registers (TMR1H and TMR1L) which are readable and writable. The TMR1 register pair (TMR1H:TMR1L) increments from 0000h to FFFFh and rolls over to 0000h. The TMR1 interrupt, if enabled, is generated on overflow which is latched in interrupt flag bit, TMR1IF (PIR1<0>). This interrupt can be enabled/disabled by setting/clearing TMR1 interrupt enable bit, TMR1IE (PIE1<0>).

Timer1 can operate in one of two modes:

- · As a Timer

- · As a Counter

The operating mode is determined by the clock select bit, TMR1CS (T1CON<1>).

In Timer mode, Timer1 increments every instruction cycle. In Counter mode, it increments on every rising edge of the external clock input.

Timer1 can be enabled/disabled by setting/clearing control bit, TMR1ON (T1CON<0>).

Timer1 also has an internal "Reset input". This Reset can be generated by either of the two CCP modules (Section 8.0 "Capture/Compare/PWM Modules"). Register 6-1 shows the Timer1 Control register.

When the Timer1 oscillator is enabled (T1OSCEN is set), the RC1/T1OSI/CCP2 and RC0/T1OSO/T1CKI pins become inputs. That is, the TRISC<1:0> value is ignored and these pins read as '0'.

Additional information on timer modules is available in the PIC<sup>®</sup> Mid-Range MCU Family Reference Manual (DS33023).

### REGISTER 6-1: T1CON: TIMER1 CONTROL REGISTER (ADDRESS 10h)

| U-0   | U-0 | R/W-0   | R/W-0   | R/W-0   | R/W-0  | R/W-0  | R/W-0  |

|-------|-----|---------|---------|---------|--------|--------|--------|

| _     | _   | T1CKPS1 | T1CKPS0 | T1OSCEN | T1SYNC | TMR1CS | TMR10N |

| bit 7 |     |         |         |         |        |        | bit 0  |

bit 7-6 Unimplemented: Read as '0'

bit 5-4 T1CKPS1:T1CKPS0: Timer1 Input Clock Prescale Select bits

11 = 1:8 prescale value

10 = 1:4 prescale value

01 = 1:2 prescale value

00 = 1:1 prescale value

bit 3 T10SCEN: Timer1 Oscillator Enable Control bit

1 = Oscillator is enabled

0 = Oscillator is shut-off (the oscillator inverter is turned off to eliminate power drain)

bit 2 T1SYNC: Timer1 External Clock Input Synchronization Control bit

When TMR1CS = 1:

1 = Do not synchronize external clock input

0 = Synchronize external clock input

When TMR1CS = 0:

This bit is ignored. Timer1 uses the internal clock when TMR1CS = 0.

bit 1 TMR1CS: Timer1 Clock Source Select bit

1 = External clock from pin RC0/T1OSO/T1CKI (on the rising edge)

0 = Internal clock (Fosc/4)

bit 0 TMR10N: Timer1 On bit

1 = Enables Timer1

0 = Stops Timer1

#### Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0' - n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

### 7.1 Timer2 Prescaler and Postscaler

The prescaler and postscaler counters are cleared when any of the following occurs:

- a write to the TMR2 register

- a write to the T2CON register

- any device Reset (POR, MCLR Reset, WDT Reset or BOR)

TMR2 is not cleared when T2CON is written.

# 7.2 Output of TMR2

The output of TMR2 (before the postscaler) is fed to the SSP module, which optionally uses it to generate the shift clock.

# TABLE 7-1: REGISTERS ASSOCIATED WITH TIMER2 AS A TIMER/COUNTER

| Address                 | Name                       | Bit 7                | Bit 6       | Bit 5   | Bit 4   | Bit 3   | Bit 2  | Bit 1   | Bit 0   | Value<br>POR, |      | Value<br>all o<br>Res | ther |

|-------------------------|----------------------------|----------------------|-------------|---------|---------|---------|--------|---------|---------|---------------|------|-----------------------|------|

| 0Bh, 8Bh,<br>10Bh, 18Bh | INTCON                     | GIE                  | PEIE        | TMR0IE  | INTE    | RBIE    | TMR0IF | INTF    | RBIF    | 0000          | 000x | 0000                  | 000u |

| 0Ch                     | PIR1                       | PSPIF <sup>(1)</sup> | ADIF        | RCIF    | TXIF    | SSPIF   | CCP1IF | TMR2IF  | TMR1IF  | 0000          | 0000 | 0000                  | 0000 |

| 8Ch                     | PIE1                       | PSPIE <sup>(1)</sup> | ADIE        | RCIE    | TXIE    | SSPIE   | CCP1IE | TMR2IE  | TMR1IE  | 0000          | 0000 | 0000                  | 0000 |

| 11h                     | TMR2                       | Timer2 M             | lodule's Re | gister  |         |         |        |         |         | 0000          | 0000 | 0000                  | 0000 |

| 12h                     | T2CON                      | _                    | TOUTPS3     | TOUTPS2 | TOUTPS1 | TOUTPS0 | TMR2ON | T2CKPS1 | T2CKPS0 | -000          | 0000 | -000                  | 0000 |

| 92h                     | PR2 Timer2 Period Register |                      |             |         |         |         |        |         |         | 1111          | 1111 | 1111                  | 1111 |

**Legend:** x = unknown, u = unchanged, - = unimplemented, read as '0'. Shaded cells are not used by the Timer2 module.

Note 1: Bits PSPIE and PSPIF are reserved on 28-pin devices; always maintain these bits clear.

### 9.3.8 SLEEP OPERATION

In Master mode, all module clocks are halted and the transmission/reception will remain in that state until the device wakes from Sleep. After the device returns to normal mode, the module will continue to transmit/receive data.

In Slave mode, the SPI Transmit/Receive Shift register operates asynchronously to the device. This allows the device to be placed in Sleep mode and data to be shifted into the SPI Transmit/Receive Shift register. When all 8 bits have been received, the MSSP interrupt flag bit will be set and if enabled, will wake the device from Sleep.

### 9.3.9 EFFECTS OF A RESET

A Reset disables the MSSP module and terminates the current transfer.

### 9.3.10 BUS MODE COMPATIBILITY

Table 9-1 shows the compatibility between the standard SPI modes and the states of the CKP and CKE control bits.

TABLE 9-1: SPI BUS MODES

| Standard SPI Mode | Control Bits State |     |  |  |

|-------------------|--------------------|-----|--|--|

| Terminology       | CKP                | CKE |  |  |

| 0, 0              | 0                  | 1   |  |  |

| 0, 1              | 0                  | 0   |  |  |

| 1, 0              | 1                  | 1   |  |  |

| 1, 1              | 1                  | 0   |  |  |

There is also a SMP bit which controls when the data is sampled.

TABLE 9-2: REGISTERS ASSOCIATED WITH SPI OPERATION

| Name    | Bit 7                         | Bit 6         | Bit 5            | Bit 4      | Bit 3       | Bit 2    | Bit 1  | Bit 0  |      | e on<br>BOR | all o | e on<br>other<br>sets |

|---------|-------------------------------|---------------|------------------|------------|-------------|----------|--------|--------|------|-------------|-------|-----------------------|

| INTCON  | GIE/<br>GIEH                  | PEIE/<br>GIEL | TMR0IE           | INT0IE     | RBIE        | TMR0IF   | INT0IF | RBIF   | 0000 | 000x        | 0000  | 000u                  |

| PIR1    | PSPIF <sup>(1)</sup>          | ADIF          | RCIF             | TXIF       | SSPIF       | CCP1IF   | TMR2IF | TMR1IF | 0000 | 0000        | 0000  | 0000                  |

| PIE1    | PSPIE <sup>(1)</sup>          | ADIE          | RCIE             | TXIE       | SSPIE       | CCP1IE   | TMR2IE | TMR1IE | 0000 | 0000        | 0000  | 0000                  |

| TRISC   | PORTC D                       | ata Direc     | tion Regis       | ter        |             |          |        |        | 1111 | 1111        | 1111  | 1111                  |

| SSPBUF  | Synchron                      | ous Seria     | l Port Rec       | eive Buffe | er/Transmit | Register |        |        | xxxx | xxxx        | uuuu  | uuuu                  |

| SSPCON  | WCOL                          | SSPOV         | SSPEN            | CKP        | SSPM3       | SSPM2    | SSPM1  | SSPM0  | 0000 | 0000        | 0000  | 0000                  |

| TRISA   | PORTA Data Direction Register |               |                  |            |             |          |        | 11     | 1111 | 11          | 1111  |                       |

| SSPSTAT | SMP                           | CKE           | $D/\overline{A}$ | Р          | S           | R/W      | UA     | BF     | 0000 | 0000        | 0000  | 0000                  |

**Legend:** x = unknown, u = unchanged, - = unimplemented, read as '0'. Shaded cells are not used by the MSSP in SPI mode.

Note 1: The PSPIF, PSPIE and PSPIP bits are reserved on 28-pin devices; always maintain these bits clear.

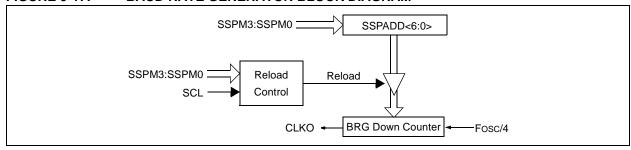

#### 9.4.7 BAUD RATE GENERATOR

In I<sup>2</sup>C Master mode, the Baud Rate Generator (BRG) reload value is placed in the lower 7 bits of the SSPADD register (Figure 9-17). When a write occurs to SSPBUF, the Baud Rate Generator will automatically begin counting. The BRG counts down to 0 and stops until another reload has taken place. The BRG count is decremented twice per instruction cycle (TcY) on the Q2 and Q4 clocks. In I<sup>2</sup>C Master mode, the BRG is reloaded automatically.

Once the given operation is complete (i.e., transmission of the last data bit is followed by  $\overline{ACK}$ ), the internal clock will automatically stop counting and the SCL pin will remain in its last state.

Table 9-3 demonstrates clock rates based on instruction cycles and the BRG value loaded into SSPADD.

FIGURE 9-17: BAUD RATE GENERATOR BLOCK DIAGRAM

TABLE 9-3: I<sup>2</sup>C CLOCK RATE W/BRG

| FcY    | Fcy*2  | BRG Value | FSCL<br>(2 Rollovers of BRG) |

|--------|--------|-----------|------------------------------|

| 10 MHz | 20 MHz | 19h       | 400 kHz <sup>(1)</sup>       |

| 10 MHz | 20 MHz | 20h       | 312.5 kHz                    |

| 10 MHz | 20 MHz | 3Fh       | 100 kHz                      |

| 4 MHz  | 8 MHz  | 0Ah       | 400 kHz <sup>(1)</sup>       |

| 4 MHz  | 8 MHz  | 0Dh       | 308 kHz                      |

| 4 MHz  | 8 MHz  | 28h       | 100 kHz                      |

| 1 MHz  | 2 MHz  | 03h       | 333 kHz <sup>(1)</sup>       |

| 1 MHz  | 2 MHz  | 0Ah       | 100 kHz                      |

| 1 MHz  | 2 MHz  | 00h       | 1 MHz <sup>(1)</sup>         |

**Note 1:** The I<sup>2</sup>C interface does not conform to the 400 kHz I<sup>2</sup>C specification (which applies to rates greater than 100 kHz) in all details, but may be used with care where higher rates are required by the application.

# 10.0 ADDRESSABLE UNIVERSAL SYNCHRONOUS ASYNCHRONOUS RECEIVER TRANSMITTER (USART)

The Universal Synchronous Asynchronous Receiver Transmitter (USART) module is one of the two serial I/O modules. (USART is also known as a Serial Communications Interface or SCI.) The USART can be configured as a full-duplex asynchronous system that can communicate with peripheral devices, such as CRT terminals and personal computers, or it can be configured as a half-duplex synchronous system that can communicate with peripheral devices, such as A/D or D/A integrated circuits, serial EEPROMs, etc.

The USART can be configured in the following modes:

- Asynchronous (full-duplex)

- Synchronous Master (half-duplex)

- Synchronous Slave (half-duplex)

Bit SPEN (RCSTA<7>) and bits TRISC<7:6> have to be set in order to configure pins RC6/TX/CK and RC7/RX/DT as the Universal Synchronous Asynchronous Receiver Transmitter.

The USART module also has a multi-processor communication capability using 9-bit address detection.

### REGISTER 10-1: TXSTA: TRANSMIT STATUS AND CONTROL REGISTER (ADDRESS 98h)

|   | R/W-0 | R/W-0 | R/W-0 | R/W-0 | U-0 | R/W-0 | R-1  | R/W-0 |

|---|-------|-------|-------|-------|-----|-------|------|-------|

|   | CSRC  | TX9   | TXEN  | SYNC  | _   | BRGH  | TRMT | TX9D  |

| b | oit 7 |       |       |       |     |       |      | bit 0 |

bit 7 CSRC: Clock Source Select bit

Asynchronous mode:

Don't care.

Synchronous mode:

- 1 = Master mode (clock generated internally from BRG)

- 0 = Slave mode (clock from external source)

- bit 6 **TX9**: 9-bit Transmit Enable bit

- 1 = Selects 9-bit transmission

- 0 = Selects 8-bit transmission

- bit 5 **TXEN**: Transmit Enable bit

- 1 = Transmit enabled

- 0 = Transmit disabled

Note: SREN/CREN overrides TXEN in Sync mode.

- bit 4 SYNC: USART Mode Select bit

- 1 = Synchronous mode

- 0 = Asynchronous mode

- bit 3 **Unimplemented:** Read as '0'

- bit 2 BRGH: High Baud Rate Select bit

Asynchronous mode:

- 1 = High speed

- 0 = Low speed

Synchronous mode:

Unused in this mode.

- bit 1 TRMT: Transmit Shift Register Status bit

- 1 = TSR empty

- 0 = TSR full

- bit 0 **TX9D:** 9th bit of Transmit Data, can be Parity bit

| _ |   |   |   |   |   |   |

|---|---|---|---|---|---|---|

|   | _ | ~ | Δ | n | ᆈ | ١ |

| ᆫ | е | u | е | n | u | ľ |

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

# 12.7 Comparator Operation During Sleep

When a comparator is active and the device is placed in Sleep mode, the comparator remains active and the interrupt is functional if enabled. This interrupt will wake-up the device from Sleep mode when enabled. While the comparator is powered up, higher Sleep currents than shown in the power-down current specification will occur. Each operational comparator will consume additional current as shown in the comparator specifications. To minimize power consumption while in Sleep mode, turn off the comparators, CM<2:0> = 111, before entering Sleep. If the device wakes up from Sleep, the contents of the CMCON register are not affected.

#### 12.8 Effects of a Reset

A device Reset forces the CMCON register to its Reset state, causing the comparator module to be in the Comparator Off mode, CM<2:0>=111. This ensures compatibility to the PIC16F87X devices.

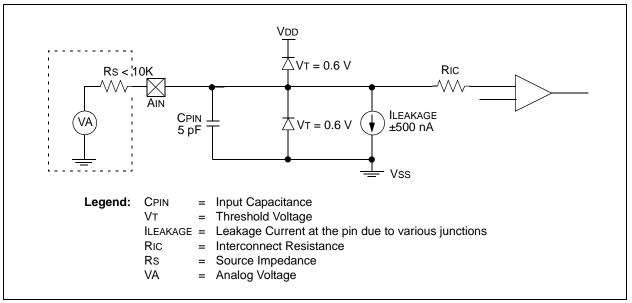

# 12.9 Analog Input Connection Considerations

A simplified circuit for an analog input is shown in Figure 12-4. Since the analog pins are connected to a digital output, they have reverse biased diodes to VDD and Vss. The analog input, therefore, must be between Vss and VDD. If the input voltage deviates from this range by more than 0.6V in either direction, one of the diodes is forward biased and a latch-up condition may occur. A maximum source impedance of 10  $k\Omega$  is recommended for the analog sources. Any external component connected to an analog input pin, such as a capacitor or a Zener diode, should have very little leakage current.

FIGURE 12-4: ANALOG INPUT MODEL

# 14.10 Power Control/Status Register (PCON)

The Power Control/Status Register, PCON, has up to two bits depending upon the device.

Bit 0 is the Brown-out Reset Status bit, BOR. The BOR bit is unknown on a Power-on Reset. It must then be set by the user and checked on subsequent Resets to see if it has been cleared, indicating that a BOR has occurred.

$\underline{\text{When}}$  the Brown-out Reset is disabled, the state of the  $\overline{\text{BOR}}$  bit is unpredictable and is, therefore, not valid at any time.

Bit 1 is the Power-on Reset Status bit, POR. It is cleared on a Power-on Reset and unaffected otherwise. The user must set this bit following a Power-on Reset

TABLE 14-3: TIME-OUT IN VARIOUS SITUATIONS

| Oscillator Configuration | Power             | Power-up<br>Brown-out |                   | Wake-up from |

|--------------------------|-------------------|-----------------------|-------------------|--------------|

| Oscillator Configuration | PWRTE = 0         | PWRTE = 1             | Brown-out         | Sleep        |

| XT, HS, LP               | 72 ms + 1024 Tosc | 1024 Tosc             | 72 ms + 1024 Tosc | 1024 Tosc    |

| RC                       | 72 ms             | _                     | 72 ms             | _            |

TABLE 14-4: STATUS BITS AND THEIR SIGNIFICANCE

| POR | BOR | ТО | PD | Condition                                               |  |  |  |

|-----|-----|----|----|---------------------------------------------------------|--|--|--|

| 0   | x   | 1  | 1  | Power-on Reset                                          |  |  |  |

| 0   | х   | 0  | х  | egal, TO is set on POR                                  |  |  |  |

| 0   | х   | х  | 0  | egal, PD is set on POR                                  |  |  |  |

| 1   | 0   | 1  | 1  | rown-out Reset                                          |  |  |  |

| 1   | 1   | 0  | 1  | /DT Reset                                               |  |  |  |

| 1   | 1   | 0  | 0  | WDT Wake-up                                             |  |  |  |

| 1   | 1   | u  | u  | MCLR Reset during normal operation                      |  |  |  |

| 1   | 1   | 1  | 0  | ICLR Reset during Sleep or Interrupt Wake-up from Sleep |  |  |  |

**Legend:** x = don't care, u = unchanged

TABLE 14-5: RESET CONDITIONS FOR SPECIAL REGISTERS

| Condition                          | Program<br>Counter    | Status<br>Register | PCON<br>Register |

|------------------------------------|-----------------------|--------------------|------------------|

| Power-on Reset                     | 000h                  | 0001 1xxx          | 0x               |

| MCLR Reset during normal operation | 000h                  | 000u uuuu          | uu               |

| MCLR Reset during Sleep            | 000h                  | 0001 0uuu          | uu               |

| WDT Reset                          | 000h                  | 0000 luuu          | uu               |

| WDT Wake-up                        | PC + 1                | uuu0 0uuu          | uu               |

| Brown-out Reset                    | 000h                  | 0001 1uuu          | u0               |

| Interrupt Wake-up from Sleep       | PC + 1 <sup>(1)</sup> | uuu1 0uuu          | uu               |

**Legend:** u = unchanged, x = unknown, - = unimplemented bit, read as '0'

**Note 1:** When the wake-up is due to an interrupt and the GIE bit is set, the PC is loaded with the interrupt vector (0004h).

TABLE 14-6: INITIALIZATION CONDITIONS FOR ALL REGISTERS (CONTINUED)

| Register | Devices |     | Power-on Reset,<br>Brown-out Reset | MCLR Resets,<br>WDT Reset | Wake-up via WDT or<br>Interrupt |           |           |  |

|----------|---------|-----|------------------------------------|---------------------------|---------------------------------|-----------|-----------|--|

| TRISD    | 73A     | 74A | 76A                                | 77A                       | 1111 1111                       | 1111 1111 | uuuu uuuu |  |

| TRISE    | 73A     | 74A | 76A                                | 77A                       | 0000 -111                       | 0000 -111 | uuuu -uuu |  |

| PIE1     | 73A     | 74A | 76A                                | 77A                       | r000 0000                       | r000 0000 | ruuu uuuu |  |

| FIET     | 73A     | 74A | 76A                                | 77A                       | 0000 0000                       | 0000 0000 | uuuu uuuu |  |

| PIE2     | 73A     | 74A | 76A                                | 77A                       | -0-0 00                         | -0-0 00   | -u-u uu   |  |

| PCON     | 73A     | 74A | 76A                                | 77A                       | qq                              | uu        | uu        |  |

| SSPCON2  | 73A     | 74A | 76A                                | 77A                       | 0000 0000                       | 0000 0000 | uuuu uuuu |  |

| PR2      | 73A     | 74A | 76A                                | 77A                       | 1111 1111                       | 1111 1111 | 1111 1111 |  |

| SSPADD   | 73A     | 74A | 76A                                | 77A                       | 0000 0000                       | 0000 0000 | uuuu uuuu |  |

| SSPSTAT  | 73A     | 74A | 76A                                | 77A                       | 00 0000                         | 00 0000   | uu uuuu   |  |

| TXSTA    | 73A     | 74A | 76A                                | 77A                       | 0000 -010                       | 0000 -010 | uuuu -uuu |  |

| SPBRG    | 73A     | 74A | 76A                                | 77A                       | 0000 0000                       | 0000 0000 | uuuu uuuu |  |

| CMCON    | 73A     | 974 | 76A                                | 77A                       | 0000 0111                       | 0000 0111 | uuuu uuuu |  |

| CVRCON   | 73A     | 74A | 76A                                | 77A                       | 000- 0000                       | 000- 0000 | uuu- uuuu |  |

| ADRESL   | 73A     | 74A | 76A                                | 77A                       | xxxx xxxx                       | uuuu uuuu | uuuu uuuu |  |

| ADCON1   | 73A     | 74A | 76A                                | 77A                       | 00 0000                         | 00 0000   | uu uuuu   |  |

| EEDATA   | 73A     | 74A | 76A                                | 77A                       | xxxx xxxx                       | uuuu uuuu | uuuu uuuu |  |

| EEADR    | 73A     | 74A | 76A                                | 77A                       | xxxx xxxx                       | uuuu uuuu | uuuu uuuu |  |

| EEDATH   | 73A     | 74A | 76A                                | 77A                       | xxxx xxxx                       | uuuu uuuu | uuuu uuuu |  |

| EEADRH   | 73A     | 74A | 76A                                | 77A                       | xxxx xxxx                       | uuuu uuuu | uuuu uuuu |  |

| EECON1   | 73A     | 74A | 76A                                | 77A                       | x x000                          | u u000    | u uuuu    |  |

| EECON2   | 73A     | 74A | 76A                                | 77A                       |                                 |           |           |  |

**Legend:** u = unchanged, x = unknown, - = unimplemented bit, read as '0', <math>q = value depends on condition, r = reserved, maintain clear. Shaded cells indicate conditions do not apply for the designated device.

- Note 1: One or more bits in INTCON, PIR1 and/or PIR2 will be affected (to cause wake-up).

- 2: When the wake-up is due to an interrupt and the GIE bit is set, the PC is loaded with the interrupt vector (0004h).

- 3: See Table 14-5 for Reset value for specific condition.

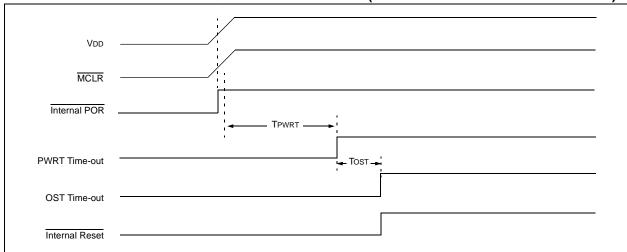

FIGURE 14-6: TIME-OUT SEQUENCE ON POWER-UP (MCLR TIED TO VDD VIA RC NETWORK)

| DECFSZ           | Decrement f, Skip if 0                                                                                                                                                                                                                                                                                       |

|------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [label] DECFSZ f,d                                                                                                                                                                                                                                                                                           |

| Operands:        | $0 \le f \le 127$<br>$d \in [0,1]$                                                                                                                                                                                                                                                                           |

| Operation:       | (f) - 1 $\rightarrow$ (destination);<br>skip if result = 0                                                                                                                                                                                                                                                   |

| Status Affected: | None                                                                                                                                                                                                                                                                                                         |

| Description:     | The contents of register 'f' are decremented. If 'd' is '0', the result is placed in the W register. If 'd' is '1', the result is placed back in register 'f'.  If the result is '1', the next instruction is executed. If the result is '0', then a NOP is executed instead, making it a 2 Tcy instruction. |

| INCFSZ           | Increment f, Skip if 0                                                                                                                                                                                                                                                                                  |

|------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [ label ] INCFSZ f,d                                                                                                                                                                                                                                                                                    |

| Operands:        | $0 \le f \le 127$<br>$d \in [0,1]$                                                                                                                                                                                                                                                                      |

| Operation:       | (f) + 1 $\rightarrow$ (destination),<br>skip if result = 0                                                                                                                                                                                                                                              |

| Status Affected: | None                                                                                                                                                                                                                                                                                                    |

| Description:     | The contents of register 'f' are incremented. If 'd' is '0', the result is placed in the W register. If 'd' is '1', the result is placed back in register 'f'.  If the result is '1', the next instruction is executed. If the result is '0', a NOP is executed instead, making it a 2 Tcy instruction. |

| GOTO             | Unconditional Branch                                                                                                                                                              |

|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [ label ] GOTO k                                                                                                                                                                  |

| Operands:        | $0 \leq k \leq 2047$                                                                                                                                                              |

| Operation:       | $k \rightarrow PC<10:0>$<br>PCLATH<4:3> $\rightarrow$ PC<12:11>                                                                                                                   |

| Status Affected: | None                                                                                                                                                                              |

| Description:     | GOTO is an unconditional branch. The eleven-bit immediate value is loaded into PC bits <10:0>. The upper bits of PC are loaded from PCLATH<4:3>. GOTO is a two-cycle instruction. |

| IORLW            | Inclusive OR Literal with W                                                                                      |

|------------------|------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [ label ] IORLW k                                                                                                |

| Operands:        | $0 \leq k \leq 255$                                                                                              |

| Operation:       | (W) .OR. $k \rightarrow (W)$                                                                                     |

| Status Affected: | Z                                                                                                                |

| Description:     | The contents of the W register are OR'ed with the eight-bit literal 'k'. The result is placed in the W register. |

| INCF             | Increment f                                                                                                                                                    |  |  |  |  |  |

|------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| Syntax:          | [ label ] INCF f,d                                                                                                                                             |  |  |  |  |  |

| Operands:        | $0 \le f \le 127$<br>$d \in [0,1]$                                                                                                                             |  |  |  |  |  |

| Operation:       | (f) + 1 $\rightarrow$ (destination)                                                                                                                            |  |  |  |  |  |

| Status Affected: | Z                                                                                                                                                              |  |  |  |  |  |

| Description:     | The contents of register 'f' are incremented. If 'd' is '0', the result is placed in the W register. If 'd' is '1', the result is placed back in register 'f'. |  |  |  |  |  |

| IORWF            | Inclusive OR W with f                                                                                                                                           |  |  |  |  |  |  |

|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

| Syntax:          | [ label ] IORWF f,d                                                                                                                                             |  |  |  |  |  |  |

| Operands:        | $0 \le f \le 127$<br>$d \in [0,1]$                                                                                                                              |  |  |  |  |  |  |

| Operation:       | (W) .OR. (f) $\rightarrow$ (destination)                                                                                                                        |  |  |  |  |  |  |

| Status Affected: | Z                                                                                                                                                               |  |  |  |  |  |  |

| Description:     | Inclusive OR the W register with register 'f'. If 'd' is '0', the result is placed in the W register. If 'd' is '1', the result is placed back in register 'f'. |  |  |  |  |  |  |

OSCI

CLKO

OSCI

TABLE 17-4: CLKO AND I/O TIMING REQUIREMENTS

| Param<br>No. | Symbol   | Characteristic                     | Min           | Тур† | Max | Units        | Conditions |          |

|--------------|----------|------------------------------------|---------------|------|-----|--------------|------------|----------|

| 10*          | TosH2ckL | OSC1 ↑ to CLKO ↓                   |               | _    | 75  | 200          | ns         | (Note 1) |

| 11*          | TosH2ckH | OSC1 ↑ to CLKO ↑                   |               | _    | 75  | 200          | ns         | (Note 1) |

| 12*          | TCKR     | CLKO Rise Time                     |               | _    | 35  | 100          | ns         | (Note 1) |

| 13*          | TCKF     | CLKO Fall Time                     |               | _    | 35  | 100          | ns         | (Note 1) |

| 14*          | TckL2ioV | CLKO ↓ to Port Out Valid           |               | _    | _   | 0.5 Tcy + 20 | ns         | (Note 1) |

| 15*          | TioV2ckH | Port In Valid before CLKO ↑        | Tosc + 200    | _    | _   | ns           | (Note 1)   |          |

| 16*          | TckH2iol | Port In Hold after CLKO ↑          | 0             | _    | _   | ns           | (Note 1)   |          |

| 17*          | TosH2IOV | OSC1 ↑ (Q1 cycle) to Port Out Va   | alid          | _    | 100 | 255          | ns         |          |

| 18*          | TosH2iol | OSC1 ↑ (Q2 cycle) to Port Input    | Standard (F)  | 100  | _   | _            | ns         |          |

|              |          | Invalid (I/O in hold time)         | Extended (LF) | 200  | _   | _            | ns         |          |

| 19*          | TioV2osH | Port Input Valid to OSC1 ↑ (I/O in | setup time)   | 0    | _   | _            | ns         |          |

| 20*          | TioR     | Port Output Rise Time              | Standard (F)  | _    | 10  | 40           | ns         |          |

|              |          |                                    | Extended (LF) | _    | _   | 145          | ns         |          |

| 21*          | TioF     | Port Output Fall Time              | Standard (F)  | _    | 10  | 40           | ns         |          |

|              |          |                                    | Extended (LF) | _    | _   | 145          | ns         |          |

| 22††*        | TINP     | INT pin High or Low Time           |               | Tcy  | _   | _            | ns         |          |

| 23††*        | TRBP     | RB7:RB4 Change INT High or Lo      | w Time        | Tcy  | _   | _            | ns         |          |

<sup>\*</sup> These parameters are characterized but not tested.

Note 1: Measurements are taken in RC mode where CLKO output is 4 x Tosc.

<sup>†</sup> Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

<sup>††</sup> These parameters are asynchronous events not related to any internal clock edges.

TABLE 17-11: I<sup>2</sup>C BUS DATA REQUIREMENTS

| Param<br>No. | Sym        | Characte                      | Min          | Max         | Units | Conditions |                                         |

|--------------|------------|-------------------------------|--------------|-------------|-------|------------|-----------------------------------------|

| 100          | THIGH      | Clock High Time               | 100 kHz mode | 4.0         | _     | μS         |                                         |

|              |            |                               | 400 kHz mode | 0.6         | _     | μS         |                                         |

|              |            |                               | SSP Module   | 0.5 Tcy     | _     |            |                                         |

| 101          | TLOW       | Clock Low Time                | 100 kHz mode | 4.7         | _     | μS         |                                         |

|              |            |                               | 400 kHz mode | 1.3         | _     | μS         |                                         |

|              |            |                               | SSP Module   | 0.5 Tcy     | _     |            |                                         |

| 102          | TR         | SDA and SCL Rise              | 100 kHz mode | _           | 1000  | ns         |                                         |

|              |            | Time                          | 400 kHz mode | 20 + 0.1 CB | 300   | ns         | Cb is specified to be from 10 to 400 pF |

| 103          | 03 TF      | SDA and SCL Fall              | 100 kHz mode | _           | 300   | ns         |                                         |

|              |            | Time                          | 400 kHz mode | 20 + 0.1 CB | 300   | ns         | CB is specified to be from 10 to 400 pF |

| 90           | Tsu:sta St | Start Condition Setup<br>Time | 100 kHz mode | 4.7         | _     | μS         | Only relevant for Repeated Start        |

|              |            |                               | 400 kHz mode | 0.6         | _     | μS         | condition                               |

| 91           | THD:STA    | Start Condition Hold          | 100 kHz mode | 4.0         | _     | μS         | After this period, the first clock      |

|              |            | Time                          | 400 kHz mode | 0.6         | _     | μS         | pulse is generated                      |

| 106          | THD:DAT    | Data Input Hold Time          | 100 kHz mode | 0           | _     | ns         |                                         |

|              |            |                               | 400 kHz mode | 0           | 0.9   | μS         |                                         |

| 107          | TSU:DAT    | Data Input Setup Time         | 100 kHz mode | 250         | _     | ns         | (Note 2)                                |

|              |            |                               | 400 kHz mode | 100         |       | ns         |                                         |

| 92           | Tsu:sto    | Stop Condition Setup          | 100 kHz mode | 4.7         |       | μS         |                                         |

|              |            | Time                          | 400 kHz mode | 0.6         |       | μS         |                                         |

| 109          | TAA        | Output Valid from             | 100 kHz mode | _           | 3500  | ns         | (Note 1)                                |

|              |            | Clock                         | 400 kHz mode | _           | _     | ns         |                                         |

| 110          | TBUF       | Bus Free Time                 | 100 kHz mode | 4.7         | _     | μS         | Time the bus must be free before        |

|              |            |                               | 400 kHz mode | 1.3         | _     | μS         | a new transmission can start            |

|              | Св         | Bus Capacitive Loading        | <u> </u>     | _           | 400   | pF         |                                         |

Note 1: As a transmitter, the device must provide this internal minimum delay time to bridge the undefined region (min. 300 ns) of the falling edge of SCL to avoid unintended generation of Start or Stop conditions.

<sup>2:</sup> A fast mode (400 kHz) I²C bus device can be used in a standard mode (100 kHz) I²C bus system, but the requirement that, Tsu:DAT ≥ 250 ns, must then be met. This will automatically be the case if the device does not stretch the LOW period of the SCL signal. If such a device does stretch the LOW period of the SCL signal, it must output the next data bit to the SDA line, TR MAX. + Tsu:DAT = 1000 + 250 = 1250 ns (according to the standard mode I²C bus specification), before the SCL line is released.

### 19.0 PACKAGING INFORMATION

## 19.1 Package Marking Information

#### 40-Lead PDIP

### Example

44-Lead TQFP

### Example

### 44-Lead PLCC

### Example

**Legend:** XX...X Customer-specific information

Y Year code (last digit of calendar year)

YY Year code (last 2 digits of calendar year)

WW Week code (week of January 1 is week '01')

NNN Alphanumeric traceability code

(e3) Pb-free JEDEC designator for Matte Tin (Sn)

This package is Pb-free. The Pb-free JEDEC designator (@3)

can be found on the outer packaging for this package.

**Note**: In the event the full Microchip part number cannot be marked on one line, it will be carried over to the next line, thus limiting the number of available characters for customer-specific information.

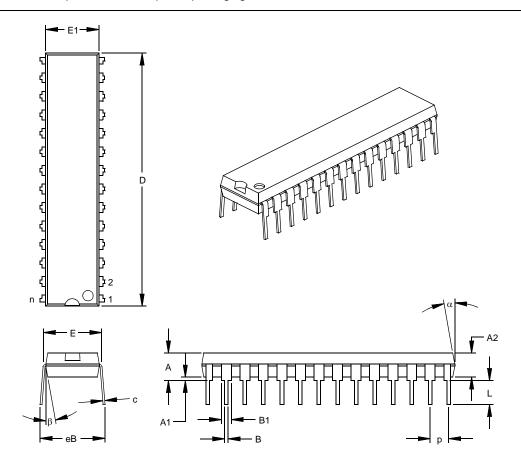

# 28-Lead Skinny Plastic Dual In-line (SP) - 300 mil (PDIP)

Note:

For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

|                            |        | INCHES* |       |       | MILLIMETERS |       |       |

|----------------------------|--------|---------|-------|-------|-------------|-------|-------|

| Dimension                  | Limits | MIN     | NOM   | MAX   | MIN         | NOM   | MAX   |

| Number of Pins             | n      |         | 28    |       |             | 28    |       |

| Pitch                      | р      |         | .100  |       |             | 2.54  |       |

| Top to Seating Plane       | Α      | .140    | .150  | .160  | 3.56        | 3.81  | 4.06  |

| Molded Package Thickness   | A2     | .125    | .130  | .135  | 3.18        | 3.30  | 3.43  |

| Base to Seating Plane      | A1     | .015    |       |       | 0.38        |       |       |

| Shoulder to Shoulder Width | Е      | .300    | .310  | .325  | 7.62        | 7.87  | 8.26  |

| Molded Package Width       | E1     | .275    | .285  | .295  | 6.99        | 7.24  | 7.49  |

| Overall Length             | D      | 1.345   | 1.365 | 1.385 | 34.16       | 34.67 | 35.18 |

| Tip to Seating Plane       | L      | .125    | .130  | .135  | 3.18        | 3.30  | 3.43  |

| Lead Thickness             | С      | .008    | .012  | .015  | 0.20        | 0.29  | 0.38  |

| Upper Lead Width           | B1     | .040    | .053  | .065  | 1.02        | 1.33  | 1.65  |

| Lower Lead Width           | В      | .016    | .019  | .022  | 0.41        | 0.48  | 0.56  |

| Overall Row Spacing §      | eВ     | .320    | .350  | .430  | 8.13        | 8.89  | 10.92 |

| Mold Draft Angle Top       | α      | 5       | 10    | 15    | 5           | 10    | 15    |

| Mold Draft Angle Bottom    | β      | 5       | 10    | 15    | 5           | 10    | 15    |

Dimension D and E1 do not include mold flash or protrusions. Mold flash or protrusions shall not exceed

.010" (0.254mm) per side. JEDEC Equivalent: MO-095

Drawing No. C04-070

<sup>\*</sup> Controlling Parameter § Significant Characteristic

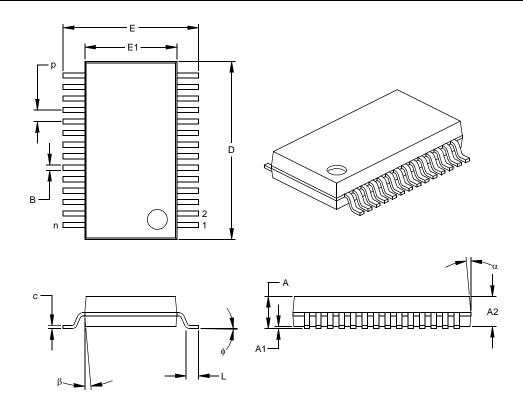

# 28-Lead Plastic Shrink Small Outline (SS) - 209 mil, 5.30 mm (SSOP)

For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

|                          | INCHES |      |      | MILLIMETERS* |       |        |        |

|--------------------------|--------|------|------|--------------|-------|--------|--------|

| Dimension                | Limits | MIN  | NOM  | MAX          | MIN   | NOM    | MAX    |

| Number of Pins           | n      |      | 28   |              |       | 28     |        |

| Pitch                    | р      |      | .026 |              |       | 0.65   |        |

| Overall Height           | Α      | .068 | .073 | .078         | 1.73  | 1.85   | 1.98   |

| Molded Package Thickness | A2     | .064 | .068 | .072         | 1.63  | 1.73   | 1.83   |

| Standoff §               | A1     | .002 | .006 | .010         | 0.05  | 0.15   | 0.25   |

| Overall Width            | Е      | .299 | .309 | .319         | 7.59  | 7.85   | 8.10   |

| Molded Package Width     | E1     | .201 | .207 | .212         | 5.11  | 5.25   | 5.38   |

| Overall Length           | D      | .396 | .402 | .407         | 10.06 | 10.20  | 10.34  |

| Foot Length              | L      | .022 | .030 | .037         | 0.56  | 0.75   | 0.94   |

| Lead Thickness           | С      | .004 | .007 | .010         | 0.10  | 0.18   | 0.25   |

| Foot Angle               | ф      | 0    | 4    | 8            | 0.00  | 101.60 | 203.20 |

| Lead Width               | В      | .010 | .013 | .015         | 0.25  | 0.32   | 0.38   |

| Mold Draft Angle Top     | α      | 0    | 5    | 10           | 0     | 5      | 10     |

| Mold Draft Angle Bottom  | β      | 0    | 5    | 10           | 0     | 5      | 10     |

#### Notes:

Dimensions D and E1 do not include mold flash or protrusions. Mold flash or protrusions shall not exceed

.010" (0.254mm) per side.

JEDEC Equivalent: MS-150

Drawing No. C04-073

<sup>\*</sup> Controlling Parameter § Significant Characteristic

| Power-up Timer (PWRT)148                         | RE0/RD/AN5 Pin                                    |     |

|--------------------------------------------------|---------------------------------------------------|-----|

| PR2 Register 20, 61                              | RE1/WR/AN6 Pin                                    | 13  |

| Prescaler, Timer0                                | RE2/CS/AN7 Pin                                    | 13  |

| Assignment (PSA Bit)23                           | Read-Modify-Write Operations 1                    | 59  |

| Rate Select (PS2:PS0 Bits)23                     | Register File                                     | 16  |

| PRO MATE II Universal Device Programmer169       | Register File Map (PIC16F873A/874A)               |     |

| Program Counter                                  | Register File Map (PIC16F876A/877A)               |     |

| Reset Conditions149                              | Registers                                         |     |

| Program Memory15                                 | ADCON0 (A/D Control 0) 1                          | 27  |

| Interrupt Vector                                 | ADCON1 (A/D Control 1) 1                          |     |

| Paging                                           | CCP1CON/CCP2CON (CCP Control 1                    |     |

| Program Memory Map and Stack                     | and CCP Control 2)                                | 64  |

| (PIC16F873A/874A)15                              | CMCON (Comparator Control)                        |     |

| Program Memory Map and Stack                     | CVRCON (Comparator Voltage                        | 00  |

| (PIC16F876A/877A)15                              | Reference Control)1                               | 11  |

| Reset Vector                                     | EECON1 (EEPROM Control 1)                         |     |

| Program Verification                             | FSR                                               |     |

|                                                  | INTCON                                            |     |

| Programming Pin (VPP)                            |                                                   |     |

|                                                  | OPTION_REG23,                                     |     |

| PSP. See Parallel Slave Port.                    | PCON (Power Control)                              |     |

| Pulse Width Modulation. See Capture/Compare/PWM, | PIE1 (Peripheral Interrupt Enable 1)              |     |

| PWM Mode.                                        | PIE2 (Peripheral Interrupt Enable 2)              |     |

| PUSH30                                           | PIR1 (Peripheral Interrupt Request 1)             |     |

| R                                                | PIR2 (Peripheral Interrupt Request 2)             |     |

|                                                  | RCSTA (Receive Status and Control)                |     |

| RAO/ANO Pin                                      | Special Function, Summary                         |     |

| RA1/AN1 Pin                                      | SSPCON (MSSP Control 1, I <sup>2</sup> C Mode)    |     |

| RA2/AN2/VREF-/CVREF Pin                          | SSPCON (MSSP Control 1, SPI Mode)                 |     |

| RA3/AN3/VREF+ Pin                                | SSPCON2 (MSSP Control 2, I <sup>2</sup> C Mode)   |     |

| RA4/T0CKI/C1OUT Pin                              | SSPSTAT (MSSP Status, I <sup>2</sup> C Mode)      |     |

| RA5/AN4/SS/C2OUT Pin                             | SSPSTAT (MSSP Status, SPI Mode)                   |     |

| RAM. See Data Memory.                            | Status                                            |     |

| RB0/INT Pin                                      | T1CON (Timer1 Control)                            |     |

| RB1 Pin                                          | T2CON (Timer2 Control)                            |     |

| RB2 Pin                                          | TRISE Register                                    |     |

| RB3/PGM Pin                                      | TXSTA (Transmit Status and Control) 1             |     |

| RB4 Pin                                          | Reset143, 1                                       |     |

| RB5 Pin                                          | Brown-out Reset (BOR). See Brown-out Reset (BOR)  | ).  |

| RB6/PGC Pin                                      | MCLR Reset. See MCLR.                             |     |

| RB7/PGD Pin                                      | Power-on Reset (POR). See Power-on Reset (POR).   |     |

| RC0/T10S0/T1CKI Pin                              | Reset Conditions for PCON Register 1              |     |

| RC1/T1OSI/CCP2 Pin                               | Reset Conditions for Program Counter 1            | 49  |

| RC2/CCP1 Pin                                     | Reset Conditions for Status Register 1            | 49  |

| RC3/SCK/SCL Pin                                  | WDT Reset. See Watchdog Timer (WDT).              |     |

| RC4/SDI/SDA Pin                                  | Reset, Watchdog Timer, Oscillator Start-up Timer, |     |

| RC5/SDO Pin                                      | Power-up Timer and Brown-out Reset                |     |

| RC6/TX/CK Pin                                    | Requirements1                                     | 84  |

| RC7/RX/DT Pin                                    | Revision History 2                                | 219 |

| RCREG Register19                                 | •                                                 |     |

| RCSTA Register19                                 | \$                                                |     |

| ADDEN Bit112                                     | SCI. See USART.                                   |     |

| CREN Bit112                                      | SCK                                               | 71  |

| FERR Bit112                                      | SDI                                               | 71  |

| OERR Bit112                                      | SDO                                               | 71  |

| RX9 Bit112                                       | Serial Clock, SCK                                 | 71  |

| RX9D Bit112                                      | Serial Communication Interface. See USART.        |     |

| SPEN Bit111, 112                                 | Serial Data In, SDI                               | 71  |

| SREN Bit112                                      | Serial Data Out, SDO                              |     |

| RD0/PSP0 Pin                                     | Serial Peripheral Interface. See SPI.             |     |

| RD1/PSP1 Pin                                     | Slave Select Synchronization                      | 77  |

| RD2/PSP2 Pin                                     | Slave Select, SS                                  |     |

| RD3/PSP3 Pin                                     | Sleep143, 147, 1                                  |     |

| RD4/PSP4 Pin                                     | Software Simulator (MPLAB SIM)                    |     |

| RD5/PSP5 Pin                                     | Software Simulator (MPLAB SIM30)                  | 68  |

| RD6/PSP6 Pin                                     | SPBRG Register                                    |     |

| RD7/PSP7 Pin                                     | Special Features of the CPU                       |     |

|                                                  |                                                   |     |

| I <sup>2</sup> C Bus Data191                                  | TDICD Domintor                             | 20  |

|---------------------------------------------------------------|--------------------------------------------|-----|

|                                                               | TRISB Register                             |     |

| I <sup>2</sup> C Bus Start/Stop Bits                          | TRISC Register                             |     |

| I <sup>2</sup> C Master Mode (Reception, 7-bit Address) 103   | TRISD Register                             |     |

| I <sup>2</sup> C Master Mode (Transmission,                   | TRISE Register                             |     |

| 7 or 10-bit Address)102                                       | IBF Bit                                    | 50  |

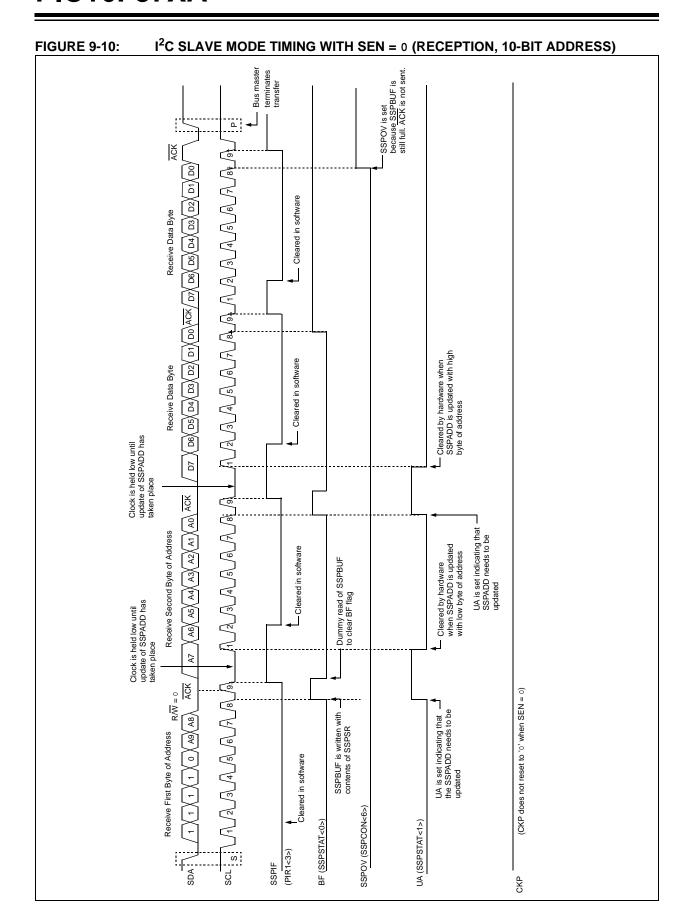

| I <sup>2</sup> C Slave Mode (Transmission, 10-bit Address) 89 | IBOV Bit                                   | 50  |

| I <sup>2</sup> C Slave Mode (Transmission, 7-bit Address) 87  | OBF Bit                                    | 50  |

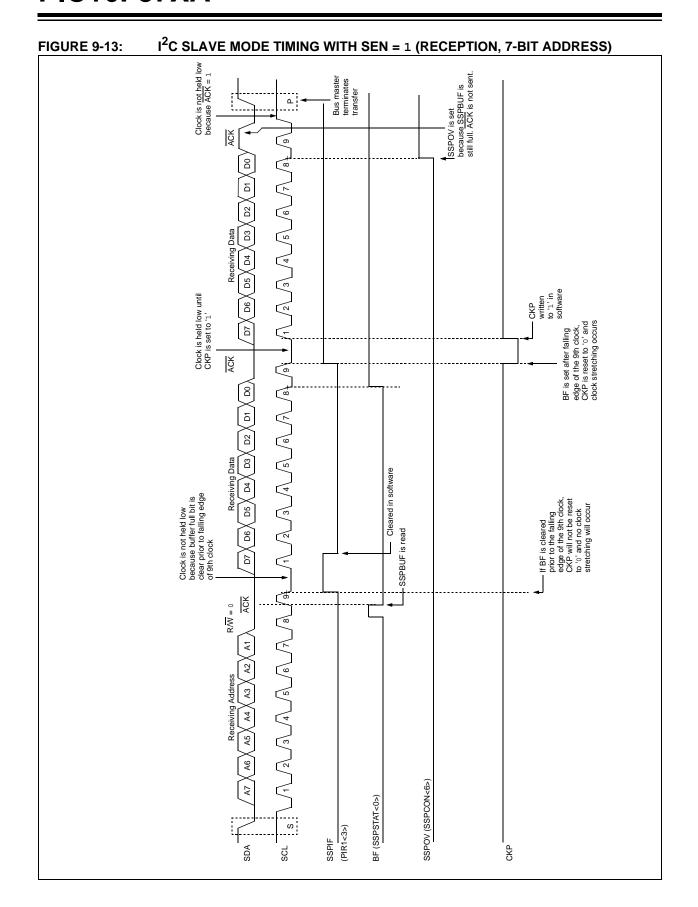

| I <sup>2</sup> C Slave Mode with SEN = 1 (Reception,          | PSPMODE Bit48, 49, 50,                     | 51  |

| 10-bit Address)                                               | TXREG Register                             |     |

| I <sup>2</sup> C Slave Mode with SEN = 0 (Reception,          | TXSTA Register                             |     |

| 10-bit Address)                                               | BRGH Bit 1                                 |     |

| I <sup>2</sup> C Slave Mode with SEN = 0 (Reception,          | CSRC Bit                                   |     |

| , , ,                                                         | SYNC Bit                                   |     |

| 7-bit Address)                                                |                                            |     |

| I <sup>2</sup> C Slave Mode with SEN = 1 (Reception,          | TRMT Bit                                   |     |

| 7-bit Address)                                                | TX9 Bit                                    |     |

| Parallel Slave Port (PIC16F874A/877A Only) 187                | TX9D Bit 1                                 |     |

| Parallel Slave Port (PSP) Read52                              | TXEN Bit 1                                 | 11  |

| Parallel Slave Port (PSP) Write52                             | U                                          |     |

| Repeat Start Condition100                                     | U                                          |     |

| Reset, Watchdog Timer, Start-up Timer                         | USART 1                                    | 11  |

| and Power-up Timer184                                         | Address Detect Enable (ADDEN Bit)          | 12  |

| Slave Mode General Call Address Sequence                      | Asynchronous Mode 1                        |     |

| (7 or 10-bit Address Mode)94                                  | Asynchronous Receive (9-bit Mode) 1        |     |

| Slave Synchronization77                                       | Asynchronous Receive with Address Detect.  | . • |

|                                                               | · · · · · · · · · · · · · · · · · · ·      |     |

| Slow Rise Time (MCLR Tied to VDD via                          | See Asynchronous Receive (9-bit Mode).     | 17  |

| RC Network)                                                   | Asynchronous Receiver                      |     |

| SPI Master Mode (CKE = 0, SMP = 0)188                         | Asynchronous Reception                     |     |

| SPI Master Mode (CKE = 1, SMP = 1)188                         | Asynchronous Transmitter 1                 |     |

| SPI Mode (Master Mode)76                                      | Baud Rate Generator (BRG)1                 |     |

| SPI Mode (Slave Mode with CKE = 0)78                          | Baud Rate Formula1                         | 13  |

| SPI Mode (Slave Mode with CKE = 1)78                          | Baud Rates, Asynchronous Mode              |     |

| SPI Slave Mode (CKE = 0)189                                   | (BRGH = 0) 1                               | 14  |

| SPI Slave Mode (CKE = 1)189                                   | Baud Rates, Asynchronous Mode              |     |

| Stop Condition Receive or Transmit Mode                       | (BRGH = 1)1                                | 14  |

| Synchronous Reception                                         | High Baud Rate Select (BRGH Bit)1          |     |

| (Master Mode, SREN)124                                        | Sampling 1                                 |     |

|                                                               | Clock Source Select (CSRC Bit)             |     |

| Synchronous Transmission                                      |                                            |     |

| Synchronous Transmission (Through TXEN) 122                   | Continuous Receive Enable (CREN Bit)       |     |

| Time-out Sequence on Power-up                                 | Framing Error (FERR Bit)                   |     |

| (MCLR Not Tied to VDD)                                        | Mode Select (SYNC Bit)                     |     |

| Case 1152                                                     | Overrun Error (OERR Bit) 1                 |     |

| Case 2 152                                                    | Receive Data, 9th Bit (RX9D Bit)1          |     |

| Time-out Sequence on Power-up (MCLR Tied                      | Receive Enable, 9-bit (RX9 Bit)1           | 12  |

| to VDD via RC Network)151                                     | Serial Port Enable (SPEN Bit)111, 1        | 12  |

| Timer0 and Timer1 External Clock                              | Single Receive Enable (SREN Bit) 1         | 12  |

| USART Synchronous Receive                                     | Synchronous Master Mode1                   |     |

| (Master/Slave)193                                             | Synchronous Master Reception 1             |     |

|                                                               | Synchronous Master Transmission            |     |

| USART Synchronous Transmission  (Master/(Slave)               | Synchronous Slave Mode 1                   |     |

| (Master/Slave)                                                |                                            |     |

| Wake-up from Sleep via Interrupt157                           | Synchronous Slave Reception                |     |

| iming Parameter Symbology181                                  | Synchronous Slave Transmit                 |     |

| MR0 Register19                                                | Transmit Data, 9th Bit (TX9D) 1            |     |

| MR1CS Bit57                                                   | Transmit Enable (TXEN Bit)1                |     |

| MR1H Register19                                               | Transmit Enable, 9-bit (TX9 Bit)           | 11  |

| MR1L Register19                                               | Transmit Shift Register Status (TRMT Bit)1 | 11  |

| MR1ON Bit57                                                   | USART Synchronous Receive Requirements 1   |     |

| MR2 Register19                                                |                                            |     |

| MR2ON Bit                                                     | V                                          |     |

| MRO Register                                                  | VDD Pin9,                                  | 13  |

|                                                               | Voltage Reference Specifications 1         |     |

| OUTPS0 Bit                                                    | Vss Pin                                    |     |

| OUTPS1 Bit                                                    | v 55 T III                                 | 13  |

| OUTPS2 Bit61                                                  |                                            |     |

| OUTPS3 Bit61                                                  |                                            |     |

| RISA Register20                                               |                                            |     |