Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                     |

|----------------------------|----------------------------------------------------------------------------|

| Core Processor             | PIC                                                                        |

| Core Size                  | 8-Bit                                                                      |

| Speed                      | 10MHz                                                                      |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                          |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                      |

| Number of I/O              | 33                                                                         |

| Program Memory Size        | 14KB (8K x 14)                                                             |

| Program Memory Type        | FLASH                                                                      |

| EEPROM Size                | 256 x 8                                                                    |

| RAM Size                   | 368 x 8                                                                    |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 5.5V                                                                  |

| Data Converters            | A/D 8x10b                                                                  |

| Oscillator Type            | External                                                                   |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                          |

| Mounting Type              | Surface Mount                                                              |

| Package / Case             | 44-TQFP                                                                    |

| Supplier Device Package    | 44-TQFP (10x10)                                                            |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16lf877a-i-pt |

|                            |                                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| TABLE 1-3:      |              | TABLE 1-3:         PIC16F874A/877A PINOUT DESCRIPTION (CONTINUED) |              |                 |               |                       |                                                                 |  |  |  |

|-----------------|--------------|-------------------------------------------------------------------|--------------|-----------------|---------------|-----------------------|-----------------------------------------------------------------|--|--|--|

| Pin Name        | PDII<br>Pin# |                                                                   | TQFP<br>Pin# | QFN<br>Pin#     | I/O/P<br>Type | Buffer<br>Type        | Description                                                     |  |  |  |

|                 |              |                                                                   |              |                 |               |                       | PORTD is a bidirectional I/O port or Parallel Slave             |  |  |  |

|                 |              |                                                                   |              |                 |               |                       | Port when interfacing to a microprocessor bus.                  |  |  |  |

| RD0/PSP0        | 19           | 21                                                                | 38           | 38              |               | ST/TTL <sup>(3)</sup> |                                                                 |  |  |  |

| RD0             |              |                                                                   |              |                 | I/O           |                       | Digital I/O.                                                    |  |  |  |

| PSP0            |              |                                                                   |              |                 | I/O           |                       | Parallel Slave Port data.                                       |  |  |  |

| RD1/PSP1        | 20           | 22                                                                | 39           | 39              |               | ST/TTL <sup>(3)</sup> |                                                                 |  |  |  |

| RD1             |              |                                                                   |              |                 | I/O           |                       | Digital I/O.                                                    |  |  |  |

| PSP1            |              |                                                                   |              |                 | I/O           | (2)                   | Parallel Slave Port data.                                       |  |  |  |

| RD2/PSP2        | 21           | 23                                                                | 40           | 40              |               | ST/TTL <sup>(3)</sup> |                                                                 |  |  |  |

| RD2<br>PSP2     |              |                                                                   |              |                 | I/O<br>I/O    |                       | Digital I/O.<br>Parallel Slave Port data.                       |  |  |  |

| -               |              |                                                                   |              |                 | 1/0           | o = (=== (3)          | Parallel Slave Port data.                                       |  |  |  |

| RD3/PSP3        | 22           | 24                                                                | 41           | 41              | I/O           | ST/TTL <sup>(3)</sup> |                                                                 |  |  |  |

| RD3<br>PSP3     |              |                                                                   |              |                 | 1/O<br>1/O    |                       | Digital I/O.<br>Parallel Slave Port data.                       |  |  |  |

|                 | 07           | 20                                                                | 0            | 0               | 1/0           | ST/TTL <sup>(3)</sup> | i arallel Slave i Olt Gata.                                     |  |  |  |

| RD4/PSP4<br>RD4 | 27           | 30                                                                | 2            | 2               | I/O           | 51/11L*/              | Digital I/O.                                                    |  |  |  |

| PSP4            |              |                                                                   |              |                 | 1/O           |                       | Parallel Slave Port data.                                       |  |  |  |

| RD5/PSP5        | 28           | 31                                                                | 3            | 3               |               | ST/TTL <sup>(3)</sup> |                                                                 |  |  |  |

| RD5             | 20           | 51                                                                | 5            | 5               | I/O           | 31/112.7              | Digital I/O.                                                    |  |  |  |

| PSP5            |              |                                                                   |              |                 | I/O           |                       | Parallel Slave Port data.                                       |  |  |  |

| RD6/PSP6        | 29           | 32                                                                | 4            | 4               |               | ST/TTL <sup>(3)</sup> |                                                                 |  |  |  |

| RD6             | 20           | 02                                                                | -            | -               | I/O           | OWITE                 | Digital I/O.                                                    |  |  |  |

| PSP6            |              |                                                                   |              |                 | I/O           |                       | Parallel Slave Port data.                                       |  |  |  |

| RD7/PSP7        | 30           | 33                                                                | 5            | 5               |               | ST/TTL <sup>(3)</sup> |                                                                 |  |  |  |

| RD7             |              |                                                                   | Ũ            | Ŭ               | I/O           | 0.,                   | Digital I/O.                                                    |  |  |  |

| PSP7            |              |                                                                   |              |                 | I/O           |                       | Parallel Slave Port data.                                       |  |  |  |

|                 |              |                                                                   |              |                 |               |                       | PORTE is a bidirectional I/O port.                              |  |  |  |

| RE0/RD/AN5      | 8            | 9                                                                 | 25           | 25              |               | ST/TTL(3)             |                                                                 |  |  |  |

| RE0             | _            | _                                                                 | _            |                 | I/O           |                       | Digital I/O.                                                    |  |  |  |

| RD              |              |                                                                   |              |                 | I             |                       | Read control for Parallel Slave Port.                           |  |  |  |

| AN5             |              |                                                                   |              |                 | I             |                       | Analog input 5.                                                 |  |  |  |

| RE1/WR/AN6      | 9            | 10                                                                | 26           | 26              |               | ST/TTL <sup>(3)</sup> |                                                                 |  |  |  |

| RE1             |              |                                                                   |              |                 | I/O           |                       | Digital I/O.                                                    |  |  |  |

| WR              |              |                                                                   |              |                 |               |                       | Write control for Parallel Slave Port.                          |  |  |  |

| AN6             |              |                                                                   |              |                 | I             | (2)                   | Analog input 6.                                                 |  |  |  |

| RE2/CS/AN7      | 10           | 11                                                                | 27           | 27              |               | ST/TTL <sup>(3)</sup> |                                                                 |  |  |  |

| RE2<br>CS       |              |                                                                   |              |                 | I/O           |                       | Digital I/O.<br>Chip coloct control for Parallel Slove Part     |  |  |  |

| AN7             |              |                                                                   |              |                 |               |                       | Chip select control for Parallel Slave Port.<br>Analog input 7. |  |  |  |

| Vss             | 10.0         | 1 13, 34                                                          | 6.20         | 6 20            | P             |                       |                                                                 |  |  |  |

| v               | 12, 3        | 1 13, 34                                                          | 6, 29        | 6, 30,<br>31    |               |                       | Ground reference for logic and I/O pins.                        |  |  |  |

| Vdd             | 11, 3        | 2 12, 35                                                          | 7, 28        | 7, 8,<br>28, 29 | Р             | —                     | Positive supply for logic and I/O pins.                         |  |  |  |

| NC              | <u> </u>     | 1, 17,                                                            | 12,13,       | 13              |               | _                     | These pins are not internally connected. These pins             |  |  |  |

|                 | 1            | 28, 40                                                            | 33, 34       | -               |               |                       | should be left unconnected.                                     |  |  |  |

#### TARI E 1-3. PIC16E8744/8774 PINOLIT DESCRIPTION (CONTINUED)

= input I. — = Not used TTL = TTL input

I/O = input/output I ST = Schmitt Trigger input

Note 1: This buffer is a Schmitt Trigger input when configured as the external interrupt.2: This buffer is a Schmitt Trigger input when used in Serial Programming mode.

3: This buffer is a Schmitt Trigger input when configured in RC Oscillator mode and a CMOS input otherwise.

## 2.2 Data Memory Organization

The data memory is partitioned into multiple banks which contain the General Purpose Registers and the Special Function Registers. Bits RP1 (Status<6>) and RP0 (Status<5>) are the bank select bits.

| RP1:RP0 | Bank |

|---------|------|

| 00      | 0    |

| 01      | 1    |

| 10      | 2    |

| 11      | 3    |

Each bank extends up to 7Fh (128 bytes). The lower locations of each bank are reserved for the Special Function Registers. Above the Special Function Registers are General Purpose Registers, implemented as static RAM. All implemented banks contain Special Function Registers. Some frequently used Special Function Registers from one bank may be mirrored in another bank for code reduction and quicker access.

| Note: | The EEPROM data memory description can |

|-------|----------------------------------------|

|       | be found in Section 3.0 "Data EEPROM   |

|       | and Flash Program Memory" of this data |

|       | sheet.                                 |

#### 2.2.1 GENERAL PURPOSE REGISTER FILE

The register file can be accessed either directly, or indirectly, through the File Select Register (FSR).

#### 2.2.2.8 PCON Register

bit 1

The Power Control (PCON) register contains flag bits to allow differentiation between a Power-on Reset (POR), a Brown-out Reset (BOR), a Watchdog Reset (WDT) and an external MCLR Reset.

Note: BOR is unknown on Power-on Reset. It must be set by the user and checked on subsequent Resets to see if BOR is clear, indicating a brown-out has occurred. The BOR status bit is a "don't care" and is not predictable if the brown-out circuit is disabled (by clearing the BODEN bit in the configuration word).

#### REGISTER 2-8: PCON REGISTER (ADDRESS 8Eh)

| U-0   | U-0 | U-0 | U-0 | U-0 | U-0 | R/W-0 | R/W-1 |

|-------|-----|-----|-----|-----|-----|-------|-------|

| _     |     | _   | —   | —   | —   | POR   | BOR   |

| bit 7 |     |     |     |     |     |       | bit 0 |

- bit 7-2 Unimplemented: Read as '0'

- **POR**: Power-on Reset Status bit

- 1 = No Power-on Reset occurred

0 = A Power-on Reset occurred (must be set in software after a Power-on Reset occurs)

- bit 0 BOR: Brown-out Reset Status bit

- 1 = No Brown-out Reset occurred

0 = A Brown-out Reset occurred (must be set in software after a Brown-out Reset occurs)

| Legend:            |                  |                      |                    |

|--------------------|------------------|----------------------|--------------------|

| R = Readable bit   | W = Writable bit | U = Unimplemented    | l bit, read as '0' |

| - n = Value at POR | '1' = Bit is set | '0' = Bit is cleared | x = Bit is unknown |

# PIC16F87XA

| REGISTER 3-1: | EECON1 F                                                                                                                                                           | REGISTER                                 | (ADDRES                                     | SS 18Ch)             |               |               |                |             |

|---------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------|---------------------------------------------|----------------------|---------------|---------------|----------------|-------------|

|               | R/W-x                                                                                                                                                              | U-0                                      | U-0                                         | U-0                  | R/W-x         | R/W-0         | R/S-0          | R/S-0       |

|               | EEPGD                                                                                                                                                              | _                                        | _                                           | _                    | WRERR         | WREN          | WR             | RD          |

|               | bit 7                                                                                                                                                              |                                          |                                             |                      |               |               |                | bit 0       |

| bit 7         | EEPGD: Pi                                                                                                                                                          | ogram/Data                               | EEPROM                                      | Select bit           |               |               |                |             |

|               | 0 = Access                                                                                                                                                         | es program<br>es data mer<br>fter a POR; | mory                                        | not be chang         | jed while a v | write operati | on is in prog  | ress.       |

| bit 6-4       | Unimplem                                                                                                                                                           | ented: Read                              | <b>d as</b> '0'                             |                      |               | ·             |                |             |

| bit 3         | WRERR: E                                                                                                                                                           | EPROM Er                                 | ror Flag bit                                |                      |               |               |                |             |

|               | <ul> <li>1 = A write operation is prematurely terminated (any MCLR or any WDT Reset during normal operation)</li> <li>0 = The write operation completed</li> </ul> |                                          |                                             |                      |               |               |                | ring normal |

| bit 2         | WREN: EE                                                                                                                                                           | PROM Writ                                | e Enable bit                                |                      |               |               |                |             |

|               | <ul> <li>1 = Allows write cycles</li> <li>0 = Inhibits write to the EEPROM</li> <li>WR: Write Control bit</li> </ul>                                               |                                          |                                             |                      |               |               |                |             |

| bit 1         |                                                                                                                                                                    |                                          |                                             |                      |               |               |                |             |

|               | can on                                                                                                                                                             | ly be set (no                            | cle. The bit<br>ot cleared) ii<br>EEPROM is |                      | / hardware o  | once write is | s complete.    | The WR bit  |

| bit 0         | RD: Read                                                                                                                                                           | Control bit                              |                                             |                      |               |               |                |             |

|               | cleared                                                                                                                                                            | d) in softwar                            |                                             | D is cleared<br>read | in hardwar    | e. The RD I   | oit can only   | be set (not |

|               | Legend:                                                                                                                                                            |                                          |                                             |                      |               |               |                |             |

|               | R = Reada                                                                                                                                                          | ble bit                                  | W = W                                       | /ritable bit         | U = Unim      | plemented     | bit, read as ' | 0'          |

| Legend:            |                  |                          |                  |

|--------------------|------------------|--------------------------|------------------|

| R = Readable bit   | W = Writable bit | U = Unimplemented bit,   | read as '0'      |

| - n = Value at POR | '1' = Bit is set | '0' = Bit is cleared x = | = Bit is unknown |

#### 3.5 Reading Flash Program Memory

To read a program memory location, the user must write two bytes of the address to the EEADR and EEADRH registers, set the EEPGD control bit (EECON1<7>) and then set control bit RD (EECON1<0>). Once the read control bit is set, the program memory Flash controller will use the next two instruction cycles to read the data. This causes these two instructions immediately following the "BSF EECON1, RD" instruction to be ignored. The data is available in the very next cycle in the EEDATA and EEDATH registers; therefore, it can be read as two bytes in the following instructions. EEDATA and EEDATH registers will hold this value until another read or until it is written to by the user (during a write operation).

| EXAMPLE 3-3: | FLASH PROGRAM READ |

|--------------|--------------------|

|              |                    |

|                           | BSF   | STATUS, RP1     | i                                                    |  |

|---------------------------|-------|-----------------|------------------------------------------------------|--|

|                           | BCF   | STATUS, RPO     | ; Bank 2                                             |  |

|                           | MOVLW | MS PROG EE ADDR | i                                                    |  |

|                           | MOVWF | EEADRH          | ; MS Byte of Program Address to read                 |  |

|                           | MOVLW | LS_PROG_EE_ADDR | i                                                    |  |

|                           | MOVWF | EEADR           | ; LS Byte of Program Address to read                 |  |

|                           | BSF   | STATUS, RPO     | ; Bank 3                                             |  |

|                           | BSF   | EECON1, EEPGD   | ; Point to PROGRAM memory                            |  |

|                           | BSF   | EECON1, RD      | ; EE Read                                            |  |

| Required<br>Sequence<br>; |       |                 |                                                      |  |

| luer                      | NOP   |                 |                                                      |  |

| Seq                       | NOP   |                 | ; Any instructions here are ignored as program       |  |

|                           |       |                 | ; memory is read in second cycle after BSF EECON1,RD |  |

| ;                         |       |                 |                                                      |  |

|                           | BCF   | STATUS, RPO     | ; Bank 2                                             |  |

|                           | MOVF  | EEDATA, W       | ; W = LS Byte of Program EEDATA                      |  |

|                           | MOVWF | DATAL           | ;                                                    |  |

|                           | MOVF  | EEDATH, W       | ; W = MS Byte of Program EEDATA                      |  |

|                           | MOVWF | DATAH           | ;                                                    |  |

|                           |       |                 |                                                      |  |

# 9.0 MASTER SYNCHRONOUS SERIAL PORT (MSSP) MODULE

### 9.1 Master SSP (MSSP) Module Overview

The Master Synchronous Serial Port (MSSP) module is a serial interface, useful for communicating with other peripheral or microcontroller devices. These peripheral devices may be serial EEPROMs, shift registers, display drivers, A/D converters, etc. The MSSP module can operate in one of two modes:

- Serial Peripheral Interface (SPI)

- Inter-Integrated Circuit (I<sup>2</sup>C)

- Full Master mode

- Slave mode (with general address call)

The I<sup>2</sup>C interface supports the following modes in hardware:

- Master mode

- Multi-Master mode

- Slave mode

## 9.2 Control Registers

The MSSP module has three associated registers. These include a status register (SSPSTAT) and two control registers (SSPCON and SSPCON2). The use of these registers and their individual configuration bits differ significantly, depending on whether the MSSP module is operated in SPI or  $I^2C$  mode.

Additional details are provided under the individual sections.

## 9.3 SPI Mode

The SPI mode allows 8 bits of data to be synchronously transmitted and received simultaneously. All four modes of SPI are supported. To accomplish communication, typically three pins are used:

- Serial Data Out (SDO) RC5/SDO

- Serial Data In (SDI) RC4/SDI/SDA

- Serial Clock (SCK) RC3/SCK/SCL

Additionally, a fourth pin may be used when in a Slave mode of operation:

Slave Select (SS) – RA5/AN4/SS/C2OUT

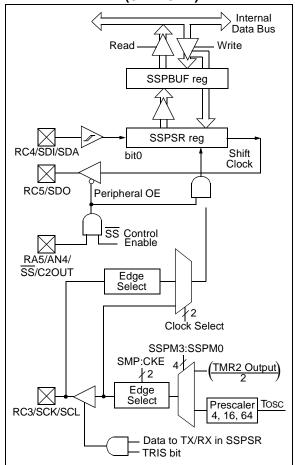

Figure 9-1 shows the block diagram of the MSSP module when operating in SPI mode.

#### FIGURE 9-1:

#### MSSP BLOCK DIAGRAM (SPI MODE)

| Note: | When the SPI is in Slave mode with $\overline{SS}$ pin<br>control enabled (SSPCON<3:0> = 0100),<br>the state of the SS pin can affect the state<br>read back from the TRISC<5> bit. The<br>Peripheral OE signal from the SSP mod-<br>ule in PORTC controls the state that is<br>read back from the TRISC<5> bit (see<br>Section 4.3 "PORTC and the TRISC<br>Register" for information on PORTC). If<br>Read-Modify-Write instructions, such as<br>BSF, are performed on the TRISC register<br>while the SS pin is high, this will cause the<br>TRISC of the table part thus displayed by |

|-------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|       | while the SS pin is high, this will cause the TRISC<5> bit to be set, thus disabling the SDO output.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

#### 9.3.1 REGISTERS

The MSSP module has four registers for SPI mode operation. These are:

- MSSP Control Register (SSPCON)

- MSSP Status Register (SSPSTAT)

- Serial Receive/Transmit Buffer Register (SSPBUF)

- MSSP Shift Register (SSPSR) Not directly accessible

SSPCON and SSPSTAT are the control and status registers in SPI mode operation. The SSPCON register is readable and writable. The lower six bits of the SSPSTAT are read-only. The upper two bits of the SSPSTAT are read/write. SSPSR is the shift register used for shifting data in or out. SSPBUF is the buffer register to which data bytes are written to or read from.

In receive operations, SSPSR and SSPBUF together create a double-buffered receiver. When SSPSR receives a complete byte, it is transferred to SSPBUF and the SSPIF interrupt is set.

During transmission, the SSPBUF is not doublebuffered. A write to SSPBUF will write to both SSPBUF and SSPSR.

#### REGISTER 9-1: SSPSTAT: MSSP STATUS REGISTER (SPI MODE) (ADDRESS 94h)

|       | R/W-0                    | R/W-0                                                | R-0             | R-0          | R-0           | R-0           | R-0          | R-0           |  |  |  |

|-------|--------------------------|------------------------------------------------------|-----------------|--------------|---------------|---------------|--------------|---------------|--|--|--|

|       | SMP                      | CKE                                                  | D/A             | Р            | S             | R/W           | UA           | BF            |  |  |  |

|       | bit 7                    |                                                      |                 |              |               |               |              | bit 0         |  |  |  |

| bit 7 | SMP: Sam                 | ple bit                                              |                 |              |               |               |              |               |  |  |  |

|       | SPI Master               |                                                      |                 |              |               |               |              |               |  |  |  |

|       |                          | 1 = Input data sampled at end of data output time    |                 |              |               |               |              |               |  |  |  |

|       |                          | 0 = Input data sampled at middle of data output time |                 |              |               |               |              |               |  |  |  |

|       | SMP must                 | be cleared v                                         | when SPI is     | used in Slav | ve mode       |               |              |               |  |  |  |

| bit 6 |                          | Clock Select                                         |                 |              | o modo.       |               |              |               |  |  |  |

|       | 1 = Transm               | nit occurs on                                        | transition fr   | om active to | ldle clock s  | state         |              |               |  |  |  |

|       | 0 = Transm               | nit occurs on                                        | transition fr   | om Idle to a | ctive clock s | state         |              |               |  |  |  |

|       | Note:                    | Polarity of o                                        | clock state is  | s set by the | CKP bit (SS   | PCON1<4>      | ).           |               |  |  |  |

| bit 5 | D/A: Data/               | Address bit                                          |                 |              |               |               |              |               |  |  |  |

|       | Used in I <sup>2</sup> C | c mode only.                                         |                 |              |               |               |              |               |  |  |  |

| bit 4 | P: Stop bit              |                                                      |                 |              |               |               |              |               |  |  |  |

|       | Used in I <sup>2</sup> C | mode only.                                           | This bit is cle | ared when t  | he MSSP me    | odule is disa | bled, SSPEI  | N is cleared. |  |  |  |

| bit 3 | S: Start bit             |                                                      |                 |              |               |               |              |               |  |  |  |

|       | Used in I <sup>2</sup> C | c mode only.                                         |                 |              |               |               |              |               |  |  |  |

| bit 2 | R/W: Read                | I/Write bit inf                                      | ormation        |              |               |               |              |               |  |  |  |

|       | Used in I <sup>2</sup> C | c mode only.                                         |                 |              |               |               |              |               |  |  |  |

| bit 1 | UA: Update               | e Address b                                          | it              |              |               |               |              |               |  |  |  |

|       | Used in I <sup>2</sup> C | c mode only.                                         |                 |              |               |               |              |               |  |  |  |

| bit 0 | BF: Buffer               | Full Status b                                        | oit (Receive    | mode only)   |               |               |              |               |  |  |  |

|       | 1 = Receiv               | e complete,                                          | SSPBUF is       | full         |               |               |              |               |  |  |  |

|       | 0 = Receiv               | e not comple                                         | ete, SSPBU      | F is empty   |               |               |              |               |  |  |  |

|       | Legend:                  |                                                      |                 |              |               |               |              |               |  |  |  |

|       | R = Reada                | ble bit                                              | W = W           | ritable bit  | U = Unim      | plemented     | bit, read as | '0'           |  |  |  |

|       | - n = Value              | at POR                                               | '1' = B         | it is set    | '0' = Bit i   | s cleared     | x = Bit is ι | Inknown       |  |  |  |

### 9.3.2 OPERATION

When initializing the SPI, several options need to be specified. This is done by programming the appropriate control bits (SSPCON<5:0> and SSPSTAT<7:6>). These control bits allow the following to be specified:

- Master mode (SCK is the clock output)

- Slave mode (SCK is the clock input)

- Clock Polarity (Idle state of SCK)

- Data Input Sample Phase (middle or end of data output time)

- Clock Edge (output data on rising/falling edge of SCK)

- Clock Rate (Master mode only)

- Slave Select mode (Slave mode only)

The MSSP consists of a transmit/receive shift register (SSPSR) and a buffer register (SSPBUF). The SSPSR shifts the data in and out of the device, MSb first. The SSPBUF holds the data that was written to the SSPSR until the received data is ready. Once the eight bits of data have been received, that byte is moved to the SSPBUF register. Then, the Buffer Full detect bit, BF (SSPSTAT<0>), and the interrupt flag bit, SSPIF, are set. This double-buffering of the received data (SSPBUF) allows the next byte to start reception before reading the data that was just received. Any write to the

SSPBUF register during transmission/reception of data will be ignored and the write collision detect bit, WCOL (SSPCON<7>), will be set. User software must clear the WCOL bit so that it can be determined if the following write(s) to the SSPBUF register completed successfully.

When the application software is expecting to receive valid data, the SSPBUF should be read before the next byte of data to transfer is written to the SSPBUF. Buffer Full bit, BF (SSPSTAT<0>), indicates when SSPBUF has been loaded with the received data (transmission is complete). When the SSPBUF is read, the BF bit is cleared. This data may be irrelevant if the SPI is only a transmitter. Generally, the MSSP interrupt is used to determine when the transmission/reception has completed. The SSPBUF must be read and/or written. If the interrupt method is not going to be used, then software polling can be done to ensure that a write collision does not occur. Example 9-1 shows the loading of the SSPBUF (SSPSR) for data transmission.

The SSPSR is not directly readable or writable and can only be accessed by addressing the SSPBUF register. Additionally, the MSSP Status register (SSPSTAT) indicates the various status conditions.

#### EXAMPLE 9-1: LOADING THE SSPBUF (SSPSR) REGISTER

| LOOP | BRA           | SSPSTAT, BF<br>LOOP<br>SSPBUF, W | ;Has data been received(transmit complete)?<br>;No<br>;WREG reg = contents of SSPBUF |

|------|---------------|----------------------------------|--------------------------------------------------------------------------------------|

|      | MOVWF         | RXDATA                           | ;Save in user RAM, if data is meaningful                                             |

|      | MOVF<br>MOVWF | TXDATA, W<br>SSPBUF              | ;W reg = contents of TXDATA<br>;New data to xmit                                     |

#### 9.4.4 CLOCK STRETCHING

Both 7 and 10-bit Slave modes implement automatic clock stretching during a transmit sequence.

The SEN bit (SSPCON2<0>) allows clock stretching to be enabled during receives. Setting SEN will cause the SCL pin to be held low at the end of each data receive sequence.

#### 9.4.4.1 Clock Stretching for 7-bit Slave Receive Mode (SEN = 1)

In 7-bit Slave Receive mode, <u>on the falling edge of the</u> ninth clock at the end of the ACK sequence, if the BF bit is set, the CKP bit in the SSPCON register is automatically cleared, forcing the SCL output to be held low. The CKP bit being cleared to '0' will assert the SCL line low. The CKP bit must be set in the user's ISR before reception is allowed to continue. By holding the SCL line low, the user has time to service the ISR and read the contents of the SSPBUF before the master device can initiate another receive sequence. This will prevent buffer overruns from occurring (see Figure 9-13).

- Note 1: If the user reads the contents of the SSPBUF before the falling edge of the ninth clock, thus clearing the BF bit, the CKP bit will not be cleared and clock stretching will not occur.

- 2: The CKP bit can be set in software regardless of the state of the BF bit. The user should be careful to clear the BF bit in the ISR before the next receive sequence in order to prevent an overflow condition.

#### 9.4.4.2 Clock Stretching for 10-bit Slave Receive Mode (SEN = 1)

In 10-bit Slave Receive mode, during the address sequence, clock stretching automatically takes place but CKP is not cleared. During this time, if the UA bit is set after the ninth clock, clock stretching is initiated. The UA bit is set after receiving the upper byte of the 10-bit address and following the receive of the second byte of the 10-bit address, with the R/W bit cleared to '0'. The release of the clock line occurs upon updating SSPADD. Clock stretching will occur on each data receive sequence as described in 7-bit mode.

**Note:** If the user polls the UA bit and clears it by updating the SSPADD register before the falling edge of the ninth clock occurs and if the user hasn't cleared the BF bit by reading the SSPBUF register before that time, then the CKP bit will still NOT be asserted low. Clock stretching, on the basis of the state of the BF bit, only occurs during a data sequence, not an address sequence.

#### 9.4.4.3 Clock Stretching for 7-bit Slave Transmit Mode

7-bit Slave Transmit mode implements clock stretching by clearing the CKP bit after the falling edge of the ninth clock, if the BF bit is clear. This occurs regardless of the state of the SEN bit.

The user's ISR must set the CKP bit before transmission is allowed to continue. By holding the SCL line low, the user has time to service the ISR and load the contents of the SSPBUF before the master device can initiate another transmit sequence (see Figure 9-9).

| Note 1: | If the user loads the contents of SSPBUF,     |  |  |  |  |  |  |

|---------|-----------------------------------------------|--|--|--|--|--|--|

|         | setting the BF bit before the falling edge of |  |  |  |  |  |  |

|         | the ninth clock, the CKP bit will not be      |  |  |  |  |  |  |

|         | cleared and clock stretching will not occur.  |  |  |  |  |  |  |

| 2:      | The CKP bit can be set in software            |  |  |  |  |  |  |

# regardless of the state of the BF bit.9.4.4.4Clock Stretching for 10-bit Slave

Transmit Mode In 10-bit Slave Transmit mode, clock stretching is controlled during the first two address sequences by the state of the UA bit, just as it is in 10-bit Slave Receive mode. The first two addresses are followed by a third address sequence, which contains the high order bits of the 10-bit address and the R/W bit set to '1'. After the third address sequence is performed, the UA bit is not set, the module is now configured in Transmit mode and clock stretching is controlled by the BF flag as in 7-bit Slave Transmit mode (see Figure 9-11).

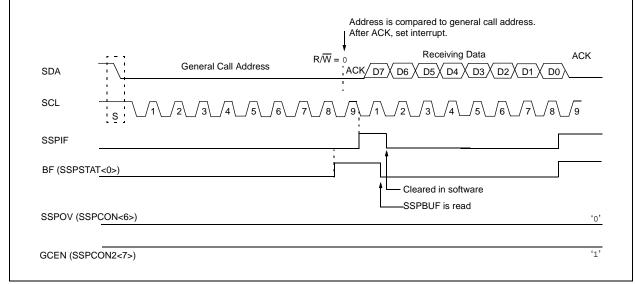

#### 9.4.5 GENERAL CALL ADDRESS SUPPORT

The addressing procedure for the  $I^2C$  bus is such that the first byte after the Start condition usually determines which device will be the slave addressed by the master. The exception is the general call address which can address all devices. When this address is used, all devices should, in theory, respond with an Acknowledge.

The general call address is one of eight addresses reserved for specific purposes by the  $I^2C$  protocol. It consists of all '0's with R/W = 0.

The general call address is recognized when the General Call Enable bit (GCEN) is enabled (SSPCON2<7> set). Following a Start bit detect, 8 bits are shifted into the SSPSR and the address is compared against the SSPADD. It is also compared to the general call address and fixed in hardware.

If the general call address matches, the SSPSR is transferred to the SSPBUF, the BF flag bit is set (eighth bit) and on the falling edge of the ninth bit (ACK bit), the SSPIF interrupt flag bit is set.

When the interrupt is serviced, the source for the interrupt can be checked by reading the contents of the SSPBUF. The value can be used to determine if the address was device specific or a general call address.

In 10-bit mode, the SSPADD is required to be updated for the second half of the address to match and the UA bit is set (SSPSTAT<1>). If the general call address is sampled when the GCEN bit is set, while the slave is configured in 10-bit Address mode, then the second half of the address is not necessary, the UA bit will not be set and the slave will begin receiving data after the Acknowledge (Figure 9-15).

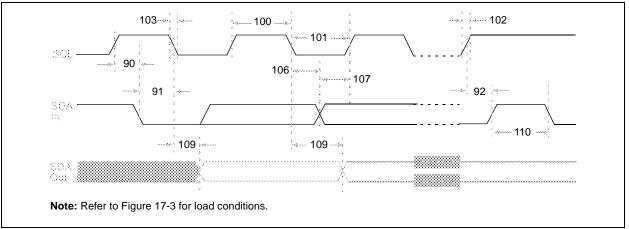

#### 9.4.10 I<sup>2</sup>C MASTER MODE TRANSMISSION

Transmission of a data byte, a 7-bit address or the other half of a 10-bit address is accomplished by simply writing a value to the SSPBUF register. This action will set the Buffer Full flag bit, BF, and allow the Baud Rate Generator to begin counting and start the next transmission. Each bit of address/data will be shifted out onto the SDA pin after the falling edge of SCL is asserted (see data hold time specification, parameter #106). SCL is held low for one Baud Rate Generator rollover count (TBRG). Data should be valid before SCL is released high (see data setup time specification, parameter #107). When the SCL pin is released high, it is held that way for TBRG. The data on the SDA pin must remain stable for that duration and some hold time after the next falling edge of SCL. After the eighth bit is shifted out (the falling edge of the eighth clock), the BF flag is cleared and the master releases SDA. This allows the slave device being addressed to respond with an ACK bit during the ninth bit time, if an address match occurred or if data was received properly. The status of ACK is written into the ACKDT bit on the falling edge of the ninth clock. If the master receives an Acknowledge, the Acknowledge Status bit, ACKSTAT, is cleared. If not, the bit is set. After the ninth clock, the SSPIF bit is set and the master clock (Baud Rate Generator) is suspended until the next data byte is loaded into the SSPBUF, leaving SCL low and SDA unchanged (Figure 9-21).

After the write to the SSPBUF, each bit of address will be shifted out on the falling edge of SCL, until all seven address bits and the R/W bit are completed. On the falling edge of the eighth clock, the master will deassert the SDA pin, allowing the slave to respond with an Acknowledge. On the falling edge of the ninth clock, the master will sample the SDA pin to see if the address was recognized by a slave. The status of the ACK bit is loaded into the ACKSTAT status bit (SSPCON2<6>). Following the falling edge of the ninth clock transmission of the address, the SSPIF is set, the BF flag is cleared and the Baud Rate Generator is turned off until another write to the SSPBUF takes place, holding SCL low and allowing SDA to float.

#### 9.4.10.1 BF Status Flag

In Transmit mode, the BF bit (SSPSTAT<0>) is set when the CPU writes to SSPBUF and is cleared when all eight bits are shifted out.

#### 9.4.10.2 WCOL Status Flag

If the user writes the SSPBUF when a transmit is already in progress (i.e., SSPSR is still shifting out a data byte), the WCOL is set and the contents of the buffer are unchanged (the write doesn't occur).

WCOL must be cleared in software.

#### 9.4.10.3 ACKSTAT Status Flag

In Transmit mode, the ACKSTAT bit (SSPCON2<6>) is cleared when the slave has sent an Acknowledge  $(\overline{ACK} = 0)$  and is set when the slave does Not Acknowledge  $(\overline{ACK} = 1)$ . A slave sends an Acknowledge when it has recognized its address (including a general call) or when the slave has properly received its data.

#### 9.4.11 I<sup>2</sup>C MASTER MODE RECEPTION

Master mode reception is enabled by programming the Receive Enable bit, RCEN (SSPCON2<3>).

Note: The MSSP module must be in an Idle state before the RCEN bit is set or the RCEN bit will be disregarded.

The Baud Rate Generator begins counting and on each rollover, the state of the SCL pin changes (high to low/ low to high) and data is shifted into the SSPSR. After the falling edge of the eighth clock, the receive enable flag is automatically cleared, the contents of the SSPSR are loaded into the SSPBUF, the BF flag bit is set, the SSPIF flag bit is set and the Baud Rate Generator is suspended from counting, holding SCL low. The MSSP is now in Idle state, awaiting the next command. When the buffer is read by the CPU, the BF flag bit is automatically cleared. The user can then send an Acknowledge bit at the end of reception by setting the Acknowledge Sequence Enable bit, ACKEN (SSPCON2<4>).

#### 9.4.11.1 BF Status Flag

In receive operation, the BF bit is set when an address or data byte is loaded into SSPBUF from SSPSR. It is cleared when the SSPBUF register is read.

#### 9.4.11.2 SSPOV Status Flag

In receive operation, the SSPOV bit is set when 8 bits are received into the SSPSR and the BF flag bit is already set from a previous reception.

#### 9.4.11.3 WCOL Status Flag

If the user writes the SSPBUF when a receive is already in progress (i.e., SSPSR is still shifting in a data byte), the WCOL bit is set and the contents of the buffer are unchanged (the write doesn't occur).

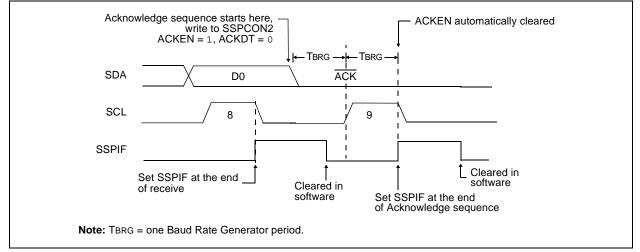

#### 9.4.12 ACKNOWLEDGE SEQUENCE TIMING

An Acknowledge sequence is enabled by setting the Acknowledge Sequence Enable bit. ACKEN (SSPCON2<4>). When this bit is set, the SCL pin is pulled low and the contents of the Acknowledge data bit are presented on the SDA pin. If the user wishes to generate an Acknowledge, then the ACKDT bit should be cleared. If not, the user should set the ACKDT bit before starting an Acknowledge sequence. The Baud Rate Generator then counts for one rollover period (TBRG) and the SCL pin is deasserted (pulled high). When the SCL pin is sampled high (clock arbitration), the Baud Rate Generator counts for TBRG. The SCL pin is then pulled low. Following this, the ACKEN bit is automatically cleared, the baud rate generator is turned off and the MSSP module then goes into Idle mode (Figure 9-23).

#### 9.4.12.1 WCOL Status Flag

If the user writes the SSPBUF when an Acknowledge sequence is in progress, then WCOL is set and the contents of the buffer are unchanged (the write doesn't occur).

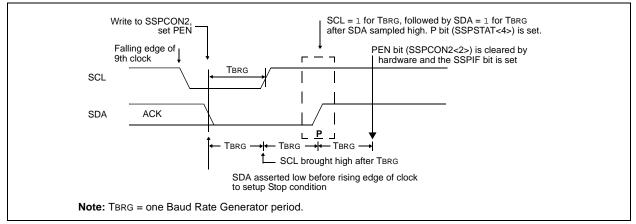

#### 9.4.13 STOP CONDITION TIMING

A Stop bit is asserted on the SDA pin at the end of a receive/transmit by setting the Stop Sequence Enable bit, PEN (SSPCON2<2>). At the end of a receive/ transmit, the SCL line is held low after the falling edge of the ninth clock. When the PEN bit is set, the master will assert the SDA line low. When the SDA line is sampled low, the Baud Rate Generator is reloaded and counts down to 0. When the Baud Rate Generator times out, the SCL pin will be brought high and one TBRG (Baud Rate Generator rollover count) later, the SDA pin will be deasserted. When the SDA pin is sampled high while SCL is high, the P bit (SSPSTAT<4>) is set. A TBRG later, the PEN bit is cleared and the SSPIF bit is set (Figure 9-24).

#### 9.4.13.1 WCOL Status Flag

If the user writes the SSPBUF when a Stop sequence is in progress, then the WCOL bit is set and the contents of the buffer are unchanged (the write doesn't occur).

### FIGURE 9-23: ACKNOWLEDGE SEQUENCE WAVEFORM

#### FIGURE 9-24: STOP CONDITION RECEIVE OR TRANSMIT MODE

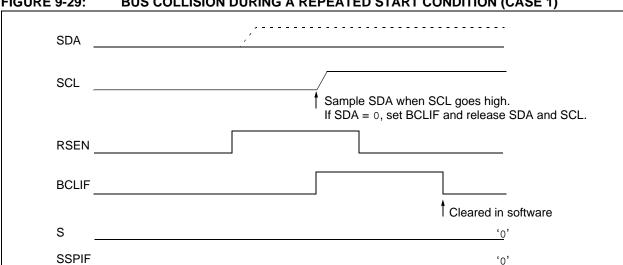

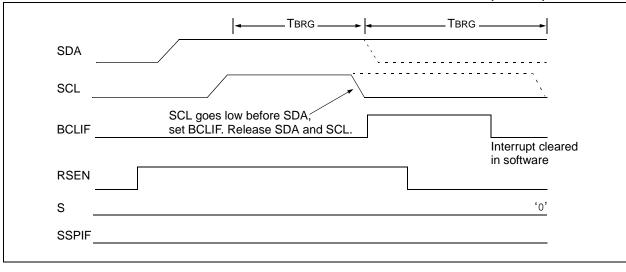

#### Bus Collision During a Repeated 9.4.17.2 Start Condition

During a Repeated Start condition, a bus collision occurs if:

- a) A low level is sampled on SDA when SCL goes from low level to high level.

- b) SCL goes low before SDA is asserted low, indicating that another master is attempting to transmit a data '1'.

When the user deasserts SDA and the pin is allowed to float high, the BRG is loaded with SSPADD<6:0> and counts down to 0. The SCL pin is then deasserted and when sampled high, the SDA pin is sampled.

If SDA is low, a bus collision has occurred (i.e., another master is attempting to transmit a data '0', see Figure 9-29). If SDA is sampled high, the BRG is

reloaded and begins counting. If SDA goes from high to low before the BRG times out, no bus collision occurs because no two masters can assert SDA at exactly the same time.

If SCL goes from high to low before the BRG times out and SDA has not already been asserted, a bus collision occurs. In this case, another master is attempting to transmit a data '1' during the Repeated Start condition (Figure 9-30).

If at the end of the BRG time-out, both SCL and SDA are still high, the SDA pin is driven low and the BRG is reloaded and begins counting. At the end of the count, regardless of the status of the SCL pin, the SCL pin is driven low and the Repeated Start condition is complete.

#### FIGURE 9-29: **BUS COLLISION DURING A REPEATED START CONDITION (CASE 1)**

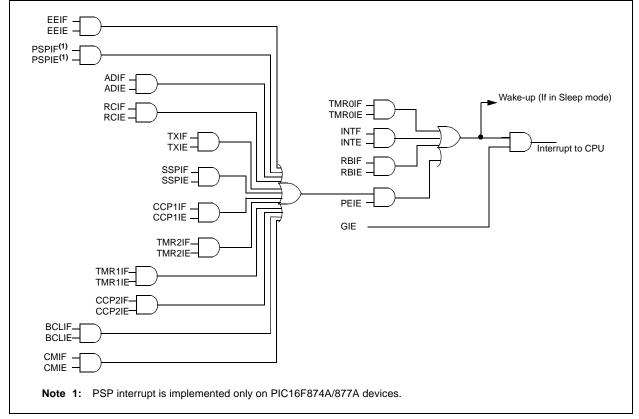

#### 14.11 Interrupts

The PIC16F87XA family has up to 15 sources of interrupt. The Interrupt Control register (INTCON) records individual interrupt requests in flag bits. It also has individual and global interrupt enable bits.

| Note: | Individual interrupt flag bits are set regard- |  |  |  |

|-------|------------------------------------------------|--|--|--|

|       | less of the status of their corresponding      |  |  |  |

|       | mask bit or the GIE bit.                       |  |  |  |

A global interrupt enable bit, GIE (INTCON<7>), enables (if set) all unmasked interrupts or disables (if cleared) all interrupts. When bit GIE is enabled and an interrupt's flag bit and mask bit are set, the interrupt will vector immediately. Individual interrupts can be disabled through their corresponding enable bits in various registers. Individual interrupt bits are set regardless of the status of the GIE bit. The GIE bit is cleared on Reset.

The "return from interrupt" instruction, RETFIE, exits the interrupt routine, as well as sets the GIE bit, which re-enables interrupts.

The RB0/INT pin interrupt, the RB port change interrupt and the TMR0 overflow interrupt flags are contained in the INTCON register.

The peripheral interrupt flags are contained in the Special Function Registers, PIR1 and PIR2. The corresponding interrupt enable bits are contained in Special Function Registers, PIE1 and PIE2, and the peripheral interrupt enable bit is contained in Special Function Register, INTCON.

When an interrupt is responded to, the GIE bit is cleared to disable any further interrupt, the return address is pushed onto the stack and the PC is loaded with 0004h. Once in the Interrupt Service Routine, the source(s) of the interrupt can be determined by polling the interrupt flag bits. The interrupt flag bit(s) must be cleared in software before re-enabling interrupts to avoid recursive interrupts.

For external interrupt events, such as the INT pin or PORTB change interrupt, the interrupt latency will be three or four instruction cycles. The exact latency depends when the interrupt event occurs. The latency is the same for one or two-cycle instructions. Individual interrupt flag bits are set regardless of the status of their corresponding mask bit, PEIE bit or GIE bit.

#### FIGURE 14-10: INTERRUPT LOGIC

# 15.0 INSTRUCTION SET SUMMARY

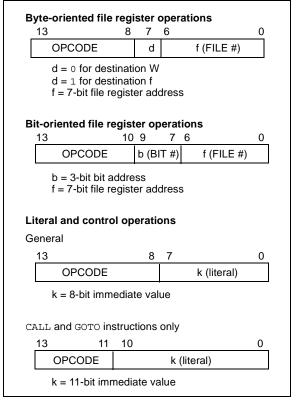

The PIC16 instruction set is highly orthogonal and is comprised of three basic categories:

- Byte-oriented operations

- Bit-oriented operations

- Literal and control operations

Each PIC16 instruction is a 14-bit word divided into an **opcode** which specifies the instruction type and one or more **operands** which further specify the operation of the instruction. The formats for each of the categories is presented in Figure 15-1, while the various opcode fields are summarized in Table 15-1.

Table 15-2 lists the instructions recognized by the MPASM<sup>™</sup> Assembler. A complete description of each instruction is also available in the PIC<sup>®</sup> Mid-Range MCU Family Reference Manual (DS33023).

For **byte-oriented** instructions, 'f' represents a file register designator and 'd' represents a destination designator. The file register designator specifies which file register is to be used by the instruction.

The destination designator specifies where the result of the operation is to be placed. If 'd' is zero, the result is placed in the W register. If 'd' is one, the result is placed in the file register specified in the instruction.

For **bit-oriented** instructions, 'b' represents a bit field designator which selects the bit affected by the operation, while 'f' represents the address of the file in which the bit is located.

For **literal and control** operations, 'k' represents an eight or eleven-bit constant or literal value

One instruction cycle consists of four oscillator periods; for an oscillator frequency of 4 MHz, this gives a normal instruction execution time of 1  $\mu$ s. All instructions are executed within a single instruction cycle, unless a conditional test is true, or the program counter is changed as a result of an instruction. When this occurs, the execution takes two instruction cycles with the second cycle executed as a NOP.

| Note: | To maintain upward compatibility with  |  |  |  |  |

|-------|----------------------------------------|--|--|--|--|

|       | future PIC16F87XA products, do not use |  |  |  |  |

|       | the OPTION and TRIS instructions.      |  |  |  |  |

All instruction examples use the format '0xhh' to represent a hexadecimal number, where 'h' signifies a hexadecimal digit.

### 15.1 READ-MODIFY-WRITE OPERATIONS

Any instruction that specifies a file register as part of the instruction performs a Read-Modify-Write (R-M-W) operation. The register is read, the data is modified, and the result is stored according to either the instruction or the destination designator 'd'. A read operation is performed on a register even if the instruction writes to that register. For example, a "CLRF PORTB" instruction will read PORTB, clear all the data bits, then write the result back to PORTB. This example would have the unintended result that the condition that sets the RBIF flag would be cleared.

# TABLE 15-1: OPCODE FIELD DESCRIPTIONS

| Field | Description                                                                                                                                                                  |  |  |  |

|-------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| f     | Register file address (0x00 to 0x7F)                                                                                                                                         |  |  |  |

| W     | Working register (accumulator)                                                                                                                                               |  |  |  |

| b     | Bit address within an 8-bit file register                                                                                                                                    |  |  |  |

| k     | Literal field, constant data or label                                                                                                                                        |  |  |  |

| х     | Don't care location (= 0 or 1).<br>The assembler will generate code with x = 0.<br>It is the recommended form of use for<br>compatibility with all Microchip software tools. |  |  |  |

| d     | Destination select; $d = 0$ : store result in W,<br>d = 1: store result in file register f.<br>Default is $d = 1$ .                                                          |  |  |  |

| PC    | Program Counter                                                                                                                                                              |  |  |  |

| ТО    | Time-out bit                                                                                                                                                                 |  |  |  |

| PD    | Power-down bit                                                                                                                                                               |  |  |  |

# FIGURE 15-1: GENERAL FORMAT FOR INSTRUCTIONS

#### 16.3 MPLAB C17 and MPLAB C18 C Compilers

The MPLAB C17 and MPLAB C18 Code Development Systems are complete ANSI C compilers for Microchip's PIC17CXXX and PIC18CXXX family of microcontrollers. These compilers provide powerful integration capabilities, superior code optimization and ease of use not found with other compilers.

For easy source level debugging, the compilers provide symbol information that is optimized to the MPLAB IDE debugger.

### 16.4 MPLINK Object Linker/ MPLIB Object Librarian

The MPLINK object linker combines relocatable objects created by the MPASM assembler and the MPLAB C17 and MPLAB C18 C compilers. It can link relocatable objects from precompiled libraries, using directives from a linker script.

The MPLIB object librarian manages the creation and modification of library files of pre-compiled code. When a routine from a library is called from a source file, only the modules that contain that routine will be linked in with the application. This allows large libraries to be used efficiently in many different applications.

The object linker/library features include:

- Efficient linking of single libraries instead of many smaller files

- Enhanced code maintainability by grouping related modules together

- Flexible creation of libraries with easy module listing, replacement, deletion and extraction

## 16.5 MPLAB C30 C Compiler

The MPLAB C30 C compiler is a full-featured, ANSI compliant, optimizing compiler that translates standard ANSI C programs into dsPIC30F assembly language source. The compiler also supports many command-line options and language extensions to take full advantage of the dsPIC30F device hardware capabilities, and afford fine control of the compiler code generator.

MPLAB C30 is distributed with a complete ANSI C standard library. All library functions have been validated and conform to the ANSI C library standard. The library includes functions for string manipulation, dynamic memory allocation, data conversion, time-keeping, and math functions (trigonometric, exponential and hyperbolic). The compiler provides symbolic information for high level source debugging with the MPLAB IDE.

# 16.6 MPLAB ASM30 Assembler, Linker, and Librarian

MPLAB ASM30 assembler produces relocatable machine code from symbolic assembly language for dsPIC30F devices. MPLAB C30 compiler uses the assembler to produce it's object file. The assembler generates relocatable object files that can then be archived or linked with other relocatable object files and archives to create an executable file. Notable features of the assembler include:

- Support for the entire dsPIC30F instruction set

- · Support for fixed-point and floating-point data

- Command line interface

- Rich directive set

- Flexible macro language

- MPLAB IDE compatibility

### 16.7 MPLAB SIM Software Simulator

The MPLAB SIM software simulator allows code development in a PC hosted environment by simulating the PIC series microcontrollers on an instruction level. On any given instruction, the data areas can be examined or modified and stimuli can be applied from a file, or user defined key press, to any pin. The execution can be performed in Single-Step, Execute Until Break, or Trace mode.

The MPLAB SIM simulator fully supports symbolic debugging using the MPLAB C17 and MPLAB C18 C Compilers, as well as the MPASM assembler. The software simulator offers the flexibility to develop and debug code outside of the laboratory environment, making it an excellent, economical software development tool.

## 16.8 MPLAB SIM30 Software Simulator

The MPLAB SIM30 software simulator allows code development in a PC hosted environment by simulating the dsPIC30F series microcontrollers on an instruction level. On any given instruction, the data areas can be examined or modified and stimuli can be applied from a file, or user defined key press, to any of the pins.

The MPLAB SIM30 simulator fully supports symbolic debugging using the MPLAB C30 C Compiler and MPLAB ASM30 assembler. The simulator runs in either a Command Line mode for automated tasks, or from MPLAB IDE. This high speed simulator is designed to debug, analyze and optimize time intensive DSP routines.

| Param<br>No. | Symbol  | Characteristic  |              | Min  | Тур | Max | Units | Conditions                               |

|--------------|---------|-----------------|--------------|------|-----|-----|-------|------------------------------------------|

| 90           | TSU:STA | Start condition | 100 kHz mode | 4700 | _   |     | ns    | Only relevant for Repeated Start         |

|              |         | Setup time      | 400 kHz mode | 600  |     | —   |       | condition                                |

| 91           | THD:STA | Start condition | 100 kHz mode | 4000 | _   | _   | ns    | After this period, the first clock pulse |

|              |         | Hold time       | 400 kHz mode | 600  | _   | _   |       | is generated                             |

| 92           | Tsu:sto | Stop condition  | 100 kHz mode | 4700 | _   |     | ns    |                                          |

|              |         | Setup time      | 400 kHz mode | 600  | _   | _   |       |                                          |

| 93           | THD:STO | Stop condition  | 100 kHz mode | 4000 | _   |     | ns    |                                          |

|              |         | Hold time       | 400 kHz mode | 600  | _   | —   |       |                                          |

# FIGURE 17-16: I<sup>2</sup>C BUS DATA TIMING

# PIC16F87XA

NOTES:

# PIC16F87XA

# THE MICROCHIP WEB SITE

Microchip provides online support via our WWW site at www.microchip.com. This web site is used as a means to make files and information easily available to customers. Accessible by using your favorite Internet browser, the web site contains the following information:

- Product Support Data sheets and errata, application notes and sample programs, design resources, user's guides and hardware support documents, latest software releases and archived software

- General Technical Support Frequently Asked Questions (FAQ), technical support requests, online discussion groups, Microchip consultant program member listing

- Business of Microchip Product selector and ordering guides, latest Microchip press releases, listing of seminars and events, listings of Microchip sales offices, distributors and factory representatives

# CUSTOMER CHANGE NOTIFICATION SERVICE

Microchip's customer notification service helps keep customers current on Microchip products. Subscribers will receive e-mail notification whenever there are changes, updates, revisions or errata related to a specified product family or development tool of interest.

To register, access the Microchip web site at www.microchip.com. Under "Support", click on "Customer Change Notification" and follow the registration instructions.

# **CUSTOMER SUPPORT**

Users of Microchip products can receive assistance through several channels:

- Distributor or Representative

- Local Sales Office

- Field Application Engineer (FAE)

- Technical Support

Customers should contact their distributor, representative or field application engineer (FAE) for support. Local sales offices are also available to help customers. A listing of sales offices and locations is included in the back of this document.

Technical support is available through the web site at: http://microchip.com/support