Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                            |

|----------------------------|----------------------------------------------------------------------------|

| Product Status             | Active                                                                     |

| Core Processor             | PIC                                                                        |

| Core Size                  | 8-Bit                                                                      |

| Speed                      | 10MHz                                                                      |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                          |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                      |

| Number of I/O              | 33                                                                         |

| Program Memory Size        | 14KB (8K x 14)                                                             |

| Program Memory Type        | FLASH                                                                      |

| EEPROM Size                | 256 x 8                                                                    |

| RAM Size                   | 368 x 8                                                                    |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 5.5V                                                                  |

| Data Converters            | A/D 8x10b                                                                  |

| Oscillator Type            | External                                                                   |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                          |

| Mounting Type              | Surface Mount                                                              |

| Package / Case             | 44-LCC (J-Lead)                                                            |

| Supplier Device Package    | 44-PLCC (16.59x16.59)                                                      |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16lf877at-i-l |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# 1.0 DEVICE OVERVIEW

This document contains device specific information about the following devices:

- PIC16F873A

- PIC16F874A

- PIC16F876A

- PIC16F877A

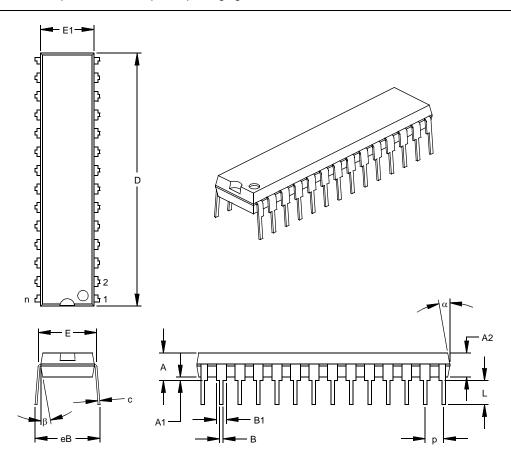

PIC16F873A/876A devices are available only in 28-pin packages, while PIC16F874A/877A devices are available in 40-pin and 44-pin packages. All devices in the PIC16F87XA family share common architecture with the following differences:

- The PIC16F873A and PIC16F874A have one-half of the total on-chip memory of the PIC16F876A and PIC16F877A

- The 28-pin devices have three I/O ports, while the 40/44-pin devices have five

- The 28-pin devices have fourteen interrupts, while the 40/44-pin devices have fifteen

- The 28-pin devices have five A/D input channels, while the 40/44-pin devices have eight

- The Parallel Slave Port is implemented only on the 40/44-pin devices

The available features are summarized in Table 1-1. Block diagrams of the PIC16F873A/876A and PIC16F874A/877A devices are provided in Figure 1-1 and Figure 1-2, respectively. The pinouts for these device families are listed in Table 1-2 and Table 1-3.

Additional information may be found in the PIC<sup>®</sup> Mid-Range Reference Manual (DS33023), which may be obtained from your local Microchip Sales Representative or downloaded from the Microchip web site. The Reference Manual should be considered a complementary document to this data sheet and is highly recommended reading for a better understanding of the device architecture and operation of the peripheral modules.

| Key Features                           | PIC16F873A                                              | PIC16F874A                                              | PIC16F876A                                              | PIC16F877A                                              |

|----------------------------------------|---------------------------------------------------------|---------------------------------------------------------|---------------------------------------------------------|---------------------------------------------------------|

| Operating Frequency                    | DC – 20 MHz                                             |

| Resets (and Delays)                    | POR, BOR<br>(PWRT, OST)                                 | POR, BOR<br>(PWRT, OST)                                 | POR, BOR<br>(PWRT, OST)                                 | POR, BOR<br>(PWRT, OST)                                 |

| Flash Program Memory<br>(14-bit words) | 4K                                                      | 4K                                                      | 8K                                                      | 8K                                                      |

| Data Memory (bytes)                    | 192                                                     | 192                                                     | 368                                                     | 368                                                     |

| EEPROM Data Memory (bytes)             | 128                                                     | 128                                                     | 256                                                     | 256                                                     |

| Interrupts                             | 14                                                      | 15                                                      | 14                                                      | 15                                                      |

| I/O Ports                              | Ports A, B, C                                           | Ports A, B, C, D, E                                     | Ports A, B, C                                           | Ports A, B, C, D, E                                     |

| Timers                                 | 3                                                       | 3                                                       | 3                                                       | 3                                                       |

| Capture/Compare/PWM modules            | 2                                                       | 2                                                       | 2                                                       | 2                                                       |

| Serial Communications                  | MSSP, USART                                             | MSSP, USART                                             | MSSP, USART                                             | MSSP, USART                                             |

| Parallel Communications                | —                                                       | PSP                                                     | _                                                       | PSP                                                     |

| 10-bit Analog-to-Digital Module        | 5 input channels                                        | 8 input channels                                        | 5 input channels                                        | 8 input channels                                        |

| Analog Comparators                     | 2                                                       | 2                                                       | 2                                                       | 2                                                       |

| Instruction Set                        | 35 Instructions                                         | 35 Instructions                                         | 35 Instructions                                         | 35 Instructions                                         |

| Packages                               | 28-pin PDIP<br>28-pin SOIC<br>28-pin SSOP<br>28-pin QFN | 40-pin PDIP<br>44-pin PLCC<br>44-pin TQFP<br>44-pin QFN | 28-pin PDIP<br>28-pin SOIC<br>28-pin SSOP<br>28-pin QFN | 40-pin PDIP<br>44-pin PLCC<br>44-pin TQFP<br>44-pin QFN |

#### TABLE 1-1:PIC16F87XA DEVICE FEATURES

| Pin Name          | PDIP<br>Pin# | PLCC<br>Pin# | TQFP<br>Pin# | QFN<br>Pin# | I/O/P<br>Type | Buffer<br>Type        | Description                                          |

|-------------------|--------------|--------------|--------------|-------------|---------------|-----------------------|------------------------------------------------------|

|                   |              |              |              |             |               |                       | PORTB is a bidirectional I/O port. PORTB can be      |

|                   |              |              |              |             |               |                       | software programmed for internal weak pull-up on all |

|                   |              |              |              |             |               |                       | inputs.                                              |

| RB0/INT           | 33           | 36           | 8            | 9           |               | TTL/ST <sup>(1)</sup> |                                                      |

| RB0               |              |              |              |             | I/O           |                       | Digital I/O.                                         |

| INT               |              |              |              |             | I             |                       | External interrupt.                                  |

| RB1               | 34           | 37           | 9            | 10          | I/O           | TTL                   | Digital I/O.                                         |

| RB2               | 35           | 38           | 10           | 11          | I/O           | TTL                   | Digital I/O.                                         |

| RB3/PGM           | 36           | 39           | 11           | 12          |               | TTL                   |                                                      |

| RB3               |              |              |              |             | I/O           |                       | Digital I/O.                                         |

| PGM               |              |              |              |             | I             |                       | Low-voltage ICSP programming enable pin.             |

| RB4               | 37           | 41           | 14           | 14          | I/O           | TTL                   | Digital I/O.                                         |

| RB5               | 38           | 42           | 15           | 15          | I/O           | TTL                   | Digital I/O.                                         |

| RB6/PGC           | 39           | 43           | 16           | 16          |               | TTL/ST <sup>(2)</sup> |                                                      |

| RB6               |              |              |              |             | I/O           |                       | Digital I/O.                                         |

| PGC               |              |              |              |             | I             |                       | In-circuit debugger and ICSP programming clock.      |

| RB7/PGD           | 40           | 44           | 17           | 17          |               | TTL/ST <sup>(2)</sup> |                                                      |

| RB7               |              |              |              |             | I/O           |                       | Digital I/O.                                         |

| PGD               |              |              |              |             | I/O           |                       | In-circuit debugger and ICSP programming data.       |

| Legend: I = input | 0            | = outpu      | t            | I/O = i     | input/outp    | out F                 | p = power                                            |

#### TABLE 1-3: PIC16F874A/877A PINOUT DESCRIPTION (CONTINUED)

Legend: I = input O = output — = Not used TTL = TTL input

ST = Schmitt Trigger input

Note 1: This buffer is a Schmitt Trigger input when configured as the external interrupt.

2: This buffer is a Schmitt Trigger input when used in Serial Programming mode.

3: This buffer is a Schmitt Trigger input when configured in RC Oscillator mode and a CMOS input otherwise.

| TABLE 1-3:         PIC16F874A/877A PINOUT DESCRIPTION (CONTINUED) |              |          |              |                 |               |                       |                                                                 |  |  |

|-------------------------------------------------------------------|--------------|----------|--------------|-----------------|---------------|-----------------------|-----------------------------------------------------------------|--|--|

| Pin Name                                                          | PDII<br>Pin# |          | TQFP<br>Pin# | QFN<br>Pin#     | I/O/P<br>Type | Buffer<br>Type        | Description                                                     |  |  |

|                                                                   |              |          |              |                 |               |                       | PORTD is a bidirectional I/O port or Parallel Slave             |  |  |

|                                                                   |              |          |              |                 |               |                       | Port when interfacing to a microprocessor bus.                  |  |  |

| RD0/PSP0                                                          | 19           | 21       | 38           | 38              |               | ST/TTL <sup>(3)</sup> |                                                                 |  |  |

| RD0                                                               |              |          |              |                 | I/O           |                       | Digital I/O.                                                    |  |  |

| PSP0                                                              |              |          |              |                 | I/O           |                       | Parallel Slave Port data.                                       |  |  |

| RD1/PSP1                                                          | 20           | 22       | 39           | 39              |               | ST/TTL <sup>(3)</sup> |                                                                 |  |  |

| RD1                                                               |              |          |              |                 | I/O           |                       | Digital I/O.                                                    |  |  |

| PSP1                                                              |              |          |              |                 | I/O           | (2)                   | Parallel Slave Port data.                                       |  |  |

| RD2/PSP2                                                          | 21           | 23       | 40           | 40              |               | ST/TTL <sup>(3)</sup> |                                                                 |  |  |

| RD2<br>PSP2                                                       |              |          |              |                 | I/O<br>I/O    |                       | Digital I/O.<br>Parallel Slave Port data.                       |  |  |

| -                                                                 |              |          |              |                 | 1/0           | o = (=== (3)          | Parallel Slave Port data.                                       |  |  |

| RD3/PSP3                                                          | 22           | 24       | 41           | 41              | I/O           | ST/TTL <sup>(3)</sup> |                                                                 |  |  |

| RD3<br>PSP3                                                       |              |          |              |                 | 1/O<br>1/O    |                       | Digital I/O.<br>Parallel Slave Port data.                       |  |  |

|                                                                   | 07           | 20       | 0            | 0               | 1/0           | ST/TTL <sup>(3)</sup> |                                                                 |  |  |

| RD4/PSP4<br>RD4                                                   | 27           | 30       | 2            | 2               | I/O           | 51/11L*/              | Digital I/O.                                                    |  |  |

| PSP4                                                              |              |          |              |                 | 1/O           |                       | Parallel Slave Port data.                                       |  |  |

| RD5/PSP5                                                          | 28           | 31       | 3            | 3               |               | ST/TTL <sup>(3)</sup> |                                                                 |  |  |

| RD5                                                               | 20           | 51       | 5            | 5               | I/O           | 31/112.7              | Digital I/O.                                                    |  |  |

| PSP5                                                              |              |          |              |                 | I/O           |                       | Parallel Slave Port data.                                       |  |  |

| RD6/PSP6                                                          | 29           | 32       | 4            | 4               |               | ST/TTL <sup>(3)</sup> |                                                                 |  |  |

| RD6                                                               | 20           | 02       | -            | -               | I/O           | OWITE                 | Digital I/O.                                                    |  |  |

| PSP6                                                              |              |          |              |                 | I/O           |                       | Parallel Slave Port data.                                       |  |  |

| RD7/PSP7                                                          | 30           | 33       | 5            | 5               |               | ST/TTL <sup>(3)</sup> |                                                                 |  |  |

| RD7                                                               |              |          | Ũ            | Ŭ               | I/O           | 0.,                   | Digital I/O.                                                    |  |  |

| PSP7                                                              |              |          |              |                 | I/O           |                       | Parallel Slave Port data.                                       |  |  |

|                                                                   |              |          |              |                 |               |                       | PORTE is a bidirectional I/O port.                              |  |  |

| RE0/RD/AN5                                                        | 8            | 9        | 25           | 25              |               | ST/TTL(3)             |                                                                 |  |  |

| RE0                                                               | _            | _        | _            |                 | I/O           |                       | Digital I/O.                                                    |  |  |

| RD                                                                |              |          |              |                 | I             |                       | Read control for Parallel Slave Port.                           |  |  |

| AN5                                                               |              |          |              |                 | I             |                       | Analog input 5.                                                 |  |  |

| RE1/WR/AN6                                                        | 9            | 10       | 26           | 26              |               | ST/TTL <sup>(3)</sup> |                                                                 |  |  |

| RE1                                                               |              |          |              |                 | I/O           |                       | Digital I/O.                                                    |  |  |

| WR                                                                |              |          |              |                 |               |                       | Write control for Parallel Slave Port.                          |  |  |

| AN6                                                               |              |          |              |                 | I             | (2)                   | Analog input 6.                                                 |  |  |

| RE2/CS/AN7                                                        | 10           | 11       | 27           | 27              |               | ST/TTL <sup>(3)</sup> |                                                                 |  |  |

| RE2<br>CS                                                         |              |          |              |                 | I/O           |                       | Digital I/O.<br>Chip coloct control for Parallel Slove Part     |  |  |

| AN7                                                               |              |          |              |                 |               |                       | Chip select control for Parallel Slave Port.<br>Analog input 7. |  |  |

| Vss                                                               | 10.0         | 1 13, 34 | 6.20         | 6 20            | P             |                       |                                                                 |  |  |

| v                                                                 | 12, 3        | 1 13, 34 | 6, 29        | 6, 30,<br>31    |               |                       | Ground reference for logic and I/O pins.                        |  |  |

| Vdd                                                               | 11, 3        | 2 12, 35 | 7, 28        | 7, 8,<br>28, 29 | Р             | —                     | Positive supply for logic and I/O pins.                         |  |  |

| NC                                                                | <u> </u>     | 1, 17,   | 12,13,       | 13              |               | _                     | These pins are not internally connected. These pins             |  |  |

|                                                                   | 1            | 28, 40   | 33, 34       | -               |               |                       | should be left unconnected.                                     |  |  |

#### TARI E 1-3. PIC16E8744/8774 PINOLIT DESCRIPTION (CONTINUED)

= input I. — = Not used TTL = TTL input

I/O = input/output I ST = Schmitt Trigger input

Note 1: This buffer is a Schmitt Trigger input when configured as the external interrupt.2: This buffer is a Schmitt Trigger input when used in Serial Programming mode.

3: This buffer is a Schmitt Trigger input when configured in RC Oscillator mode and a CMOS input otherwise.

NOTES:

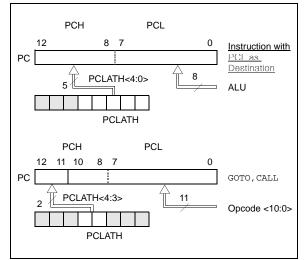

### 2.3 PCL and PCLATH

The Program Counter (PC) is 13 bits wide. The low byte comes from the PCL register which is a readable and writable register. The upper bits (PC<12:8>) are not readable, but are indirectly writable through the PCLATH register. On any Reset, the upper bits of the PC will be cleared. Figure 2-5 shows the two situations for the loading of the PC. The upper example in the figure shows how the PC is loaded on a write to PCL (PCLATH<4:0>  $\rightarrow$  PCH). The lower example in the figure shows how the PC is loaded during a CALL or GOTO instruction (PCLATH<4:3>  $\rightarrow$  PCH).

#### FIGURE 2-5: LOADING OF PC IN DIFFERENT SITUATIONS

#### 2.3.1 COMPUTED GOTO

A computed GOTO is accomplished by adding an offset to the program counter (ADDWF PCL). When doing a table read using a computed GOTO method, care should be exercised if the table location crosses a PCL memory boundary (each 256-byte block). Refer to the application note, *AN556, "Implementing a Table Read"* (DS00556).

#### 2.3.2 STACK

The PIC16F87XA family has an 8-level deep x 13-bit wide hardware stack. The stack space is not part of either program or data space and the stack pointer is not readable or writable. The PC is PUSHed onto the stack when a CALL instruction is executed, or an interrupt causes a branch. The stack is POP'ed in the event of a RETURN, RETLW or a RETFIE instruction execution. PCLATH is not affected by a PUSH or POP operation.

The stack operates as a circular buffer. This means that after the stack has been PUSHed eight times, the ninth push overwrites the value that was stored from the first push. The tenth push overwrites the second push (and so on).

- **Note 1:** There are no status bits to indicate stack overflow or stack underflow conditions.

- 2: There are no instructions/mnemonics called PUSH or POP. These are actions that occur from the execution of the CALL, RETURN, RETLW and RETFIE instructions or the vectoring to an interrupt address.

### 2.4 Program Memory Paging

All PIC16F87XA devices are capable of addressing a continuous 8K word block of program memory. The CALL and GOTO instructions provide only 11 bits of address to allow branching within any 2K program memory page. When doing a CALL or GOTO instruction, the upper 2 bits of the address are provided by PCLATH<4:3>. When doing a CALL or GOTO instruction, the user must ensure that the page select bits are programmed so that the desired program memory page is addressed. If a return from a CALL instruction (or interrupt) is executed, the entire 13-bit PC is popped off the stack. Therefore, manipulation of the PCLATH<4:3> bits is not required for the RETURN instructions (which POPs the address from the stack).

| Note: | The contents of the PCLATH register are    |  |  |  |  |  |  |

|-------|--------------------------------------------|--|--|--|--|--|--|

|       | unchanged after a RETURN or RETFIE         |  |  |  |  |  |  |

|       | instruction is executed. The user must     |  |  |  |  |  |  |

|       | rewrite the contents of the PCLATH regis-  |  |  |  |  |  |  |

|       | ter for any subsequent subroutine calls or |  |  |  |  |  |  |

|       | GOTO instructions.                         |  |  |  |  |  |  |

Example 2-1 shows the calling of a subroutine in page 1 of the program memory. This example assumes that PCLATH is saved and restored by the Interrupt Service Routine (if interrupts are used).

#### EXAMPLE 2-1: CALL OF A SUBROUTINE IN PAGE 1 FROM PAGE 0

|         | ORG 0x500    |                     |

|---------|--------------|---------------------|

|         | BCF PCLATH,4 |                     |

|         | BSF PCLATH,3 | ;Select page 1      |

|         |              | ; (800h-FFFh)       |

|         | CALL SUB1_P1 | ;Call subroutine in |

|         | :            | ;page 1 (800h-FFFh) |

|         | :            |                     |

|         | ORG 0x900    | ;page 1 (800h-FFFh) |

| SUB1_P1 |              |                     |

|         | :            | ;called subroutine  |

|         |              | ;page 1 (800h-FFFh) |

|         | :            |                     |

|         | RETURN       | ;return to          |

|         |              | ;Call subroutine    |

|         |              | ;in page 0          |

|         |              | ;(000h-7FFh)        |

|         |              |                     |

| REGISTER 3-1: | EECON1 REGISTER (ADDRESS 18Ch)                                                                                                                                                                                   |                                                                                                                                                                                      |                 |              |          |           |                |       |  |  |

|---------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|--------------|----------|-----------|----------------|-------|--|--|

|               | R/W-x                                                                                                                                                                                                            | U-0                                                                                                                                                                                  | U-0             | U-0          | R/W-x    | R/W-0     | R/S-0          | R/S-0 |  |  |

|               | EEPGD                                                                                                                                                                                                            | _                                                                                                                                                                                    | _               | _            | WRERR    | WREN      | WR             | RD    |  |  |

|               | bit 7                                                                                                                                                                                                            |                                                                                                                                                                                      |                 |              |          |           |                | bit 0 |  |  |

| bit 7         | EEPGD: Pi                                                                                                                                                                                                        | ogram/Data                                                                                                                                                                           | EEPROM          | Select bit   |          |           |                |       |  |  |

|               | 0 = Access                                                                                                                                                                                                       | <ul> <li>1 = Accesses program memory</li> <li>0 = Accesses data memory</li> <li>Reads '0' after a POR; this bit cannot be changed while a write operation is in progress.</li> </ul> |                 |              |          |           |                |       |  |  |

| bit 6-4       | Unimplem                                                                                                                                                                                                         | ented: Read                                                                                                                                                                          | <b>d as</b> '0' |              |          | ·         |                |       |  |  |

| bit 3         | WRERR: E                                                                                                                                                                                                         | EPROM Er                                                                                                                                                                             | ror Flag bit    |              |          |           |                |       |  |  |

|               | <ul> <li>1 = A write operation is prematurely terminated (any MCLR or any WDT Reset during normal operation)</li> <li>0 = The write operation completed</li> </ul>                                               |                                                                                                                                                                                      |                 |              |          |           |                |       |  |  |

| bit 2         | WREN: EE                                                                                                                                                                                                         | PROM Writ                                                                                                                                                                            | e Enable bit    |              |          |           |                |       |  |  |

|               |                                                                                                                                                                                                                  | write cycles<br>write to the                                                                                                                                                         |                 |              |          |           |                |       |  |  |

| bit 1         | WR: Write                                                                                                                                                                                                        | Control bit                                                                                                                                                                          |                 |              |          |           |                |       |  |  |

|               | <ul> <li>1 = Initiates a write cycle. The bit is cleared by hardware once write is complete. The WR bit can only be set (not cleared) in software.</li> <li>0 = Write cycle to the EEPROM is complete</li> </ul> |                                                                                                                                                                                      |                 |              |          |           |                |       |  |  |

| bit 0         | RD: Read                                                                                                                                                                                                         | Control bit                                                                                                                                                                          |                 |              |          |           |                |       |  |  |

|               | <ul> <li>1 = Initiates an EEPROM read; RD is cleared in hardware. The RD bit can only be set (not cleared) in software.</li> <li>0 = Does not initiate an EEPROM read</li> </ul>                                 |                                                                                                                                                                                      |                 |              |          |           |                |       |  |  |

|               | Legend:                                                                                                                                                                                                          |                                                                                                                                                                                      |                 |              |          |           |                |       |  |  |

|               | R = Reada                                                                                                                                                                                                        | ble bit                                                                                                                                                                              | W = W           | /ritable bit | U = Unim | plemented | bit, read as ' | 0'    |  |  |

| Legend:            |                  |                          |                  |

|--------------------|------------------|--------------------------|------------------|

| R = Readable bit   | W = Writable bit | U = Unimplemented bit,   | read as '0'      |

| - n = Value at POR | '1' = Bit is set | '0' = Bit is cleared x = | = Bit is unknown |

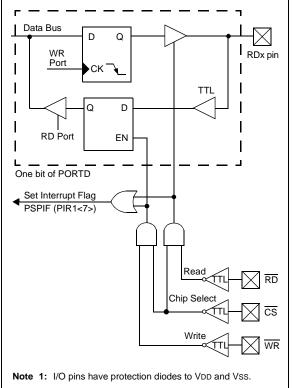

### 4.6 Parallel Slave Port

The Parallel Slave Port (PSP) is not implemented on the PIC16F873A or PIC16F876A.

PORTD operates as an 8-bit wide Parallel Slave Port, or microprocessor port, when control bit PSPMODE (TRISE<4>) is set. In Slave mode, it is asynchronously readable and writable by the external world through RD control input pin, RE0/RD/AN5, and WR control input pin, RE1/WR/AN6.

The PSP can directly interface to an 8-bit microprocessor data bus. The external microprocessor can read or write the PORTD latch as an 8-bit latch. Setting bit PSPMODE enables port pin RE0/RD/AN5 to be the RD input, RE1/WR/AN6 to be the WR input and RE2/CS/AN7 to be the CS (Chip Select) input. For this functionality, the corresponding data direction bits of the TRISE register (TRISE<2:0>) must be configured as inputs (set). The A/D port configuration bits, PCFG3:PCFG0 (ADCON1<3:0>), must be set to configure pins RE2:RE0 as digital I/O.

There are actually two 8-bit latches: one for data output and one for data input. The user writes 8-bit data to the PORTD data latch and reads data from the port pin latch (note that they have the same address). In this mode, the TRISD register is ignored since the external device is controlling the direction of data flow.

A write to the PSP occurs when both the  $\overline{CS}$  and  $\overline{WR}$ lines are first detected low. When either the  $\overline{CS}$  or  $\overline{WR}$ lines become high (level triggered), the Input Buffer Full (IBF) status flag bit (TRISE<7>) is set on the Q4 clock cycle, following the next Q2 cycle, to signal the write is complete (Figure 4-11). The interrupt flag bit, PSPIF (PIR1<7>), is also set on the same Q4 clock cycle. IBF can only be cleared by reading the PORTD input latch. The Input Buffer Overflow (IBOV) status flag bit (TRISE<5>) is set if a second write to the PSP is attempted when the previous byte has not been read out of the buffer.

A read from the PSP occurs when both the CS and RD lines are first detected low. The Output Buffer Full (OBF) status flag bit (TRISE<6>) is cleared immediately (Figure 4-12), indicating that the PORTD latch is waiting to be read by the external bus. When either the CS or RD pin becomes high (level triggered), the interrupt flag bit PSPIF is set on the Q4 clock cycle, following the next Q2 cycle, indicating that the read is complete. OBF remains low until data is written to PORTD by the user firmware. When not in PSP mode, the IBF and OBF bits are held clear. However, if flag bit IBOV was previously set, it must be cleared in firmware.

An interrupt is generated and latched into flag bit PSPIF when a read or write operation is completed. PSPIF must be cleared by the user in firmware and the interrupt can be disabled by clearing the interrupt enable bit PSPIE (PIE1<7>).

#### 9.4.10 I<sup>2</sup>C MASTER MODE TRANSMISSION

Transmission of a data byte, a 7-bit address or the other half of a 10-bit address is accomplished by simply writing a value to the SSPBUF register. This action will set the Buffer Full flag bit, BF, and allow the Baud Rate Generator to begin counting and start the next transmission. Each bit of address/data will be shifted out onto the SDA pin after the falling edge of SCL is asserted (see data hold time specification, parameter #106). SCL is held low for one Baud Rate Generator rollover count (TBRG). Data should be valid before SCL is released high (see data setup time specification, parameter #107). When the SCL pin is released high, it is held that way for TBRG. The data on the SDA pin must remain stable for that duration and some hold time after the next falling edge of SCL. After the eighth bit is shifted out (the falling edge of the eighth clock), the BF flag is cleared and the master releases SDA. This allows the slave device being addressed to respond with an ACK bit during the ninth bit time, if an address match occurred or if data was received properly. The status of ACK is written into the ACKDT bit on the falling edge of the ninth clock. If the master receives an Acknowledge, the Acknowledge Status bit, ACKSTAT, is cleared. If not, the bit is set. After the ninth clock, the SSPIF bit is set and the master clock (Baud Rate Generator) is suspended until the next data byte is loaded into the SSPBUF, leaving SCL low and SDA unchanged (Figure 9-21).

After the write to the SSPBUF, each bit of address will be shifted out on the falling edge of SCL, until all seven address bits and the R/W bit are completed. On the falling edge of the eighth clock, the master will deassert the SDA pin, allowing the slave to respond with an Acknowledge. On the falling edge of the ninth clock, the master will sample the SDA pin to see if the address was recognized by a slave. The status of the ACK bit is loaded into the ACKSTAT status bit (SSPCON2<6>). Following the falling edge of the ninth clock transmission of the address, the SSPIF is set, the BF flag is cleared and the Baud Rate Generator is turned off until another write to the SSPBUF takes place, holding SCL low and allowing SDA to float.

#### 9.4.10.1 BF Status Flag

In Transmit mode, the BF bit (SSPSTAT<0>) is set when the CPU writes to SSPBUF and is cleared when all eight bits are shifted out.

#### 9.4.10.2 WCOL Status Flag

If the user writes the SSPBUF when a transmit is already in progress (i.e., SSPSR is still shifting out a data byte), the WCOL is set and the contents of the buffer are unchanged (the write doesn't occur).

WCOL must be cleared in software.

#### 9.4.10.3 ACKSTAT Status Flag

In Transmit mode, the ACKSTAT bit (SSPCON2<6>) is cleared when the slave has sent an Acknowledge  $(\overline{ACK} = 0)$  and is set when the slave does Not Acknowledge  $(\overline{ACK} = 1)$ . A slave sends an Acknowledge when it has recognized its address (including a general call) or when the slave has properly received its data.

#### 9.4.11 I<sup>2</sup>C MASTER MODE RECEPTION

Master mode reception is enabled by programming the Receive Enable bit, RCEN (SSPCON2<3>).

Note: The MSSP module must be in an Idle state before the RCEN bit is set or the RCEN bit will be disregarded.

The Baud Rate Generator begins counting and on each rollover, the state of the SCL pin changes (high to low/ low to high) and data is shifted into the SSPSR. After the falling edge of the eighth clock, the receive enable flag is automatically cleared, the contents of the SSPSR are loaded into the SSPBUF, the BF flag bit is set, the SSPIF flag bit is set and the Baud Rate Generator is suspended from counting, holding SCL low. The MSSP is now in Idle state, awaiting the next command. When the buffer is read by the CPU, the BF flag bit is automatically cleared. The user can then send an Acknowledge bit at the end of reception by setting the Acknowledge Sequence Enable bit, ACKEN (SSPCON2<4>).

#### 9.4.11.1 BF Status Flag

In receive operation, the BF bit is set when an address or data byte is loaded into SSPBUF from SSPSR. It is cleared when the SSPBUF register is read.

#### 9.4.11.2 SSPOV Status Flag

In receive operation, the SSPOV bit is set when 8 bits are received into the SSPSR and the BF flag bit is already set from a previous reception.

#### 9.4.11.3 WCOL Status Flag

If the user writes the SSPBUF when a receive is already in progress (i.e., SSPSR is still shifting in a data byte), the WCOL bit is set and the contents of the buffer are unchanged (the write doesn't occur).

| Address                | Name   | Bit 7                           | Bit 6     | Bit 5  | Bit 4 | Bit 3 | Bit 2  | Bit 1  | Bit 0  | Value on:<br>POR, BOR | Value on<br>all other<br>Resets |

|------------------------|--------|---------------------------------|-----------|--------|-------|-------|--------|--------|--------|-----------------------|---------------------------------|

| 0Bh, 8Bh,<br>10Bh,18Bh | INTCON | GIE                             | PEIE      | TMR0IE | INTE  | RBIE  | TMR0IF | INTF   | R0IF   | 0000 000x             | 0000 000u                       |

| 0Ch                    | PIR1   | PSPIF <sup>(1)</sup>            | ADIF      | RCIF   | TXIF  | SSPIF | CCP1IF | TMR2IF | TMR1IF | 0000 0000             | 0000 0000                       |

| 18h                    | RCSTA  | SPEN                            | RX9       | SREN   | CREN  |       | FERR   | OERR   | RX9D   | x00- 0000             | 0000 -00x                       |

| 19h                    | TXREG  | USART Tr                        | ansmit Re | gister |       |       |        |        |        | 0000 0000             | 0000 0000                       |

| 8Ch                    | PIE1   | PSPIE <sup>(1)</sup>            | ADIE      | RCIE   | TXIE  | SSPIE | CCP1IE | TMR2IE | TMR1IE | 0000 0000             | 0000 0000                       |

| 98h                    | TXSTA  | CSRC                            | TX9       | TXEN   | SYNC  | —     | BRGH   | TRMT   | TX9D   | 0000 -010             | 0000 -010                       |

| 99h                    | SPBRG  | RG Baud Rate Generator Register |           |        |       |       |        |        |        | 0000 0000             | 0000 0000                       |

Legend: x = unknown, - = unimplemented, read as '0'. Shaded cells are not used for synchronous master transmission.

Note 1: Bits PSPIE and PSPIF are reserved on 28-pin devices; always maintain these bits clear.

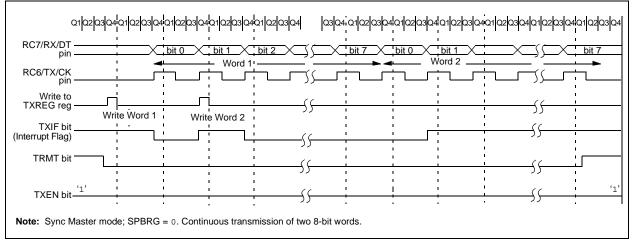

#### FIGURE 10-9: SYNCHRONOUS TRANSMISSION

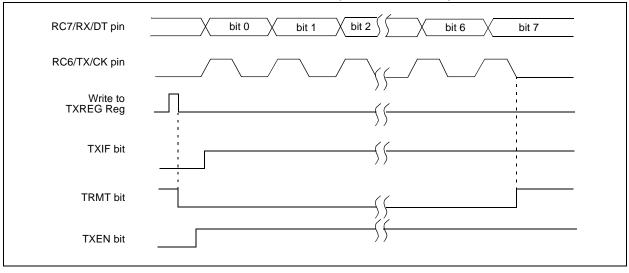

#### FIGURE 10-10: SYNCHRONOUS TRANSMISSION (THROUGH TXEN)

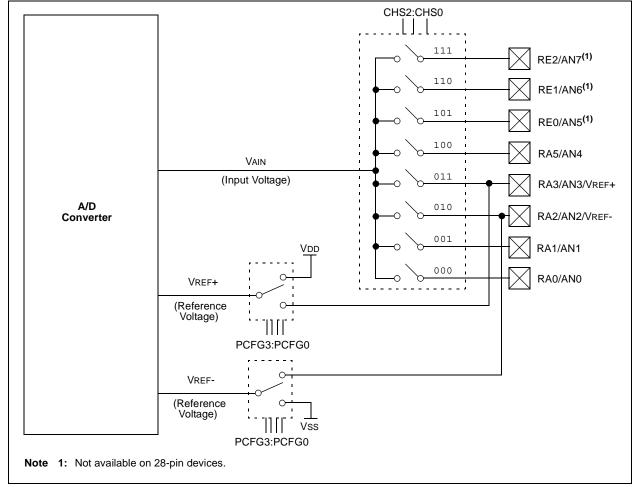

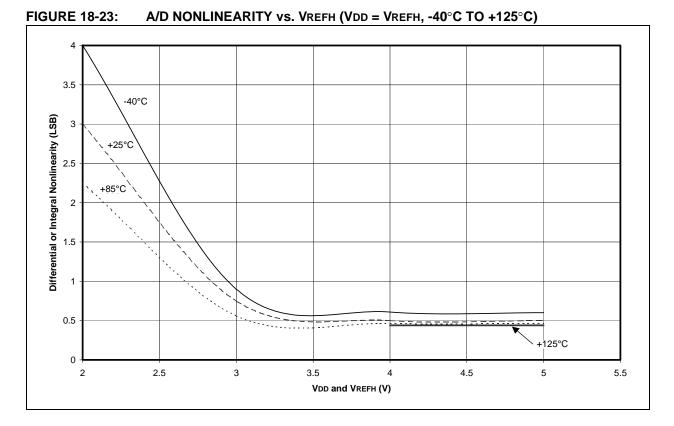

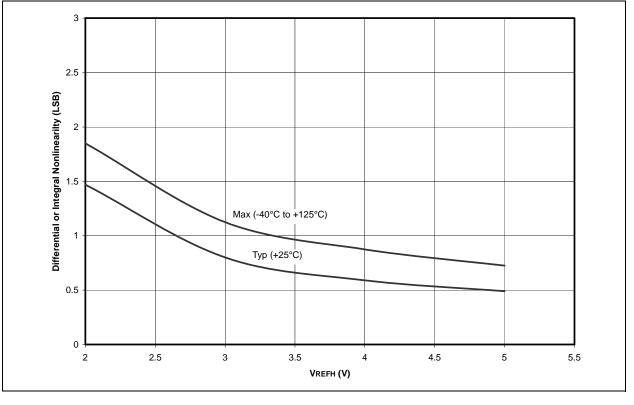

The ADRESH:ADRESL registers contain the 10-bit result of the A/D conversion. When the A/D conversion is complete, the result is loaded into this A/D Result register pair, the GO/DONE bit (ADCON0<2>) is cleared and the A/D interrupt flag bit ADIF is set. The block diagram of the A/D module is shown in Figure 11-1.

After the A/D module has been configured as desired, the selected channel must be acquired before the conversion is started. The analog input channels must have their corresponding TRIS bits selected as inputs.

To determine sample time, see **Section 11.1 "A/D Acquisition Requirements"**. After this acquisition time has elapsed, the A/D conversion can be started.

To do an A/D Conversion, follow these steps:

- 1. Configure the A/D module:

- Configure analog pins/voltage reference and digital I/O (ADCON1)

- Select A/D input channel (ADCON0)

- Select A/D conversion clock (ADCON0)

- Turn on A/D module (ADCON0)

- 2. Configure A/D interrupt (if desired):

- Clear ADIF bit

- Set ADIE bit

- Set PEIE bit

- Set GIE bit

- 3. Wait the required acquisition time.

- 4. Start conversion:

- Set GO/DONE bit (ADCON0)

- 5. Wait for A/D conversion to complete by either:

- Polling for the GO/DONE bit to be cleared (interrupts disabled); OR

- Waiting for the A/D interrupt

- 6. Read A/D Result register pair (ADRESH:ADRESL), clear bit ADIF if required.

- 7. For the next conversion, go to step 1 or step 2 as required. The A/D conversion time per bit is defined as TAD.

### FIGURE 11-1: A/D BLOCK DIAGRAM

## 12.0 COMPARATOR MODULE

The comparator module contains two analog comparators. The inputs to the comparators are multiplexed with I/O port pins RA0 through RA3, while the outputs are multiplexed to pins RA4 and RA5. The on-chip voltage reference (Section 13.0 "Comparator Voltage Reference Module") can also be an input to the comparators. The CMCON register (Register 12-1) controls the comparator input and output multiplexers. A block diagram of the various comparator configurations is shown in Figure 12-1.

|       | R-0                                                              | R-0                                                | R/W-0        | R/W-0       | R/W-0       | R/W-1      | R/W-1        | R/W-1  |  |  |

|-------|------------------------------------------------------------------|----------------------------------------------------|--------------|-------------|-------------|------------|--------------|--------|--|--|

|       | C2OUT                                                            | C1OUT                                              | C2INV        | C1INV       | CIS         | CM2        | CM1          | CM0    |  |  |

|       | bit 7                                                            |                                                    |              | •           | •           |            |              | bit 0  |  |  |

|       |                                                                  |                                                    |              |             |             |            |              |        |  |  |

| bit 7 | <b>C2OUT</b> : Co                                                | omparator 2                                        | Output bit   |             |             |            |              |        |  |  |

|       | When C2IN                                                        |                                                    |              |             |             |            |              |        |  |  |

|       | -                                                                | + > C2 VIN-<br>+ < C2 VIN-                         |              |             |             |            |              |        |  |  |

|       | 0 = C2 VIN<br>When C2IN                                          |                                                    |              |             |             |            |              |        |  |  |

|       |                                                                  | <u>nv = ⊥.</u><br>+ < C2 VIN-                      |              |             |             |            |              |        |  |  |

|       |                                                                  | + > C2 VIN-                                        |              |             |             |            |              |        |  |  |

| bit 6 | <b>C10UT</b> : Co                                                | omparator 1                                        | Output bit   |             |             |            |              |        |  |  |

|       | When C1IN                                                        |                                                    |              |             |             |            |              |        |  |  |

|       |                                                                  | + > C1 VIN-                                        |              |             |             |            |              |        |  |  |

|       |                                                                  | + < C1 VIN-                                        |              |             |             |            |              |        |  |  |

|       | When C1IN                                                        |                                                    |              |             |             |            |              |        |  |  |

|       |                                                                  | + < C1 VIN-<br>+ > C1 VIN-                         |              |             |             |            |              |        |  |  |

| bit 5 |                                                                  | mparator 2 (                                       | Dutput Inver | sion bit    |             |            |              |        |  |  |

|       |                                                                  | put inverted                                       |              |             |             |            |              |        |  |  |

|       |                                                                  | put not inver                                      | ted          |             |             |            |              |        |  |  |

| bit 4 | C1INV: Co                                                        | mparator 1 C                                       | Dutput Inver | sion bit    |             |            |              |        |  |  |

|       | 1 = C1 out                                                       | put inverted                                       |              |             |             |            |              |        |  |  |

|       | 0 = C1 out                                                       | put not inver                                      | ted          |             |             |            |              |        |  |  |

| bit 3 | CIS: Comp                                                        | arator Input                                       | Switch bit   |             |             |            |              |        |  |  |

|       |                                                                  | 2:CM0 = 110                                        | -            |             |             |            |              |        |  |  |

|       | -                                                                | I- connects t                                      |              |             |             |            |              |        |  |  |

|       | -                                                                | <ul> <li>connects t</li> <li>connects t</li> </ul> |              |             |             |            |              |        |  |  |

|       |                                                                  | - connects t                                       |              |             |             |            |              |        |  |  |

| bit 2 | CM2:CM0:                                                         | Comparato                                          | r Mode bits  |             |             |            |              |        |  |  |

|       | Figure 12-1 shows the Comparator modes and CM2:CM0 bit settings. |                                                    |              |             |             |            |              |        |  |  |

|       | -                                                                |                                                    |              |             |             | -          |              |        |  |  |

|       | Legend:                                                          |                                                    |              |             |             |            |              |        |  |  |

|       | R = Reada                                                        | ble bit                                            | W = W        | ritable bit | U = Unin    | nplemented | bit, read as | ʻ0'    |  |  |

|       | - n = Value                                                      | at POR                                             | '1' = B      | it is set   | '0' = Bit i | s cleared  | x = Bit is u | nknown |  |  |

|       |                                                                  |                                                    |              |             |             |            |              |        |  |  |

| mparators. |  |  |  |

|------------|--|--|--|

|            |  |  |  |

|            |  |  |  |

**REGISTER 12-1: CMCON REGISTER**

| TABLE 15-2: PIC16 | F87XA INSTRUCTION SET |

|-------------------|-----------------------|

|-------------------|-----------------------|

| Mnemonic,<br>Operands                  |      | Description                                    | Cycles        | 14-Bit Opcode |      |      |      | Status   | Notes |

|----------------------------------------|------|------------------------------------------------|---------------|---------------|------|------|------|----------|-------|

|                                        |      | Description                                    | Cycles        | MSb           |      |      | LSb  | Affected | Notes |

| BYTE-ORIENTED FILE REGISTER OPERATIONS |      |                                                |               |               |      |      |      |          |       |

| ADDWF                                  | f, d | Add W and f                                    | 1             | 00            | 0111 | dfff | ffff | C,DC,Z   | 1,2   |

| ANDWF                                  | f, d | AND W with f                                   | 1             | 00            | 0101 | dfff | ffff | Z        | 1,2   |

| CLRF                                   | f    | Clear f                                        | 1             | 00            | 0001 | lfff | ffff | Z        | 2     |

| CLRW                                   | -    | Clear W                                        | 1             | 00            | 0001 | 0xxx | xxxx | Z        |       |

| COMF                                   | f, d | Complement f                                   | 1             | 00            | 1001 | dfff | ffff | Z        | 1,2   |

| DECF                                   | f, d | Decrement f                                    | 1             | 00            | 0011 | dfff | ffff | Z        | 1,2   |

| DECFSZ                                 | f, d | Decrement f, Skip if 0                         | 1(2)          | 00            | 1011 | dfff | ffff |          | 1,2,3 |

| INCF                                   | f, d | Increment f                                    | 1             | 00            | 1010 | dfff | ffff | Z        | 1,2   |

| INCFSZ                                 | f, d | Increment f, Skip if 0                         | 1(2)          | 00            | 1111 | dfff | ffff |          | 1,2,3 |

| IORWF                                  | f, d | Inclusive OR W with f                          | 1             | 00            | 0100 | dfff | ffff | Z        | 1,2   |

| MOVF                                   | f, d | Move f                                         | 1             | 00            | 1000 | dfff | ffff | Z        | 1,2   |

| MOVWF                                  | f    | Move W to f                                    | 1             | 00            | 0000 | lfff | ffff |          |       |

| NOP                                    | -    | No Operation                                   | 1             | 00            | 0000 | 0xx0 | 0000 |          |       |

| RLF                                    | f, d | Rotate Left f through Carry                    | 1             | 00            | 1101 | dfff | ffff | С        | 1,2   |

| RRF                                    | f, d | Rotate Right f through Carry                   | 1             | 00            | 1100 | dfff | ffff | С        | 1,2   |

| SUBWF                                  | f, d | Subtract W from f                              | 1             | 00            | 0010 | dfff | ffff | C,DC,Z   | 1,2   |

| SWAPF                                  | f, d | Swap nibbles in f                              | 1             | 00            | 1110 | dfff | ffff |          | 1,2   |

| XORWF                                  | f, d | Exclusive OR W with f                          | 1             | 00            | 0110 | dfff | ffff | Z        | 1,2   |

|                                        |      | BIT-ORIENTED FILE                              | REGISTER OPER | ATION         | ١S   |      |      |          |       |

| BCF                                    | f, b | Bit Clear f                                    | 1             | 01            | 00bb | bfff | ffff |          | 1,2   |

| BSF                                    | f, b | Bit Set f                                      | 1             | 01            | 01bb | bfff | ffff |          | 1,2   |

| BTFSC                                  | f, b | Bit Test f, Skip if Clear                      | 1 (2)         | 01            | 10bb | bfff | ffff |          | 3     |

| BTFSS                                  | f, b | Bit Test f, Skip if Set                        | 1 (2)         | 01            | 11bb | bfff | ffff |          | 3     |

|                                        |      | LITERAL AND CO                                 | NTROL OPERAT  | IONS          |      |      |      |          |       |

| ADDLW                                  | k    | Add Literal and W                              | 1             | 11            | 111x | kkkk | kkkk | C,DC,Z   |       |

| ANDLW                                  | k    | AND Literal with W                             | 1             | 11            | 1001 | kkkk | kkkk | Z        |       |

| CALL                                   | k    | Call Subroutine                                | 2             | 10            | 0kkk | kkkk | kkkk |          |       |

| CLRWDT                                 | -    | Clear Watchdog Timer                           | 1             | 00            | 0000 | 0110 | 0100 | TO,PD    |       |

| GOTO                                   | k    | Go to Address                                  | 2             | 10            | 1kkk | kkkk | kkkk | -        |       |

| IORLW                                  | k    | Inclusive OR Literal with W                    | 1             | 11            | 1000 | kkkk | kkkk | Z        |       |

| MOVLW                                  | k    | Move Literal to W                              | 1             | 11            | 00xx | kkkk | kkkk |          |       |

| RETFIE                                 | -    | Return from Interrupt                          | 2             | 00            | 0000 | 0000 | 1001 |          |       |

| RETLW                                  | k    | Return with Literal in W                       | 2             | 11            | 01xx | kkkk |      |          |       |

| RETURN                                 | -    | Return from Subroutine                         | 2             | 00            | 0000 | 0000 | 1000 |          |       |

| SLEEP                                  | -    | Go into Standby mode                           | 1             | 00            | 0000 | 0110 | 0011 | TO,PD    |       |

| SUBLW                                  | k    | Subtract W from Literal                        | 1             | 11            |      | kkkk |      | C,DC,Z   |       |

| XORLW                                  | k    | Exclusive OR Literal with W                    | 1             | 11            | 1010 | kkkk |      | Z        |       |

| Note 1:                                |      | I/O register is modified as a function of itse |               |               |      |      |      |          |       |

Note 1: When an I/O register is modified as a function of itself (e.g., MOVF PORTE, 1), the value used will be that value present on the pins themselves. For example, if the data latch is '1' for a pin configured as input and is driven low by an external device, the data will be written back with a '0'.

2: If this instruction is executed on the TMR0 register (and where applicable, d = 1), the prescaler will be cleared if assigned to the Timer0 module.

3: If Program Counter (PC) is modified, or a conditional test is true, the instruction requires two cycles. The second cycle is executed as a NOP.

**Note:** Additional information on the mid-range instruction set is available in the PIC<sup>®</sup> Mid-Range MCU Family Reference Manual (DS33023).

| RLF              | Rotate Left f through Carry                                                                                                                                                                                       |  |  |  |  |  |  |

|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

| Syntax:          | [ <i>label</i> ] RLF f,d                                                                                                                                                                                          |  |  |  |  |  |  |

| Operands:        | $\begin{array}{l} 0\leq f\leq 127\\ d\in [0,1] \end{array}$                                                                                                                                                       |  |  |  |  |  |  |

| Operation:       | See description below                                                                                                                                                                                             |  |  |  |  |  |  |

| Status Affected: | С                                                                                                                                                                                                                 |  |  |  |  |  |  |

| Description:     | The contents of register 'f' are<br>rotated one bit to the left through the<br>Carry flag. If 'd' is '0', the result is<br>placed in the W register. If 'd' is '1',<br>the result is stored back in register 'f'. |  |  |  |  |  |  |

| Syntax:          | [label] SLEEP                                                                                                                                                                                                                          |

|------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Operands:        | None                                                                                                                                                                                                                                   |

| Operation:       | $\begin{array}{l} 00h \rightarrow WDT, \\ 0 \rightarrow WDT \ prescaler, \\ 1 \rightarrow \overline{TO}, \\ 0 \rightarrow \overline{PD} \end{array}$                                                                                   |

| Status Affected: | TO, PD                                                                                                                                                                                                                                 |

| Description:     | The power-down status bit, $\overline{PD}$ ,<br>is cleared. Time-out status bit,<br>$\overline{TO}$ , is set. Watchdog Timer and<br>its prescaler are cleared.<br>The processor is put into Sleep<br>mode with the oscillator stopped. |

| RETURN           | Return from Subroutine                                                                                                                                     |  |  |  |  |

|------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| Syntax:          | [label] RETURN                                                                                                                                             |  |  |  |  |

| Operands:        | None                                                                                                                                                       |  |  |  |  |

| Operation:       | $TOS \rightarrow PC$                                                                                                                                       |  |  |  |  |

| Status Affected: | None                                                                                                                                                       |  |  |  |  |

| Description:     | Return from subroutine. The stack<br>is POPed and the top of the stack<br>(TOS) is loaded into the program<br>counter. This is a two-cycle<br>instruction. |  |  |  |  |

| SUBLW            | Subtract W from Literal                                                                                                      |  |  |  |  |

|------------------|------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| Syntax:          | [ <i>label</i> ] SUBLW k                                                                                                     |  |  |  |  |

| Operands:        | $0 \leq k \leq 255$                                                                                                          |  |  |  |  |

| Operation:       | $k - (W) \rightarrow (W)$                                                                                                    |  |  |  |  |

| Status Affected: | C, DC, Z                                                                                                                     |  |  |  |  |

| Description:     | The W register is subtracted (2's complement method) from the eight-bit literal 'k'. The result is placed in the W register. |  |  |  |  |

| RRF              | Rotate Right f through Carry                                                                                                                                                                                          |  |  |  |  |  |  |

|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

| Syntax:          | [ <i>label</i> ] RRF f,d                                                                                                                                                                                              |  |  |  |  |  |  |

| Operands:        | $\begin{array}{l} 0\leq f\leq 127\\ d\in [0,1] \end{array}$                                                                                                                                                           |  |  |  |  |  |  |

| Operation:       | See description below                                                                                                                                                                                                 |  |  |  |  |  |  |

| Status Affected: | С                                                                                                                                                                                                                     |  |  |  |  |  |  |

| Description:     | The contents of register 'f' are<br>rotated one bit to the right through<br>the Carry flag. If 'd' is '0', the<br>result is placed in the W register.<br>If 'd' is '1', the result is placed<br>back in register 'f'. |  |  |  |  |  |  |

| SUBWF               | Subtract W from f                                                                                                                                                                           |  |  |  |  |  |

|---------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| Syntax:             | [ <i>label</i> ] SUBWF f,d                                                                                                                                                                  |  |  |  |  |  |

| Operands:           | $\begin{array}{l} 0 \leq f \leq 127 \\ d  \in  [0,1] \end{array}$                                                                                                                           |  |  |  |  |  |

| Operation:          | (f) - (W) $\rightarrow$ (destination)                                                                                                                                                       |  |  |  |  |  |

| Status<br>Affected: | C, DC, Z                                                                                                                                                                                    |  |  |  |  |  |

| Description:        | Subtract (2's complement method)<br>W register from register 'f'. If 'd' is<br>'0', the result is stored in the W<br>register. If 'd' is '1', the result is<br>stored back in register 'f'. |  |  |  |  |  |

# 16.0 DEVELOPMENT SUPPORT

The PIC<sup>®</sup> microcontrollers are supported with a full range of hardware and software development tools:

- Integrated Development Environment

- MPLAB<sup>®</sup> IDE Software

- Assemblers/Compilers/Linkers

- MPASM<sup>™</sup> Assembler

- MPLAB C17 and MPLAB C18 C Compilers

- MPLINK<sup>™</sup> Object Linker/

- MPLIB<sup>™</sup> Object Librarian

- MPLAB C30 C Compiler

- MPLAB ASM30 Assembler/Linker/Library

- Simulators

- MPLAB SIM Software Simulator

- MPLAB dsPIC30 Software Simulator

- Emulators

- MPLAB ICE 2000 In-Circuit Emulator

- MPLAB ICE 4000 In-Circuit Emulator

- In-Circuit Debugger

- MPLAB ICD 2

- Device Programmers

- PRO MATE<sup>®</sup> II Universal Device Programmer

- PICSTART<sup>®</sup> Plus Development Programmer

- Low Cost Demonstration Boards

- PICDEM<sup>™</sup> 1 Demonstration Board

- PICDEM.net<sup>™</sup> Demonstration Board

- PICDEM 2 Plus Demonstration Board

- PICDEM 3 Demonstration Board

- PICDEM 4 Demonstration Board

- PICDEM 17 Demonstration Board

- PICDEM 18R Demonstration Board

- PICDEM LIN Demonstration Board

- PICDEM USB Demonstration Board

- Evaluation Kits

- KEELOQ<sup>®</sup>

- PICDEM MSC

- microID<sup>®</sup>

- CAN

- PowerSmart<sup>®</sup>

- Analog

#### 16.1 MPLAB Integrated Development Environment Software

The MPLAB IDE software brings an ease of software development previously unseen in the 8/16-bit microcontroller market. The MPLAB IDE is a Windows<sup>®</sup> based application that contains:

- · An interface to debugging tools

- simulator

- programmer (sold separately)

- emulator (sold separately)

- in-circuit debugger (sold separately)

- · A full-featured editor with color coded context

- A multiple project manager

- Customizable data windows with direct edit of contents

- High level source code debugging

- Mouse over variable inspection

- Extensive on-line help

- The MPLAB IDE allows you to:

- Edit your source files (either assembly or C)

- One touch assemble (or compile) and download to PIC MCU emulator and simulator tools (automatically updates all project information)

- Debug using:

- source files (assembly or C)

- absolute listing file (mixed assembly and C)

- machine code

MPLAB IDE supports multiple debugging tools in a single development paradigm, from the cost effective simulators, through low cost in-circuit debuggers, to full-featured emulators. This eliminates the learning curve when upgrading to tools with increasing flexibility and power.

#### 16.2 MPASM Assembler

The MPASM assembler is a full-featured, universal macro assembler for all PIC MCUs.