# E·XFL

#### NXP USA Inc. - MC68S711E9CFN2 Datasheet

#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Obsolete                                                               |

|----------------------------|------------------------------------------------------------------------|

| Core Processor             | HC11                                                                   |

| Core Size                  | 8-Bit                                                                  |

| Speed                      | 2MHz                                                                   |

| Connectivity               | SCI, SPI                                                               |

| Peripherals                | POR, WDT                                                               |

| Number of I/O              | 38                                                                     |

| Program Memory Size        | 12KB (12K x 8)                                                         |

| Program Memory Type        | OTP                                                                    |

| EEPROM Size                | 512 x 8                                                                |

| RAM Size                   | 512 x 8                                                                |

| Voltage - Supply (Vcc/Vdd) | 4.5V ~ 5.5V                                                            |

| Data Converters            | A/D 8x8b                                                               |

| Oscillator Type            | External                                                               |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                      |

| Mounting Type              | Surface Mount                                                          |

| Package / Case             | 52-LCC (J-Lead)                                                        |

| Supplier Device Package    | 52-PLCC (19.1x19.1)                                                    |

| Purchase URL               | https://www.e-xfl.com/product-detail/nxp-semiconductors/mc68s711e9cfn2 |

|                            |                                                                        |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

To provide the most up-to-date information, the revision of our documents on the World Wide Web will be the most current. Your printed copy may be an earlier revision. To verify you have the latest information available, refer to:

http://www.motorola.com/mcu/

The following revision history table summarizes changes contained in this document. For your convenience, the page number designators have been linked to the appropriate location.

| Date       | Revision<br>Level | Description                                                                              | Page<br>Number(s) |

|------------|-------------------|------------------------------------------------------------------------------------------|-------------------|

| May, 2001  | 3.1               | <b>4.4.3.1 System Configuration Register</b> — Addition to NOCOP bit description         | 88                |

|            |                   | Added 11.22 EPROM Characteristics                                                        | 251               |

| June, 2001 | 3.2               | <b>11.22 EPROM Characteristics</b> — For clarity, addition to note 2 following the table | 251               |

#### **Revision History**

| 9.5.9  | Timer Interrupt Mask 2 Register                         |

|--------|---------------------------------------------------------|

| 9.5.10 | Timer Interrupt Flag Register 2198                      |

| 9.6    | Real-Time Interrupt (RTI)199                            |

| 9.6.1  | Timer Interrupt Mask Register 2                         |

| 9.6.2  | Timer Interrupt Flag Register 2                         |

| 9.6.3  | Pulse Accumulator Control Register                      |

| 9.7    | Computer Operating Properly (COP) Watchdog Function 203 |

| 9.8    | Pulse Accumulator                                       |

| 9.8.1  | Pulse Accumulator Control Register                      |

| 9.8.2  | Pulse Accumulator Count Register                        |

| 9.8.3  | Pulse Accumulator Status and Interrupt Bits             |

# Section 10. Analog-to-Digital (A/D) Converter

| 10.1   | Contents                                |

|--------|-----------------------------------------|

| 10.2   | Introduction                            |

| 10.3   | Overview                                |

| 10.3.1 | Multiplexer                             |

| 10.3.2 | Analog Converter                        |

| 10.3.3 | Digital Control                         |

| 10.3.4 | Result Registers                        |

| 10.3.5 | A/D Converter Clocks                    |

| 10.3.6 | Conversion Sequence                     |

| 10.4   | A/D Converter Power-Up and Clock Select |

| 10.5   | Conversion Process                      |

| 10.6   | Channel Assignments                     |

| 10.7   | Single-Channel Operation                |

| 10.8   | Multiple-Channel Operation              |

| 10.9   | Operation in Stop and Wait Modes        |

| 10.10  | A/D Control/Status Register             |

| 10.11  | A/D Converter Result Registers          |

| Figure     | Title                                                                 | Page |

|------------|-----------------------------------------------------------------------|------|

| 7-8<br>7-9 | SCI Baud Rate Generator Block Diagram<br>MC68HC(7)11E20 SCI Baud Rate | 160  |

|            | Generator Block Diagram                                               | 161  |

| 7-10       | Interrupt Source Resolution Within SCI                                |      |

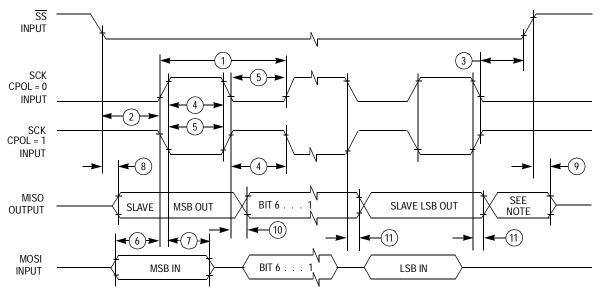

| 8-1        | SPI Block Diagram                                                     | 167  |

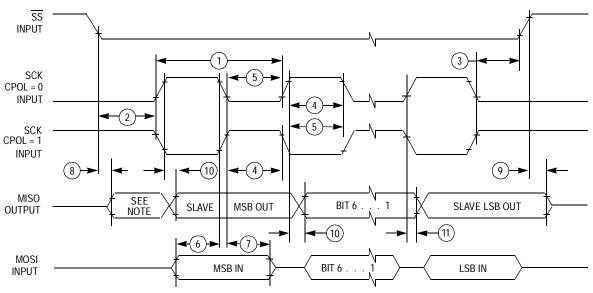

| 8-2        | SPI Transfer Format                                                   |      |

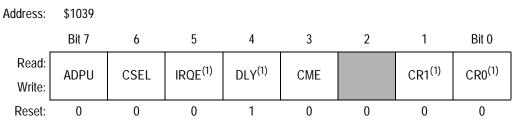

| 8-3        | Serial Peripheral Control Register (SPCR)                             |      |

| 8-4        | Serial Peripheral Status Register (SPSR)                              | 175  |

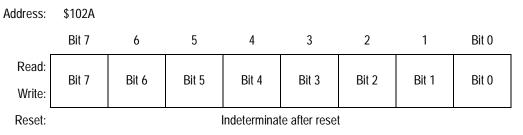

| 8-5        | Serial Peripheral Data I/O Register (SPDR)                            | 176  |

| 9-1        | Timer Clock Divider Chains                                            | 179  |

| 9-2        | Capture/Compare Block Diagram                                         | 181  |

| 9-3        | Timer Control Register 2 (TCTL2)                                      | 183  |

| 9-4        | Timer Input Capture 1 Register Pair (TIC1)                            |      |

| 9-5        | Timer Input Capture 2 Register Pair (TIC2)                            | 185  |

| 9-6        | Timer Input Capture 3 Register Pair (TIC3)                            | 185  |

| 9-7        | Timer Input Capture 4/Output                                          |      |

|            | Compare 5 Register Pair (TI4/O5)                                      |      |

| 9-8        | Timer Output Compare 1 Register Pair (TOC1)                           |      |

| 9-9        | Timer Output Compare 2 Register Pair (TOC2)                           |      |

| 9-10       | Timer Output Compare 3 Register Pair (TOC3)                           |      |

| 9-11       | Timer Output Compare 4 Register Pair (TOC4)                           |      |

| 9-12       | Timer Compare Force Register (CFORC)                                  |      |

| 9-13       | Output Compare 1 Mask Register (OC1M)                                 |      |

| 9-14       | Output Compare 1 Data Register (OC1D)                                 |      |

| 9-15       | Timer Counter Register (TCNT)                                         |      |

| 9-16       | Timer Control Register 1 (TCTL1)                                      |      |

| 9-17       | Timer Interrupt Mask 1 Register (TMSK1)                               |      |

| 9-18       | Timer Interrupt Flag 1 Register (TFLG1)                               |      |

| 9-19       | Timer Interrupt Mask 2 Register (TMSK2)                               |      |

| 9-20       | Timer Interrupt Flag 2 Register (TFLG2)                               |      |

| 9-21       | Timer Interrupt Mask 2 Register (TMSK2)                               |      |

| 9-22       | Timer Interrupt Flag 2 Register (TFLG2)                               |      |

| 9-23       | Pulse Accumulator Control Register (PACTL)                            |      |

| 9-24       | Pulse Accumulator                                                     | 204  |

There should be a single pullup resistor near the MCU interrupt input pin (typically 4.7 k $\Omega$ ). There must also be an interlock mechanism at each interrupt source so that the source holds the interrupt line low until the MCU recognizes and acknowledges the interrupt request. If one or more interrupt sources are still pending after the MCU services a request, the interrupt line will still be held low and the MCU will be interrupted again as soon as the interrupt mask bit in the MCU is cleared (normally upon return from an interrupt). Refer to Section 5. Resets and Interrupts.

$V_{PPE}$  is the input for the 12-volt nominal programming voltage required for EPROM/OTPROM programming. On devices without EPROM/OTPROM, this pin is only an XIRQ input.

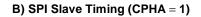

# 2.9 MODA and MODB (MODA/LIR and MODB/V<sub>STBY</sub>)

During reset, MODA and MODB select one of the four operating modes:

- Single-chip mode

- Expanded mode

- Test mode

- Bootstrap mode

#### Refer to Section 4. Operating Modes and On-Chip Memory.

After the operating mode has been selected, the load instruction register  $(\overline{\text{LIR}})$  pin provides an open-drain output to indicate that execution of an instruction has begun. A series of E-clock cycles occurs during execution of each instruction. The  $\overline{\text{LIR}}$  signal goes low during the first E-clock cycle of each instruction (opcode fetch). This output is provided for assistance in program debugging.

The V<sub>STBY</sub> pin is used to input random-access memory (RAM) standby power. When the voltage on this pin is more than one MOS threshold (about 0.7 volts) above the V<sub>DD</sub> voltage, the internal RAM and part of the reset logic are powered from this signal rather than the V<sub>DD</sub> input. This allows RAM contents to be retained without V<sub>DD</sub> power applied to the MCU. Reset must be driven low before V<sub>DD</sub> is removed and must remain low until V<sub>DD</sub> has been restored to a valid level.

| $ \begin{array}{ c c c c c c c c c c c c c c c c c c c$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |              | <u>г</u> г              |                        |   | drocoina | 1   | l. | struction |        | 1 |   | <u> </u> | nditio | n Co. | 100 |   |   |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------|-------------------------|------------------------|---|----------|-----|----|-----------|--------|---|---|----------|--------|-------|-----|---|---|

| $ \begin{array}{cccccccccccccccccccccccccccccccccccc$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | Mnemonic     | Operation               | Description            | A | -        | Onc |    |           | Cycles | s | x |          |        |       |     | v | C |

| $\begin{array}{c c c c c c c c c c c c c c c c c c c $                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | BCS (rel)    |                         | ? C = 1                |   |          | Ορυ |    |           | -      | - | _ | _        | _      |       | _   | _ | _ |

| $\begin{array}{cccccccccccccccccccccccccccccccccccc$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |              |                         | 27-1                   |   | DEI      |     | 27 | **        | 2      |   |   |          |        |       |     |   |   |

| $ \begin{array}{c c c c c c c c c c c c c c c c c c c $                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |              |                         |                        |   |          |     |    |           |        |   | _ | _        |        |       | _   |   | _ |

| $ \begin{array}{c c c c c c c c c c c c c c c c c c c $                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | BGE (Iel)    |                         |                        |   |          |     |    |           |        |   | _ |          | _      |       |     | _ | _ |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |              |                         | . ,                    | _ |          |     |    |           |        |   |   |          |        |       |     |   |   |

| $ \begin{array}{ c c c c c c c c c c c c c c c c c c c$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |              | Higher                  |                        |   |          |     |    |           |        | _ | _ | _        | _      | _     | _   | _ | _ |

| $ \begin{array}{c c c c c c c c c c c c c c c c c c c $                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | BHS (rel)    |                         | ? C = 0                |   | REL      |     | 24 | rr        | 3      | - | _ | _        | _      | -     | _   | _ | - |

| $ \begin{array}{ c c c c c c c c c c c c c c c c c c c$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | BITA (opr)   | Bit(s) Test A           | A • M                  | А | IMM      |     | 85 | ii        |        | — | — | _        | —      | Δ     | Δ   | 0 | _ |

| $ \begin{array}{ c c c c c c c c c c c c c c c c c c c$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 1            | with Memory             |                        |   |          |     |    |           |        |   |   |          |        |       |     |   |   |

| $ \begin{array}{ c c c c c c c c c c c c c c c c c c c$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |              |                         |                        |   |          |     |    |           |        |   |   |          |        |       |     |   |   |

| $ \begin{array}{c c c c c c c c c c c c c c c c c c c $                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |              |                         |                        |   | ,        | 10  |    |           |        |   |   |          |        |       |     |   |   |

| $ \begin{array}{c c c c c c c c c c c c c c c c c c c $                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | PITP (opr)   | Bit(a) Teat B           | P • M                  |   |          | 10  |    |           |        |   |   |          |        | •     |     | 0 |   |

| $ \begin{array}{ c c c c c c c c c c c c c c c c c c c$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | ыть (орг)    |                         | D • IVI                |   |          |     |    |           |        | _ | _ | _        | _      | Δ     | Δ   | 0 | _ |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |              | with Memory             |                        |   |          |     |    |           |        |   |   |          |        |       |     |   |   |

| $ \begin{array}{ c c c c c c c c c c c c c c c c c c c$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |              |                         |                        |   |          |     |    |           |        |   |   |          |        |       |     |   |   |

| $ \begin{array}{c c c c c c c c c c c c c c c c c c c $                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |              |                         |                        |   |          | 18  |    |           |        |   |   |          |        |       |     |   |   |

| $ \begin{array}{c c c c c c c c c c c c c c c c c c c $                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | BLE (rel)    | Branch if $\Delta$ Zero | ? Z + (N ⊕ V) = 1      |   | REL      |     | 2F | rr        | 3      | _ | _ | _        | _      | _     | _   | _ | _ |

| $ \begin{array}{c c c c c c c c c c c c c c c c c c c $                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | BLO (rel)    | Branch if Lower         | ? C = 1                |   | REL      |     | 25 | rr        | 3      | _ | _ | _        | _      | _     | _   | _ | _ |

| or Same      <                                                                                                         |              | Branch if Lower         |                        |   |          |     |    |           |        | _ | _ | _        | _      | _     | _   | _ | _ |

| $ \begin{array}{c c c c c c c c c c c c c c c c c c c $                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 220 (101)    |                         |                        |   |          |     | 20 |           |        |   |   |          |        |       |     |   |   |

| $ \begin{array}{c c c c c c c c c c c c c c c c c c c $                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |              |                         | ? N ⊕ V = 1            |   | REL      |     | 2D | rr        | 3      | — | — | —        | —      | —     | —   | — | — |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | BMI (rel)    | Branch if Minus         | ? N = 1                |   | REL      |     | 2B | rr        | 3      | — | — | —        | —      | —     | —   | — | — |

| $ \begin{array}{c c c c c c c c c c c c c c c c c c c $                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | BNE (rel)    |                         | ? Z = 0                |   | REL      |     | 26 | rr        | 3      | — | — | —        | —      | —     | —   | — | - |

| $ \begin{array}{c c c c c c c c c c c c c c c c c c c $                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | BPL (rel)    |                         | ? N = 0                |   | REL      |     | 2A | rr        | 3      | _ | _ | _        | _      | _     | _   | _ | _ |

| $\begin{array}{c c c c c c c c c c c c c c c c c c c $                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |              |                         |                        |   |          |     |    |           |        | _ | _ | _        | _      |       | _   | _ | _ |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | . ,          |                         |                        |   |          |     |    |           |        | _ | _ | _        | _      | _     | _   | _ | _ |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |              |                         |                        |   |          |     |    |           |        |   |   |          |        |       |     |   |   |

| $\begin{array}{c c c c c c c c c c c c c c c c c c c $                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |              |                         |                        |   | IND,Y    | 18  | 1F | ff mm rr  | 8      |   |   |          |        |       |     |   |   |

| $ \begin{array}{ c c c c c c c c c c c c c c c c c c c$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | BRN (rel)    | Branch Never            | ? 1 = 0                |   | REL      |     | 21 | rr        | 3      | — | _ | _        | _      | —     | _   | _ | _ |

| $ \begin{array}{ c c c c c c c c c c c c c c c c c c c$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | BRSET(opr)   | Branch if Bit(s)        | ? (M) • mm = 0         |   | DIR      |     | 12 | dd mm rr  | 6      | _ | _ | _        | _      | _     | _   | _ | _ |

| $ \begin{array}{c ccccccccccccccccccccccccccccccccccc$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |              | Set                     |                        |   | IND,X    |     | 1E | ff mm rr  | 7      |   |   |          |        |       |     |   |   |

| $\begin{array}{c c c c c c c c c c c c c c c c c c c $                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | (rel)        |                         |                        |   | IND,Y    | 18  | 1E | ff mm rr  | 8      |   |   |          |        |       |     |   |   |

| $ \begin{array}{ c c c c c c c c c c c c c c c c c c c$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | BSET (opr)   | Set Bit(s)              | $M + mm \Rightarrow M$ |   |          |     |    |           |        |   | _ | _        | —      | Δ     | Δ   | 0 | - |

| $ \begin{array}{ c c c c c c c c c c c c c c c c c c c$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | (msk)        |                         |                        |   |          |     |    |           |        |   |   |          |        |       |     |   |   |

| Subroutine      Subrou |              |                         |                        |   |          | 18  |    |           |        |   |   |          |        |       |     |   |   |

| $ \begin{array}{ c c c c c c c c c c c c c c c c c c c$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |              |                         | See Figure 3–2         |   | REL      |     | 8D | rr        | 6      | _ | _ | —        | _      | -     | _   | _ | _ |

| $ \begin{array}{ c c c c c c c c c c c c c c c c c c c$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | BVC (rel)    |                         | ? V = 0                |   | REL      |     | 28 | rr        | 3      | — | — | —        | —      | —     | —   | — | - |

| $ \begin{array}{c ccccccccccccccccccccccccccccccccccc$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | BVS (rel)    |                         | ? V = 1                |   | REL      |     | 29 | rr        | 3      | — | — | —        | —      | —     | —   | — | - |

| $ \begin{array}{c ccccccccccccccccccccccccccccccccccc$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | CBA          | Compare A to B          | A – B                  |   | INH      |     | 11 |           | 2      | _ | _ | _        | _      | Δ     | Δ   | Δ | Δ |

| $ \begin{array}{c c c c c c c c c c c c c c c c c c c $                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |              |                         |                        |   |          |     |    |           |        | _ | _ | _        | _      | _     | _   | _ |   |

| $ \begin{array}{c ccccccccccccccccccccccccccccccccccc$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |              | Clear Interrupt         |                        |   |          |     |    | _         |        | _ | _ | _        | 0      | —     | _   | _ | _ |

| $ \begin{array}{c c c c c c c c c c c c c c c c c c c $                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |              |                         | $0 \rightarrow M$      | + | EYT      | +   | 75 | bb ll     | 6      | - |   |          |        | 0     | 1   | 0 | 0 |

| $ \begin{array}{c c c c c c c c c c c c c c c c c c c $                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |              |                         | U ⇒ IVI                |   |          |     |    |           |        | _ | _ | _        | _      | 0     | 1   | 0 | U |

| $ \begin{array}{c c c c c c c c c c c c c c c c c c c $                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |              | Dyto                    |                        |   |          | 18  |    |           |        |   |   |          |        |       |     |   |   |

| $ \begin{array}{c c c c c c c c c c c c c c c c c c c $                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | CLRA         |                         | $0 \Rightarrow A$      | A |          |     |    |           |        | - | — | -        | -      | 0     | 1   | 0 | 0 |

| $ \begin{array}{c c c c c c c c c c c c c c c c c c c $                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | CLRB         | Clear                   | $0 \Rightarrow B$      | В | INH      |     | 5F | _         | 2      | — | — | —        | —      | 0     | 1   | 0 | 0 |

| CMPA (opr)  Compare A to<br>Memory  A - M  A  IMM  81  ii  2    Δ  Δ  Δ    A  DIR  91  dd  3     Δ  Δ  Δ    A  EXT  B1  hh II  4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | CLV          | Clear Overflow          | $0 \Rightarrow V$      |   | INH      |     | 0A | -         | 2      | - | _ | _        | _      | -     | _   | 0 | _ |

| MemoryADIR91dd3AEXTB1hh II4AIND,XA1ff4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |              | •                       | A 14                   | • | 10.46.4  |     | 04 |           |        |   |   |          |        |       |     |   |   |

| A EXT B1 hh ll 4<br>A IND,X A1 ff 4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | CIVIPA (opr) |                         | A – M                  |   |          |     |    |           |        | - | — | _        | —      | Δ     | Δ   | Δ | Δ |