Welcome to **E-XFL.COM**

# Understanding <u>Embedded - FPGAs (Field Programmable Gate Array)</u>

Embedded - FPGAs, or Field Programmable Gate Arrays, are advanced integrated circuits that offer unparalleled flexibility and performance for digital systems. Unlike traditional fixed-function logic devices, FPGAs can be programmed and reprogrammed to execute a wide array of logical operations, enabling customized functionality tailored to specific applications. This reprogrammability allows developers to iterate designs quickly and implement complex functions without the need for custom hardware.

## **Applications of Embedded - FPGAs**

The versatility of Embedded - FPGAs makes them indispensable in numerous fields. In telecommunications.

| Details                        |                                                              |

|--------------------------------|--------------------------------------------------------------|

| Product Status                 | Obsolete                                                     |

| Number of LABs/CLBs            | 7776                                                         |

| Number of Logic Elements/Cells | 34992                                                        |

| Total RAM Bits                 | 589824                                                       |

| Number of I/O                  | 404                                                          |

| Number of Gates                | 2188742                                                      |

| Voltage - Supply               | 1.71V ~ 1.89V                                                |

| Mounting Type                  | Surface Mount                                                |

| Operating Temperature          | 0°C ~ 85°C (TJ)                                              |

| Package / Case                 | 560-LBGA Exposed Pad, Metal                                  |

| Supplier Device Package        | 560-MBGA (42.5x42.5)                                         |

| Purchase URL                   | https://www.e-xfl.com/product-detail/xilinx/xcv1600e-6bg560c |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

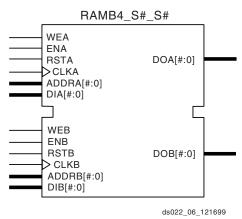

Figure 6: Dual-Port Block SelectRAM

Table 5 shows the depth and width aspect ratios for the block SelectRAM. The Virtex-E block SelectRAM also includes dedicated routing to provide an efficient interface with both CLBs and other block SelectRAMs. Refer to XAPP130 for block SelectRAM timing waveforms.

Table 5: Block SelectRAM Port Aspect Ratios

| Width | Depth | ADDR Bus   | Data Bus   |

|-------|-------|------------|------------|

| 1     | 4096  | ADDR<11:0> | DATA<0>    |

| 2     | 2048  | ADDR<10:0> | DATA<1:0>  |

| 4     | 1024  | ADDR<9:0>  | DATA<3:0>  |

| 8     | 512   | ADDR<8:0>  | DATA<7:0>  |

| 16    | 256   | ADDR<7:0>  | DATA<15:0> |

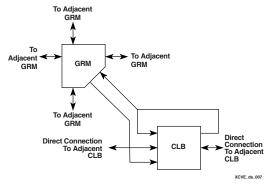

#### **Programmable Routing Matrix**

It is the longest delay path that limits the speed of any worst-case design. Consequently, the Virtex-E routing architecture and its place-and-route software were defined in a joint optimization process. This joint optimization minimizes long-path delays, and consequently, yields the best system performance.

The joint optimization also reduces design compilation times because the architecture is software-friendly. Design cycles are correspondingly reduced due to shorter design iteration times.

#### Local Routing

The VersaBlock provides local routing resources (see Figure 7), providing three types of connections:

- Interconnections among the LUTs, flip-flops, and GRM

- Internal CLB feedback paths that provide high-speed connections to LUTs within the same CLB, chaining them together with minimal routing delay

Direct paths that provide high-speed connections between horizontally adjacent CLBs, eliminating the delay of the GRM.

Figure 7: Virtex-E Local Routing

#### General Purpose Routing

Most Virtex-E signals are routed on the general purpose routing, and consequently, the majority of interconnect resources are associated with this level of the routing hierarchy. General-purpose routing resources are located in horizontal and vertical routing channels associated with the CLB rows and columns and are as follows:

- Adjacent to each CLB is a General Routing Matrix (GRM). The GRM is the switch matrix through which horizontal and vertical routing resources connect, and is also the means by which the CLB gains access to the general purpose routing.

- 24 single-length lines route GRM signals to adjacent GRMs in each of the four directions.

- 72 buffered Hex lines route GRM signals to another GRMs six-blocks away in each one of the four directions. Organized in a staggered pattern, Hex lines are driven only at their endpoints. Hex-line signals can be accessed either at the endpoints or at the midpoint (three blocks from the source). One third of the Hex lines are bidirectional, while the remaining ones are uni-directional.

- 12 Longlines are buffered, bidirectional wires that distribute signals across the device quickly and efficiently. Vertical Longlines span the full height of the device, and horizontal ones span the full width of the device.

#### I/O Routing

Virtex-E devices have additional routing resources around their periphery that form an interface between the CLB array and the IOBs. This additional routing, called the VersaRing, facilitates pin-swapping and pin-locking, such that logic redesigns can adapt to existing PCB layouts. Time-to-market is reduced, since PCBs and other system components can be manufactured while the logic design is still in progress.

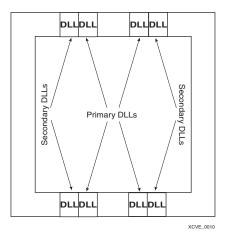

The DLL also operates as a clock mirror. By driving the output from a DLL off-chip and then back on again, the DLL can be used to deskew a board level clock among multiple devices.

To guarantee that the system clock is operating correctly prior to the FPGA starting up after configuration, the DLL can delay the completion of the configuration process until after it has achieved lock. For more information about DLL functionality, see the Design Consideration section of the data sheet.

Figure 10: DLL Locations

## **Boundary Scan**

Virtex-E devices support all the mandatory Boundary Scan instructions specified in the IEEE standard 1149.1. A Test Access Port (TAP) and registers are provided that implement the EXTEST, INTEST, SAMPLE/PRELOAD, BYPASS, IDCODE, USERCODE, and HIGHZ instructions. The TAP

also supports two internal scan chains and configuration/readback of the device.

The JTAG input pins (TDI, TMS, TCK) do not have a  $V_{CCO}$  requirement and operate with either 2.5 V or 3.3 V input signalling levels. The output pin (TDO) is sourced from the  $V_{CCO}$  in bank 2, and for proper operation of LVTTL 3.3 V levels, the bank should be supplied with 3.3 V.

Boundary Scan operation is independent of individual IOB configurations, and unaffected by package type. All IOBs, including un-bonded ones, are treated as independent 3-state bidirectional pins in a single scan chain. Retention of the bidirectional test capability after configuration facilitates the testing of external interconnections, provided the user design or application is turned off.

Table 6 lists the Boundary Scan instructions supported in Virtex-E FPGAs. Internal signals can be captured during EXTEST by connecting them to un-bonded or unused IOBs. They can also be connected to the unused outputs of IOBs defined as unidirectional input pins.

Before the device is configured, all instructions except USER1 and USER2 are available. After configuration, all instructions are available. During configuration, it is recommended that those operations using the Boundary Scan register (SAMPLE/PRELOAD, INTEST, EXTEST) not be performed.

In addition to the test instructions outlined above, the Boundary Scan circuitry can be used to configure the FPGA, and also to read back the configuration data.

Figure 11 is a diagram of the Virtex-E Series Boundary Scan logic. It includes three bits of Data Register per IOB, the IEEE 1149.1 Test Access Port controller, and the Instruction Register with decodes.

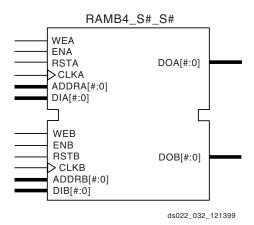

Figure 31: Dual-Port Block SelectRAM+ Memory

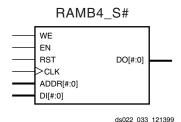

Figure 32: Single-Port Block SelectRAM+ Memory

Table 14: Available Library Primitives

| Primitive     | Port A Width | Port B Width |

|---------------|--------------|--------------|

| RAMB4_S1      |              | N/A          |

| RAMB4_S1_S1   |              | 1            |

| RAMB4_S1_S2   | 1            | 2            |

| RAMB4_S1_S4   | ı            | 4            |

| RAMB4_S1_S8   |              | 8            |

| RAMB4_S1_S16  |              | 16           |

| RAMB4_S2      |              | N/A          |

| RAMB4_S2_S2   |              | 2            |

| RAMB4_S2_S4   | 2            | 4            |

| RAMB4_S2_S8   |              | 8            |

| RAMB4_S2_S16  |              | 16           |

| RAMB4_S4      |              | N/A          |

| RAMB4_S4_S4   | 4            | 4            |

| RAMB4_S4_S8   | 4            | 8            |

| RAMB4_S4_S16  |              | 16           |

| RAMB4_S8      |              | N/A          |

| RAMB4_S8_S8   | 8            | 8            |

| RAMB4_S8_S16  |              | 16           |

| RAMB4_S16     | 16           | N/A          |

| RAMB4_S16_S16 | 16           | 16           |

## **Port Signals**

Each block SelectRAM+ port operates independently of the others while accessing the same set of 4096 memory cells.

Table 15 describes the depth and width aspect ratios for the block SelectRAM+ memory.

Table 15: Block SelectRAM+ Port Aspect Ratios

| Width | Depth | ADDR Bus   | Data Bus   |

|-------|-------|------------|------------|

| 1     | 4096  | ADDR<11:0> | DATA<0>    |

| 2     | 2048  | ADDR<10:0> | DATA<1:0>  |

| 4     | 1024  | ADDR<9:0>  | DATA<3:0>  |

| 8     | 512   | ADDR<8:0>  | DATA<7:0>  |

| 16    | 256   | ADDR<7:0>  | DATA<15:0> |

#### Clock—CLK[A|B]

Each port is fully synchronous with independent clock pins. All port input pins have setup time referenced to the port CLK pin. The data output bus has a clock-to-out time referenced to the CLK pin.

## Enable—EN[A|B]

The enable pin affects the read, write and reset functionality of the port. Ports with an inactive enable pin keep the output pins in the previous state and do not write data to the memory cells.

## Write Enable—WE[A/B]

Activating the write enable pin allows the port to write to the memory cells. When active, the contents of the data input bus are written to the RAM at the address pointed to by the address bus, and the new data also reflects on the data out bus. When inactive, a read operation occurs and the contents of the memory cells referenced by the address bus reflect on the data out bus.

#### Reset—RST[A/B]

The reset pin forces the data output bus latches to zero synchronously. This does not affect the memory cells of the RAM and does not disturb a write operation on the other port.

## Address Bus—ADDR[A/B]<#:0>

The address bus selects the memory cells for read or write. The width of the port determines the required width of this bus as shown in Table 15.

#### Data In Bus—DI[A|B]<#:0>

The data in bus provides the new data value to be written into the RAM. This bus and the port have the same width, as shown in Table 15.

### Data Output Bus-DO[A/B]<#:0>

The data out bus reflects the contents of the memory cells referenced by the address bus at the last active clock edge. During a write operation, the data out bus reflects the data in bus. The width of this bus equals the width of the port. The allowed widths appear in Table 15.

#### **Inverting Control Pins**

The four control pins (CLK, EN, WE and RST) for each port have independent inversion control as a configuration option.

## **Address Mapping**

Each port accesses the same set of 4096 memory cells using an addressing scheme dependent on the width of the port.

The physical RAM location addressed for a particular width are described in the following formula (of interest only when the two ports use different aspect ratios).

Start =

$$((ADDR_{port} + 1) * Width_{port}) - 1$$

End =  $ADDR_{port} * Width_{port}$

# width.

Table 16: Port Address Mapping

| Port  | Port |           |       |   |   |       |   |       |   |   |    |   |   |   |   |   |   |

|-------|------|-----------|-------|---|---|-------|---|-------|---|---|----|---|---|---|---|---|---|

| Width |      | Addresses |       |   |   |       |   |       |   |   |    |   |   |   |   |   |   |

| 1     | 4095 | 1         | 1     | 1 | 1 | 1     | 1 | 0     | 0 | 0 | 0  | 0 | 0 | 0 | 0 | 0 | 0 |

|       |      | 5         | 4     | 3 | 2 | 1     | 0 | 9     | 8 | 7 | 6  | 5 | 4 | 3 | 2 | 1 | 0 |

| 2     | 2047 | 0         | 7     | 0 | 6 | 05 04 |   | 03 02 |   | 2 | 01 |   | 0 | 0 |   |   |   |

| 4     | 1023 |           | 0     | 3 |   |       | 0 | 2     |   |   | 0  | 1 |   |   | 0 | 0 |   |

| 8     | 511  |           | 01 00 |   |   |       |   |       |   |   |    |   |   |   |   |   |   |

| 16    | 255  |           | 00    |   |   |       |   |       |   |   |    |   |   |   |   |   |   |

Table 16 shows low order address mapping for each port

## **Creating Larger RAM Structures**

The block SelectRAM+ columns have specialized routing to allow cascading blocks together with minimal routing delays. This achieves wider or deeper RAM structures with a smaller timing penalty than when using normal routing channels.

#### **Location Constraints**

Block SelectRAM+ instances can have LOC properties attached to them to constrain the placement. The block SelectRAM+ placement locations are separate from the CLB location naming convention, allowing the LOC properties to transfer easily from array to array.

The LOC properties use the following form.

$LOC = RAMB4_R#C#$

RAMB4\_R0C0 is the upper left RAMB4 location on the device.

#### **Conflict Resolution**

The block SelectRAM+ memory is a true dual-read/write port RAM that allows simultaneous access of the same memory cell from both ports. When one port writes to a given memory cell, the other port must not address that memory cell (for a write or a read) within the clock-to-clock setup window. The following lists specifics of port and memory cell write conflict resolution.

- If both ports write to the same memory cell simultaneously, violating the clock-to-clock setup requirement, consider the data stored as invalid.

- If one port attempts a read of the same memory cell the other simultaneously writes, violating the clock-to-clock setup requirement, the following occurs.

- The write succeeds

- The data out on the writing port accurately reflects the data written.

- The data out on the reading port is invalid.

Conflicts do not cause any physical damage.

### Single Port Timing

Figure 33 shows a timing diagram for a single port of a block SelectRAM+ memory. The block SelectRAM+ AC switching characteristics are specified in the data sheet. The block SelectRAM+ memory is initially disabled.

At the first rising edge of the CLK pin, the ADDR, DI, EN, WE, and RST pins are sampled. The EN pin is High and the WE pin is Low indicating a read operation. The DO bus contains the contents of the memory location, 0x00, as indicated by the ADDR bus.

At the second rising edge of the CLK pin, the ADDR, DI, EN, WR, and RST pins are sampled again. The EN and WE pins are High indicating a write operation. The DO bus mirrors the DI bus. The DI bus is written to the memory location 0x0F.

At the third rising edge of the CLK pin, the ADDR, DI, EN, WR, and RST pins are sampled again. The EN pin is High and the WE pin is Low indicating a read operation. The DO bus contains the contents of the memory location 0x7E as indicated by the ADDR bus.

At the fourth rising edge of the CLK pin, the ADDR, DI, EN, WR, and RST pins are sampled again. The EN pin is Low

## **Verilog Initialization Example**

```

module MYMEM (CLK, WE, ADDR, DIN, DOUT);

input CLK, WE;

input [8:0] ADDR;

input [7:0] DIN;

output [7:0] DOUT;

wire logic0, logic1;

//synopsys dc script begin

//set_attribute ram0 INIT_00

"0123456789ABCDEF0123456789ABCDEF0123456789ABCDEF0123456789ABCDEF" -type string

//set attribute ram0 INIT 01

"FEDCBA9876543210FEDCBA9876543210FEDCBA9876543210FEDCBA9876543210" -type string

//synopsys dc_script_end

assign logic0 = 1'b0;

assign logic1 = 1'b1;

RAMB4 S8 ram0 (.WE(WE), .EN(logic1), .RST(logic0), .CLK(CLK), .ADDR(ADDR), .DI(DIN),

.DO(DOUT));

//synopsys translate off

defparam ram0.INIT_00 =

256h'0123456789ABCDEF0123456789ABCDEF0123456789ABCDEF;

defparam ram0.INIT 01 =

256h'FEDCBA9876543210FEDCBA9876543210FEDCBA9876543210FEDCBA9876543210;

//synopsys translate on

endmodule

```

## **Using SelectI/O**

The Virtex-E FPGA series includes a highly configurable, high-performance I/O resource, called SelectI/O™ to provide support for a wide variety of I/O standards. The SelectI/O resource is a robust set of features including programmable control of output drive strength, slew rate, and input delay and hold time. Taking advantage of the flexibility and SelectI/O features and the design considerations described in this document can improve and simplify system level design.

#### Introduction

As FPGAs continue to grow in size and capacity, the larger and more complex systems designed for them demand an increased variety of I/O standards. Furthermore, as system clock speeds continue to increase, the need for high performance I/O becomes more important.

While chip-to-chip delays have an increasingly substantial impact on overall system speed, the task of achieving the desired system performance becomes more difficult with the proliferation of low-voltage I/O standards. SelectI/O, the revolutionary input/output resources of Virtex-E devices, resolve this potential problem by providing a highly configurable, high-performance alternative to the I/O resources of more conventional programmable devices. Virtex-E SelectI/O features combine the flexibility and time-to-market advantages of programmable logic with the high performance previously available only with ASICs and custom ICs.

Each SelectI/O block can support up to 20 I/O standards. Supporting such a variety of I/O standards allows the support of a wide variety of applications, from general purpose standard applications to high-speed low-voltage memory buses.

SelectI/O blocks also provide selectable output drive strengths and programmable slew rates for the LVTTL output buffers, as well as an optional, programmable weak pull-up, weak pull-down, or weak "keeper" circuit ideal for use in external bussing applications.

Each Input/Output Block (IOB) includes three registers, one each for the input, output, and 3-state signals within the IOB. These registers are optionally configurable as either a D-type flip-flop or as a level sensitive latch.

The input buffer has an optional delay element used to guarantee a zero hold time requirement for input signals registered within the IOB.

The Virtex-E Selectl/O features also provide dedicated resources for input reference voltage ( $V_{REF}$ ) and output source voltage ( $V_{CCO}$ ), along with a convenient banking system that simplifies board design.

By taking advantage of the built-in features and wide variety of I/O standards supported by the SelectI/O features, system-level design and board design can be greatly simplified and improved.

# Virtex<sup>™</sup>-E 1.8 V Field Programmable Gate Arrays

DS022-3 (v2.9.2) March 14, 2003

**Production Product Specification**

## Virtex-E Electrical Characteristics

#### **Definition of Terms**

Electrical and switching characteristics are specified on a per-speed-grade basis and can be designated as Advance, Preliminary, or Production. Each designation is defined as follows:

**Advance**: These speed files are based on simulations only and are typically available soon after device design specifications are frozen. Although speed grades with this designation are considered relatively stable and conservative, some under-reporting might still occur.

**Preliminary**: These speed files are based on complete ES (engineering sample) silicon characterization. Devices and speed grades with this designation are intended to give a better indication of the expected performance of production silicon. The probability of under-reporting delays is greatly reduced as compared to Advance data.

**Production**: These speed files are released once enough production silicon of a particular device family member has been characterized to provide full correlation between speed files and devices over numerous production lots. There is no under-reporting of delays, and customers receive formal notification of any subsequent changes. Typically, the slowest speed grades transition to Production before faster speed grades.

All specifications are representative of worst-case supply voltage and junction temperature conditions. The parameters included are common to popular designs and typical applications. Contact the factory for design considerations requiring more detailed information.

Table 1 correlates the current status of each Virtex-E device with a corresponding speed file designation.

Table 1: Virtex-E Device Speed Grade Designations

|          | Speed Grade Designations |             |            |  |  |  |  |  |

|----------|--------------------------|-------------|------------|--|--|--|--|--|

| Device   | Advance                  | Preliminary | Production |  |  |  |  |  |

| XCV50E   |                          |             | -8, -7, -6 |  |  |  |  |  |

| XCV100E  |                          |             | -8, -7, -6 |  |  |  |  |  |

| XCV200E  |                          |             | -8, -7, -6 |  |  |  |  |  |

| XCV300E  |                          |             | -8, -7, -6 |  |  |  |  |  |

| XCV400E  |                          |             | -8, -7, -6 |  |  |  |  |  |

| XCV600E  |                          |             | -8, -7, -6 |  |  |  |  |  |

| XCV1000E |                          |             | -8, -7, -6 |  |  |  |  |  |

| XCV1600E |                          |             | -8, -7, -6 |  |  |  |  |  |

| XCV2000E |                          |             | -8, -7, -6 |  |  |  |  |  |

| XCV2600E |                          |             | -8, -7, -6 |  |  |  |  |  |

| XCV3200E |                          |             | -8, -7, -6 |  |  |  |  |  |

All specifications are subject to change without notice.

# **Virtex-E Pin-to-Pin Input Parameter Guidelines**

All devices are 100% functionally tested. Listed below are representative values for typical pin locations and normal clock loading. Values are expressed in nanoseconds unless otherwise noted

## Global Clock Set-Up and Hold for LVTTL Standard, with DLL

|                                                                                                                                      |                                        |          |            | Speed G    | rade <sup>(2, 3)</sup> |            |       |

|--------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------|----------|------------|------------|------------------------|------------|-------|

| Description <sup>(1)</sup>                                                                                                           | Symbol                                 | Device   | Min        | -8         | -7                     | -6         | Units |

| Input Setup and Hold Time Relator LVTTL Standard. For data inpadjust the setup time delay by the Switching Characteristics Standard. |                                        |          |            |            |                        |            |       |

| No Delay                                                                                                                             | T <sub>PSDLL</sub> /T <sub>PHDLL</sub> | XCV50E   | 1.5 / -0.4 | 1.5 / -0.4 | 1.6/-0.4               | 1.7/-0.4   | ns    |

| Global Clock and IFF, with DLL                                                                                                       |                                        | XCV100E  | 1.5 / -0.4 | 1.5 / -0.4 | 1.6/-0.4               | 1.7 / -0.4 | ns    |

|                                                                                                                                      |                                        | XCV200E  | 1.5 / -0.4 | 1.5 / -0.4 | 1.6/-0.4               | 1.7/-0.4   | ns    |

|                                                                                                                                      |                                        | XCV300E  | 1.5 / -0.4 | 1.5 / -0.4 | 1.6/-0.4               | 1.7/-0.4   | ns    |

|                                                                                                                                      |                                        | XCV400E  | 1.5 / -0.4 | 1.5 / -0.4 | 1.6/-0.4               | 1.7/-0.4   | ns    |

|                                                                                                                                      |                                        | XCV600E  | 1.5 / -0.4 | 1.5 / -0.4 | 1.6/-0.4               | 1.7/-0.4   | ns    |

|                                                                                                                                      |                                        | XCV1000E | 1.5 / -0.4 | 1.5 / -0.4 | 1.6/-0.4               | 1.7/-0.4   | ns    |

|                                                                                                                                      |                                        | XCV1600E | 1.5 / -0.4 | 1.5 / -0.4 | 1.6/-0.4               | 1.7/-0.4   | ns    |

|                                                                                                                                      |                                        | XCV2000E | 1.5 / -0.4 | 1.5 / -0.4 | 1.6/-0.4               | 1.7/-0.4   | ns    |

|                                                                                                                                      |                                        | XCV2600E | 1.5 / -0.4 | 1.5 / -0.4 | 1.6/-0.4               | 1.7/-0.4   | ns    |

|                                                                                                                                      |                                        | XCV3200E | 1.5 / -0.4 | 1.5 / -0.4 | 1.6/-0.4               | 1.7/-0.4   | ns    |

#### Notes:

- 1. IFF = Input Flip-Flop or Latch

- 2. Setup time is measured relative to the Global Clock input signal with the fastest route and the lightest load. Hold time is measured relative to the Global Clock input signal with the slowest route and heaviest load.

- 3. DLL output jitter is already included in the timing calculation.

## **DLL Timing Parameters**

All devices are 100 percent functionally tested. Because of the difficulty in directly measuring many internal timing parameters, those parameters are derived from benchmark timing patterns. The following guidelines reflect worst-case values across the recommended operating conditions.

|                                  |                    |                    | Speed Grade |     |     |     |     |     |       |

|----------------------------------|--------------------|--------------------|-------------|-----|-----|-----|-----|-----|-------|

|                                  |                    |                    | -           | -8  | -7  |     | -6  |     |       |

| Description                      | Symbol             | F <sub>CLKIN</sub> | Min         | Max | Min | Max | Min | Max | Units |

| Input Clock Frequency (CLKDLLHF) | FCLKINHF           |                    | 60          | 350 | 60  | 320 | 60  | 275 | MHz   |

| Input Clock Frequency (CLKDLL)   | FCLKINLF           |                    | 25          | 160 | 25  | 160 | 25  | 135 | MHz   |

| Input Clock Low/High Pulse Width | T <sub>DLLPW</sub> | ≥2□5 MHz           | 5.0         |     | 5.0 |     | 5.0 |     | ns    |

|                                  |                    | ≥□50 MHz           | 3.0         |     | 3.0 |     | 3.0 |     | ns    |

|                                  |                    | ≥100 MHz           | 2.4         |     | 2.4 |     | 2.4 |     | ns    |

|                                  |                    | ≥□150<br>MHz       | 2.0         |     | 2.0 |     | 2.0 |     | ns    |

|                                  |                    | ≥□200<br>MHz       | 1.8         |     | 1.8 |     | 1.8 |     | ns    |

|                                  |                    | ≥□250<br>MHz       | 1.5         |     | 1.5 |     | 1.5 |     | ns    |

|                                  |                    | ≥□300<br>MHz       | 1.3         |     | 1.3 |     | NA  |     | ns    |

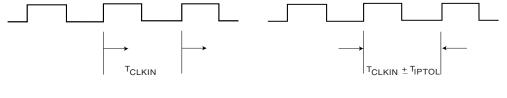

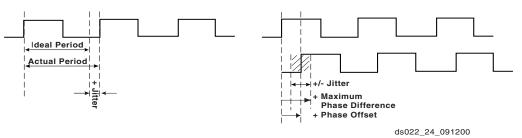

Period Tolerance: the allowed input clock period change in nanoseconds.

Output Jitter: the difference between an ideal Phase reference clock edge and the actual design.

Phase Offset and Maximum Phase Difference

Figure 4: DLL Timing Waveforms

| Date     | Version | Revision                                                                                                                                                                                                |

|----------|---------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 07/23/01 | 2.2     | <ul> <li>Under Absolute Maximum Ratings, changed (T<sub>SOL</sub>) to 220 °C.</li> </ul>                                                                                                                |

|          |         | <ul> <li>Changes made to SSTL symbol names in IOB Input Switching Characteristics<br/>Standard Adjustments table.</li> </ul>                                                                            |

| 07/26/01 | 2.3     | Removed T <sub>SOL</sub> parameter and added footnote to Absolute Maximum Ratings table.                                                                                                                |

| 9/18/01  | 2.4     | Reworded power supplies footnote to Absolute Maximum Ratings table.                                                                                                                                     |

| 10/25/01 | 2.5     | Updated the speed grade designations used in data sheets, and added Table 1, which shows the current speed grade designation for each device.      Updated the speed grade designation for each device. |

|          |         | <ul> <li>Added XCV2600E and XCV3200E values to DC Characteristics Over Recommended<br/>Operating Conditions and Power-On Power Supply Requirements tables.</li> </ul>                                   |

| 11/09/01 | 2.6     | Updated the Power-On Power Supply Requirements table.                                                                                                                                                   |

| 02/01/02 | 2.7     | <ul> <li>Updated footnotes to the DC Input and Output Levels and DLL Clock Tolerance,<br/>Jitter, and Phase Information tables.</li> </ul>                                                              |

| 07/17/02 | 2.8     | Data sheet designation upgraded from Preliminary to Production.                                                                                                                                         |

|          |         | Removed mention of MIL-M-38510/605 specification.                                                                                                                                                       |

|          |         | <ul> <li>Added link to XAPP158 from the Power-On Power Supply Requirements section.</li> </ul>                                                                                                          |

| 09/10/02 | 2.9     | Revised V <sub>IN</sub> in Absolute Maximum Ratings table.                                                                                                                                              |

|          |         | <ul> <li>Added Clock CLK switching characteristics to Table 2, "IOB Input Switching<br/>Characteristics," on page 6 and IOB Output Switching Characteristics, Figure 1.</li> </ul>                      |

| 12/22/02 | 2.9.1   | Added footnote regarding V <sub>IN</sub> PCI compliance to Absolute Maximum Ratings table.                                                                                                              |

|          |         | The fastest ramp rate is 0V to nominal voltage in 2 ms                                                                                                                                                  |

| 03/14/03 | 2.9.2   | Under Power-On Power Supply Requirements, the fastest ramp rate is no longer a "suggested" rate.                                                                                                        |

## **Virtex-E Data Sheet**

The Virtex-E Data Sheet contains the following modules:

- DS022-1, Virtex-E 1.8V FPGAs: Introduction and Ordering Information (Module 1)

- DS022-2, Virtex-E 1.8V FPGAs: Functional Description (Module 2)

- DS022-3, Virtex-E 1.8V FPGAs:

DC and Switching Characteristics (Module 3)

- DS022-4, Virtex-E 1.8V FPGAs: <u>Pinout Tables (Module 4)</u>

# Virtex<sup>™</sup>-E 1.8 V Field Programmable Gate Arrays

DS022-4 (v2.5) March 14, 2003

## **Production Product Specification**

## **Virtex-E Pin Definitions**

| Pin Name                                       | Dedicated Pin | Direction                  | Description                                                                                                                                                                                                                                      |

|------------------------------------------------|---------------|----------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| GCK0, GCK1,<br>GCK2, GCK3                      | Yes           | Input                      | Clock input pins that connect to Global Clock Buffers.                                                                                                                                                                                           |

| M0, M1, M2                                     | Yes           | Input                      | Mode pins are used to specify the configuration mode.                                                                                                                                                                                            |

| CCLK                                           | Yes           | Input or<br>Output         | The configuration Clock I/O pin: it is an input for SelectMAP and slave-serial modes, and output in master-serial mode. After configuration, it is input only, logic level = Don't Care.                                                         |

| PROGRAM                                        | Yes           | Input                      | Initiates a configuration sequence when asserted Low.                                                                                                                                                                                            |

| DONE                                           | Yes           | Bidirectional              | Indicates that configuration loading is complete, and that the start-up sequence is in progress. The output can be open drain.                                                                                                                   |

| INIT                                           | No            | Bidirectional (Open-drain) | When Low, indicates that the configuration memory is being cleared. The pin becomes a user I/O after configuration.                                                                                                                              |

| BUSY/DOUT                                      | No            | Output                     | In SelectMAP mode, BUSY controls the rate at which configuration data is loaded. The pin becomes a user I/O after configuration unless the SelectMAP port is retained.                                                                           |

|                                                |               |                            | In bit-serial modes, DOUT provides preamble and configuration data to downstream devices in a daisy-chain. The pin becomes a user I/O after configuration.                                                                                       |

| D0/DIN,<br>D1, D2,<br>D3, D4,<br>D5, D6,<br>D7 | No            | Input or<br>Output         | In SelectMAP mode, D0-7 are configuration data pins. These pins become user I/Os after configuration unless the SelectMAP port is retained.  In bit-serial modes, DIN is the single data input. This pin becomes a user I/O after configuration. |

| WRITE                                          | No            | Input                      | In SelectMAP mode, the active-low Write Enable signal. The pin becomes a user I/O after configuration unless the SelectMAP port is retained.                                                                                                     |

| CS                                             | No            | Input                      | In SelectMAP mode, the active-low Chip Select signal. The pin becomes a user I/O after configuration unless the SelectMAP port is retained.                                                                                                      |

| TDI, TDO,<br>TMS, TCK                          | Yes           | Mixed                      | Boundary-scan Test-Access-Port pins, as defined in IEEE1149.1.                                                                                                                                                                                   |

| DXN, DXP                                       | Yes           | N/A                        | Temperature-sensing diode pins. (Anode: DXP, cathode: DXN)                                                                                                                                                                                       |

| V <sub>CCINT</sub>                             | Yes           | Input                      | Power-supply pins for the internal core logic.                                                                                                                                                                                                   |

| V <sub>CCO</sub>                               | Yes           | Input                      | Power-supply pins for the output drivers (subject to banking rules)                                                                                                                                                                              |

| V <sub>REF</sub>                               | No            | Input                      | Input threshold voltage pins. Become user I/Os when an external threshold voltage is not needed (subject to banking rules).                                                                                                                      |

| GND                                            | Yes           | Input                      | Ground                                                                                                                                                                                                                                           |

© 2000-2003 Xilinx, Inc. All rights reserved. All Xilinx trademarks, registered trademarks, patents, and disclaimers are as listed at <a href="http://www.xilinx.com/legal.htm">http://www.xilinx.com/legal.htm</a>. All other trademarks and registered trademarks are the property of their respective owners. All specifications are subject to change without notice.

*Table 10:* **BG352** — **XCV100E**, **XCV200E**, **XCV300E**

| Bank | Pin Description   | Pin #            |

|------|-------------------|------------------|

| 6    | IO_L74P _Y        | R25              |

| 6    | IO_L75N           | R26              |

| 6    | IO_L75P           | P24              |

| 6    | IO                | P23 <sup>1</sup> |

| 6    | Ю                 | N26              |

|      |                   |                  |

| 7    | IO_L76N_YY        | N25              |

| 7    | IO_L76P_YY        | N24              |

| 7    | 10                | M26 <sup>1</sup> |

| 7    | IO_L77N           | M25              |

| 7    | IO_L77P           | M24              |

| 7    | IO_L78N _Y        | M23              |

| 7    | IO_VREF_7_L78P _Y | L26              |

| 7    | IO_L79N_YY        | K25              |

| 7    | IO_L79P_YY        | L24              |

| 7    | IO                | L23 <sup>1</sup> |

| 7    | IO_L80N           | J26              |

| 7    | IO_L80P           | J25              |

| 7    | IO                | K24 <sup>1</sup> |

| 7    | IO_L81N_YY        | K23              |

| 7    | IO_L81P_YY        | H25              |

| 7    | IO_L82N _Y        | J23              |

| 7    | IO_VREF_7_L82P _Y | G26              |

| 7    | IO_L83N _Y        | G25              |

| 7    | IO_L83P _Y        | H24              |

| 7    | IO                | H23              |

| 7    | Ю                 | F26 <sup>1</sup> |

| 7    | IO                | F25 <sup>1</sup> |

| 7    | IO_L84N_Y         | G24              |

| 7    | IO_VREF_7_L84P_Y  | D26              |

| 7    | IO_L85N_YY        | E25              |

| 7    | IO_L85P_YY        | F24              |

| 7    | Ю                 | F23 <sup>1</sup> |

| 7    | IO_L86N_YY        | D25              |

*Table 10:* **BG352** — **XCV100E**, **XCV200E**, **XCV300E**

| Bank | Bank Pin Description |                  |  |  |  |

|------|----------------------|------------------|--|--|--|

| 7    | IO_VREF_7_L86P_YY    | E24 <sup>2</sup> |  |  |  |

| 7    | IO                   | C26              |  |  |  |

| 7    | IO                   | E23 <sup>1</sup> |  |  |  |

| 7    | IO                   | D24 <sup>1</sup> |  |  |  |

| 7    | IO                   | C25              |  |  |  |

|      |                      |                  |  |  |  |

| NA   | TDI                  | В3               |  |  |  |

| NA   | TDO                  | D4               |  |  |  |

| NA   | CCLK                 | C3               |  |  |  |

| NA   | TCK                  | C24              |  |  |  |

| NA   | TMS                  | D23              |  |  |  |

| NA   | PROGRAM              | AC4              |  |  |  |

| NA   | DONE                 | AD3              |  |  |  |

| NA   | DXN                  | AD23             |  |  |  |

| NA   | DXP                  | AE24             |  |  |  |

| NA   | M2                   | AC23             |  |  |  |

| NA   | MO                   | AD24             |  |  |  |

| NA   | M1                   | AB23             |  |  |  |

|      |                      |                  |  |  |  |

| NA   | VCCINT               | A20              |  |  |  |

| NA   | VCCINT               | B16              |  |  |  |

| NA   | VCCINT               | C14              |  |  |  |

| NA   | VCCINT               | D12              |  |  |  |

| NA   | VCCINT               | D10              |  |  |  |

| NA   | VCCINT               | K4               |  |  |  |

| NA   | VCCINT               | L1               |  |  |  |

| NA   | VCCINT               | P2               |  |  |  |

| NA   | VCCINT               | T1               |  |  |  |

| NA   | VCCINT               | W2               |  |  |  |

| NA   | VCCINT               | AC10             |  |  |  |

| NA   | VCCINT               | AF11             |  |  |  |

| NA   | VCCINT               | AE14             |  |  |  |

| NA   | VCCINT               | AF16             |  |  |  |

| NA   | VCCINT               | AE19             |  |  |  |

#### **BG432 Differential Pin Pairs**

Virtex-E devices have differential pin pairs that can also Virtex-E devices have differential pin pairs that can also provide other functions when not used as a differential pair. A  $\sqrt{}$  in the AO column indicates that the pin pair can be used as an asynchronous output for all devices provided in this package. Pairs with a note number in the AO column are device dependent. They can have asynchronous outputs if the pin pair are in the same CLB row and column in the device. Numbers in this column refer to footnotes that indicate which devices have pin pairs than can be asynchronous outputs. The Other Functions column indicates alternative function(s) not available when the pair is used as a differential pair or differential clock.

*Table 13:* **BG432 Differential Pin Pair Summary XCV300E, XCV400E, XC600E**

| Pair | Bank                      | Р                  | N        | AO        | Other           |  |  |

|------|---------------------------|--------------------|----------|-----------|-----------------|--|--|

|      |                           | Pin                | Pin      |           | Functions       |  |  |

|      | Global Differential Clock |                    |          |           |                 |  |  |

| 0    | 4                         | AL16               | AH15     | NA        | IO_DLL_L86P     |  |  |

| 1    | 5                         | AK16               | AL17     | NA        | IO_DLL_L86N     |  |  |

| 2    | 1                         | A16                | B16      | NA        | IO_DLL_L16P     |  |  |

| 3    | 0                         | D17                | C17      | NA        | IO_DLL_L16N     |  |  |

|      | 1                         |                    | IO LVDS  |           |                 |  |  |

| To   | tal Outpu                 | ıts: 137, <i>I</i> | Asynchro | nous O    | utput Pairs: 63 |  |  |

| 0    | 0                         | D27                | B29      | 1         | -               |  |  |

| 1    | 0                         | C27                | B28      | $\sqrt{}$ | -               |  |  |

| 2    | 0                         | A28                | D26      | $\sqrt{}$ | VREF            |  |  |

| 3    | 0                         | C26                | B27      | 2         | -               |  |  |

| 4    | 0                         | A27                | D25      | $\sqrt{}$ | -               |  |  |

| 5    | 0                         | C25                | D24      | $\sqrt{}$ | VREF            |  |  |

| 6    | 0                         | D23                | B25      | 1         | -               |  |  |

| 7    | 0                         | B24                | C24      | 1         | VREF            |  |  |

| 8    | 0                         | A24                | D22      | $\sqrt{}$ | VREF            |  |  |

| 9    | 0                         | B22                | C22      | $\sqrt{}$ | -               |  |  |

| 10   | 0                         | D20                | C21      | $\sqrt{}$ | -               |  |  |

| 11   | 0                         | C20                | B21      | <b>√</b>  | -               |  |  |

| 12   | 0                         | D19                | A20      | V         | -               |  |  |

| 13   | 0                         | A19                | B19      | V         | VREF            |  |  |

| 14   | 0                         | D18                | B18      | 1         | -               |  |  |

| 15   | 0                         | B17                | C18      | 1         | VREF            |  |  |

*Table 13:* **BG432 Differential Pin Pair Summary XCV300E**, **XCV400E**, **XC600E**

| Pin                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | Pair | Bank | P   | N   | AO | Other         |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|------|-----|-----|----|---------------|

| 17                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |      |      | Pin | Pin |    |               |

| 18       1       D15       C15       1       -         19       1       A13       B14       √       VREF         20       1       D14       B13       √       -         21       1       B12       C13       √       -         21       1       B12       C13       √       -         22       1       C12       D13       √       -         23       1       C11       D12       √       -         24       1       C10       B10       √       VREF         25       1       D10       C9       1       VREF         26       1       B8       A8       1       -         27       1       B7       C8       √       VREF         28       1       A6       D8       √       -         30       1       C6       A5       √       VREF <t< td=""><td>16</td><td>1</td><td>B16</td><td>C17</td><td>NA</td><td>IO_LVDS_DLL</td></t<> | 16   | 1    | B16 | C17 | NA | IO_LVDS_DLL   |

| 19                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 17   | 1    | B15 | A15 | 1  | VREF          |

| 20                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 18   | 1    | D15 | C15 | 1  | -             |

| 21                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 19   | 1    | A13 | B14 | √  | VREF          |

| 22                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 20   | 1    | D14 | B13 | √  | -             |

| 23       1       C11       D12       √       -         24       1       C10       B10       √       VREF         25       1       D10       C9       1       VREF         26       1       B8       A8       1       -         27       1       B7       C8       √       VREF         28       1       A6       D8       √       -         29       1       D7       B6       2       -         30       1       C6       A5       √       VREF         31       1       D6       B5       √       -         32       1       C5       A4       1       -         33       1       D5       B4       √       CS, WRITE         34       2       D3       C2       √       DIN, DO, BUSY         35       2       D2       E4       3       -         36       2       D1       E3       4       -         37       2       E2       F4       1       VREF         38       2       E1       F3       5       -                                                                                     | 21   | 1    | B12 | C13 | √  | -             |

| 24       1       C10       B10       √       VREF         25       1       D10       C9       1       VREF         26       1       B8       A8       1       -         27       1       B7       C8       √       VREF         28       1       A6       D8       √       -         29       1       D7       B6       2       -         30       1       C6       A5       √       VREF         31       1       D6       B5       √       -         32       1       C5       A4       1       -         33       1       D5       B4       √       CS, WRITE         34       2       D3       C2       √       DIN, D0, BUSY         35       2       D2       E4       3       -         36       2       D1       E3       4       -         37       2       E2       F4       1       VREF         38       2       E1       F3       5       -         39       2       F2       G4       1       -                                                                                       | 22   | 1    | C12 | D13 | √  | -             |

| 25                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 23   | 1    | C11 | D12 | V  | -             |

| 26       1       B8       A8       1       -         27       1       B7       C8       √       VREF         28       1       A6       D8       √       -         29       1       D7       B6       2       -         30       1       C6       A5       √       VREF         31       1       D6       B5       √       -         32       1       C5       A4       1       -         33       1       D5       B4       √       CS, WRITE         34       2       D3       C2       √       DIN, D0, BUSY         35       2       D2       E4       3       -         36       2       D1       E3       4       -         37       2       E2       F4       1       VREF         38       2       E1       F3       5       -         39       2       F2       G4       1       -         40       2       G3       G2       √       VREF         41       2       H3       H2       4       - <t< td=""><td>24</td><td>1</td><td>C10</td><td>B10</td><td>√</td><td>VREF</td></t<>         | 24   | 1    | C10 | B10 | √  | VREF          |

| 27                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 25   | 1    | D10 | C9  | 1  | VREF          |

| 28                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 26   | 1    | B8  | A8  | 1  | -             |

| 29                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 27   | 1    | В7  | C8  | √  | VREF          |

| 30                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 28   | 1    | A6  | D8  | √  | -             |

| 31       1       D6       B5       √       -         32       1       C5       A4       1       -         33       1       D5       B4       √       CS, WRITE         34       2       D3       C2       √       DIN, D0, BUSY         35       2       D2       E4       3       -         36       2       D1       E3       4       -         37       2       E2       F4       1       VREF         38       2       E1       F3       5       -         39       2       F2       G4       1       -         40       2       G3       G2       √       VREF         41       2       H3       H2       4       -         42       2       H1       J4       1       VREF         43       2       J2       K4       √       D1         44       2       K2       K1       √       D2         45       2       L2       M4       4       -         46       2       M3       M2       1       - <td>29</td> <td>1</td> <td>D7</td> <td>B6</td> <td>2</td> <td>-</td>                         | 29   | 1    | D7  | B6  | 2  | -             |

| 32       1       C5       A4       1       -         33       1       D5       B4       √       CS, WRITE         34       2       D3       C2       √       DIN, D0, BUSY         35       2       D2       E4       3       -         36       2       D1       E3       4       -         37       2       E2       F4       1       VREF         38       2       E1       F3       5       -         39       2       F2       G4       1       -         40       2       G3       G2       √       VREF         41       2       H3       H2       4       -         42       2       H1       J4       1       VREF         43       2       J2       K4       √       D1         44       2       K2       K1       √       D2         45       2       L2       M4       4       -         46       2       M3       M2       1       -                                                                                                                                                   | 30   | 1    | C6  | A5  | √  | VREF          |

| 33       1       D5       B4       √       CS, WRITE         34       2       D3       C2       √       DIN, D0, BUSY         35       2       D2       E4       3       -         36       2       D1       E3       4       -         37       2       E2       F4       1       VREF         38       2       E1       F3       5       -         39       2       F2       G4       1       -         40       2       G3       G2       √       VREF         41       2       H3       H2       4       -         42       2       H1       J4       1       VREF         43       2       J2       K4       √       D1         44       2       K2       K1       √       D2         45       2       L2       M4       4       -         46       2       M3       M2       1       -                                                                                                                                                                                                        | 31   | 1    | D6  | B5  | √  | -             |

| 34       2       D3       C2       √       DIN, D0, BUSY         35       2       D2       E4       3       -         36       2       D1       E3       4       -         37       2       E2       F4       1       VREF         38       2       E1       F3       5       -         39       2       F2       G4       1       -         40       2       G3       G2       √       VREF         41       2       H3       H2       4       -         42       2       H1       J4       1       VREF         43       2       J2       K4       √       D1         44       2       K2       K1       √       D2         45       2       L2       M4       4       -         46       2       M3       M2       1       -                                                                                                                                                                                                                                                                     | 32   | 1    | C5  | A4  | 1  | -             |

| 35                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 33   | 1    | D5  | B4  | √  | CS, WRITE     |

| 36       2       D1       E3       4       -         37       2       E2       F4       1       VREF         38       2       E1       F3       5       -         39       2       F2       G4       1       -         40       2       G3       G2       √       VREF         41       2       H3       H2       4       -         42       2       H1       J4       1       VREF         43       2       J2       K4       √       D1         44       2       K2       K1       √       D2         45       2       L2       M4       4       -         46       2       M3       M2       1       -                                                                                                                                                                                                                                                                                                                                                                                           | 34   | 2    | D3  | C2  | √  | DIN, D0, BUSY |

| 37       2       E2       F4       1       VREF         38       2       E1       F3       5       -         39       2       F2       G4       1       -         40       2       G3       G2       √       VREF         41       2       H3       H2       4       -         42       2       H1       J4       1       VREF         43       2       J2       K4       √       D1         44       2       K2       K1       √       D2         45       2       L2       M4       4       -         46       2       M3       M2       1       -                                                                                                                                                                                                                                                                                                                                                                                                                                                | 35   | 2    | D2  | E4  | 3  | -             |

| 38       2       E1       F3       5       -         39       2       F2       G4       1       -         40       2       G3       G2       √       VREF         41       2       H3       H2       4       -         42       2       H1       J4       1       VREF         43       2       J2       K4       √       D1         44       2       K2       K1       √       D2         45       2       L2       M4       4       -         46       2       M3       M2       1       -                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 36   | 2    | D1  | E3  | 4  | -             |

| 39       2       F2       G4       1       -         40       2       G3       G2       √       VREF         41       2       H3       H2       4       -         42       2       H1       J4       1       VREF         43       2       J2       K4       √       D1         44       2       K2       K1       √       D2         45       2       L2       M4       4       -         46       2       M3       M2       1       -                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 37   | 2    | E2  | F4  | 1  | VREF          |

| 40       2       G3       G2       √       VREF         41       2       H3       H2       4       -         42       2       H1       J4       1       VREF         43       2       J2       K4       √       D1         44       2       K2       K1       √       D2         45       2       L2       M4       4       -         46       2       M3       M2       1       -                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 38   | 2    | E1  | F3  | 5  | -             |

| 41       2       H3       H2       4       -         42       2       H1       J4       1       VREF         43       2       J2       K4       √       D1         44       2       K2       K1       √       D2         45       2       L2       M4       4       -         46       2       M3       M2       1       -                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 39   | 2    | F2  | G4  | 1  | -             |

| 42       2       H1       J4       1       VREF         43       2       J2       K4       √       D1         44       2       K2       K1       √       D2         45       2       L2       M4       4       -         46       2       M3       M2       1       -                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 40   | 2    | G3  | G2  | V  | VREF          |