Welcome to **E-XFL.COM**

# Understanding <u>Embedded - FPGAs (Field Programmable Gate Array)</u>

Embedded - FPGAs, or Field Programmable Gate Arrays, are advanced integrated circuits that offer unparalleled flexibility and performance for digital systems. Unlike traditional fixed-function logic devices, FPGAs can be programmed and reprogrammed to execute a wide array of logical operations, enabling customized functionality tailored to specific applications. This reprogrammability allows developers to iterate designs quickly and implement complex functions without the need for custom hardware.

## **Applications of Embedded - FPGAs**

The versatility of Embedded - FPGAs makes them indispensable in numerous fields. In telecommunications.

| Details                        |                                                               |

|--------------------------------|---------------------------------------------------------------|

| Product Status                 | Obsolete                                                      |

| Number of LABs/CLBs            | 7776                                                          |

| Number of Logic Elements/Cells | 34992                                                         |

| Total RAM Bits                 | 589824                                                        |

| Number of I/O                  | 724                                                           |

| Number of Gates                | 2188742                                                       |

| Voltage - Supply               | 1.71V ~ 1.89V                                                 |

| Mounting Type                  | Surface Mount                                                 |

| Operating Temperature          | -40°C ~ 100°C (TJ)                                            |

| Package / Case                 | 1156-BBGA                                                     |

| Supplier Device Package        | 1156-FBGA (35x35)                                             |

| Purchase URL                   | https://www.e-xfl.com/product-detail/xilinx/xcv1600e-7fg1156i |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

DS022-2 (v2.8) January 16, 2006

# Virtex<sup>™</sup>-E 1.8 V Field Programmable Gate Arrays

**Production Product Specification**

# **Architectural Description**

## **Virtex-E Array**

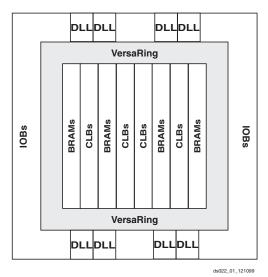

The Virtex-E user-programmable gate array, shown in Figure 1, comprises two major configurable elements: configurable logic blocks (CLBs) and input/output blocks (IOBs).

- CLBs provide the functional elements for constructing logic

- IOBs provide the interface between the package pins and the CLBs

CLBs interconnect through a general routing matrix (GRM). The GRM comprises an array of routing switches located at the intersections of horizontal and vertical routing channels. Each CLB nests into a VersaBlock™ that also provides local routing resources to connect the CLB to the GRM.

Figure 1: Virtex-E Architecture Overview

The VersaRing™ I/O interface provides additional routing resources around the periphery of the device. This routing improves I/O routability and facilitates pin locking.

The Virtex-E architecture also includes the following circuits that connect to the GRM.

- Dedicated block memories of 4096 bits each

- Clock DLLs for clock-distribution delay compensation and clock domain control

- 3-State buffers (BUFTs) associated with each CLB that drive dedicated segmentable horizontal routing resources

Values stored in static memory cells control the configurable logic elements and interconnect resources. These values load into the memory cells on power-up, and can reload if necessary to change the function of the device.

# Input/Output Block

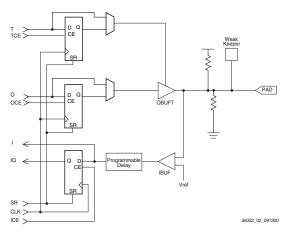

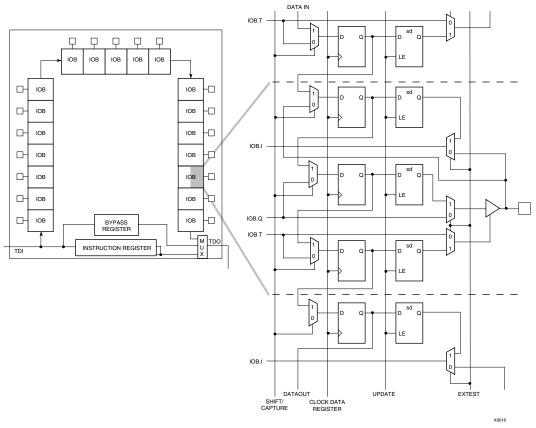

The Virtex-E IOB, Figure 2, features SelectI/O+ inputs and outputs that support a wide variety of I/O signalling standards, see Table 1.

Figure 2: Virtex-E Input/Output Block (IOB)

The three IOB storage elements function either as edge-triggered D-type flip-flops or as level-sensitive latches. Each IOB has a clock signal (CLK) shared by the three flip-flops and independent clock enable signals for each flip-flop.

© 2000–2006 Xilinx, Inc. All rights reserved. All Xilinx trademarks, registered trademarks, patents, and disclaimers are as listed at <a href="http://www.xilinx.com/legal.htm">http://www.xilinx.com/legal.htm</a>.

All other trademarks and registered trademarks are the property of their respective owners. All specifications are subject to change without notice.

Table 1: Supported I/O Standards

| I/O           | Output           | Input     | Input            | Board<br>Termination       |

|---------------|------------------|-----------|------------------|----------------------------|

| Standard      | v <sub>cco</sub> | $v_{cco}$ | V <sub>REF</sub> | Voltage (V <sub>TT</sub> ) |

| LVTTL         | 3.3              | 3.3       | N/A              | N/A                        |

| LVCMOS2       | 2.5              | 2.5       | N/A              | N/A                        |

| LVCMOS18      | 1.8              | 1.8       | N/A              | N/A                        |

| SSTL3   & II  | 3.3              | N/A       | 1.50             | 1.50                       |

| SSTL2   & II  | 2.5              | N/A       | 1.25             | 1.25                       |

| GTL           | N/A              | N/A       | 0.80             | 1.20                       |

| GTL+          | N/A              | N/A       | 1.0              | 1.50                       |

| HSTL I        | 1.5              | N/A       | 0.75             | 0.75                       |

| HSTL III & IV | 1.5              | N/A       | 0.90             | 1.50                       |

| CTT           | 3.3              | N/A       | 1.50             | 1.50                       |

| AGP-2X        | 3.3              | N/A       | 1.32             | N/A                        |

| PCl33_3       | 3.3              | 3.3       | N/A              | N/A                        |

| PCI66_3       | 3.3              | 3.3       | N/A              | N/A                        |

| BLVDS & LVDS  | 2.5              | N/A       | N/A              | N/A                        |

| LVPECL        | 3.3              | N/A       | N/A              | N/A                        |

In addition to the CLK and CE control signals, the three flip-flops share a Set/Reset (SR). For each flip-flop, this signal can be independently configured as a synchronous Set, a synchronous Reset, an asynchronous Preset, or an asynchronous Clear.

The output buffer and all of the IOB control signals have independent polarity controls.

All pads are protected against damage from electrostatic discharge (ESD) and from over-voltage transients. After configuration, clamping diodes are connected to  $V_{CCO}$  with the exception of LVCMOS18, LVCMOS25, GTL, GTL+, LVDS, and LVPECL.

Optional pull-up, pull-down and weak-keeper circuits are attached to each pad. Prior to configuration all outputs not involved in configuration are forced into their high-impedance state. The pull-down resistors and the weak-keeper circuits are inactive, but I/Os can optionally be pulled up.

The activation of pull-up resistors prior to configuration is controlled on a global basis by the configuration mode pins. If the pull-up resistors are not activated, all the pins are in a high-impedance state. Consequently, external pull-up or pull-down resistors must be provided on pins required to be at a well-defined logic level prior to configuration.

All Virtex-E IOBs support IEEE 1149.1-compatible Boundary Scan testing.

## Input Path

The Virtex-E IOB input path routes the input signal directly to internal logic and/ or through an optional input flip-flop.

An optional delay element at the D-input of this flip-flop eliminates pad-to-pad hold time. The delay is matched to the internal clock-distribution delay of the FPGA, and when used, assures that the pad-to-pad hold time is zero.

Each input buffer can be configured to conform to any of the low-voltage signalling standards supported. In some of these standards the input buffer utilizes a user-supplied threshold voltage,  $V_{REF}$  The need to supply  $V_{REF}$  imposes constraints on which standards can be used in close proximity to each other. See **I/O Banking**.

There are optional pull-up and pull-down resistors at each user I/O input for use after configuration. Their value is in the range  $50-100~k\Omega$ .

## **Output Path**

The output path includes a 3-state output buffer that drives the output signal onto the pad. The output signal can be routed to the buffer directly from the internal logic or through an optional IOB output flip-flop.

The 3-state control of the output can also be routed directly from the internal logic or through a flip-flip that provides synchronous enable and disable.

Each output driver can be individually programmed for a wide range of low-voltage signalling standards. Each output buffer can source up to 24 mA and sink up to 48 mA. Drive strength and slew rate controls minimize bus transients.

In most signalling standards, the output High voltage depends on an externally supplied  $V_{CCO}$  voltage. The need to supply  $V_{CCO}$  imposes constraints on which standards can be used in close proximity to each other. See <code>I/O Banking</code>.

An optional weak-keeper circuit is connected to each output. When selected, the circuit monitors the voltage on the pad and weakly drives the pin High or Low to match the input signal. If the pin is connected to a multiple-source signal, the weak keeper holds the signal in its last state if all drivers are disabled. Maintaining a valid logic level in this way eliminates bus chatter.

Since the weak-keeper circuit uses the IOB input buffer to monitor the input level, an appropriate  $V_{REF}$  voltage must be provided if the signalling standard requires one. The provision of this voltage must comply with the I/O banking rules.

#### I/O Banking

Some of the I/O standards described above require  $V_{CCO}$  and/or  $V_{REF}$  voltages. These voltages are externally supplied and connected to device pins that serve groups of IOBs, called banks. Consequently, restrictions exist about which I/O standards can be combined within a given bank.

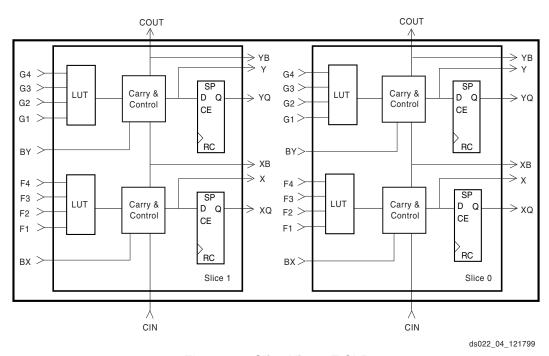

Figure 4: 2-Slice Virtex-E CLB

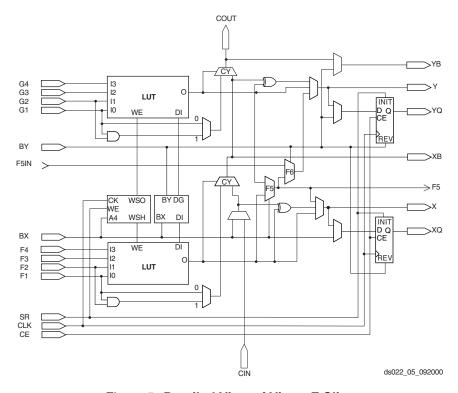

Figure 5: Detailed View of Virtex-E Slice

## Storage Elements

The storage elements in the Virtex-E slice can be configured either as edge-triggered D-type flip-flops or as level-sensitive latches. The D inputs can be driven either by

the function generators within the slice or directly from slice inputs, bypassing the function generators.

In addition to Clock and Clock Enable signals, each Slice has synchronous set and reset signals (SR and BY). SR

Figure 11: Virtex-E Family Boundary Scan Logic

## Instruction Set

The Virtex-E series Boundary Scan instruction set also includes instructions to configure the device and read back configuration data (CFG\_IN, CFG\_OUT, and JSTART). The complete instruction set is coded as shown in Table 6.

Table 6: Boundary Scan Instructions

| Boundary Scan<br>Command | Binary<br>Code(4:0) | Description                                          |

|--------------------------|---------------------|------------------------------------------------------|

| EXTEST                   | 00000               | Enables Boundary Scan EXTEST operation               |

| SAMPLE/<br>PRELOAD       | 00001               | Enables Boundary Scan<br>SAMPLE/PRELOAD<br>operation |

| USER1                    | 00010               | Access user-defined register 1                       |

| USER2                    | 00011               | Access user-defined register 2                       |

| CFG_OUT                  | 00100               | Access the configuration bus for read operations.    |

Table 6: Boundary Scan Instructions (Continued)

| Boundary Scan<br>Command | Binary<br>Code(4:0) | Description                                                   |

|--------------------------|---------------------|---------------------------------------------------------------|

| CFG_IN                   | 00101               | Access the configuration bus for write operations.            |

| INTEST                   | 00111               | Enables Boundary Scan INTEST operation                        |

| USERCODE                 | 01000               | Enables shifting out USER code                                |

| IDCODE                   | 01001               | Enables shifting out of ID Code                               |

| HIGHZ                    | 01010               | 3-states output pins<br>while enabling the<br>Bypass Register |

| JSTART                   | 01100               | Clock the start-up<br>sequence when<br>StartupClk is TCK      |

| BYPASS                   | 11111               | Enables BYPASS                                                |

| RESERVED                 | All other codes     | Xilinx reserved instructions                                  |

the internal storage elements to begin changing state in response to the logic and the user clock.

The relative timing of these events can be changed. In addition, the GTS, GSR, and GWE events can be made depen-

## Readback

The configuration data stored in the Virtex-E configuration memory can be readback for verification. Along with the configuration data it is possible to readback the contents all flip-flops/latches, LUT RAMs, and block RAMs. This capa-

dent on the DONE pins of multiple devices all going High, forcing the devices to start synchronously. The sequence can also be paused at any stage until lock has been achieved on any or all DLLs.

bility is used for real-time debugging. For more detailed information, see application note XAPP138 "Virtex FPGA Series Configuration and Readback".

# **Design Considerations**

This section contains more detailed design information on the following features.

- Delay-Locked Loop . . . see page 19

- BlockRAM . . . see page 24

- SelectI/O . . . see page 31

# **Using DLLs**

The Virtex-E FPGA series provides up to eight fully digital dedicated on-chip Delay-Locked Loop (DLL) circuits which provide zero propagation delay, low clock skew between output clock signals distributed throughout the device, and advanced clock domain control. These dedicated DLLs can be used to implement several circuits which improve and simplify system level design.

## Introduction

As FPGAs grow in size, quality on-chip clock distribution becomes increasingly important. Clock skew and clock delay impact device performance and the task of managing clock skew and clock delay with conventional clock trees becomes more difficult in large devices. The Virtex-E series of devices resolve this potential problem by providing up to eight fully digital dedicated on-chip DLL circuits, which provide zero propagation delay and low clock skew between output clock signals distributed throughout the device.

Each DLL can drive up to two global clock routing networks within the device. The global clock distribution network minimizes clock skews due to loading differences. By monitoring a sample of the DLL output clock, the DLL can compensate for the delay on the routing network, effectively eliminating the delay from the external input port to the individual clock loads within the device.

In addition to providing zero delay with respect to a user source clock, the DLL can provide multiple phases of the source clock. The DLL can also act as a clock doubler or it can divide the user source clock by up to 16.

Clock multiplication gives the designer a number of design alternatives. For instance, a 50 MHz source clock doubled by the DLL can drive an FPGA design operating at 100 MHz. This technique can simplify board design because the clock path on the board no longer distributes such a

high-speed signal. A multiplied clock also provides designers the option of time-domain-multiplexing, using one circuit twice per clock cycle, consuming less area than two copies of the same circuit. Two DLLs in can be connected in series to increase the effective clock multiplication factor to four.

The DLL can also act as a clock mirror. By driving the DLL output off-chip and then back in again, the DLL can be used to deskew a board level clock between multiple devices.

In order to guarantee the system clock establishes prior to the device "waking up," the DLL can delay the completion of the device configuration process until after the DLL achieves lock.

By taking advantage of the DLL to remove on-chip clock delay, the designer can greatly simplify and improve system level design involving high-fanout, high-performance clocks.

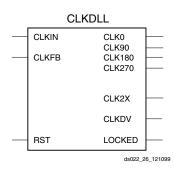

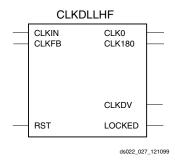

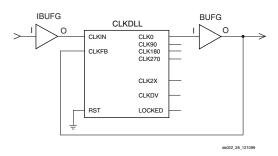

# **Library DLL Symbols**

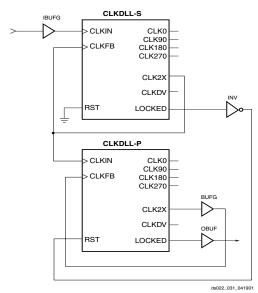

Figure 21 shows the simplified Xilinx library DLL macro symbol, BUFGDLL. This macro delivers a quick and efficient way to provide a system clock with zero propagation delay throughout the device. Figure 22 and Figure 23 show the two library DLL primitives. These symbols provide access to the complete set of DLL features when implementing more complex applications.

Figure 21: Simplified DLL Macro Symbol BUFGDLL

Figure 22: Standard DLL Symbol CLKDLL

Figure 23: High Frequency DLL Symbol CLKDLLHF

## **BUFGDLL Pin Descriptions**

Use the BUFGDLL macro as the simplest way to provide zero propagation delay for a high-fanout on-chip clock from an external input. This macro uses the IBUFG, CLKDLL and BUFG primitives to implement the most basic DLL application as shown in Figure 24.

Figure 24: BUFGDLL Schematic

This symbol does not provide access to the advanced clock domain controls or to the clock multiplication or clock division features of the DLL. This symbol also does not provide access to the RST, or LOCKED pins of the DLL. For access to these features, a designer must use the library DLL primitives described in the following sections.

## Source Clock Input — I

The I pin provides the user source clock, the clock signal on which the DLL operates, to the BUFGDLL. For the BUFGDLL macro the source clock frequency must fall in the low frequency range as specified in the data sheet. The BUF-

GDLL requires an external signal source clock. Therefore, only an external input port can source the signal that drives the BUFGDLL I pin.

## Clock Output — O

The clock output pin O represents a delay-compensated version of the source clock (I) signal. This signal, sourced by a global clock buffer BUFG symbol, takes advantage of the dedicated global clock routing resources of the device.

The output clock has a 50-50 duty cycle unless you deactivate the duty cycle correction property.

## **CLKDLL Primitive Pin Descriptions**

The library CLKDLL primitives provide access to the complete set of DLL features needed when implementing more complex applications with the DLL.

## Source Clock Input — CLKIN

The CLKIN pin provides the user source clock (the clock signal on which the DLL operates) to the DLL. The CLKIN frequency must fall in the ranges specified in the data sheet. A global clock buffer (BUFG) driven from another CLKDLL, one of the global clock input buffers (IBUFG), or an IO\_LVDS\_DLL pin on the same edge of the device (top or bottom) must source this clock signal. There are four IO\_LVDS\_DLL input pins that can be used as inputs to the DLLs. This makes a total of eight usable input pins for DLLs in the Virtex-E family.

## Feedback Clock Input — CLKFB

The DLL requires a reference or feedback signal to provide the delay-compensated output. Connect only the CLK0 or CLK2X DLL outputs to the feedback clock input (CLKFB) pin to provide the necessary feedback to the DLL. The feedback clock input can also be provided through one of the following pins.

IBUFG - Global Clock Input Pad

IO LVDS DLL - the pin adjacent to IBUFG

If an IBUFG sources the CLKFB pin, the following special rules apply.

- 1. An external input port must source the signal that drives the IBUFG I pin.

- The CLK2X output must feedback to the device if both the CLK0 and CLK2X outputs are driving off chip devices.

- That signal must directly drive only OBUFs and nothing else.

These rules enable the software determine which DLL clock output sources the CLKFB pin.

#### Reset Input — RST

When the reset pin RST activates the LOCKED signal deactivates within four source clock cycles. The RST pin, active High, must either connect to a dynamic signal or tied to

Because any single DLL can access only two BUFGs at most, any additional output clock signals must be routed from the DLL in this example on the high speed backbone routing.

The dll\_2x files in the <u>xapp132.zip</u> file show the VHDL and Verilog implementation of this circuit.

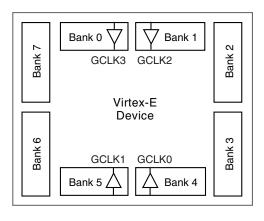

#### Virtex-E 4x Clock

Two DLLs located in the same half-edge (top-left, top-right, bottom-right, bottom-left) can be connected together, without using a BUFG between the CLKDLLs, to generate a 4x clock as shown in Figure 30. Virtex-E devices, like the Virtex devices, have four clock networks that are available for internal deskewing of the clock. Each of the eight DLLs have access to two of the four clock networks. Although all the DLLs can be used for internal deskewing, the presence of two GCLKBUFs on the top and two on the bottom indicate that only two of the four DLLs on the top (and two of the four DLLs on the bottom) can be used for this purpose.

Figure 30: DLL Generation of 4x Clock in Virtex-E Devices

The dll\_4xe files in the xapp132.zip file show the DLL implementation in Verilog for Virtex-E devices. These files can be found at:

ftp://ftp.xilinx.com/pub/applications/xapp/xapp132.zip

# **Using Block SelectRAM+ Features**

The Virtex FPGA Series provides dedicated blocks of on-chip, true dual-read/write port synchronous RAM, with 4096 memory cells. Each port of the block SelectRAM+memory can be independently configured as a read/write port, a read port, a write port, and can be configured to a specific data width. The block SelectRAM+ memory offers

new capabilities allowing the FPGA designer to simplify designs.

## **Operating Modes**

VIrtex-E block SelectRAM+ memory supports two operating modes:

- Read Through

- Write Back

## Read Through (one clock edge)

The read address is registered on the read port clock edge and data appears on the output after the RAM access time. Some memories might place the latch/register at the outputs, depending on whether a faster clock-to-out versus set-up time is desired. This is generally considered to be an inferior solution, since it changes the read operation to an asynchronous function with the possibility of missing an address/control line transition during the generation of the read pulse clock.

## Write Back (one clock edge)

The write address is registered on the write port clock edge and the data input is written to the memory and mirrored on the output.

#### **Block SelectRAM+ Characteristics**

- All inputs are registered with the port clock and have a set-up to clock timing specification.

- All outputs have a read through or write back function depending on the state of the port WE pin. The outputs relative to the port clock are available after the clock-to-out timing specification.

- The block SelectRAMs are true SRAM memories and do not have a combinatorial path from the address to the output. The LUT SelectRAM+ cells in the CLBs are still available with this function.

- The ports are completely independent from each other (i.e., clocking, control, address, read/write function, and data width) without arbitration.

- A write operation requires only one clock edge.

- · A read operation requires only one clock edge.

The output ports are latched with a self timed circuit to guarantee a glitch free read. The state of the output port does not change until the port executes another read or write operation.

## **Library Primitives**

Figure 31 and Figure 32 show the two generic library block SelectRAM+ primitives. Table 14 describes all of the available primitives for synthesis and simulation.

The voltage reference signal is "banked" within the Virtex-E device on a half-edge basis such that for all packages there are eight independent  $V_{REF}$  banks internally. See Figure 38 for a representation of the Virtex-E I/O banks. Within each bank approximately one of every six I/O pins is automatically configured as a  $V_{REF}$  input. After placing a differential amplifier input signal within a given  $V_{REF}$  bank, the same external source must drive all I/O pins configured as a  $V_{REF}$  input.

IBUF placement restrictions require that any differential amplifier input signals within a bank be of the same standard. How to specify a specific location for the IBUF via the LOC property is described below. Table 19 summarizes the Virtex-E input standards compatibility requirements.

An optional delay element is associated with each IBUF. When the IBUF drives a flip-flop within the IOB, the delay element by default activates to ensure a zero hold-time requirement. The NODELAY=TRUE property overrides this default.

When the IBUF does not drive a flip-flop within the IOB, the delay element de-activates by default to provide higher performance. To delay the input signal, activate the delay element with the DELAY=TRUE property.

**Table 19: Xilinx Input Standards Compatibility Requirements**

Rule 1 Standards with the same input  $V_{CCO}$ , output  $V_{CCO}$ , and  $V_{REF}$  can be placed within the same bank.

Figure 38: Virtex-E I/O Banks

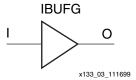

#### **IBUFG**

Signals used as high fanout clock inputs to the Virtex-E device should drive a global clock input buffer (IBUFG) via an external input port in order to take advantage of one of the four dedicated global clock distribution networks. The output of the IBUFG should only drive a CLKDLL,

CLKDLLHF, or BUFG symbol. The generic Virtex-E IBUFG symbol appears in Figure 39.

Figure 39: Virtex-E Global Clock Input Buffer (IBUFG)

Symbol

The extension to the base name determines which I/O standard is used by the IBUFG. With no extension specified for the generic IBUFG symbol, the assumed standard is LVTTL.

The following list details variations of the IBUFG symbol.

- IBUFG

- IBUFG LVCMOS2

- IBUFG PCI33 3

- IBUFG PCI66 3

- IBUFG GTL

- IBUFG\_GTLP

- IBUFG HSTL I

- IBUFG\_HSTL\_III

- IBUFG HSTL IV

- IBUFG SSTL3 I

- IBUFG\_SSTL3\_II

- IBUFG\_SSTL2\_I

- IBUFG\_SSTL2\_II

- IBUFG\_CTT

- IBUFG\_AGP

- IBUFG\_LVCMOS18

- IBUFG\_LVDS

- IBUFG LVPECL

When the IBUFG symbol supports an I/O standard that requires a differential amplifier input, the IBUFG automatically configures as a differential amplifier input buffer. The low-voltage I/O standards with a differential amplifier input require an external reference voltage input  $V_{\rm REF}$

The voltage reference signal is "banked" within the Virtex-E device on a half-edge basis such that for all packages there are eight independent  $V_{REF}$  banks internally. See Figure 38 for a representation of the Virtex-E I/O banks. Within each bank approximately one of every six I/O pins is automatically configured as a  $V_{REF}$  input. After placing a differential amplifier input signal within a given  $V_{REF}$  bank, the same external source must drive all I/O pins configured as a  $V_{REF}$  input.

IBUFG placement restrictions require any differential amplifier input signals within a bank be of the same standard. The LOC property can specify a location for the IBUFG.

As an added convenience, the BUFGP can be used to instantiate a high fanout clock input. The BUFGP symbol

## IOB Flip-Flop/Latch Property

The Virtex-E series I/O Block (IOB) includes an optional register on the input path, an optional register on the output path, and an optional register on the 3-state control pin. The design implementation software automatically takes advantage of these registers when the following option for the Map program is specified.

map -pr b <filename>

Alternatively, the IOB = TRUE property can be placed on a register to force the mapper to place the register in an IOB.

#### **Location Constraints**

Specify the location of each SelectI/O symbol with the location constraint LOC attached to the SelectI/O symbol. The external port identifier indicates the value of the location constrain. The format of the port identifier depends on the package chosen for the specific design.

The LOC properties use the following form:

LOC=A42

LOC=P37

## **Output Slew Rate Property**

As mentioned above, a variety of symbol names provide the option of choosing the desired slew rate for the output buffers. In the case of the LVTTL output buffers (OBUF, OBUFT, and IOBUF), slew rate control can be alternatively programed with the SLEW= property. By default, the slew rate for each output buffer is reduced to minimize power bus transients when switching non-critical signals. The SLEW= property has one of the two following values.

SLEW=SLOW

SLEW=FAST

## **Output Drive Strength Property**

The desired output drive strength can be additionally specified by choosing the appropriate library symbol. The Xilinx library also provides an alternative method for specifying this feature. For the LVTTL output buffers (OBUF, OBUFT, and IOBUF, the desired drive strength can be specified with the DRIVE= property. This property could have one of the following seven values.

DRIVE=2

DRIVE=4

DRIVE=6

DRIVE=8

DRIVE=12 (Default)

DRIVE=16

DRIVE=24

## **Design Considerations**

# Reference Voltage (V<sub>REF</sub>) Pins

Low-voltage I/O standards with a differential amplifier input buffer require an input reference voltage ( $V_{REF}$ ). Provide the  $V_{RFF}$  as an external signal to the device.

The voltage reference signal is "banked" within the device on a half-edge basis such that for all packages there are eight independent  $V_{REF}$  banks internally. See Figure 38 for a representation of the Virtex-E I/O banks. Within each bank approximately one of every six I/O pins is automatically configured as a  $V_{REF}$  input. After placing a differential amplifier input signal within a given  $V_{REF}$  bank, the same external source must drive all I/O pins configured as a  $V_{REF}$  input.

Within each  $V_{REF}$  bank, any input buffers that require a  $V_{REF}$  signal must be of the same type. Output buffers of any type and input buffers can be placed without requiring a reference voltage within the same  $V_{REF}$  bank.

## Output Drive Source Voltage (V<sub>CCO</sub>) Pins

Many of the low voltage I/O standards supported by SelectI/O devices require a different output drive source voltage ( $V_{\rm CCO}$ ). As a result each device can often have to support multiple output drive source voltages.

The Virtex-E series supports eight banks for the HQ and PQ packages. The CS package supports four  $V_{CCO}$  banks.

Output buffers within a given  $V_{CCO}$  bank must share the same output drive source voltage. Input buffers for LVTTL, LVCMOS2, LVCMOS18, PCI33\_3, and PCI 66\_3 use the  $V_{CCO}$  voltage for Input  $V_{CCO}$  voltage.

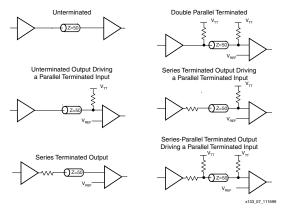

## Transmission Line Effects

The delay of an electrical signal along a wire is dominated by the rise and fall times when the signal travels a short distance. Transmission line delays vary with inductance and capacitance, but a well-designed board can experience delays of approximately 180 ps per inch.

Transmission line effects, or reflections, typically start at 1.5" for fast (1.5 ns) rise and fall times. Poor (or non-existent) termination or changes in the transmission line impedance cause these reflections and can cause additional delay in longer traces. As system speeds continue to increase, the effect of I/O delays can become a limiting factor and therefore transmission line termination becomes increasingly more important.

#### Termination Techniques

A variety of termination techniques reduce the impact of transmission line effects.

The following are output termination techniques:

- None

- Series

- Parallel (Shunt)

- Series and Parallel (Series-Shunt)

Input termination techniques include the following.

- None

- Parallel (Shunt)

These termination techniques can be applied in any combination. A generic example of each combination of termination methods appears in Figure 43.

Figure 43: Overview of Standard Input and Output Termination Methods

## Simultaneous Switching Guidelines

Ground bounce can occur with high-speed digital ICs when multiple outputs change states simultaneously, causing undesired transient behavior on an output, or in the internal logic. This problem is also referred to as the Simultaneous Switching Output (SSO) problem.

Ground bounce is primarily due to current changes in the combined inductance of ground pins, bond wires, and ground metallization. The IC internal ground level deviates from the external system ground level for a short duration (a few nanoseconds) after multiple outputs change state simultaneously.

Ground bounce affects stable Low outputs and all inputs because they interpret the incoming signal by comparing it to the internal ground. If the ground bounce amplitude exceeds the actual instantaneous noise margin, then a non-changing input can be interpreted as a short pulse with a polarity opposite to the ground bounce.

Table 21 provides guidelines for the maximum number of simultaneously switching outputs allowed per output power/ground pair to avoid the effects of ground bounce. See Table 22 for the number of effective output power/ground pairs for each Virtex-E device and package combination.

Table 21: Guidelines for Max Number of Simultaneously Switching Outputs per Power/Ground Pair

|                                   | Pa           | Package |        |

|-----------------------------------|--------------|---------|--------|

| Standard                          | BGA, CS, FGA | HQ      | PQ, TQ |

| LVTTL Slow Slew Rate, 2 mA drive  | 68           | 49      | 36     |

| LVTTL Slow Slew Rate, 4 mA drive  | 41           | 31      | 20     |

| LVTTL Slow Slew Rate, 6 mA drive  | 29           | 22      | 15     |

| LVTTL Slow Slew Rate, 8 mA drive  | 22           | 17      | 12     |

| LVTTL Slow Slew Rate, 12 mA drive | 17           | 12      | 9      |

| LVTTL Slow Slew Rate, 16 mA drive | 14           | 10      | 7      |

| LVTTL Slow Slew Rate, 24 mA drive | 9            | 7       | 5      |

| LVTTL Fast Slew Rate, 2 mA drive  | 40           | 29      | 21     |

| LVTTL Fast Slew Rate, 4 mA drive  | 24           | 18      | 12     |

| LVTTL Fast Slew Rate, 6 mA drive  | 17           | 13      | 9      |

| LVTTL Fast Slew Rate, 8 mA drive  | 13           | 10      | 7      |

| LVTTL Fast Slew Rate, 12 mA drive | 10           | 7       | 5      |

| LVTTL Fast Slew Rate, 16 mA drive | 8            | 6       | 4      |

| LVTTL Fast Slew Rate, 24 mA drive | 5            | 4       | 3      |

| LVCMOS                            | 10           | 7       | 5      |

| PCI                               | 8            | 6       | 4      |

| GTL                               | 4            | 4       | 4      |

| GTL+                              | 4            | 4       | 4      |

# Global Clock Input to Output Delay for LVTTL, 12 mA, Fast Slew Rate, without DLL

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                    |          |     | Speed ( | Grade <sup>(2)</sup> |     |       |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------|----------|-----|---------|----------------------|-----|-------|

| Description <sup>(1)</sup>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | Symbol             | Device   | Min | -8      | -7                   | -6  | Units |

| LVTTL Global Clock Input to Output Delay using                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | T <sub>ICKOF</sub> | XCV50E   | 1.5 | 4.2     | 4.4                  | 4.6 | ns    |

| Output Flip-flop, 12 mA, Fast Slew Rate, without DLL. For data output with different standards,                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                    | XCV100E  | 1.5 | 4.2     | 4.4                  | 4.6 | ns    |

| adjust the delays with the values shown in IOB                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                    | XCV200E  | 1.5 | 4.3     | 4.5                  | 4.7 | ns    |

| Output Switching Characteristics Standard Adjustments, page 10.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                    | XCV300E  | 1.5 | 4.3     | 4.5                  | 4.7 | ns    |

| July and the state of the state |                    | XCV400E  | 1.5 | 4.4     | 4.6                  | 4.8 | ns    |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                    | XCV600E  | 1.6 | 4.5     | 4.7                  | 4.9 | ns    |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                    | XCV1000E | 1.7 | 4.6     | 4.8                  | 5.0 | ns    |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                    | XCV1600E | 1.8 | 4.7     | 4.9                  | 5.1 | ns    |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                    | XCV2000E | 1.8 | 4.8     | 5.0                  | 5.2 | ns    |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                    | XCV2600E | 2.0 | 5.0     | 5.2                  | 5.4 | ns    |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                    | XCV3200E | 2.2 | 5.2     | 5.4                  | 5.6 | ns    |

#### Notes:

- Listed above are representative values where one global clock input drives one vertical clock line in each accessible column, and where all accessible IOB and CLB flip-flops are clocked by the global clock net.

- Output timing is measured at 50% V<sub>CC</sub> threshold with 35 pF external capacitive load. For other I/O standards and different loads, see Table 3 and Table 4.

# Global Clock Set-Up and Hold for LVTTL Standard, without DLL

|                                                                                                                                                                                                                                                   |                                      |          |         | Speed G | rade <sup>(2, 3)</sup> |         |       |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------|----------|---------|---------|------------------------|---------|-------|

| Description <sup>(1)</sup>                                                                                                                                                                                                                        | Symbol                               | Device   | Min     | -8      | -7                     | -6      | Units |

| Input Setup and Hold Time Relative to Global Clock Input Signal for LVTTL Standard. For data input with different standards, adjust the setup time delay by the values shown in IOB Input Switching Characteristics Standard Adjustments, page 8. |                                      |          |         |         |                        |         |       |

| Full Delay                                                                                                                                                                                                                                        | T <sub>PSFD</sub> /T <sub>PHFD</sub> | XCV50E   | 1.8 / 0 | 1.8 / 0 | 1.8 / 0                | 1.8 / 0 | ns    |

| Global Clock and IFF, without DLL                                                                                                                                                                                                                 |                                      | XCV100E  | 1.8 / 0 | 1.8 / 0 | 1.8 / 0                | 1.8 / 0 | ns    |

|                                                                                                                                                                                                                                                   |                                      | XCV200E  | 1.9 / 0 | 1.9 / 0 | 1.9 / 0                | 1.9 / 0 | ns    |

|                                                                                                                                                                                                                                                   |                                      | XCV300E  | 2.0 / 0 | 2.0 / 0 | 2.0 / 0                | 2.0 / 0 | ns    |

|                                                                                                                                                                                                                                                   |                                      | XCV400E  | 2.0 / 0 | 2.0 / 0 | 2.0 / 0                | 2.0 / 0 | ns    |

|                                                                                                                                                                                                                                                   |                                      | XCV600E  | 2.1 / 0 | 2.1 / 0 | 2.1 / 0                | 2.1 / 0 | ns    |

|                                                                                                                                                                                                                                                   |                                      | XCV1000E | 2.3 / 0 | 2.3 / 0 | 2.3 / 0                | 2.3 / 0 | ns    |

|                                                                                                                                                                                                                                                   |                                      | XCV1600E | 2.5 / 0 | 2.5 / 0 | 2.5 / 0                | 2.5 / 0 | ns    |

|                                                                                                                                                                                                                                                   |                                      | XCV2000E | 2.5 / 0 | 2.5 / 0 | 2.5 / 0                | 2.5 / 0 | ns    |

|                                                                                                                                                                                                                                                   |                                      | XCV2600E | 2.7 / 0 | 2.7 / 0 | 2.7 / 0                | 2.7 / 0 | ns    |

|                                                                                                                                                                                                                                                   |                                      | XCV3200E | 2.8 / 0 | 2.8 / 0 | 2.8 / 0                | 2.8 / 0 | ns    |

#### Notes:

- 1. IFF = Input Flip-Flop or Latch

- 2. Setup time is measured relative to the Global Clock input signal with the fastest route and the lightest load. Hold time is measured relative to the Global Clock input signal with the slowest route and heaviest load.

- 3. A Zero "0" Hold Time listing indicates no hold time or a negative hold time. Negative values can not be guaranteed "best-case", but if a "0" is listed, there is no positive hold time.

## **DLL Timing Parameters**

All devices are 100 percent functionally tested. Because of the difficulty in directly measuring many internal timing parameters, those parameters are derived from benchmark timing patterns. The following guidelines reflect worst-case values across the recommended operating conditions.

|                                  |                    |                    | Speed Grade |     |     |     |       |     |       |

|----------------------------------|--------------------|--------------------|-------------|-----|-----|-----|-------|-----|-------|

|                                  |                    |                    | -           | -8  | -7  |     | -7 -6 |     |       |

| Description                      | Symbol             | F <sub>CLKIN</sub> | Min         | Max | Min | Max | Min   | Max | Units |

| Input Clock Frequency (CLKDLLHF) | FCLKINHF           |                    | 60          | 350 | 60  | 320 | 60    | 275 | MHz   |

| Input Clock Frequency (CLKDLL)   | FCLKINLF           |                    | 25          | 160 | 25  | 160 | 25    | 135 | MHz   |

| Input Clock Low/High Pulse Width | T <sub>DLLPW</sub> | ≥2□5 MHz           | 5.0         |     | 5.0 |     | 5.0   |     | ns    |

|                                  |                    | ≥□50 MHz           | 3.0         |     | 3.0 |     | 3.0   |     | ns    |

|                                  |                    | ≥100 MHz           | 2.4         |     | 2.4 |     | 2.4   |     | ns    |

|                                  |                    | ≥□150<br>MHz       | 2.0         |     | 2.0 |     | 2.0   |     | ns    |

|                                  |                    | ≥□200<br>MHz       | 1.8         |     | 1.8 |     | 1.8   |     | ns    |

|                                  |                    | ≥□250<br>MHz       | 1.5         |     | 1.5 |     | 1.5   |     | ns    |

|                                  |                    | ≥□300<br>MHz       | 1.3         |     | 1.3 |     | NA    |     | ns    |

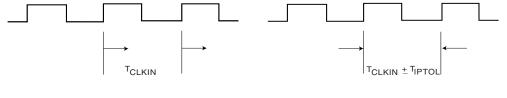

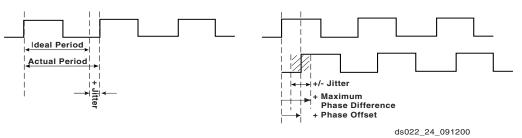

Period Tolerance: the allowed input clock period change in nanoseconds.

Output Jitter: the difference between an ideal Phase reference clock edge and the actual design.

Phase Offset and Maximum Phase Difference

Figure 4: DLL Timing Waveforms

*Table 8:* **HQ240** — **XCV600E**, **XCV1000E**

| Pin # | Pin Description | Bank |

|-------|-----------------|------|

| P138  | IO_D5_L26N_YY   | 3    |

| P137  | VCCINT          | NA   |

| P136  | VCCO            | 3    |

| P135  | GND             | NA   |

| P134  | IO_D6_L27P_Y    | 3    |

| P133  | IO_VREF_L27N_Y  | 3    |

| P132  | IO_VREF         | 3    |

| P131  | IO_L28P_Y       | 3    |

| P130  | IO_VREF_L28N_Y  | 3    |

| P129  | GND             | NA   |

| P128  | IO_L29P_Y       | 3    |

| P127  | IO_L29N_Y       | 3    |

| P126  | IO_VREF_L30P_Y  | 3    |

| P125  | IO_L30N_Y       | 3    |

| P124  | IO_D7_L31P_YY   | 3    |

| P123  | IO_INIT_L31N_YY | 3    |

| P122  | PROGRAM         | NA   |

| P121  | VCCO            | 3    |

| P120  | DONE            | 3    |

| P119  | GND             | NA   |

| P118  | IO_L32P_YY      | 4    |

| P117  | IO_L32N_YY      | 4    |

| P116  | VCCO            | 4    |

| P115  | IO_VREF         | 4    |

| P114  | IO_L33P_YY      | 4    |

| P113  | IO_L33N_YY      | 4    |

| P112  | GND             | NA   |

| P111  | IO_VREF_L34P_YY | 4    |

| P110  | IO_L34N_YY      | 4    |

| P109  | IO_VREF         | 4    |

| P108  | IO_VREF_L35P_YY | 4    |

| P107  | IO_L35N_YY      | 4    |

| P106  | GND             | NA   |

| P105  | VCCO            | 4    |

| P104  | VCCINT          | NA   |

| P103  | IO_L36P_YY      | 4    |

Table 8: HQ240 — XCV600E, XCV1000E

| Pin #             | Pin Description  | Bank |

|-------------------|------------------|------|

| P102              | IO_L36N_YY       | 4    |

| P101 <sup>1</sup> | IO_VREF          | 4    |

| P100              | IO_L37P_Y        | 4    |

| P99               | IO_L37N_Y        | 4    |

| P98               | GND              | NA   |

| P97               | IO_VREF_L38P_Y   | 4    |

| P96               | IO_L38N_Y        | 4    |

| P95               | IO_L39P          | 4    |

| P94               | IO_VREF_L39N     | 4    |

| P93               | IO_LVDS_DLL_L40P | 4    |

| P92               | GCK0             | 4    |

| P91               | GND              | NA   |

| P90               | VCCO             | 4    |

| P89               | GCK1             | 5    |

| P88               | VCCINT           | NA   |

| P87               | IO_LVDS_DLL_L40N | 5    |

| P86               | IO_VREF          | 5    |

| P85               | VCCO             | 5    |

| P84               | IO_VREF_L41P     | 5    |

| P83               | GND              | NA   |

| P82               | IO_L41N          | 5    |

| P81               | IO               | 5    |

| P80 <sup>1</sup>  | IO_VREF          | 5    |

| P79               | IO_L42P_YY       | 5    |

| P78               | IO_L42N_YY       | 5    |

| P77               | VCCINT           | NA   |

| P76               | VCCO             | 5    |

| P75               | GND              | NA   |

| P74               | IO_L43P_YY       | 5    |

| P73               | IO_VREF_L43N_YY  | 5    |

| P72               | IO_VREF          | 5    |

| P71               | IO_L44P_YY       | 5    |

| P70               | IO_VREF_L44N_YY  | 5    |

| P69               | GND              | NA   |

| P68               | IO_L45P_YY       | 5    |

| P67               | IO_L45N_YY       | 5    |

Table 12: BG432 — XCV300E, XCV400E, XCV600E

| Bank | Pin Description  | Pin #             |

|------|------------------|-------------------|

| 4    | IO_L70N_Y        | AK4               |

| 4    | IO_L71P_YY       | AJ5               |

| 4    | IO_L71N_YY       | AH6               |

| 4    | IO_VREF_L72P_YY  | AL4               |

| 4    | IO_L72N_YY       | AK5               |

| 4    | IO_L73P_Y        | AJ6               |

| 4    | IO_L73N_Y        | AH7               |

| 4    | IO_L74P_YY       | AL5               |

| 4    | IO_L74N_YY       | AK6               |

| 4    | IO_VREF_L75P_YY  | AJ7               |

| 4    | IO_L75N_YY       | AL6               |

| 4    | IO_L76P_Y        | AH9               |

| 4    | IO_L76N_Y        | AJ8               |

| 4    | IO_VREF_L77P_Y   | AK8 <sup>1</sup>  |

| 4    | IO_L77N_Y        | AJ9               |

| 4    | IO_VREF_L78P_YY  | AL8               |

| 4    | IO_L78N_YY       | AK9               |

| 4    | IO_L79P_YY       | AK10              |

| 4    | IO_L79N_YY       | AL10              |

| 4    | IO_L80P_YY       | AH12              |

| 4    | IO_L80N_YY       | AK11              |

| 4    | IO_L81P_YY       | AJ12              |

| 4    | IO_L81N_YY       | AK12              |

| 4    | IO_L82P_YY       | AH13              |

| 4    | IO_L82N_YY       | AJ13              |

| 4    | IO_VREF_L83P_YY  | AL13              |

| 4    | IO_L83N_YY       | AK14              |

| 4    | IO_L84P_Y        | AH14              |

| 4    | IO_L84N_Y        | AJ14              |

| 4    | IO_VREF_L85P_Y   | AK15 <sup>2</sup> |

| 4    | IO_L85N_Y        | AJ15              |

| 4    | IO_LVDS_DLL_L86P | AH15              |

|      |                  |                   |

| 5    | GCK1             | AK16              |

| 5    | 10               | AH20              |

| 5    | Ю                | AJ19              |

Table 12: BG432 — XCV300E, XCV400E, XCV600E