Welcome to **E-XFL.COM**

# Understanding <u>Embedded - FPGAs (Field Programmable Gate Array)</u>

Embedded - FPGAs, or Field Programmable Gate Arrays, are advanced integrated circuits that offer unparalleled flexibility and performance for digital systems. Unlike traditional fixed-function logic devices, FPGAs can be programmed and reprogrammed to execute a wide array of logical operations, enabling customized functionality tailored to specific applications. This reprogrammability allows developers to iterate designs quickly and implement complex functions without the need for custom hardware.

#### **Applications of Embedded - FPGAs**

The versatility of Embedded - FPGAs makes them indispensable in numerous fields. In telecommunications.

| Details                        |                                                             |

|--------------------------------|-------------------------------------------------------------|

| Product Status                 | Obsolete                                                    |

| Number of LABs/CLBs            | 2400                                                        |

| Number of Logic Elements/Cells | 10800                                                       |

| Total RAM Bits                 | 163840                                                      |

| Number of I/O                  | 404                                                         |

| Number of Gates                | 569952                                                      |

| Voltage - Supply               | 1.71V ~ 1.89V                                               |

| Mounting Type                  | Surface Mount                                               |

| Operating Temperature          | 0°C ~ 85°C (TJ)                                             |

| Package / Case                 | 676-BGA                                                     |

| Supplier Device Package        | 676-FBGA (27x27)                                            |

| Purchase URL                   | https://www.e-xfl.com/product-detail/xilinx/xcv400e-8fg676c |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

Table 1: Supported I/O Standards

| I/O           | Output           | Input     | Input            | Board<br>Termination       |

|---------------|------------------|-----------|------------------|----------------------------|

| Standard      | v <sub>cco</sub> | $v_{cco}$ | V <sub>REF</sub> | Voltage (V <sub>TT</sub> ) |

| LVTTL         | 3.3              | 3.3       | N/A              | N/A                        |

| LVCMOS2       | 2.5              | 2.5       | N/A              | N/A                        |

| LVCMOS18      | 1.8              | 1.8       | N/A              | N/A                        |

| SSTL3   & II  | 3.3              | N/A       | 1.50             | 1.50                       |

| SSTL2   & II  | 2.5              | N/A       | 1.25             | 1.25                       |

| GTL           | N/A              | N/A       | 0.80             | 1.20                       |

| GTL+          | N/A              | N/A       | 1.0              | 1.50                       |

| HSTL I        | 1.5              | N/A       | 0.75             | 0.75                       |

| HSTL III & IV | 1.5              | N/A       | 0.90             | 1.50                       |

| CTT           | 3.3              | N/A       | 1.50             | 1.50                       |

| AGP-2X        | 3.3              | N/A       | 1.32             | N/A                        |

| PCl33_3       | 3.3              | 3.3       | N/A              | N/A                        |

| PCI66_3       | 3.3              | 3.3       | N/A              | N/A                        |

| BLVDS & LVDS  | 2.5              | N/A       | N/A              | N/A                        |

| LVPECL        | 3.3              | N/A       | N/A              | N/A                        |

In addition to the CLK and CE control signals, the three flip-flops share a Set/Reset (SR). For each flip-flop, this signal can be independently configured as a synchronous Set, a synchronous Reset, an asynchronous Preset, or an asynchronous Clear.

The output buffer and all of the IOB control signals have independent polarity controls.

All pads are protected against damage from electrostatic discharge (ESD) and from over-voltage transients. After configuration, clamping diodes are connected to  $V_{CCO}$  with the exception of LVCMOS18, LVCMOS25, GTL, GTL+, LVDS, and LVPECL.

Optional pull-up, pull-down and weak-keeper circuits are attached to each pad. Prior to configuration all outputs not involved in configuration are forced into their high-impedance state. The pull-down resistors and the weak-keeper circuits are inactive, but I/Os can optionally be pulled up.

The activation of pull-up resistors prior to configuration is controlled on a global basis by the configuration mode pins. If the pull-up resistors are not activated, all the pins are in a high-impedance state. Consequently, external pull-up or pull-down resistors must be provided on pins required to be at a well-defined logic level prior to configuration.

All Virtex-E IOBs support IEEE 1149.1-compatible Boundary Scan testing.

### Input Path

The Virtex-E IOB input path routes the input signal directly to internal logic and/ or through an optional input flip-flop.

An optional delay element at the D-input of this flip-flop eliminates pad-to-pad hold time. The delay is matched to the internal clock-distribution delay of the FPGA, and when used, assures that the pad-to-pad hold time is zero.

Each input buffer can be configured to conform to any of the low-voltage signalling standards supported. In some of these standards the input buffer utilizes a user-supplied threshold voltage,  $V_{REF}$  The need to supply  $V_{REF}$  imposes constraints on which standards can be used in close proximity to each other. See **I/O Banking**.

There are optional pull-up and pull-down resistors at each user I/O input for use after configuration. Their value is in the range  $50-100~k\Omega$ .

# **Output Path**

The output path includes a 3-state output buffer that drives the output signal onto the pad. The output signal can be routed to the buffer directly from the internal logic or through an optional IOB output flip-flop.

The 3-state control of the output can also be routed directly from the internal logic or through a flip-flip that provides synchronous enable and disable.

Each output driver can be individually programmed for a wide range of low-voltage signalling standards. Each output buffer can source up to 24 mA and sink up to 48 mA. Drive strength and slew rate controls minimize bus transients.

In most signalling standards, the output High voltage depends on an externally supplied  $V_{CCO}$  voltage. The need to supply  $V_{CCO}$  imposes constraints on which standards can be used in close proximity to each other. See <code>I/O Banking</code>.

An optional weak-keeper circuit is connected to each output. When selected, the circuit monitors the voltage on the pad and weakly drives the pin High or Low to match the input signal. If the pin is connected to a multiple-source signal, the weak keeper holds the signal in its last state if all drivers are disabled. Maintaining a valid logic level in this way eliminates bus chatter.

Since the weak-keeper circuit uses the IOB input buffer to monitor the input level, an appropriate  $V_{REF}$  voltage must be provided if the signalling standard requires one. The provision of this voltage must comply with the I/O banking rules.

#### I/O Banking

Some of the I/O standards described above require  $V_{CCO}$  and/or  $V_{REF}$  voltages. These voltages are externally supplied and connected to device pins that serve groups of IOBs, called banks. Consequently, restrictions exist about which I/O standards can be combined within a given bank.

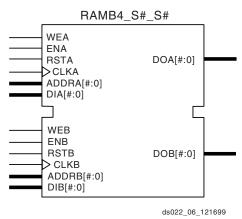

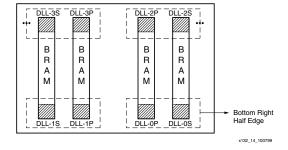

Figure 6: Dual-Port Block SelectRAM

Table 5 shows the depth and width aspect ratios for the block SelectRAM. The Virtex-E block SelectRAM also includes dedicated routing to provide an efficient interface with both CLBs and other block SelectRAMs. Refer to XAPP130 for block SelectRAM timing waveforms.

Table 5: Block SelectRAM Port Aspect Ratios

| Width | Depth | ADDR Bus             | Data Bus |

|-------|-------|----------------------|----------|

| 1     | 4096  | ADDR<11:0> DATA<0>   |          |

| 2     | 2048  | ADDR<10:0> DATA<1:0> |          |

| 4     | 1024  | ADDR<9:0> DATA<3:0>  |          |

| 8     | 512   | ADDR<8:0> DATA<7:0   |          |

| 16    | 256   | ADDR<7:0> DATA<15:0> |          |

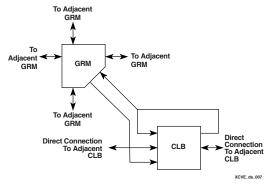

#### **Programmable Routing Matrix**

It is the longest delay path that limits the speed of any worst-case design. Consequently, the Virtex-E routing architecture and its place-and-route software were defined in a joint optimization process. This joint optimization minimizes long-path delays, and consequently, yields the best system performance.

The joint optimization also reduces design compilation times because the architecture is software-friendly. Design cycles are correspondingly reduced due to shorter design iteration times.

#### Local Routing

The VersaBlock provides local routing resources (see Figure 7), providing three types of connections:

- Interconnections among the LUTs, flip-flops, and GRM

- Internal CLB feedback paths that provide high-speed connections to LUTs within the same CLB, chaining them together with minimal routing delay

Direct paths that provide high-speed connections between horizontally adjacent CLBs, eliminating the delay of the GRM.

Figure 7: Virtex-E Local Routing

### General Purpose Routing

Most Virtex-E signals are routed on the general purpose routing, and consequently, the majority of interconnect resources are associated with this level of the routing hierarchy. General-purpose routing resources are located in horizontal and vertical routing channels associated with the CLB rows and columns and are as follows:

- Adjacent to each CLB is a General Routing Matrix (GRM). The GRM is the switch matrix through which horizontal and vertical routing resources connect, and is also the means by which the CLB gains access to the general purpose routing.

- 24 single-length lines route GRM signals to adjacent GRMs in each of the four directions.

- 72 buffered Hex lines route GRM signals to another GRMs six-blocks away in each one of the four directions. Organized in a staggered pattern, Hex lines are driven only at their endpoints. Hex-line signals can be accessed either at the endpoints or at the midpoint (three blocks from the source). One third of the Hex lines are bidirectional, while the remaining ones are uni-directional.

- 12 Longlines are buffered, bidirectional wires that distribute signals across the device quickly and efficiently. Vertical Longlines span the full height of the device, and horizontal ones span the full width of the device.

#### I/O Routing

Virtex-E devices have additional routing resources around their periphery that form an interface between the CLB array and the IOBs. This additional routing, called the VersaRing, facilitates pin-swapping and pin-locking, such that logic redesigns can adapt to existing PCB layouts. Time-to-market is reduced, since PCBs and other system components can be manufactured while the logic design is still in progress.

#### Data Registers

The primary data register is the Boundary Scan register. For each IOB pin in the FPGA, bonded or not, it includes three bits for In, Out, and 3-State Control. Non-IOB pins have appropriate partial bit population if input-only or output-only. Each EXTEST CAPTURED-OR state captures all In, Out, and 3-state pins.

The other standard data register is the single flip-flop BYPASS register. It synchronizes data being passed through the FPGA to the next downstream Boundary Scan device.

The FPGA supports up to two additional internal scan chains that can be specified using the BSCAN macro. The macro provides two user pins (SEL1 and SEL2) which are decodes of the USER1 and USER2 instructions respectively. For these instructions, two corresponding pins (T DO1 and TDO2) allow user scan data to be shifted out of TDO.

Likewise, there are individual clock pins (DRCK1 and DRCK2) for each user register. There is a common input pin (TDI) and shared output pins that represent the state of the TAP controller (RESET, SHIFT, and UPDATE).

### Bit Sequence

The order within each IOB is: In, Out, 3-State. The input-only pins contribute only the In bit to the Boundary Scan I/O data register, while the output-only pins contributes all three bits.

From a cavity-up view of the chip (as shown in EPIC), starting in the upper right chip corner, the Boundary Scan data-register bits are ordered as shown in Figure 12.

| Bit 0 ( TDO end)<br>Bit 1 | Right half of top-edge IOBs (Right to Left)    |

|---------------------------|------------------------------------------------|

| Bit 2                     | GCLK2<br>GCLK3                                 |

|                           | Left half of top-edge IOBs (Right to Left)     |

|                           | Left-edge IOBs (Top to Bottom)                 |

|                           | M1<br>M0<br>M2                                 |

|                           | Left half of bottom-edge IOBs (Left to Right)  |

|                           | GCLK1<br>GCLK0                                 |

|                           | Right half of bottom-edge IOBs (Left to Right) |

|                           | DONE<br>PROG                                   |

|                           | Right-edge IOBs (Bottom to Top)                |

| (TDI end)                 | CCLK                                           |

|                           | 990602001                                      |

Figure 12: Boundary Scan Bit Sequence

BSDL (Boundary Scan Description Language) files for Virtex-E Series devices are available on the Xilinx web site in the File Download area.

### Identification Registers

The IDCODE register is supported. By using the IDCODE, the device connected to the JTAG port can be determined.

The IDCODE register has the following binary format:

vvvv:ffff:fffa:aaaa:aaaa:cccc:cccc1

#### where

v = the die version number

f = the family code (05 for Virtex-E family)

a = the number of CLB rows (ranges from 16 for

XCV50E to 104 for XCV3200E)

c = the company code (49h for Xilinx)

The USERCODE register is supported. By using the USERCODE, a user-programmable identification code can be loaded and shifted out for examination. The identification code (see Table 7) is embedded in the bitstream during bitstream generation and is valid only after configuration.

Table 7: IDCODEs Assigned to Virtex-E FPGAs

| FPGA     | IDCODE    |

|----------|-----------|

| XCV50E   | v0A10093h |

| XCV100E  | v0A14093h |

| XCV200E  | v0A1C093h |

| XCV300E  | v0A20093h |

| XCV400E  | v0A28093h |

| XCV600E  | v0A30093h |

| XCV1000E | v0A40093h |

| XCV1600E | v0A48093h |

| XCV2000E | v0A50093h |

| XCV2600E | v0A5C093h |

| XCV3200E | v0A68093h |

#### Note:

Attempting to load an incorrect bitstream causes configuration to fail and can damage the device.

### Including Boundary Scan in a Design

Since the Boundary Scan pins are dedicated, no special element needs to be added to the design unless an internal data register (USER1 or USER2) is desired.

If an internal data register is used, insert the Boundary Scan symbol and connect the necessary pins as appropriate.

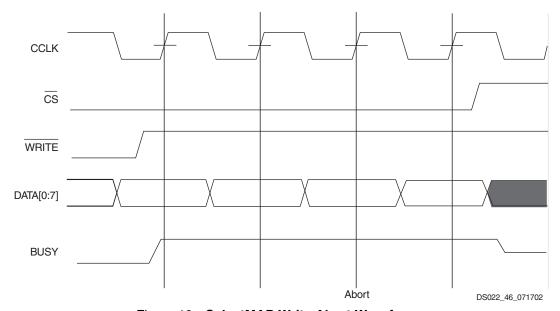

Figure 18: SelectMAP Flowchart for Write Operations

Figure 19: SelectMAP Write Abort Waveforms

# **Boundary Scan Mode**

In the Boundary Scan mode, configuration is done through the IEEE 1149.1 Test Access Port. Note that the PROGRAM pin must be pulled High prior to reconfiguration. A Low on the PROGRAM pin resets the TAP controller and no JTAG operations can be performed.

### **DLL Properties**

Properties provide access to some of the Virtex-E series DLL features, (for example, clock division and duty cycle correction).

### **Duty Cycle Correction Property**

The 1x clock outputs, CLK0, CLK90, CLK180, and CLK270, use the duty-cycle corrected default, exhibiting a 50/50 duty cycle. The DUTY\_CYCLE\_CORRECTION property (by default TRUE) controls this feature. To deactivate the DLL duty-cycle correction for the 1x clock outputs, attach the DUTY\_CYCLE\_CORRECTION=FALSE property to the DLL symbol.

## **Clock Divide Property**

The CLKDV\_DIVIDE property specifies how the signal on the CLKDV pin is frequency divided with respect to the CLK0 pin. The values allowed for this property are 1.5, 2, 2.5, 3, 4, 5, 8, or 16; the default value is 2.

## Startup Delay Property

This property, STARTUP\_WAIT, takes on a value of TRUE or FALSE (the default value). When TRUE the device configuration DONE signal waits until the DLL locks before going to High.

#### Virtex-E DLL Location Constraints

As shown in Figure 26, there are four additional DLLs in the Virtex-E devices, for a total of eight per Virtex-E device. These DLLs are located in silicon, at the top and bottom of the two innermost block SelectRAM columns. The location constraint LOC, attached to the DLL symbol with the identifier DLL0S, DLL0P, DLL1S, DLL1P, DLL2S, DLL2P, DLL3S, or DLL3P, controls the DLL location.

The LOC property uses the following form:

LOC = DLL0P

Figure 26: Virtex Series DLLs

### **Design Factors**

Use the following design considerations to avoid pitfalls and improve success designing with Xilinx devices.

### Input Clock

The output clock signal of a DLL, essentially a delayed version of the input clock signal, reflects any instability on the input clock in the output waveform. For this reason the quality of the DLL input clock relates directly to the quality of the output clock waveforms generated by the DLL. The DLL input clock requirements are specified in the data sheet.

In most systems a crystal oscillator generates the system clock. The DLL can be used with any commercially available quartz crystal oscillator. For example, most crystal oscillators produce an output waveform with a frequency tolerance of 100 PPM, meaning 0.01 percent change in the clock period. The DLL operates reliably on an input waveform with a frequency drift of up to 1 ns — orders of magnitude in excess of that needed to support any crystal oscillator in the industry. However, the cycle-to-cycle jitter must be kept to less than 300 ps in the low frequencies and 150 ps for the high frequencies.

### Input Clock Changes

Changing the period of the input clock beyond the maximum drift amount requires a manual reset of the CLKDLL. Failure to reset the DLL produces an unreliable lock signal and output clock.

It is possible to stop the input clock with little impact to the DLL. Stopping the clock should be limited to less than 100  $\mu s$  to keep device cooling to a minimum. The clock should be stopped during a Low phase, and when restored the full High period should be seen. During this time, LOCKED stays High and remains High when the clock is restored.

When the clock is stopped, one to four more clocks are still observed as the delay line is flushed. When the clock is restarted, the output clocks are not observed for one to four clocks as the delay line is filled. The most common case is two or three clocks.

In a similar manner, a phase shift of the input clock is also possible. The phase shift propagates to the output one to four clocks after the original shift, with no disruption to the CLKDLL control.

#### **Output Clocks**

As mentioned earlier in the DLL pin descriptions, some restrictions apply regarding the connectivity of the output pins. The DLL clock outputs can drive an OBUF, a global clock buffer BUFG, or they can route directly to destination clock pins. The only BUFGs that the DLL clock outputs can drive are the two on the same edge of the device (top or bottom). In addition, the CLK2X output of the secondary DLL can connect directly to the CLKIN of the primary DLL in the same quadrant.

Do not use the DLL output clock signals until after activation of the LOCKED signal. Prior to the activation of the LOCKED signal, the DLL output clocks are not valid and can exhibit glitches, spikes, or other spurious movement.

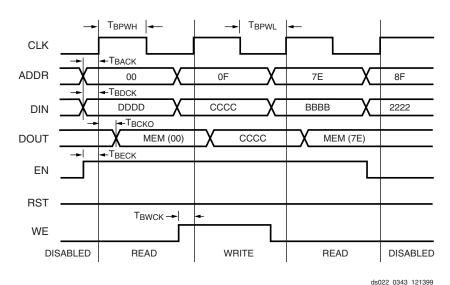

indicating that the block SelectRAM+ memory is now disabled. The DO bus retains the last value.

#### **Dual Port Timing**

Figure 34 shows a timing diagram for a true dual-port read/write block SelectRAM+ memory. The clock on port A has a longer period than the clock on Port B. The timing parameter  $T_{BCCS}$ , (clock-to-clock set-up) is shown on this diagram. The parameter,  $T_{BCCS}$  is violated once in the diagram. All other timing parameters are identical to the single port version shown in Figure 33.

T<sub>BCCS</sub> is only of importance when the address of both ports are the same and at least one port is performing a write operation. When the clock-to-clock set-up parameter is violated for a WRITE-WRITE condition, the contents of the memory at that location are invalid. When the clock-to-clock set-up parameter is violated for a WRITE-READ condition,

the contents of the memory are correct, but the read port has invalid data.

At the first rising edge of the CLKA, memory location 0x00 is to be written with the value 0xAAAA and is mirrored on the DOA bus. The last operation of Port B was a read to the same memory location 0x00. The DOB bus of Port B does not change with the new value on Port A, and retains the last read value. A short time later, Port B executes another read to memory location 0x00, and the DOB bus now reflects the new memory value written by Port A.

At the second rising edge of CLKA, memory location 0x7E is written with the value 0x9999 and is mirrored on the DOA bus. Port B then executes a read operation to the same memory location without violating the  $T_{BCCS}$  parameter and the DOB reflects the new memory values written by Port A.

Figure 33: Timing Diagram for Single Port Block SelectRAM+ Memory

### **Verilog Initialization Example**

```

module MYMEM (CLK, WE, ADDR, DIN, DOUT);

input CLK, WE;

input [8:0] ADDR;

input [7:0] DIN;

output [7:0] DOUT;

wire logic0, logic1;

//synopsys dc script begin

//set_attribute ram0 INIT_00

"0123456789ABCDEF0123456789ABCDEF0123456789ABCDEF0123456789ABCDEF" -type string

//set attribute ram0 INIT 01

"FEDCBA9876543210FEDCBA9876543210FEDCBA9876543210FEDCBA9876543210" -type string

//synopsys dc_script_end

assign logic0 = 1'b0;

assign logic1 = 1'b1;

RAMB4 S8 ram0 (.WE(WE), .EN(logic1), .RST(logic0), .CLK(CLK), .ADDR(ADDR), .DI(DIN),

.DO(DOUT));

//synopsys translate off

defparam ram0.INIT_00 =

256h'0123456789ABCDEF0123456789ABCDEF0123456789ABCDEF;

defparam ram0.INIT 01 =

256h'FEDCBA9876543210FEDCBA9876543210FEDCBA9876543210FEDCBA9876543210;

//synopsys translate on

endmodule

```

# **Using SelectI/O**

The Virtex-E FPGA series includes a highly configurable, high-performance I/O resource, called SelectI/O™ to provide support for a wide variety of I/O standards. The SelectI/O resource is a robust set of features including programmable control of output drive strength, slew rate, and input delay and hold time. Taking advantage of the flexibility and SelectI/O features and the design considerations described in this document can improve and simplify system level design.

### Introduction

As FPGAs continue to grow in size and capacity, the larger and more complex systems designed for them demand an increased variety of I/O standards. Furthermore, as system clock speeds continue to increase, the need for high performance I/O becomes more important.

While chip-to-chip delays have an increasingly substantial impact on overall system speed, the task of achieving the desired system performance becomes more difficult with the proliferation of low-voltage I/O standards. SelectI/O, the revolutionary input/output resources of Virtex-E devices, resolve this potential problem by providing a highly configurable, high-performance alternative to the I/O resources of more conventional programmable devices. Virtex-E SelectI/O features combine the flexibility and time-to-market advantages of programmable logic with the high performance previously available only with ASICs and custom ICs.

Each SelectI/O block can support up to 20 I/O standards. Supporting such a variety of I/O standards allows the support of a wide variety of applications, from general purpose standard applications to high-speed low-voltage memory buses.

SelectI/O blocks also provide selectable output drive strengths and programmable slew rates for the LVTTL output buffers, as well as an optional, programmable weak pull-up, weak pull-down, or weak "keeper" circuit ideal for use in external bussing applications.

Each Input/Output Block (IOB) includes three registers, one each for the input, output, and 3-state signals within the IOB. These registers are optionally configurable as either a D-type flip-flop or as a level sensitive latch.

The input buffer has an optional delay element used to guarantee a zero hold time requirement for input signals registered within the IOB.

The Virtex-E Selectl/O features also provide dedicated resources for input reference voltage ( $V_{REF}$ ) and output source voltage ( $V_{CCO}$ ), along with a convenient banking system that simplifies board design.

By taking advantage of the built-in features and wide variety of I/O standards supported by the SelectI/O features, system-level design and board design can be greatly simplified and improved.

XILINX®

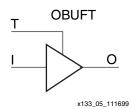

LVTTL 3-state output buffers have selectable drive strengths.

The format for LVTTL OBUFT symbol names is as follows:

OBUFT\_<slew\_rate>\_<drive\_strength>

where <slew\_rate> is either F (Fast) or S (Slow), and <drive\_strength> is specified in milliamps (2, 4, 6, 8, 12, 16, or 24).

Figure 41: 3-State Output Buffer Symbol (OBUFT)

The following list details variations of the OBUFT symbol.

- OBUFT

- OBUFT S 2

- OBUFT\_S\_4

- OBUFT\_S\_6

- OBUFT\_S\_8

- OBUFT S 12

- OBUFT\_S\_16

- OBUFT\_S\_24

- OBUFT\_F\_2

- OBUFT\_F\_4

- OBUFT\_F\_6

- OBUFT\_F\_8

- OBUFT\_F\_12

- OBUFT\_F\_16

- OBUFT\_F\_24

- OBUFT\_LVCMOS2

- OBUFT PCI33 3

- OBUFT\_PCI66\_3

- OBUFT\_GTL

- OBUFT\_GTLP

- OBUFT HSTL I

- OBUFT\_HSTL\_III

- OBUFT\_HSTL\_IV

- OBUFT\_SSTL3\_I

- OBUFT\_SSTL3\_II

- OBUFT\_SSTL2\_I

- OBUFT\_SSTL2\_II

- OBUFT CTT

- OBUFT\_AGP

- OBUFT\_LVCMOS18

- OBUFT\_LVDS

- OBUFT\_LVPECL

The Virtex-E series supports eight banks for the HQ and PQ packages. The CS package supports four  $V_{CCO}$  banks.

The SelectI/O OBUFT placement restrictions require that within a given  $V_{CCO}$  bank each OBUFT share the same output source drive voltage. Input buffers of any type and output buffers that do not require  $V_{CCO}$  can be placed within the same  $V_{CCO}$  bank.

The LOC property can specify a location for the OBUFT.

3-state output buffers and bidirectional buffers can have either a weak pull-up resistor, a weak pull-down resistor, or a weak "keeper" circuit. Control this feature by adding the appropriate symbol to the output net of the OBUFT (PULLUP, PULLDOWN, or KEEPER).

The weak "keeper" circuit requires the input buffer within the IOB to sample the I/O signal. So, OBUFTs programmed for an I/O standard that requires a  $V_{REF}$  have automatic placement of a  $V_{REF}$  in the bank with an OBUFT configured with a weak "keeper" circuit. This restriction does not affect most circuit design as applications using an OBUFT configured with a weak "keeper" typically implement a bidirectional I/O. In this case the IBUF (and the corresponding  $V_{REF}$ ) are explicitly placed.

The LOC property can specify a location for the OBUFT.

#### *IOBUF*

Use the IOBUF symbol for bidirectional signals that require both an input buffer and a 3-state output buffer with an active high 3-state pin. The generic input/output buffer IOBUF appears in Figure 42.

The extension to the base name defines which I/O standard the IOBUF uses. With no extension specified for the generic IOBUF symbol, the assumed standard is LVTTL input buffer and slew rate limited LVTTL with 12 mA drive strength for the output buffer.

The LVTTL IOBUF additionally can support one of two slew rate modes to minimize bus transients. By default, the slew rate for each output buffer is reduced to minimize power bus transients when switching non-critical signals.

LVTTL bidirectional buffers have selectable output drive strengths.

The format for LVTTL IOBUF symbol names is as follows:

IOBUF\_<slew\_rate>\_<drive\_strength>

where <slew\_rate> is either F (Fast) or S (Slow), and <drive\_strength> is specified in milliamps (2, 4, 6, 8, 12, 16, or 24).

Table 43: Output Library Macros

| Table 40: Output Library muoros |               |         |  |  |

|---------------------------------|---------------|---------|--|--|

| Name                            | Inputs        | Outputs |  |  |

| OBUFDS_FD_LVDS                  | D, C          | O, OB   |  |  |

| OBUFDS_FDE_LVDS                 | DD, CE, C     | O, OB   |  |  |

| OBUFDS_FDC_LVDS                 | D, C, CLR     | O, OB   |  |  |

| OBUFDS_FDCE_LVDS                | D, CE, C, CLR | O, OB   |  |  |

| OBUFDS_FDP_LVDS                 | D, C, PRE     | O, OB   |  |  |

| OBUFDS_FDPE_LVDS                | D, CE, C, PRE | O, OB   |  |  |

| OBUFDS_FDR_LVDS                 | D, C, R       | O, OB   |  |  |

| OBUFDS_FDRE_LVDS                | D, CE, C, R   | O, OB   |  |  |

| OBUFDS_FDS_LVDS                 | D, C, S       | O, OB   |  |  |

| OBUFDS_FDSE_LVDS                | D, CE, C, S   | O, OB   |  |  |

| OBUFDS_LD_LVDS                  | D, G          | O, OB   |  |  |

| OBUFDS_LDE_LVDS                 | D, GE, G      | O, OB   |  |  |

| OBUFDS_LDC_LVDS                 | D, G, CLR     | O, OB   |  |  |

| OBUFDS_LDCE_LVDS                | D, GE, G, CLR | O, OB   |  |  |

| OBUFDS_LDP_LVDS                 | D, G, PRE     | O, OB   |  |  |

| OBUFDS_LDPE_LVDS                | D, GE, G, PRE | O, OB   |  |  |

# **Creating LVDS Output 3-State Buffers**

LVDS output 3-state buffers can be placed in a wide number of IOB locations. The exact locations are dependent on the package used. The Virtex-E package information lists the possible locations as IO\_L#P for the P-side and IO\_L#N for the N-side, where # is the pair number.

#### **HDL** Instantiation

Both output 3-state buffers are required to be instantiated in the design and placed on the correct IO\_L#P and IO\_L#N locations. The IOB must have the same net source the following pins, clock (C), set/reset (SR), 3-state (T), 3-state clock enable (TCE), output (O), output clock enable (OCE). In addition, the output (O) pins must be inverted with respect to each other, and if output registers are used, the INIT states must be opposite values (one High and one Low). If 3-state registers are used, they must be initialized to the same state. Failure to follow these rules leads to DRC errors in the software.

#### **VHDL** Instantiation

```

data0_p: OBUFT_LVDS port map

(I=>data_int(0), T=>data_tri,

0=>data_p(0));

data0_inv: INV port map

(I=>data_int(0), O=>data_n_int(0));

data0_n: OBUFT_LVDS port map

(I=>data_n_int(0), T=>data_tri,

0=>data_n(0));

```

#### **Verilog Instantiation**

```

OBUFT_LVDS data0_p (.I(data_int[0]),

.T(data_tri), .O(data_p[0]));

INV          data0_inv (.I(data_int[0],

.O(data_n_int[0]);

OBUFT_LVDS data0_n (.I(data_n_int[0]),

.T(data_tri), .O(data_n[0]));

```

#### **Location Constraints**

All LVDS buffers must be explicitly placed on a device. For the output buffers this can be done with the following constraint in the .ucf or .ncf file.

```

NET data_p<0> LOC = D28; # IO_LOP

NET data_n<0> LOC = B29; # IO_LON

```

# Synchronous vs. Asynchronous 3-State Outputs

If the outputs are synchronous (registered in the IOB), then any IO\_L#PIN pair can be used. If the outputs are asynchronous (no output register), then they must use one of the pairs that are part of the same IOB group at the end of a ROW or COLUMN in the device. This applies for either the 3-state pin or the data out pin.

LVDS pairs that can be used as asynchronous outputs are listed in the Virtex-E pinout tables. Some pairs are marked as "asynchronous capable" for all devices in that package, and others are marked as available only for that device in the package. If the device size might be changed at some point in the product lifetime, then only the common pairs for all packages should be used.

# Adding Output and 3-State Registers

All LVDS buffers can have an output register in the IOB. The output registers must be in both the P-side and N-side IOBs. All the normal IOB register options are available (FD, FDE, FDC, FDCE, FDP, FDPE, FDR, FDRE, FDS, FDSE, LD, LDE, LDC, LDCE, LDP, LDPE). The register elements can be inferred or explicitly instantiated in the HDL code.

Special care must be taken to insure that the D pins of the registers are inverted and that the INIT states of the registers are opposite. The 3-state (T), 3-state clock enable (CE), clock pin (C), output clock enable (CE) and set/reset (CLR/PRE or S/R) pins must connect to the same source. Failure to do this leads to a DRC error in the software.

# Virtex<sup>™</sup>-E 1.8 V Field Programmable Gate Arrays

DS022-3 (v2.9.2) March 14, 2003

**Production Product Specification**

## Virtex-E Electrical Characteristics

### **Definition of Terms**

Electrical and switching characteristics are specified on a per-speed-grade basis and can be designated as Advance, Preliminary, or Production. Each designation is defined as follows:

**Advance**: These speed files are based on simulations only and are typically available soon after device design specifications are frozen. Although speed grades with this designation are considered relatively stable and conservative, some under-reporting might still occur.

**Preliminary**: These speed files are based on complete ES (engineering sample) silicon characterization. Devices and speed grades with this designation are intended to give a better indication of the expected performance of production silicon. The probability of under-reporting delays is greatly reduced as compared to Advance data.

**Production**: These speed files are released once enough production silicon of a particular device family member has been characterized to provide full correlation between speed files and devices over numerous production lots. There is no under-reporting of delays, and customers receive formal notification of any subsequent changes. Typically, the slowest speed grades transition to Production before faster speed grades.

All specifications are representative of worst-case supply voltage and junction temperature conditions. The parameters included are common to popular designs and typical applications. Contact the factory for design considerations requiring more detailed information.

Table 1 correlates the current status of each Virtex-E device with a corresponding speed file designation.

Table 1: Virtex-E Device Speed Grade Designations

|          | Speed Grade Designations |             |            |

|----------|--------------------------|-------------|------------|

| Device   | Advance                  | Preliminary | Production |

| XCV50E   |                          |             | -8, -7, -6 |

| XCV100E  |                          |             | -8, -7, -6 |

| XCV200E  |                          |             | -8, -7, -6 |

| XCV300E  |                          |             | -8, -7, -6 |

| XCV400E  |                          |             | -8, -7, -6 |

| XCV600E  |                          |             | -8, -7, -6 |

| XCV1000E |                          |             | -8, -7, -6 |

| XCV1600E |                          |             | -8, -7, -6 |

| XCV2000E |                          |             | -8, -7, -6 |

| XCV2600E |                          |             | -8, -7, -6 |

| XCV3200E |                          |             | -8, -7, -6 |

All specifications are subject to change without notice.

*Table 8:* **HQ240** — **XCV600E**, **XCV1000E**

| Pin #            | Pin Description | Bank |

|------------------|-----------------|------|

| P66              | IO_VREF_L46P    | 5    |

| P65              | IO_L46N         | 5    |

| P64              | IO_L47P_YY      | 5    |

| P63              | IO_L47N_YY      | 5    |

| P62              | M2              | NA   |

| P61              | VCCO            | 5    |

| P60              | MO              | NA   |

| P59              | GND             | NA   |

| P58              | M1              | NA   |

| P57              | IO_L48N_YY      | 6    |

| P56              | IO_L48P_YY      | 6    |

| P55              | VCCO            | 6    |

| P54              | IO_VREF         | 6    |

| P53              | IO_L49N_Y       | 6    |

| P52              | IO_L49P_Y       | 6    |

| P51              | GND             | NA   |

| P50              | IO_VREF_L50N_Y  | 6    |

| P49              | IO_L50P_Y       | 6    |

| P48              | IO_VREF         | 6    |

| P47              | IO_VREF_L51N_Y  | 6    |

| P46              | IO_L51P_Y       | 6    |

| P45              | GND             | NA   |

| P44              | VCCO            | 6    |

| P43              | VCCINT          | NA   |

| P42              | IO_L52N_YY      | 6    |

| P41              | IO_L52P_YY      | 6    |

| P40 <sup>1</sup> | IO_VREF         | 6    |

| P39              | IO_L53N_Y       | 6    |

| P38              | IO_L53P_Y       | 6    |

| P37              | GND             | NA   |

| P36              | IO_VREF_L54N_Y  | 6    |

| P35              | IO_L54P_Y       | 6    |

| P34              | IO_L55N_Y       | 6    |

| P33              | IO_VREF_L55P_Y  | 6    |

| P32              | VCCINT          | NA   |

| P31              | Ю               | 6    |

Table 8: HQ240 — XCV600E, XCV1000E

| Pin #            | Pin Description | Bank |

|------------------|-----------------|------|

| P30              | VCCO            | 6    |

| P29              | GND             | NA   |

| P28              | IO_L56N_YY      | 7    |

| P27              | IO_L56P_YY      | 7    |

| P26              | IO_VREF         | 7    |

| P25              | VCCO            | 7    |

| P24              | IO_L57N_Y       | 7    |

| P23              | IO_VREF_L57P_Y  | 7    |

| P22              | GND             | NA   |

| P21              | IO_L58N_Y       | 7    |

| P20              | IO_L58P_Y       | 7    |

| P19 <sup>1</sup> | IO_VREF         | 7    |

| P18              | IO_L59N_YY      | 7    |

| P17              | IO_L59P_YY      | 7    |

| P16              | VCCINT          | NA   |

| P15              | VCCO            | 7    |

| P14              | GND             | NA   |

| P13              | IO_L60N_Y       | 7    |

| P12              | IO_VREF_L60P_Y  | 7    |

| P11              | IO_VREF         | 7    |

| P10              | IO_L61N_Y       | 7    |

| P9               | IO_VREF_L61P_Y  | 7    |

| P8               | GND             | NA   |

| P7               | IO_L62N_Y       | 7    |

| P6               | IO_L62P_Y       | 7    |

| P5               | IO_VREF_L63N_Y  | 7    |

| P4               | IO_L63P_Y       | 7    |

| P3               | Ю               | 7    |

| P2               | TMS             | NA   |

| P1               | GND             | NA   |

1.  $V_{\mbox{REF}}$  or I/O option only in the XCV1000E; otherwise, I/O option only.

Table 10: BG352 — XCV100E, XCV200E, XCV300E

| Bank  | Pin Description | Pin # |

|-------|-----------------|-------|

| NA    | VCCINT          | V24   |

| NA    | VCCINT          | R23   |

| NA NA | VCCINT          | P25   |

| NA    | VCCINT          | L25   |

| NA    | VCCINT          | J24   |

| 147 ( | VOCIIVI         | 024   |

| 0     | VCCO            | D19   |

| 0     | VCCO            | B25   |

| 0     | VCCO            | A17   |

| 1     | VCCO            | D13   |

|       |                 | D13   |

| 1     | VCCO            | A10   |

|       |                 |       |

| 2     | VCCO            | K1    |

| 2     | VCCO            | H4    |

| 2     | VCCO            | B2    |

| 3     | VCCO            | Y4    |

| 3     | VCCO            | U1    |

| 3     | VCCO            | P4    |

| 4     | VCCO            | AF10  |

| 4     | VCCO            | AE2   |

| 4     | VCCO            | AC8   |

| 5     | VCCO            | AF17  |

| 5     | VCCO            | AC20  |

| 5     | VCCO            | AC14  |

| 6     | VCCO            | AE25  |

| 6     | VCCO            | W23   |

| 6     | VCCO            | U26   |

| 7     | VCCO            | N23   |

| 7     | VCCO            | K26   |

| 7     | VCCO            | G23   |

|       |                 |       |

| NA    | GND             | A26   |

| NA    | GND             | A25   |

| NA    | GND             | A22   |

Table 10: BG352 — XCV100E, XCV200E, XCV300E

| TABLE TO: BUDGE KOTTOOL, KOTZOOL, KOTOOCE |                 |       |  |

|-------------------------------------------|-----------------|-------|--|

| Bank                                      | Pin Description | Pin # |  |

| NA                                        | GND             | A19   |  |

| NA                                        | GND             | A14   |  |

| NA                                        | GND             | A8    |  |

| NA                                        | GND             | A5    |  |

| NA                                        | GND             | A2    |  |

| NA                                        | GND             | A1    |  |

| NA                                        | GND             | B26   |  |

| NA                                        | GND             | B1    |  |

| NA                                        | GND             | E26   |  |

| NA                                        | GND             | E1    |  |

| NA                                        | GND             | H26   |  |

| NA                                        | GND             | H1    |  |

| NA                                        | GND             | N1    |  |

| NA                                        | GND             | P26   |  |

| NA                                        | GND             | W26   |  |

| NA                                        | GND             | W1    |  |

| NA                                        | GND             | AB26  |  |

| NA                                        | GND             | AB1   |  |

| NA                                        | GND             | AE26  |  |

| NA                                        | GND             | AE1   |  |

| NA                                        | GND             | AF26  |  |

| NA                                        | GND             | AF25  |  |

| NA                                        | GND             | AF22  |  |

| NA                                        | GND             | AF19  |  |

| NA                                        | GND             | AF13  |  |

| NA                                        | GND             | AF8   |  |

| NA                                        | GND             | AF5   |  |

| NA                                        | GND             | AF2   |  |

| NA                                        | GND             | AF1   |  |

| <u> </u>                                  |                 |       |  |

- No Connect in the XCV100E.

- V<sub>REF</sub> or I/O option only in the XCV200E and XCV300E; otherwise, I/O option only.

*Table 14:* BG560 — XCV400E, XCV600E, XCV1000E, XCV1600E, XCV2000E

| Bank | Pin Description | Pin# | See Note |

|------|-----------------|------|----------|

| NA   | GND             | A29  |          |

| NA   | GND             | A32  |          |

| NA   | GND             | A33  |          |

| NA   | GND             | B1   |          |

| NA   | GND             | В6   |          |

| NA   | GND             | В9   |          |

| NA   | GND             | B15  |          |

| NA   | GND             | B23  |          |

| NA   | GND             | B27  |          |

| NA   | GND             | B31  |          |

| NA   | GND             | C2   |          |

| NA   | GND             | E1   |          |

| NA   | GND             | F32  |          |

| NA   | GND             | G2   |          |

| NA   | GND             | G33  |          |

| NA   | GND             | J32  |          |

| NA   | GND             | K1   |          |

| NA   | GND             | L2   |          |

| NA   | GND             | M33  |          |

| NA   | GND             | P1   |          |

| NA   | GND             | P33  |          |

| NA   | GND             | R32  |          |

| NA   | GND             | T1   |          |

| NA   | GND             | V33  |          |

| NA   | GND             | W2   |          |

| NA   | GND             | Y1   |          |

| NA   | GND             | Y33  |          |

| NA   | GND             | AB1  |          |

| NA   | GND             | AC32 |          |

| NA   | GND             | AD33 |          |

| NA   | GND             | AE2  |          |

| NA   | GND             | AG1  |          |

| NA   | GND             | AG32 |          |

| NA   | GND             | AH2  |          |

| NA   | GND             | AJ33 |          |

*Table 14:* BG560 — XCV400E, XCV600E, XCV1000E, XCV1600E, XCV2000E

| Bank | Pin Description | Pin# | See Note |

|------|-----------------|------|----------|

| NA   | GND             | AL32 |          |

| NA   | GND             | АМЗ  |          |

| NA   | GND             | AM7  |          |

| NA   | GND             | AM11 |          |

| NA   | GND             | AM19 |          |

| NA   | GND             | AM25 |          |

| NA   | GND             | AM28 |          |

| NA   | GND             | AM33 |          |

| NA   | GND             | AN1  |          |

| NA   | GND             | AN2  |          |

| NA   | GND             | AN5  |          |

| NA   | GND             | AN10 |          |

| NA   | GND             | AN14 |          |

| NA   | GND             | AN16 |          |

| NA   | GND             | AN20 |          |

| NA   | GND             | AN22 |          |

| NA   | GND             | AN27 |          |

| NA   | GND             | AN33 |          |

- 1.  $V_{\mbox{\scriptsize REF}}$  or I/O option only in the XCV2000E; otherwise, I/O option only.

- V<sub>REF</sub> or I/O option only in the XCV1600E & 2000E; otherwise, I/O option only.

- 3.  $V_{REF}$  or I/O option only in the XCV1000E, 1600E, & 2000E; otherwise, I/O option only.

- V<sub>REF</sub> or I/O option only in the XCV600E, 1000E, 1600E, & 2000E; otherwise, I/O option only.

Table 18: FG456 — XCV200E and XCV300E

| Bank | Pin Description | Pin # |

|------|-----------------|-------|

| NA   | GND             | M14   |

| NA   | GND             | M13   |

| NA   | GND             | M12   |

| NA   | GND             | M11   |

| NA   | GND             | M10   |

| NA   | GND             | M9    |

| NA   | GND             | L14   |

| NA   | GND             | L13   |

| NA   | GND             | L12   |

| NA   | GND             | L11   |

| NA   | GND             | L10   |

| NA   | GND             | L9    |

| NA   | GND             | K14   |

| NA   | GND             | K13   |

| NA   | GND             | K12   |

| NA   | GND             | K11   |

| NA   | GND             | K10   |

| NA   | GND             | K9    |

| NA   | GND             | J14   |

| NA   | GND             | J13   |

| NA   | GND             | J12   |

| NA   | GND             | J11   |

| NA   | GND             | J10   |

| NA   | GND             | J9    |

| NA   | GND             | C20   |

| NA   | GND             | C3    |

| NA   | GND             | B21   |

| NA   | GND             | B2    |

| NA   | GND             | A22   |

| NA   | GND             | A1    |

Note 1: NC in the XCV200E device.

#### **FG456 Differential Pin Pairs**

Virtex-E devices have differential pin pairs that can also provide other functions when not used as a differential pair. A  $\sqrt{}$  in the AO column indicates that the pin pair can be used as an asynchronous output for all devices provided in this package. Pairs with a note number in the AO column are device dependent. They can have asynchronous outputs if the pin pair are in the same CLB row and column in the device. Numbers in this column refer to footnotes that indicate which devices have pin pairs than can be asynchronous outputs. The Other Functions column indicates alternative function(s) not available when the pair is used as a differential pair or differential clock.

*Table 19:* **FG456 Differential Pin Pair Summary XCV200E, XCV300E**

|      |                           | Р        | N       |          | Other         |  |

|------|---------------------------|----------|---------|----------|---------------|--|

| Pair | Bank                      | Pin      | Pin     | AO       | Functions     |  |

|      | Global Differential Clock |          |         |          |               |  |

| 0    | 4                         | W12      | U12     | NA       | IO_DLL_L75P   |  |

| 1    | 5                         | Y11      | AA11    | NA       | IO_DLL_L75N   |  |

| 2    | 1                         | A11      | D11     | NA       | IO_DLL_L13P   |  |

| 3    | 0                         | C11      | B11     | NA       | IO_DLL_L13N   |  |

|      |                           | I        | O LVDS  |          |               |  |

| To   | tal Pairs:                | 119, Asy | nchrono | us Outp  | out Pairs: 69 |  |

| 0    | 0                         | В3       | D5      | NA       | -             |  |

| 1    | 0                         | E6       | B4      | √        | VREF          |  |

| 2    | 0                         | E7       | A4      | NA       | -             |  |

| 3    | 0                         | D6       | C6      | √        | VREF          |  |

| 4    | 0                         | В6       | A5      | 1        | -             |  |

| 5    | 0                         | C7       | D7      | 1        | -             |  |

| 6    | 0                         | В7       | E8      | V        | VREF          |  |

| 7    | 0                         | E9       | A7      | V        | -             |  |

| 8    | 0                         | B8       | C8      | 1        | -             |  |

| 9    | 0                         | A8       | D9      | 1        | -             |  |

| 10   | 0                         | E10      | C9      | NA       | -             |  |

| 11   | 0                         | C10      | A9      | <b>V</b> | VREF          |  |

| 12   | 0                         | B10      | F11     | 2        | -             |  |

| 13   | 1                         | D11      | B11     | NA       | IO_LVDS_DLL   |  |

| 14   | 1                         | D12      | C12     | 2        | -             |  |

| 15   | 1                         | A13      | B12     | 2        | -             |  |

| 16   | 1                         | B13      | E12     | √        | VREF          |  |

| 17   | 1                         | D13      | C13     | √        | -             |  |

*Table 23:* FG680 Differential Pin Pair Summary XCV600E, XCV1000E, XCV1600E, XCV2000E

|      |      | Р    | P N  |              | Other     |

|------|------|------|------|--------------|-----------|

| Pair | Bank | Pin  | Pin  | AO           | Functions |

| 120  | 3    | AN4  | AT1  | 4            | -         |

| 121  | 3    | AR2  | AP4  | 4            | VREF      |

| 122  | 3    | AT2  | AR3  | 6            | -         |

| 123  | 3    | AR4  | AU2  | √            | INIT      |

| 124  | 4    | AU4  | AV5  | √            | -         |

| 125  | 4    | AT6  | AV4  | 5            | -         |

| 126  | 4    | AU6  | AW4  | 5            | VREF      |

| 127  | 4    | AT7  | AW5  | √            | -         |

| 128  | 4    | AU7  | AV6  | √            | VREF      |

| 129  | 4    | AT8  | AW6  | 3            | -         |

| 130  | 4    | AU8  | AV7  | 3            | -         |

| 131  | 4    | AT9  | AW7  | √            | -         |

| 132  | 4    | AV8  | AU9  | √            | VREF      |

| 133  | 4    | AW8  | AT10 | 5            | -         |

| 134  | 4    | AV9  | AU10 | 5            | VREF      |

| 135  | 4    | AW9  | AT11 | √            | -         |

| 136  | 4    | AV10 | AU11 | √            | VREF      |

| 137  | 4    | AW10 | AU12 | 2            | -         |

| 138  | 4    | AV11 | AT13 | 2            | -         |

| 139  | 4    | AW11 | AU13 | $\checkmark$ | VREF      |

| 140  | 4    | AT14 | AV12 | √            | -         |

| 141  | 4    | AU14 | AW12 | 5            | -         |

| 142  | 4    | AT15 | AV13 | 5            | -         |

| 143  | 4    | AU15 | AW13 | √            | -         |

| 144  | 4    | AV14 | AT16 | √            | VREF      |

| 145  | 4    | AW14 | AU16 | 3            | -         |

| 146  | 4    | AV15 | AR17 | 3            | -         |

| 147  | 4    | AW15 | AT17 | √            | -         |

| 148  | 4    | AU17 | AV16 | √            | VREF      |

| 149  | 4    | AR18 | AW16 | 5            | -         |

| 150  | 4    | AT18 | AV17 | 5            | -         |

| 151  | 4    | AU18 | AW17 | √            | -         |

| 152  | 4    | AT19 | AV18 | √            | VREF      |

| 153  | 4    | AU19 | AW18 | 2            | -         |

*Table 23:* FG680 Differential Pin Pair Summary XCV600E, XCV1000E, XCV1600E, XCV2000E

|      |      | P    | N       |              | Other       |

|------|------|------|---------|--------------|-------------|

| Pair | Bank | Pin  | Pin     | AO           | Functions   |

| 154  | 4    | AU21 | AV19    | 2            | VREF        |

| 155  | 5    | AT21 | AT22 NA |              | IO_LVDS_DLL |

| 156  | 5    | AV20 | AR22 8  |              | VREF        |

| 157  | 5    | AV23 | AW21 √  |              | VREF        |

| 158  | 5    | AU23 | AV21    | √            | -           |

| 159  | 5    | AT23 | AW22    | 5            | -           |

| 160  | 5    | AR23 | AV22    | 5            | -           |

| 161  | 5    | AV24 | AW23    | <b>√</b>     | VREF        |

| 162  | 5    | AW24 | AU24    | V            | -           |

| 163  | 5    | AW25 | AT24    | 3            | -           |

| 164  | 5    | AV25 | AU25    | 3            | -           |

| 165  | 5    | AW26 | AT25    | √            | VREF        |

| 166  | 5    | AV26 | AW27    | √            | -           |

| 167  | 5    | AU26 | AV27    | 5            | -           |

| 168  | 5    | AT26 | AW28    | 5            | -           |

| 169  | 5    | AU27 | AV28    | √            | -           |

| 170  | 5    | AW29 | AT27    | √            | VREF        |

| 171  | 5    | AW30 | AU28    | 2            | -           |

| 172  | 5    | AV30 | AV29    | 2            | -           |

| 173  | 5    | AW31 | AU29    | √            | VREF        |

| 174  | 5    | AV31 | AT29    | √            | -           |

| 175  | 5    | AW32 | AU30    | 5            | VREF        |

| 176  | 5    | AW33 | AT30    | 5            | -           |

| 177  | 5    | AV33 | AU31    | $\checkmark$ | VREF        |

| 178  | 5    | AT31 | AW34    | $\checkmark$ | -           |

| 179  | 5    | AV32 | AV34    | 3            | -           |

| 180  | 5    | AU32 | AW35    | 3            | -           |

| 181  | 5    | AT32 | AV35    | $\checkmark$ | VREF        |

| 182  | 5    | AU33 | AW36    | $\checkmark$ | -           |

| 183  | 5    | AT33 | AV36    | 5            | VREF        |

| 184  | 5    | AU34 | AU36    | 5            | -           |

| 185  | 6    | AT38 | AR36    | √            | -           |

| 186  | 6    | AP36 | AR38    | 6            | -           |

| 187  | 6    | AP37 | AT39    | 4            | VREF        |

Table 26: FG900 — XCV600E, XCV1000E, XCV1600E

**Pin Description Bank** Pin# 0 IO\_L6N\_Y **A5** IO\_L6P\_Y 0 F8 IO\_L7N\_Y 0 D7 0 IO\_L7P\_Y N11 0 IO\_L8N\_YY G9 IO\_L8P\_YY 0 E8 0 IO\_VREF\_L9N\_YY A6 0 IO\_L9P\_YY J11 C7 0 IO\_L10N\_Y IO\_L10P\_Y 0 B7 0 IO\_L11N\_Y C8 0 IO L11P Y H<sub>10</sub> 0 IO\_L12N\_YY G10 0 IO\_L12P\_YY F10 0 IO\_VREF\_L13N\_YY **A8** 0 IO\_L13P\_YY H11 0 IO L14N D9<sup>4</sup> C93 IO\_L14P 0 0 IO\_L15N\_YY B9 0 IO\_L15P\_YY J12 E10<sup>4</sup> 0 IO\_L16N 0 IO\_VREF\_L16P Α9 0 IO\_L17N G11 IO\_L17P 0 B10 H12<sup>4</sup> 0 IO\_L18N\_YY 0 IO\_L18P\_YY C10<sup>4</sup> 0 IO\_L19N\_Y H13 0 IO\_L19P\_Y F11 IO\_L20N\_Y E11 0 0 IO\_L20P\_Y D11 B11<sup>4</sup> 0 IO\_L21N\_Y IO\_L21P\_Y G124 0 IO\_L22N\_YY F12 0 0 IO\_L22P\_YY C11 0 IO\_VREF\_L23N\_YY A10<sup>1</sup> 0 IO\_L23P\_YY D12 0 IO\_L24N\_Y E12

Table 26: FG900 — XCV600E, XCV1000E, XCV1600E

| Table 26 | : FG900 — XCV600E, XCV1000E, X | CV1600E            |

|----------|--------------------------------|--------------------|

| Bank     | Pin Description                | Pin #              |

| 0        | IO_L24P_Y                      | A11                |

| 0        | IO_L25N_Y                      | G13                |

| 0        | IO_L25P_Y                      | B12                |

| 0        | IO_L26N_YY                     | A12                |

| 0        | IO_L26P_YY                     | K13                |

| 0        | IO_VREF_L27N_YY                | F13                |

| 0        | IO_L27P_YY                     | B13                |

| 0        | IO_L28N_Y                      | G14                |

| 0        | IO_L28P_Y                      | E13                |

| 0        | IO_L29N_Y                      | D14                |

| 0        | IO_L29P_Y                      | B14                |

| 0        | IO_L30N_YY                     | A14                |

| 0        | IO_L30P_YY                     | J14                |

| 0        | IO_VREF_L31N_YY                | K14                |

| 0        | IO_L31P_YY                     | J15                |

| 0        | IO_L32N                        | B15 <sup>4</sup>   |

| 0        | IO_L32P                        | H15 <sup>3</sup>   |

| 0        | IO_VREF_L33N_YY                | F15 <sup>2,3</sup> |

| 0        | IO_L33P_YY                     | D15 <sup>4</sup>   |

| 0        | IO_LVDS_DLL_L34N               | A15                |

|          |                                |                    |

| 1        | GCK2                           | E15                |

| 1        | IO                             | A25 <sup>4</sup>   |

| 1        | IO                             | B17 <sup>4</sup>   |

| 1        | IO                             | B18 <sup>4</sup>   |

| 1        | IO                             | C23 <sup>4</sup>   |

| 1        | IO                             | D16 <sup>4</sup>   |

| 1        | IO                             | D17 <sup>5</sup>   |

| 1        | IO                             | D23 <sup>4</sup>   |

| 1        | Ю                              | E19 <sup>4</sup>   |

| 1        | Ю                              | E24 <sup>5</sup>   |

| 1        | Ю                              | F22 <sup>4</sup>   |

| 1        | Ю                              | G17 <sup>5</sup>   |

| 1        | Ю                              | G20 <sup>4</sup>   |

| 1        | Ю                              | J16 <sup>4</sup>   |

| 1        | Ю                              | J17 <sup>4</sup>   |

| 1        | Ю                              | J19 <sup>5</sup>   |

|          |                                |                    |

*Table 28:* FG1156 — XCV1000E, XCV1600E, XCV2000E, XCV2600E, XCV3200E

| 2 | IO_L126N_YY      |                   |

|---|------------------|-------------------|

| 0 | 10_212011_11     | T32               |

| 2 | IO_VREF_L127P_Y  | U29 <sup>1</sup>  |

| 2 | IO_L127N_Y       | U33               |

| 2 | IO_L128P_YY      | V33               |

| 2 | IO_L128N_YY      | U31               |

|   |                  |                   |

| 3 | Ю                | V27 <sup>3</sup>  |

| 3 | Ю                | V31               |

| 3 | Ю                | V32 <sup>3</sup>  |

| 3 | Ю                | W33               |

| 3 | Ю                | AB25 <sup>3</sup> |

| 3 | Ю                | AB26 <sup>3</sup> |

| 3 | Ю                | AB31 <sup>3</sup> |

| 3 | Ю                | AC31 <sup>3</sup> |

| 3 | Ю                | AF34              |

| 3 | Ю                | AG31 <sup>3</sup> |

| 3 | Ю                | AG33 <sup>3</sup> |

| 3 | Ю                | AG34              |

| 3 | Ю                | AH29 <sup>3</sup> |

| 3 | Ю                | AJ30 <sup>3</sup> |

| 3 | IO_L129P_Y       | V26               |

| 3 | IO_VREF_L129N_Y  | V30 <sup>1</sup>  |

| 3 | IO_L130P_YY      | W34               |

| 3 | IO_L130N_YY      | V28               |

| 3 | IO_L131P_YY      | W32               |

| 3 | IO_VREF_L131N_YY | W30               |

| 3 | IO_L132P_Y       | V29               |

| 3 | IO_L132N_Y       | Y34               |

| 3 | IO_L133P         | W29 <sup>5</sup>  |

| 3 | IO_L133N         | Y33 <sup>4</sup>  |

| 3 | IO_L134P_Y       | W26               |

| 3 | IO_L134N_Y       | W28               |

| 3 | IO_L135P_YY      | Y31               |

| 3 | IO_L135N_YY      | Y30               |

*Table 28:* FG1156 — XCV1000E, XCV1600E, XCV2000E, XCV2600E, XCV3200E

| Bank | Pin Description  | Pin #             |

|------|------------------|-------------------|

| 3    | IO_L136P_YY      | AA34 <sup>5</sup> |

| 3    | IO_L136N_YY      | W31 <sup>4</sup>  |

| 3    | IO_D4_L137P_YY   | AA33              |

| 3    | IO_VREF_L137N_YY | Y29               |

| 3    | IO_L138P_Y       | W25               |

| 3    | IO_L138N_Y       | AB34              |

| 3    | IO_L139P_Y       | Y28 <sup>5</sup>  |

| 3    | IO_L139N_Y       | AB33 <sup>4</sup> |

| 3    | IO_L140P_Y       | AA30              |

| 3    | IO_L140N_Y       | Y26               |

| 3    | IO_L141P_YY      | Y27               |

| 3    | IO_L141N_YY      | AA31              |

| 3    | IO_L142P_YY      | AA27 <sup>5</sup> |

| 3    | IO_L142N_YY      | AA29 <sup>4</sup> |

| 3    | IO_L143P_Y       | AB32              |

| 3    | IO_VREF_L143N_Y  | AB29              |

| 3    | IO_L144P_Y       | AA28              |

| 3    | IO_L144N_Y       | AC34              |

| 3    | IO_L145P         | Y25               |

| 3    | IO_L145N         | AD34              |

| 3    | IO_L146P_Y       | AB30              |

| 3    | IO_L146N_Y       | AC33              |

| 3    | IO_L147P_Y       | AA26              |

| 3    | IO_L147N_Y       | AC32              |

| 3    | IO_L148P_Y       | AD33              |

| 3    | IO_L148N_Y       | AB28              |

| 3    | IO_L149P_YY      | AE34              |

| 3    | IO_D5_L149N_YY   | AB27              |

| 3    | IO_D6_L150P_YY   | AE33              |

| 3    | IO_VREF_L150N_YY | AC30              |

| 3    | IO_L151P_Y       | AA25              |

| 3    | IO_L151N_Y       | AE32              |

| 3    | IO_L152P_YY      | AE31              |

| 3    | IO_L152N_YY      | AD29              |

*Table 28:* FG1156 — XCV1000E, XCV1600E, XCV2000E, XCV2600E, XCV3200E

| Bank | Pin Description | Pin # |

|------|-----------------|-------|

| NA   | GND             | R15   |

| NA   | GND             | P15   |

| NA   | GND             | L3    |

| NA   | GND             | G7    |

| NA   | GND             | E30   |

| NA   | GND             | C24   |

| NA   | GND             | B34   |

| NA   | GND             | AP32  |

| NA   | GND             | AM1   |

| NA   | GND             | AM34  |

| NA   | GND             | AJ29  |

| NA   | GND             | AF9   |

| NA   | GND             | AA17  |

| NA   | GND             | Y17   |

| NA   | GND             | W16   |

| NA   | GND             | V16   |

| NA   | GND             | U17   |

| NA   | GND             | T17   |

| NA   | GND             | R16   |

| NA   | GND             | P16   |

| NA   | GND             | L32   |

| NA   | GND             | G28   |

| NA   | GND             | D4    |

| NA   | GND             | C32   |

| NA   | GND             | A1    |

| NA   | GND             | AP33  |

| NA   | GND             | AM2   |

| NA   | GND             | AL4   |

| NA   | GND             | AH1   |

| NA   | GND             | AF26  |

| NA   | GND             | AA18  |

| NA   | GND             | Y18   |

| NA   | GND             | W17   |

| NA   | GND             | V17   |

*Table 28:* FG1156 — XCV1000E, XCV1600E, XCV2000E, XCV2600E, XCV3200E

| Bank | Pin Description | Pin # |

|------|-----------------|-------|

| NA   | GND             | U18   |

| NA   | GND             | T18   |

| NA   | GND             | R17   |

| NA   | GND             | P17   |

| NA   | GND             | J9    |

| NA   | GND             | G34   |

| NA   | GND             | D31   |

| NA   | GND             | C33   |

| NA   | GND             | A2    |

| NA   | GND             | AB17  |

| NA   | GND             | AB18  |

| NA   | GND             | N17   |

| NA   | GND             | N18   |

| NA   | GND             | U13   |

| NA   | GND             | V13   |

| NA   | GND             | U22   |

| NA   | GND             | V22   |

- V<sub>REF</sub> or I/O option only in the XCV1600E, XCV2000E, XCV2600E, and XCV3200E; otherwise, I/O option only.

- 2. V<sub>REF</sub> or I/O option only in the XCV2000E, XCV2600E, and XCV3200E; otherwise, I/O option only.

- 3. No Connect in the XCV1000E, XCV1600E.

- 4. No Connect in the XCV1000E.

- I/O in the XCV1000E.

*Table 29:* FG1156 Differential Pin Pair Summary: XCV1000E, XCV1600E, XCV2000E, XCV2600E, XCV3200E

Ρ Ν Other Bank Pin Pin AO Pair **Functions** 3200 2000 A27 G24 71 1 1000 72 1 G25 **B27** 3200 1600 3200 2600 73 1 C27 E26 2000 1600 **VREF** 1000 3200 2600 74 1 B28 J24 2000 1600 1000 75 1 H25 K24 3200 2600 76 1 F26 D27 3200 1000 77 1 C28 G26 3200 1000 78 1 J25 E27 2000 1600 3200 2600 79 H26 A30 2000 1600 **VREF** 1 1000 3200 2600 80 1 B29 G27 2000 1600 1000 3200 2600 C29 F27 81 1 1000 3200 2000 82 1 F28 E28 **VREF** 1000 3200 2000 B30 L25 83 1 1000 3200 1600 1 E29 B31 84 1000 3200 2600 1 D30 A31 2000 1600 CS 85 1000 3200 2600 D32 86 2 J27 2000 1600 DIN, D0 1000 3200 2600 87 2 E31 F30 2000 2600 2000 G29 F32 88 2 1000 3200 2600 89 2 E32 G30 **VREF** 1600 1000 2 90 M25 G31 2600 1600

*Table 29:* FG1156 Differential Pin Pair Summary: XCV1000E, XCV1600E, XCV2000E, XCV2600E, XCV3200E

|      | -    | Р   | N   | ,                              | Other     |

|------|------|-----|-----|--------------------------------|-----------|

| Pair | Bank | Pin | Pin | AO                             | Functions |

| 91   | 2    | L26 | D33 | 3200 2600<br>1600 1000         | -         |

| 92   | 2    | D34 | H29 | 2600 2000<br>1000              | VREF      |

| 93   | 2    | J28 | E33 | 3200 2600<br>2000 1600         | -         |

| 94   | 2    | H28 | H30 | 3200 2600<br>2000 1600<br>1000 | -         |

| 95   | 2    | H32 | K28 | 3200 2600<br>1600 1000         | -         |

| 96   | 2    | L27 | F33 | 3200 2600<br>2000              | -         |

| 97   | 2    | M26 | E34 | 2600 2000<br>1000              | -         |

| 98   | 2    | H31 | G32 | 3200 2600<br>2000 1600<br>1000 | VREF      |

| 99   | 2    | N25 | J31 | 2000 1600                      | -         |

| 100  | 2    | J30 | G33 | 3200 2600<br>2000 1600<br>1000 | -         |

| 101  | 2    | H34 | J29 | 2600 1000                      | VREF      |

| 102  | 2    | M27 | H33 | 3200 2600<br>1600              | -         |

| 103  | 2    | K29 | J34 | 3200 2600<br>1600 1000         | -         |

| 104  | 2    | L29 | J33 | 3200 2600<br>2000 1600<br>1000 | VREF      |

| 105  | 2    | M28 | K34 | 3200 2600<br>2000 1600<br>1000 | -         |

| 106  | 2    | N27 | L34 | 3200 1600<br>1000              | -         |

| 107  | 2    | K33 | P26 | 2000 1600<br>1000              | D1        |

| 108  | 2    | R25 | M34 | 3200 2600<br>2000              | -         |

| 109  | 2    | L31 | L33 | 2000 1000                      | -         |

| 110  | 2    | P27 | M33 | 3200 2600<br>1600 1000         | -         |