Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| 2014110                    |                                                                           |

|----------------------------|---------------------------------------------------------------------------|

| Product Status             | Active                                                                    |

| Core Processor             | AVR                                                                       |

| Core Size                  | 8/16-Bit                                                                  |

| Speed                      | 32MHz                                                                     |

| Connectivity               | I <sup>2</sup> C, IrDA, SPI, UART/USART                                   |

| Peripherals                | Brown-out Detect/Reset, DMA, POR, PWM, WDT                                |

| Number of I/O              | 50                                                                        |

| Program Memory Size        | 192KB (96K x 16)                                                          |

| Program Memory Type        | FLASH                                                                     |

| EEPROM Size                | 2K x 8                                                                    |

| RAM Size                   | 16K x 8                                                                   |

| Voltage - Supply (Vcc/Vdd) | 1.6V ~ 3.6V                                                               |

| Data Converters            | A/D 16x12b; D/A 2x12b                                                     |

| Oscillator Type            | Internal                                                                  |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                         |

| Mounting Type              | Surface Mount                                                             |

| Package / Case             | 64-VFQFN Exposed Pad                                                      |

| Supplier Device Package    | 64-QFN (9x9)                                                              |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/atxmega192a3-mh |

|                            |                                                                           |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# 7. Memories

# 7.1 Features

- Flash Program Memory

- One linear address space

- In-System Programmable

- Self-Programming and Bootloader support

- Application Section for application code

- Application Table Section for application code or data storage

- Boot Section for application code or bootloader code

- Separate lock bits and protection for all sections

- Built in fast CRC check of a selectable flash program memory section

- Data Memory

- One linear address space

- Single cycle access from CPU

- SRAM

- EEPROM

- Byte and page accessible

- Optional memory mapping for direct load and store

- I/O Memory

- Configuration and Status registers for all peripherals and modules

- 16 bit-accessible General Purpose Register for global variables or flags

- Bus arbitration

- Safe and deterministic handling of CPU and DMA Controller priority

- Separate buses for SRAM, EEPROM, I/O Memory and External Memory access Simultaneous bus access for CPU and DMA Controller

- Production Signature Row Memory for factory programmed data

- Device ID for each microcontroller device type

- Serial number for each device

- Oscillator calibration bytes

- ADC, DAC and temperature sensor calibration data

- User Signature Row

- One flash page in size Can be read and written from software Content is kept after chip erase

# 7.2 Overview

The AVR architecture has two main memory spaces, the Program Memory and the Data Memory. In addition, the XMEGA A3 features an EEPROM Memory for non-volatile data storage. All three memory spaces are linear and require no paging. The available memory size configurations are shown in "Ordering Information" on page 2. In addition each device has a Flash memory signature row for calibration data, device identification, serial number etc.

Non-volatile memory spaces can be locked for further write or read/write operations. This prevents unrestricted access to the application software.

# 15. I/O Ports

# 15.1 Features

- Selectable input and output configuration for each pin individually

- Flexible pin configuration through dedicated Pin Configuration Register

- · Synchronous and/or asynchronous input sensing with port interrupts and events

- Sense both edges

- Sense rising edges

- Sense falling edges

- Sense low level

- · Asynchronous wake-up from all input sensing configurations

- Two port interrupts with flexible pin masking

- Highly configurable output driver and pull settings:

- Totem-pole

- Pull-up/-down

- Wired-AND

- Wired-OR

- Bus-keeper

- Inverted I/O

- Configuration of multiple pins in a single operation

- Read-Modify-Write (RMW) support

- Toggle/clear/set registers for Output and Direction registers

- Clock output on port pin

- Event Channel 0 output on port pin 7

- Mapping of port registers (virtual ports) into bit accessible I/O memory space

# 15.2 Overview

The XMEGA A3 devices have flexible General Purpose I/O Ports. A port consists of up to 8 pins, ranging from pin 0 to pin 7. The ports implement several functions, including synchronous/asynchronous input sensing, pin change interrupts and configurable output settings. All functions are individual per pin, but several pins may be configured in a single operation.

# 15.3 I/O configuration

All port pins (Pn) have programmable output configuration. In addition, all port pins have an inverted I/O function. For an input, this means inverting the signal between the port pin and the pin register. For an output, this means inverting the output signal between the port register and the port pin. The inverted I/O function can be used also when the pin is used for alternate functions.

# 16. T/C - 16-bits Timer/Counter with PWM

# 16.1 Features

- Seven 16-bit Timer/Counters

- Four Timer/Counters of type 0

- Three Timer/Counters of type 1

- Four Compare or Capture (CC) Channels in Timer/Counter 0

- Two Compare or Capture (CC) Channels in Timer/Counter 1

- Double Buffered Timer Period Setting

- Double Buffered Compare or Capture Channels

- Waveform Generation:

- Single Slope Pulse Width Modulation

- Dual Slope Pulse Width Modulation

- Frequency Generation

- Input Capture:

- Input Capture with Noise Cancelling

- Frequency capture

- Pulse width capture

- 32-bit input capture

- Event Counter with Direction Control

- Timer Overflow and Timer Error Interrupts and Events

- One Compare Match or Capture Interrupt and Event per CC Channel

- Supports DMA Operation

- Hi-Resolution Extension (Hi-Res)

- Advanced Waveform Extension (AWEX)

### 16.2 Overview

XMEGA A3 has seven Timer/Counters, four Timer/Counter 0 and three Timer/Counter 1. The difference between them is that Timer/Counter 0 has four Compare/Capture channels, while Timer/Counter 1 has two Compare/Capture channels.

The Timer/Counters (T/C) are 16-bit and can count any clock, event or external input in the microcontroller. A programmable prescaler is available to get a useful T/C resolution. Updates of Timer and Compare registers are double buffered to ensure glitch free operation. Single slope PWM, dual slope PWM and frequency generation waveforms can be generated using the Compare Channels.

Through the Event System, any input pin or event in the microcontroller can be used to trigger input capture, hence no dedicated pins is required for this. The input capture has a noise canceller to avoid incorrect capture of the T/C, and can be used to do frequency and pulse width measurements.

A wide range of interrupt or event sources are available, including T/C Overflow, Compare match and Capture for each Compare/Capture channel in the T/C.

PORTC, PORTD and PORTE each has one Timer/Counter 0 and one Timer/Counter1. PORTF has one Timer/Counter 0. Notation of these are TCC0 (Time/Counter C0), TCC1, TCD0, TCD1, TCE0, TCE1 and TCF0, respectively.

# 19. RTC - Real-Time Counter

# 19.1 Features

- 16-bit Timer

- Flexible Tick resolution ranging from 1 Hz to 32.768 kHz

- One Compare register

- One Period register

- Clear timer on Overflow or Compare Match

- Overflow or Compare Match event and interrupt generation

# 19.2 Overview

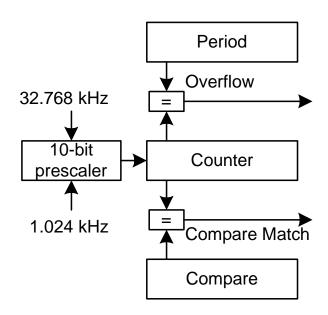

The XMEGA A3 includes a 16-bit Real-time Counter (RTC). The RTC can be clocked from an accurate 32.768 kHz Crystal Oscillator, the 32.768 kHz Calibrated Internal Oscillator, or from the 32 kHz Ultra Low Power Internal Oscillator. The RTC includes both a Period and a Compare register. For details, see Figure 19-1.

A wide range of Resolution and Time-out periods can be configured using the RTC. With a maximum resolution of  $30.5 \ \mu$ s, time-out periods range up to 2000 seconds. With a resolution of 1 second, the maximum time-out period is over 18 hours (65536 seconds).

Figure 19-1. Real-time Counter overview

Table 30-6. Port F - Alternate functions

| PORT F | PIN # | INTERRUPT  | TCF0 | USARTF0 |

|--------|-------|------------|------|---------|

| PF0    | 46    | SYNC       | OC0A |         |

| PF1    | 47    | SYNC       | OC0B | ХСКО    |

| PF2    | 48    | SYNC/ASYNC | 0000 | RXD0    |

| PF3    | 49    | SYNC       | OC0D | TXD0    |

| PF4    | 50    | SYNC       |      |         |

| PF5    | 51    | SYNC       |      |         |

| PF6    | 54    | SYNC       |      |         |

| PF7    | 55    | SYNC       |      |         |

| GND    | 52    |            |      |         |

| vcc    | 53    |            |      |         |

Table 30-7. Port R- Alternate functions

| PORT R | PIN # | INTERRUPT | PROGR     | XTAL  |

|--------|-------|-----------|-----------|-------|

| PDI    | 56    |           | PDI_DATA  |       |

| RESET  | 57    |           | PDI_CLOCK |       |

| PRO    | 58    | SYNC      |           | XTAL2 |

| PR1    | 59    | SYNC      |           | XTAL1 |

# Table 30-8. ATxmega256/192/128/64A3 Boundary Scan Order

| Bit Number | Signal Name | Module |

|------------|-------------|--------|

| 149        | PQ3.Bidir   |        |

| 148        | PQ3.Control |        |

| 147        | PQ2.Bidir   |        |

| 146        | PQ2.Control | DODT O |

| 145        | PQ1.Bidir   | PORT Q |

| 144        | PQ1.Control |        |

| 143        | PQ0.Bidir   |        |

| 142        | PQ0.Control |        |

| 141        | PK7.Bidir   |        |

| 140        | PK7.Control |        |

| 139        | PK6.Bidir   |        |

| 138        | PK6.Control |        |

| 137        | PK5.Bidir   |        |

| 136        | PK5.Control |        |

| 135        | PK4.Bidir   |        |

| 134        | PK4.Control | PORT K |

| 133        | PK3.Bidir   | PORTK  |

| 132        | PK3.Control |        |

| 131        | PK2.Bidir   |        |

| 130        | PK2.Control | ]      |

| 129        | PK1.Bidir   |        |

| 128        | PK1.Control |        |

| 127        | PK0.Bidir   | ]      |

| 126        | PK0.Control |        |

| Bit Number | Signal Name              | Module |

|------------|--------------------------|--------|

| 125        | PJ7.Bidir                |        |

| 124        | PJ7.Control              |        |

| 123        | PJ6.Bidir                |        |

| 122        | PJ6.Control              |        |

| 121        | PJ5.Bidir                |        |

| 120        | PJ5.Control              |        |

| 119        | PJ4.Bidir                |        |

| 118        | PJ4.Control              | PORT J |

| 117        | PJ3.Bidir                |        |

| 116        | PJ3.Control              |        |

| 115        | PJ2.Bidir                |        |

| 114        | PJ2.Control              |        |

| 113        | PJ1.Bidir                |        |

| 112<br>111 | PJ1.Control<br>PJ0.Bidir |        |

| 110        | PJ0.Control              |        |

| 109        | PH7.Bidir                |        |

| 108        | PH7.Control              | 1      |

| 107        | PH6.Bidir                |        |

| 106        | PH6.Control              | 1      |

| 105        | PH5.Bidir                | 1      |

| 104        | PH5.Control              | ]      |

| 103        | PH4.Bidir                | ]      |

| 102        | PH4.Control              | PORT H |

| 101        | PH3.Bidir                | FORTH  |

| 100        | PH3.Control              |        |

| 99         | PH2.Bidir                |        |

| 98         | PH2.Control              |        |

| 97         | PH1.Bidir                |        |

| 96         | PH1.Control              |        |

| 95         | PH0.Bidir                |        |

| 94<br>93   | PH0.Control              |        |

| 93         | PF7.Bidir                |        |

| 92         | PF7.Control<br>PF6.Bidir |        |

| 90         | PF6.Control              |        |

| 89         | PF5.Bidir                |        |

| 88         | PF5.Control              |        |

| 87         | PF4.Bidir                |        |

| 86         | PF4.Control              |        |

| 85         | PF3.Bidir                | PORT F |

| 84         | PF3.Control              |        |

| 83         | PF2.Bidir                |        |

| 82         | PF2.Control              |        |

| 81         | PF1.Bidir                |        |

| 80         | PF1.Control              |        |

| 79         | PF0.Bidir                |        |

| 78         | PF0.Control              |        |

| 77         | PE7.Bidir                | 4      |

| 76         | PE7.Control              | 4      |

| 75<br>74   | PE6.Bidir<br>PE6.Control | 4      |

| 73         | PE5.Bidir                | 1      |

| 72         | PE5.Control              | 1      |

| 71         | PE4.Bidir                | 1      |

| 70         | PE4.Control              |        |

| 69         | PE3.Bidir                | PORT E |

| 68         | PE3.Control              | 1      |

| 67         | PE2.Bidir                | 1      |

| 66         | PE2.Control              | 1      |

| 65         | PE1.Bidir                |        |

| 64         | PE1.Control              | ]      |

| 63         | PE0.Bidir                |        |

| 62         | PE0.Control              |        |

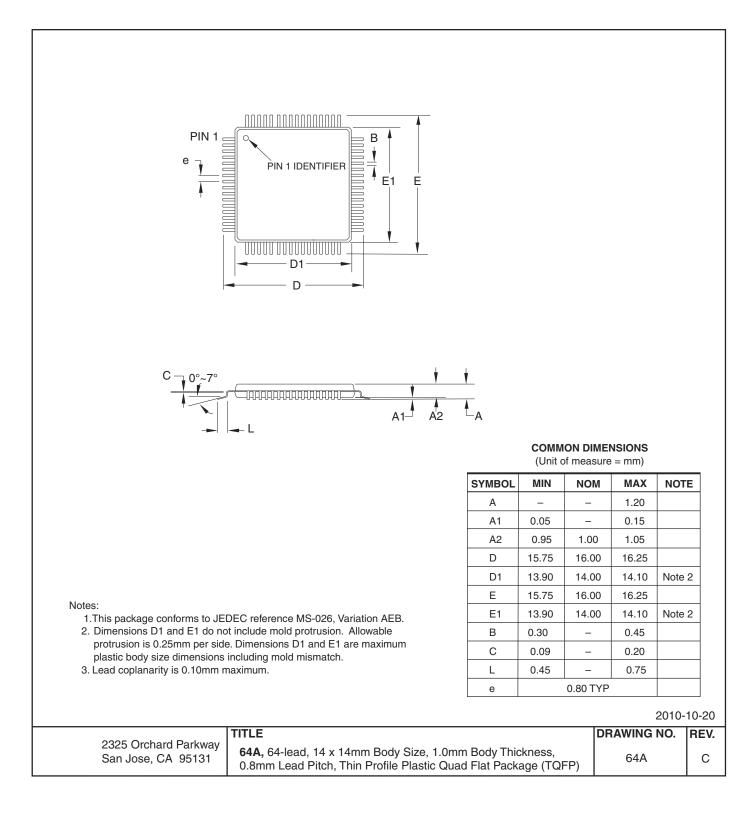

# 33. Packaging information

# 33.1 64A

# 34.11 POR Characteristics

Table 34-12. Power-on Reset Characteristics

| Symbol            | Parameter                                               | Condition                         | Min | Тур | Max  | Units |

|-------------------|---------------------------------------------------------|-----------------------------------|-----|-----|------|-------|

| V <sub>POT-</sub> | POR threshold voltage falling $V_{CC}$                  | $V_{CC}$ falls faster than 1V/ms  | 0.4 | 0.8 |      |       |

|                   |                                                         | $V_{CC}$ falls at 1V/ms or slower | 0.8 | 1.3 |      | V     |

| V <sub>POT+</sub> | POR threshold voltage rising $\mathrm{V}_{\mathrm{CC}}$ |                                   |     | 1.3 | 1.59 | V     |

# 34.12 Reset Characteristics

Table 34-13. Reset Characteristics

| Symbol | Parameter                 | Condition                    | Min | Тур                  | Max  | Units |

|--------|---------------------------|------------------------------|-----|----------------------|------|-------|

|        | Minimum reset pulse width |                              |     | 90                   | 1000 | ns    |

|        | Reset threshold voltage   | V <sub>CC</sub> = 2.7 - 3.6V |     | 0.45*V <sub>CC</sub> |      | V     |

|        |                           | V <sub>CC</sub> = 1.6 - 2.7V |     | 0.42*V <sub>CC</sub> |      | V     |

# 34.13 Oscillator Characteristics

| Table 34-14. | Internal 32.768kHz Oscillator Characteristics |

|--------------|-----------------------------------------------|

|--------------|-----------------------------------------------|

| Symbol | Parameter | Condition                                                           | Min  | Тур | Max | Units |

|--------|-----------|---------------------------------------------------------------------|------|-----|-----|-------|

|        | Accuracy  | $T = 85^{\circ}C$ , $V_{CC} = 3V$ ,<br>After production calibration | -0.5 |     | 0.5 | %     |

### Table 34-15. Internal 2MHz Oscillator Characteristics

| Symbol | Parameter                  | Condition                                                           | Min  | Тур  | Max | Units |

|--------|----------------------------|---------------------------------------------------------------------|------|------|-----|-------|

|        | Accuracy                   | $T = 85^{\circ}C$ , $V_{CC} = 3V$ ,<br>After production calibration | -1.5 |      | 1.5 | %     |

|        | DFLL Calibration step size | $T = 25^{\circ}C, V_{CC} = 3V$                                      |      | 0.15 |     |       |

Table 34-16. Internal 32MHz Oscillator Characteristics

| Symbol | Parameter                 | Condition                                                           | Min  | Тур | Max | Units |

|--------|---------------------------|---------------------------------------------------------------------|------|-----|-----|-------|

|        | Accuracy                  | $T = 85^{\circ}C$ , $V_{CC} = 3V$ ,<br>After production calibration | -1.5 |     | 1.5 | %     |

|        | DFLL Calibration stepsize | $T = 25^{\circ}C, V_{CC} = 3V$                                      |      | 0.2 |     |       |

#### Table 34-17. Internal 32kHz, ULP Oscillator Characteristics

| Symbol | Parameter                      | Condition                        | Min | Тур | Max | Units |

|--------|--------------------------------|----------------------------------|-----|-----|-----|-------|

|        | Output frequency 32kHz ULP OSC | $T = 85^{\circ}C, V_{CC} = 3.0V$ |     | 26  |     | kHz   |

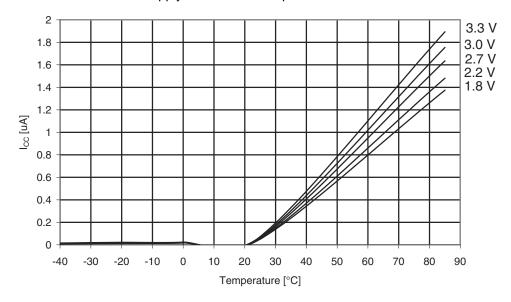

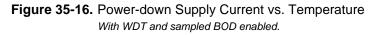

# 35.3 Power-down Supply Current

Figure 35-15. Power-down Supply Current vs. Temperature

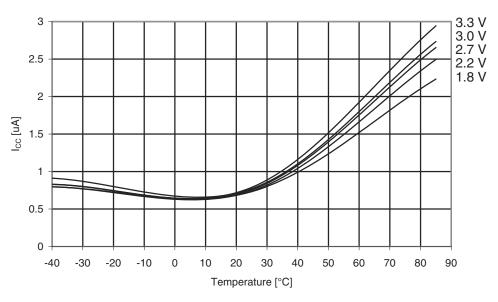

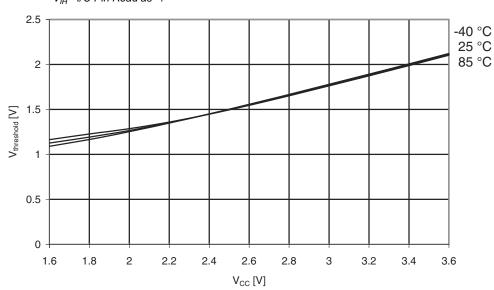

# 35.7 Pin Thresholds and Hysteresis

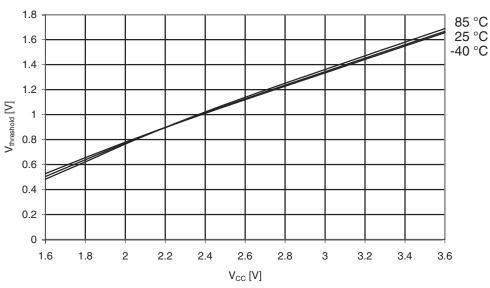

Figure 35-27. I/O Pin Input Threshold Voltage vs.  $V_{CC}$  $V_{IH}$  - I/O Pin Read as "1"

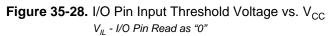

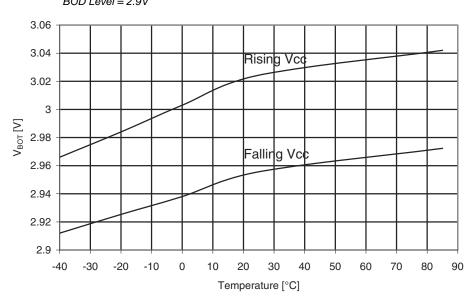

#### Figure 35-33. BOD Thresholds vs. Temperature BOD Level = 2.9V

# 35.9 Oscillators and Wake-up Time

### 35.9.1 Internal 32.768 kHz Oscillator

# 35.10 Module current consumption

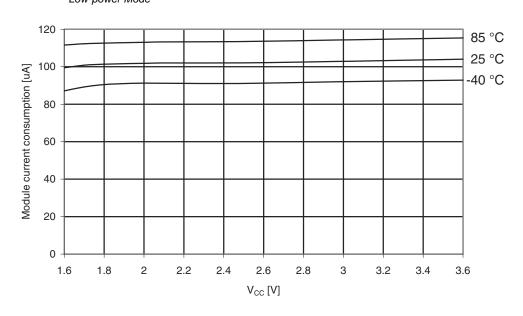

Figure 35-39. AC current consumption vs. Vcc Low-power Mode

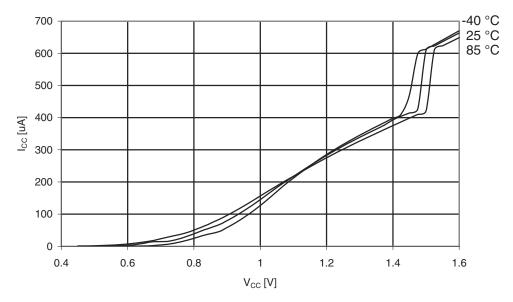

Figure 35-40. Power-up current consumption vs. Vcc

#### 16. Pending full asynchronous pin change interrupts will not wake the device

Any full asynchronous pin-change Interrupt from pin 2, on any port, that is pending when the sleep instruction is executed, will be ignored until the device is woken from another source or the source triggers again. This applies when entering all sleep modes where the System Clock is stopped.

#### Problem fix/Workaround

None.

#### 17. Pin configuration does not affect Analog Comparator output

The Output/Pull and inverted pin configuration does not affect the Analog Comparator output.

#### Problem fix/Workaround

None for Output/Pull configuration.

For inverted I/O, configure the Analog Comparator to give an inverted result (i.e. connect positive input to the negative AC input and vice versa), or use and external inverter to change polarity of Analog Comparator output.

#### 18. NMI Flag for Crystal Oscillator Failure automatically cleared

NMI flag for Crystal Oscillator Failure (XOSCFDIF) will be automatically cleared when executing the NMI interrupt handler.

#### Problem fix/Workaround

This device revision has only one NMI interrupt source, so checking the interrupt source in software is not required.

#### 19. Crystal start-up time required after power-save even if crystal is source for RTC

Even if 32.768 kHz crystal is used for RTC during sleep, the clock from the crystal will not be ready for the system before the specified start-up time. See "XOSCSEL[3:0]: Crystal Oscillator Selection" in XMEGA A Manual. If BOD is used in active mode, the BOD will be on during this period (0.5s).

#### Problem fix/Workaround

If faster start-up is required, go to sleep with internal oscillator as system clock.

#### 20. RTC Counter value not correctly read after sleep

If the RTC is set to wake up the device on RTC Overflow and bit 0 of RTC CNT is identical to bit 0 of RTC PER as the device is entering sleep, the value in the RTC count register can not be read correctly within the first prescaled RTC clock cycle after wakeup. The value read will be the same as the value in the register when entering sleep.

The same applies if RTC Compare Match is used as wake-up source.

#### Problem fix/Workaround

Wait at least one prescaled RTC clock cycle before reading the RTC CNT value.

#### 21. Pending asynchronous RTC-interrupts will not wake up device

Asynchronous Interrupts from the Real-Time-Counter that is pending when the sleep instruction is executed, will be ignored until the device is woken from another source or the source triggers again.

#### Problem fix/Workaround

None.

#### Problem fix/Workaround

Keep the amplified voltage output from the ADC gain stage below 2.4 V in order to get a correct result, or keep ADC voltage reference below 2.4 V.

#### 5. ADC Event on compare match non-functional

ADC signalling event will be given at every conversion complete even if Interrupt mode (INT-MODE) is set to BELOW or ABOVE.

#### Problem fix/Workaround

Enable and use interrupt on compare match when using the compare function.

6. Bandgap measurement with the ADC is non-functional when VCC is below 2.7V The ADC can not be used to do bandgap measurements when VCC is below 2.7V.

Problem fix/Workaround

None.

7. Accuracy lost on first three samples after switching input to ADC gain stage

Due to memory effect in the ADC gain stage, the first three samples after changing input channel must be disregarded to achieve 12-bit accuracy.

#### Problem fix/Workaround

Run three ADC conversions and discard these results after changing input channels to ADC gain stage.

#### 8. Configuration of PGM and CWCM not as described in XMEGA A Manual

Enabling Common Waveform Channel Mode will enable Pattern generation mode (PGM), but not Common Waveform Channel Mode.

Enabling Pattern Generation Mode (PGM) and not Common Waveform Channel Mode (CWCM) will enable both Pattern Generation Mode and Common Waveform Channel Mode.

#### Problem fix/Workaround

Table 36-2.

Configure PWM and CWCM according to this table:

| PGM | CWCM | Description           |

|-----|------|-----------------------|

| 0   | 0    | PGM and CWCM disabled |

| 0   | 1    | PGM enabled           |

| 1   | 0    | PGM and CWCM enabled  |

| 1   | 1    | PGM enabled           |

#### 9. PWM is not restarted properly after a fault in cycle-by-cycle mode

When the AWeX fault restore mode is set to cycle-by-cycle, the waveform output will not return to normal operation at first update after fault condition is no longer present.

#### Problem fix/Workaround

Do a write to any AWeX I/O register to re-enable the output.

#### 10. BOD will be enabled after any reset

If any reset source goes active, the BOD will be enabled and keep the device in reset if the VCC voltage is below the programmed BOD level. During Power-On Reset, reset will not be released until VCC is above the programmed BOD level even if the BOD is disabled.

#### Problem fix/Workaround

None.

#### 26. TWI Data Interrupt Flag erroneously read as set

When issuing the TWI slave response command CMD=0b11, it takes 1 Peripheral Clock cycle to clear the data interrupt flag (DIF). A read of DIF directly after issuing the command will show the DIF still set.

### Problem fix/Workaround

Add one NOP instruction before checking DIF.

### 27. WDR instruction inside closed window will not issue reset

When a WDR instruction is execute within one ULP clock cycle after updating the window control register, the counter can be cleared without giving a system reset.

### Problem fix/Workaround

Wait at least one ULP clock cycle before executing a WDR instruction.

#### 16. Pending full asynchronous pin change interrupts will not wake the device

Any full asynchronous pin-change Interrupt from pin 2, on any port, that is pending when the sleep instruction is executed, will be ignored until the device is woken from another source or the source triggers again. This applies when entering all sleep modes where the System Clock is stopped.

#### Problem fix/Workaround

None.

#### 17. Pin configuration does not affect Analog Comparator output

The Output/Pull and inverted pin configuration does not affect the Analog Comparator output.

#### Problem fix/Workaround

None for Output/Pull configuration.

For inverted I/O, configure the Analog Comparator to give an inverted result (i.e. connect positive input to the negative AC input and vice versa), or use and external inverter to change polarity of Analog Comparator output.

#### 18. NMI Flag for Crystal Oscillator Failure automatically cleared

NMI flag for Crystal Oscillator Failure (XOSCFDIF) will be automatically cleared when executing the NMI interrupt handler.

#### Problem fix/Workaround

This device revision has only one NMI interrupt source, so checking the interrupt source in software is not required.

#### 19. Crystal start-up time required after power-save even if crystal is source for RTC

Even if 32.768 kHz crystal is used for RTC during sleep, the clock from the crystal will not be ready for the system before the specified start-up time. See "XOSCSEL[3:0]: Crystal Oscillator Selection" in XMEGA A Manual. If BOD is used in active mode, the BOD will be on during this period (0.5s).

#### Problem fix/Workaround

If faster start-up is required, go to sleep with internal oscillator as system clock.

#### 20. RTC Counter value not correctly read after sleep

If the RTC is set to wake up the device on RTC Overflow and bit 0 of RTC CNT is identical to bit 0 of RTC PER as the device is entering sleep, the value in the RTC count register can not be read correctly within the first prescaled RTC clock cycle after wakeup. The value read will be the same as the value in the register when entering sleep.

The same applies if RTC Compare Match is used as wake-up source.

#### Problem fix/Workaround

Wait at least one prescaled RTC clock cycle before reading the RTC CNT value.

#### 21. Pending asynchronous RTC-interrupts will not wake up device

Asynchronous Interrupts from the Real-Time-Counter that is pending when the sleep instruction is executed, will be ignored until the device is woken from another source or the source triggers again.

#### Problem fix/Workaround

None.

#### Problem fix/Workaround

None.

#### 26. TWI Data Interrupt Flag erroneously read as set

When issuing the TWI slave response command CMD=0b11, it takes 1 Peripheral Clock cycle to clear the data interrupt flag (DIF). A read of DIF directly after issuing the command will show the DIF still set.

#### Problem fix/Workaround

Add one NOP instruction before checking DIF.

#### 27. WDR instruction inside closed window will not issue reset

When a WDR instruction is execute within one ULP clock cycle after updating the window control register, the counter can be cleared without giving a system reset.

#### Problem fix/Workaround

Wait at least one ULP clock cycle before executing a WDR instruction.

36.2.3 rev. A

Not sampled.

# 37. Datasheet Revision History

Please note that the referring page numbers in this section are referred to this document. The referring revision in this section are referring to the document revision.

# 37.1 8068U - 06/13

1. Not recommended for new designs - Use XMEGA A3U series.

### 37.2 8068T - 12/10

- 1. Datasheet status changed to complete: Preliminary removed from the front page.

- 2. Updated all tables in the "Electrical Characteristics" .

- 3. Updated "Packaging information" on page 61.

- 4. Replaced Table 34-11 on page 69

- 5. Replaced Table 34-18 on page 71 and added the figure "TOSC input capacitance" on page 71

- 6. Added ERRATA "rev. E" .

- 7. Added ERRATA "rev. B" .

- 8. Updated ERRATA for ADC (ADC has increased INL error for some operating conditions).

- 9. Updated the last page by Atmel new Brand Style Guide.

### 37.3 8068S - 09/10

10. Updated "Errata" on page 93.

### 37.4 8068R - 08/10

- 1. Updated the Footnote 3 of "Ordering Information" on page 2.

- 2. Updated Footnote 2 of Figure 2-1 on page 3.

- 3. Updated "Data Memory Map (Hexadecimal address)" on page 11. 192A3 has 2 KB EEPROM.

- 4. Updated "Features" on page 27. Event Channel 0 output on port pin 7.

- 5. Updated "Absolute Maximum Ratings\*" on page 63 by adding Icc for Flash/EEPROM Programming.

- 6. Added AVCC in "ADC Characteristics" on page 67.

- 7. Updated Start up time in "ADC Characteristics" on page 67.

# **Table of Contents**

|   | Features                                                                                                                                                                                                                                                                                                                                                | 1                                                                           |

|---|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------|

|   | Typical Applications                                                                                                                                                                                                                                                                                                                                    | 1                                                                           |

| 1 | Ordering Information                                                                                                                                                                                                                                                                                                                                    | 2                                                                           |

| 2 | Pinout/Block Diagram                                                                                                                                                                                                                                                                                                                                    | 3                                                                           |

| 3 | Overview                                                                                                                                                                                                                                                                                                                                                | 4                                                                           |

|   | 3.1Block Diagram                                                                                                                                                                                                                                                                                                                                        | 5                                                                           |

| 4 | Resources                                                                                                                                                                                                                                                                                                                                               | 6                                                                           |

|   | 4.1Recommended reading                                                                                                                                                                                                                                                                                                                                  | 6                                                                           |

| 5 | Disclaimer                                                                                                                                                                                                                                                                                                                                              | 6                                                                           |

| 6 | AVR CPU                                                                                                                                                                                                                                                                                                                                                 | 7                                                                           |

|   | 6.1Features                                                                                                                                                                                                                                                                                                                                             | 7                                                                           |

|   | 6.20verview                                                                                                                                                                                                                                                                                                                                             | 7                                                                           |

|   | 6.3Register File                                                                                                                                                                                                                                                                                                                                        | 8                                                                           |

|   | 6.4ALU - Arithmetic Logic Unit                                                                                                                                                                                                                                                                                                                          | 8                                                                           |

|   | 6.5Program Flow                                                                                                                                                                                                                                                                                                                                         | 8                                                                           |

|   |                                                                                                                                                                                                                                                                                                                                                         |                                                                             |

| 7 | Memories                                                                                                                                                                                                                                                                                                                                                | 9                                                                           |

| 7 | <i>Memories</i>                                                                                                                                                                                                                                                                                                                                         |                                                                             |

| 7 |                                                                                                                                                                                                                                                                                                                                                         | 9                                                                           |

| 7 | 7.1Features<br>7.2Overview<br>7.3In-System Programmable Flash Program Memory                                                                                                                                                                                                                                                                            | 9<br>9<br>10                                                                |

| 7 | 7.1Features<br>7.2Overview<br>7.3In-System Programmable Flash Program Memory<br>7.4Data Memory                                                                                                                                                                                                                                                          | 9<br>9<br>10<br>11                                                          |

| 7 | <ul> <li>7.1Features</li> <li>7.2Overview</li> <li>7.3In-System Programmable Flash Program Memory</li> <li>7.4Data Memory</li> <li>7.5Production Signature Row</li> </ul>                                                                                                                                                                               | 9<br>9<br>10<br>11<br>13                                                    |

| 7 | <ul> <li>7.1Features</li> <li>7.2Overview</li> <li>7.3In-System Programmable Flash Program Memory</li> <li>7.4Data Memory</li> <li>7.5Production Signature Row</li> <li>7.6User Signature Row</li> </ul>                                                                                                                                                | 9<br>10<br>11<br>13<br>13                                                   |

|   | <ul> <li>7.1Features</li> <li>7.2Overview</li> <li>7.3In-System Programmable Flash Program Memory</li> <li>7.4Data Memory</li> <li>7.5Production Signature Row</li> <li>7.6User Signature Row</li> <li>7.7Flash and EEPROM Page Size</li> </ul>                                                                                                         | 9<br>10<br>11<br>13<br>13<br>14                                             |

| 8 | 7.1Features         7.2Overview         7.3In-System Programmable Flash Program Memory         7.4Data Memory         7.5Production Signature Row         7.6User Signature Row         7.7Flash and EEPROM Page Size         DMAC - Direct Memory Access Controller                                                                                    | 9<br>10<br>11<br>13<br>13<br>14<br><b>15</b>                                |

|   | 7.1Features         7.2Overview         7.3In-System Programmable Flash Program Memory         7.4Data Memory         7.5Production Signature Row         7.6User Signature Row         7.7Flash and EEPROM Page Size <b>DMAC - Direct Memory Access Controller</b> 8.1Features                                                                         | 9<br>10<br>11<br>13<br>13<br>14<br>14<br>15                                 |

| 8 | 7.1Features         7.2Overview         7.3In-System Programmable Flash Program Memory         7.4Data Memory         7.4Data Memory         7.5Production Signature Row         7.6User Signature Row         7.7Flash and EEPROM Page Size         DMAC - Direct Memory Access Controller         8.1Features         8.2Overview                     | 9<br>10<br>11<br>13<br>13<br>14<br><b>15</b><br>15                          |

|   | 7.1Features         7.2Overview         7.3In-System Programmable Flash Program Memory         7.4Data Memory         7.4Data Memory         7.5Production Signature Row         7.6User Signature Row         7.7Flash and EEPROM Page Size         DMAC - Direct Memory Access Controller         8.1Features         8.2Overview                     | 9<br>10<br>11<br>13<br>13<br>14<br><b>15</b><br>15<br><b>16</b>             |

| 8 | 7.1Features         7.2Overview         7.3In-System Programmable Flash Program Memory         7.4Data Memory         7.4Data Memory         7.5Production Signature Row         7.6User Signature Row         7.7Flash and EEPROM Page Size         DMAC - Direct Memory Access Controller         8.1Features         8.2Overview         9.1Features | 9<br>10<br>11<br>13<br>13<br>14<br><b>15</b><br>15<br><b>16</b><br>16       |

| 8 | 7.1Features         7.2Overview         7.3In-System Programmable Flash Program Memory         7.4Data Memory         7.4Data Memory         7.5Production Signature Row         7.6User Signature Row         7.7Flash and EEPROM Page Size         DMAC - Direct Memory Access Controller         8.1Features         8.2Overview                     | 9<br>10<br>11<br>13<br>13<br>14<br><b>15</b><br>15<br><b>16</b><br>16       |

| 8 | 7.1Features         7.2Overview         7.3In-System Programmable Flash Program Memory         7.4Data Memory         7.4Data Memory         7.5Production Signature Row         7.6User Signature Row         7.7Flash and EEPROM Page Size         DMAC - Direct Memory Access Controller         8.1Features         8.2Overview         9.1Features | 9<br>10<br>11<br>13<br>13<br>13<br>14<br><b>15</b><br>15<br><b>16</b><br>16 |

# XMEGA A3

|    | 10.20verview                                         | 18 |

|----|------------------------------------------------------|----|

|    | 10.3Clock Options                                    | 19 |

| 11 | Power Management and Sleep Modes                     | 21 |

|    | 11.1Features                                         | 21 |

|    | 11.2Overview                                         | 21 |

|    | 11.3Sleep Modes                                      | 21 |

| 12 | System Control and Reset                             | 23 |

|    | 12.1Features                                         | 23 |

|    | 12.2Resetting the AVR                                | 23 |

|    | 12.3Reset Sources                                    | 23 |

| 13 | WDT - Watchdog Timer                                 | 24 |

|    | 13.1Features                                         | 24 |

|    | 13.20verview                                         | 24 |

| 14 | PMIC - Programmable Multi-level Interrupt Controller | 25 |

|    | 14.1Features                                         | 25 |

|    | 14.20verview                                         | 25 |

|    | 14.3Interrupt vectors                                | 25 |

| 15 | I/O Ports                                            | 27 |

|    | 15.1Features                                         | 27 |

|    | 15.20verview                                         | 27 |

|    | 15.3I/O configuration                                | 27 |

|    | 15.4Input sensing                                    | 30 |

|    | 15.5Port Interrupt                                   |    |

|    | 15.6Alternate Port Functions                         | 30 |

| 16 | T/C - 16-bits Timer/Counter with PWM                 | 31 |

|    | 16.1Features                                         | 31 |

|    | 16.20verview                                         | 31 |

| 17 | AWEX - Advanced Waveform Extension                   | 33 |

|    | 17.1Features                                         | 33 |

|    | 17.20verview                                         | 33 |

| 18 | Hi-Res - High Resolution Extension                   | 34 |

|    | 18.1Features                                         | 34 |

|    | 18.20verview                                         | 34 |