Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Details                    |                                                                            |

|----------------------------|----------------------------------------------------------------------------|

| Product Status             | Active                                                                     |

| Core Processor             | AVR                                                                        |

| Core Size                  | 8/16-Bit                                                                   |

| Speed                      | 32MHz                                                                      |

| Connectivity               | I <sup>2</sup> C, IrDA, SPI, UART/USART                                    |

| Peripherals                | Brown-out Detect/Reset, DMA, POR, PWM, WDT                                 |

| Number of I/O              | 50                                                                         |

| Program Memory Size        | 256KB (128K x 16)                                                          |

| Program Memory Type        | FLASH                                                                      |

| EEPROM Size                | 4K x 8                                                                     |

| RAM Size                   | 16K x 8                                                                    |

| Voltage - Supply (Vcc/Vdd) | 1.6V ~ 3.6V                                                                |

| Data Converters            | A/D 16x12b; D/A 2x12b                                                      |

| Oscillator Type            | Internal                                                                   |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                          |

| Mounting Type              | Surface Mount                                                              |

| Package / Case             | 64-TQFP                                                                    |

| Supplier Device Package    | 64-TQFP (14x14)                                                            |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/atxmega256a3-aur |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

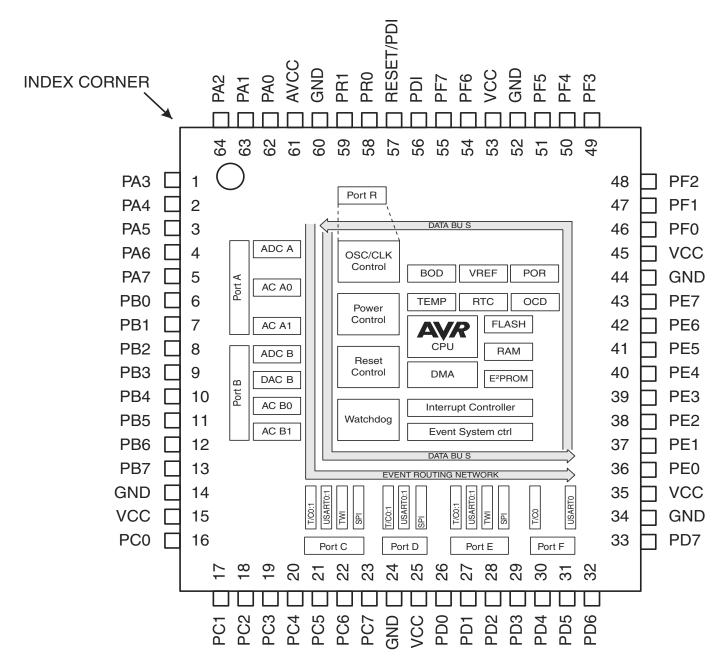

# 2. Pinout/Block Diagram

Figure 2-1. Block diagram and pinout.

- Notes: 1. For full details on pinout and alternate pin functions refer to "Pinout and Pin Functions" on page 49. 2. The large center pad underneath the QFN/MLF package should be soldered to ground on the board to ensure good

- The large center pad underneath the QFN/MLF package should be soldered to ground on the board to ensure go mechanical stability.

# 4. Resources

A comprehensive set of development tools, application notes and datasheets are available for download on http://www.atmel.com/avr.

# 4.1 Recommended reading

- XMEGA Manual

- XMEGA Application Notes

This device data sheet only contains part specific information and a short description of each peripheral and module. The XMEGA Manual describes the modules and peripherals in depth. The XMEGA application notes contain example code and show applied use of the modules and peripherals.

The XMEGA Manual and Application Notes are available from http://www.atmel.com/avr.

# 5. Disclaimer

For devices that are not available yet, typical values contained in this datasheet are based on simulations and characterization of other AVR XMEGA microcontrollers manufactured on the same process technology. Min. and Max values will be available after the device is characterized.

# **11. Power Management and Sleep Modes**

# 11.1 Features

- 5 sleep modes

- Idle

- Power-down

- Power-save

- Standby

- Extended standby

- Power Reduction registers to disable clocks to unused peripherals

# 11.2 Overview

The XMEGA A3 provides various sleep modes tailored to reduce power consumption to a minimum. All sleep modes are available and can be entered from Active mode. In Active mode the CPU is executing application code. The application code decides when and which sleep mode to enter. Interrupts from enabled peripherals and all enabled reset sources can restore the microcontroller from sleep to Active mode.

In addition, Power Reduction registers provide a method to stop the clock to individual peripherals from software. When this is done, the current state of the peripheral is frozen and there is no power consumption from that peripheral. This reduces the power consumption in Active mode and Idle sleep mode.

# 11.3 Sleep Modes

#### 11.3.1 Idle Mode

In Idle mode the CPU and Non-Volatile Memory are stopped, but all peripherals including the Interrupt Controller, Event System and DMA Controller are kept running. Interrupt requests from all enabled interrupts will wake the device.

#### 11.3.2 Power-down Mode

In Power-down mode all system clock sources, and the asynchronous Real Time Counter (RTC) clock source, are stopped. This allows operation of asynchronous modules only. The only interrupts that can wake up the MCU are the Two Wire Interface address match interrupts, and asynchronous port interrupts, e.g pin change.

#### 11.3.3 Power-save Mode

Power-save mode is identical to Power-down, with one exception: If the RTC is enabled, it will keep running during sleep and the device can also wake up from RTC interrupts.

#### 11.3.4 Standby Mode

Standby mode is identical to Power-down with the exception that all enabled system clock sources are kept running, while the CPU, Peripheral and RTC clocks are stopped. This reduces the wake-up time when external crystals or resonators are used.

# 14. PMIC - Programmable Multi-level Interrupt Controller

# 14.1 Features

- Separate interrupt vector for each interrupt

- Short, predictable interrupt response time

- Programmable Multi-level Interrupt Controller

- 3 programmable interrupt levels

- Selectable priority scheme within low level interrupts (round-robin or fixed)

- Non-Maskable Interrupts (NMI)

- Interrupt vectors can be moved to the start of the Boot Section

# 14.2 Overview

XMEGA A3 has a Programmable Multi-level Interrupt Controller (PMIC). All peripherals can define three different priority levels for interrupts; high, medium or low. Medium level interrupts may interrupt low level interrupt service routines. High level interrupts may interrupt both lowand medium level interrupt service routines. Low level interrupts have an optional round robin scheme to make sure all interrupts are serviced within a certain amount of time.

The built in oscillator failure detection mechanism can issue a Non-Maskable Interrupt (NMI).

# 14.3 Interrupt vectors

When an interrupt is serviced, the program counter will jump to the interrupt vector address. The interrupt vector is the sum of the peripheral's base interrupt address and the offset address for specific interrupts in each peripheral. The base addresses for the XMEGA A3 devices are shown in Table 14-1. Offset addresses for each interrupt available in the peripheral are described for each peripheral in the XMEGA A manual. For peripherals or modules that have only one interrupt, the interrupt vector is shown in Table 14-1. The program address is the word address.

| Program Address<br>(Base Address) | Source           | Interrupt Description                             |

|-----------------------------------|------------------|---------------------------------------------------|

| 0x000                             | RESET            |                                                   |

| 0x002                             | OSCF_INT_vect    | Crystal Oscillator Failure Interrupt vector (NMI) |

| 0x004                             | PORTC_INT_base   | Port C Interrupt base                             |

| 0x008                             | PORTR_INT_base   | Port R Interrupt base                             |

| 0x00C                             | DMA_INT_base     | DMA Controller Interrupt base                     |

| 0x014                             | RTC_INT_base     | Real Time Counter Interrupt base                  |

| 0x018                             | TWIC_INT_base    | Two-Wire Interface on Port C Interrupt base       |

| 0x01C                             | TCC0_INT_base    | Timer/Counter 0 on port C Interrupt base          |

| 0x028                             | TCC1_INT_base    | Timer/Counter 1 on port C Interrupt base          |

| 0x030                             | SPIC_INT_vect    | SPI on port C Interrupt vector                    |

| 0x032                             | USARTC0_INT_base | USART 0 on port C Interrupt base                  |

| 0x03D                             | USARTC1_INT_base | USART 1 on port C Interrupt base                  |

| 0x03E                             | AES_INT_vect     | AES Interrupt vector                              |

Table 14-1. Reset and Interrupt Vectors

# 16. T/C - 16-bits Timer/Counter with PWM

# 16.1 Features

- Seven 16-bit Timer/Counters

- Four Timer/Counters of type 0

- Three Timer/Counters of type 1

- Four Compare or Capture (CC) Channels in Timer/Counter 0

- Two Compare or Capture (CC) Channels in Timer/Counter 1

- Double Buffered Timer Period Setting

- Double Buffered Compare or Capture Channels

- Waveform Generation:

- Single Slope Pulse Width Modulation

- Dual Slope Pulse Width Modulation

- Frequency Generation

- Input Capture:

- Input Capture with Noise Cancelling

- Frequency capture

- Pulse width capture

- 32-bit input capture

- Event Counter with Direction Control

- Timer Overflow and Timer Error Interrupts and Events

- One Compare Match or Capture Interrupt and Event per CC Channel

- Supports DMA Operation

- Hi-Resolution Extension (Hi-Res)

- Advanced Waveform Extension (AWEX)

# 16.2 Overview

XMEGA A3 has seven Timer/Counters, four Timer/Counter 0 and three Timer/Counter 1. The difference between them is that Timer/Counter 0 has four Compare/Capture channels, while Timer/Counter 1 has two Compare/Capture channels.

The Timer/Counters (T/C) are 16-bit and can count any clock, event or external input in the microcontroller. A programmable prescaler is available to get a useful T/C resolution. Updates of Timer and Compare registers are double buffered to ensure glitch free operation. Single slope PWM, dual slope PWM and frequency generation waveforms can be generated using the Compare Channels.

Through the Event System, any input pin or event in the microcontroller can be used to trigger input capture, hence no dedicated pins is required for this. The input capture has a noise canceller to avoid incorrect capture of the T/C, and can be used to do frequency and pulse width measurements.

A wide range of interrupt or event sources are available, including T/C Overflow, Compare match and Capture for each Compare/Capture channel in the T/C.

PORTC, PORTD and PORTE each has one Timer/Counter 0 and one Timer/Counter1. PORTF has one Timer/Counter 0. Notation of these are TCC0 (Time/Counter C0), TCC1, TCD0, TCD1, TCE0, TCE1 and TCF0, respectively.

# 26. DAC - 12-bit Digital to Analog Converter

# 26.1 Features

- One DAC with 12-bit resolution

- Up to 1 Msps conversion rate for each DAC

- Flexible conversion range

- Multiple trigger sources

- 1 continuous output or 2 Sample and Hold (S/H) outputs for each DAC

- Built-in offset and gain calibration

- High drive capabilities

- Low Power Mode

# 26.2 Overview

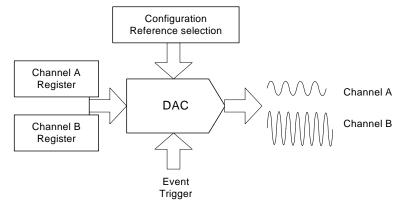

The XMEGA A3 features one two-channel, 12-bit, 1 Msps DACs with built-in offset and gain calibration, see Figure 26-1 on page 43.

A DAC converts a digital value into an analog signal. The DAC may use an internal 1.0 voltage as the upper limit for conversion, but it is also possible to use the supply voltage or any applied voltage in-between. The external reference input is shared with the ADC reference input.

#### Figure 26-1. DAC overview

The DAC has one continuous output with high drive capabilities for both resistive and capacitive loads. It is also possible to split the continuous time channel into two Sample and Hold (S/H) channels, each with separate data conversion registers.

A DAC conversion may be started from the application software by writing the data conversion registers. The DAC can also be configured to do conversions triggered by the Event System to have regular timing, independent of the application software. DMA may be used for transferring data from memory locations to DAC data registers.

The DAC has a built-in calibration system to reduce offset and gain error when loading with a calibration value from software.

PORTB each has one DAC. Notation of this peripheral is DACB.

# 27. AC - Analog Comparator

# 27.1 Features

- Four Analog Comparators

- Selectable Power vs. Speed

- Selectable hysteresis

- 0, 20 mV, 50 mV

- Analog Comparator output available on pin

- Flexible Input Selection

- All pins on the port

- Output from the DAC

- Bandgap reference voltage.

- Voltage scaler that can perform a 64-level scaling of the internal VCC voltage.

- Interrupt and event generation on

- Rising edge

- Falling edge

- Toggle

- Window function interrupt and event generation on

- Signal above window

- Signal inside window

- Signal below window

# 27.2 Overview

XMEGA A3 features four Analog Comparators (AC). An Analog Comparator compares two voltages, and the output indicates which input is largest. The Analog Comparator may be configured to give interrupt requests and/or events upon several different combinations of input change.

Both hysteresis and propagation delays may be adjusted in order to find the optimal operation for each application.

A wide range of input selection is available, both external pins and several internal signals can be used.

The Analog Comparators are always grouped in pairs (AC0 and AC1) on each analog port. They have identical behavior but separate control registers.

Optionally, the state of the comparator is directly available on a pin.

PORTA and PORTB each has one AC pair. Notations are ACA and ACB, respectively.

# 29. Program and Debug Interfaces

# 29.1 Features

- PDI Program and Debug Interface (Atmel proprietary 2-pin interface)

- JTAG Interface (IEEE std. 1149.1 compliant)

- Boundary-scan capabilities according to the IEEE Std. 1149.1 (JTAG)

- Access to the OCD system

- Programming of Flash, EEPROM, Fuses and Lock Bits

## 29.2 Overview

The programming and debug facilities are accessed through the JTAG and PDI physical interfaces. The PDI physical interface uses one dedicated pin together with the Reset pin, and no general purpose pins are used. JTAG uses four general purpose pins on PORTB.

The PDI is an Atmel proprietary protocol for communication between the microcontroller and Atmel's or third party development tools.

## 29.3 IEEE 1149.1 (JTAG) Boundary-scan

The JTAG physical layer handles the basic low-level serial communication over four I/O lines named TMS, TCK, TDI, and TDO. It complies to the IEEE Std. 1149.1 for test access port and boundary scan.

#### 29.3.1 Boundary-scan Order

Table 30-8 on page 53 shows the Scan order between TDI and TDO when the Boundary-scan chain is selected as data path. Bit 0 is the LSB; the first bit scanned in, and the first bit scanned out. The scan order follows the pin-out order. Bit 4, 5, 6 and 7 of Port B is not in the scan chain, since these pins constitute the TAP pins when the JTAG is enabled.

#### 29.3.2 Boundary-scan Description Language Files

Boundary-scan Description Language (BSDL) files describe Boundary-scan capable devices in a standard format used by automated test-generation software. The order and function of bits in the Boundary-scan Data Register are included in this description. BSDL files are available for ATxmega256/192/128/64A3 devices.

See Table 30-8 on page 53 for ATxmega256/192/128/64A3 Boundary Scan Order.

Table 30-6. Port F - Alternate functions

| PORT F | PIN # | INTERRUPT  | TCF0 | USARTF0 |

|--------|-------|------------|------|---------|

| PF0    | 46    | SYNC       | OC0A |         |

| PF1    | 47    | SYNC       | OC0B | ХСКО    |

| PF2    | 48    | SYNC/ASYNC | 0000 | RXD0    |

| PF3    | 49    | SYNC       | OC0D | TXD0    |

| PF4    | 50    | SYNC       |      |         |

| PF5    | 51    | SYNC       |      |         |

| PF6    | 54    | SYNC       |      |         |

| PF7    | 55    | SYNC       |      |         |

| GND    | 52    |            |      |         |

| vcc    | 53    |            |      |         |

Table 30-7. Port R- Alternate functions

| PORT R | PIN # | INTERRUPT | PROGR     | XTAL  |

|--------|-------|-----------|-----------|-------|

| PDI    | 56    |           | PDI_DATA  |       |

| RESET  | 57    |           | PDI_CLOCK |       |

| PRO    | 58    | SYNC      |           | XTAL2 |

| PR1    | 59    | SYNC      |           | XTAL1 |

# Table 30-8. ATxmega256/192/128/64A3 Boundary Scan Order

| Bit Number | Signal Name | Module |

|------------|-------------|--------|

| 149        | PQ3.Bidir   |        |

| 148        | PQ3.Control |        |

| 147        | PQ2.Bidir   |        |

| 146        | PQ2.Control | DODT O |

| 145        | PQ1.Bidir   | PORT Q |

| 144        | PQ1.Control |        |

| 143        | PQ0.Bidir   |        |

| 142        | PQ0.Control |        |

| 141        | PK7.Bidir   |        |

| 140        | PK7.Control |        |

| 139        | PK6.Bidir   |        |

| 138        | PK6.Control |        |

| 137        | PK5.Bidir   |        |

| 136        | PK5.Control |        |

| 135        | PK4.Bidir   |        |

| 134        | PK4.Control | PORT K |

| 133        | PK3.Bidir   | PORTK  |

| 132        | PK3.Control |        |

| 131        | PK2.Bidir   |        |

| 130        | PK2.Control | ]      |

| 129        | PK1.Bidir   |        |

| 128        | PK1.Control |        |

| 127        | PK0.Bidir   | ]      |

| 126        | PK0.Control |        |

# 34.4 Flash and EEPROM Memory Characteristics

| Symbol | mbol Parameter | Condit             | ion  | Min | Тур | Max | Units   |

|--------|----------------|--------------------|------|-----|-----|-----|---------|

|        |                |                    | 25°C | 10K |     |     | Quala   |

|        |                | Write/Erase cycles | 85°C | 10K |     |     | - Cycle |

|        | Flash          |                    | 25°C | 100 |     |     | Year    |

|        |                | Data retention     | 55°C | 25  |     |     |         |

|        |                |                    | 25°C | 80K |     |     |         |

|        | FEDDOM         | Write/Erase cycles | 85°C | 30K |     |     | Cycle   |

|        | EEPROM         |                    | 25°C | 100 |     |     | N       |

|        |                | Data retention     | 55°C | 25  |     |     | Year    |

#### Table 34-3. Endurance and Data Retention

## Table 34-4.Programming time

| Symbol | Parameter  | Condition                                   | Min | <b>Typ</b> <sup>(1)</sup> | Max | Units |

|--------|------------|---------------------------------------------|-----|---------------------------|-----|-------|

|        | Chip Erase | Flash, EEPROM <sup>(2)</sup> and SRAM Erase |     | 40                        |     |       |

|        |            | Page Erase                                  |     | 6                         |     |       |

|        | Flash      | Page Write                                  |     | 6                         |     |       |

|        |            | Page WriteAutomatic Page Erase and Write    |     | 12                        |     | ms    |

|        |            | Page Erase                                  |     | 6                         |     |       |

|        | EEPROM     | Page Write                                  |     | 6                         |     |       |

|        |            | Page WriteAutomatic Page Erase and Write    |     | 12                        |     |       |

Notes: 1. Programming is timed from the internal 2MHz oscillator.

2. EEPROM is not erased if the EESAVE fuse is programmed.

| Symbol               | Parameter                                              | Condition                                        | Min | Тур | Max | Units |

|----------------------|--------------------------------------------------------|--------------------------------------------------|-----|-----|-----|-------|

| SF                   | Safety factor                                          | Capacitive load matched to crystal specification | 3   |     |     |       |

| ESR/R <sub>1</sub>   | Recommended crystal equivalent series resistance (ESR) | Crystal load capacitance 6.5pF                   |     |     | 60  | kΩ    |

|                      |                                                        | Crystal load capacitance 9.0pF                   |     |     | 35  |       |

| C <sub>IN_TOSC</sub> | Input capacitance between TOSC pins                    | Normal mode                                      |     | 1.7 |     |       |

|                      |                                                        | Low power mode                                   |     | 2.2 |     | pF    |

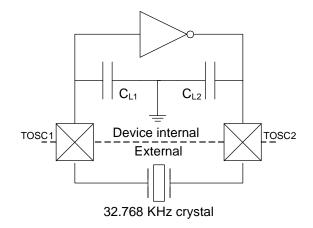

Table 34-18. External 32.768kHz Crystal Oscillator and TOSC characteristics

Note: 1. See Figure 34-2 on page 71 for definition

The input capacitance between the TOSC pins is CL1 + CL2 in series as seen from the crystal when oscillating without external capacitors.

| Symbol | Parameter                               | Condition <sup>(1)</sup> | Min | Typ <sup>(2)</sup> | Max | Units |

|--------|-----------------------------------------|--------------------------|-----|--------------------|-----|-------|

|        |                                         | Int. 32.768 kHz RC       |     | 130                |     |       |

|        | Idle Sleep, Standby and Extended        | Int. 2 MHz RC            |     | 2                  |     |       |

|        | Standby sleep mode                      | Ext. 2 MHz Clock         |     | 2                  |     |       |

|        |                                         | Int. 32 MHz RC           |     | 0.17               |     | μS    |

|        |                                         | Int. 32.768 kHz RC       |     | 320                |     |       |

|        | Power-save and Power-down<br>Sleep mode | Int. 2 MHz RC            |     | 10.3               |     |       |

|        |                                         | Ext. 2 MHz Clock         |     | 4.5                |     |       |

|        |                                         | Int. 32 MHz RC           |     | 5.8                |     |       |

Notes: 1. Non-prescaled System Clock source.

2. Time from pin change on external interrupt pin to first available clock cycle. Additional interrupt response time is minimum 5 system clock source cycles.

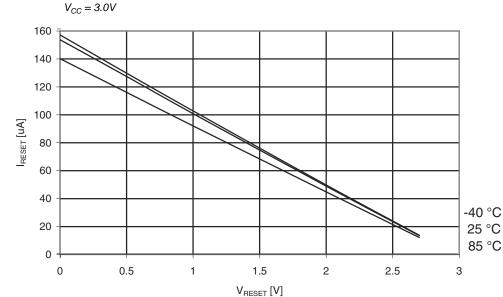

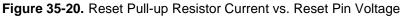

Figure 35-19. Reset Pull-up Resistor Current vs. Reset Pin Voltage  $V_{CC} = 3.0V$

#### 36.1.2 rev. B

- Bandgap voltage input for the ACs can not be changed when used for both ACs simultaneously

- VCC voltage scaler for AC is non-linear

- ADC has increased INL error for some operating conditions

- ADC gain stage output range is limited to 2.4 V

- ADC Event on compare match non-functional

- Bandgap measurement with the ADC is non-functional when VCC is below 2.7V

- Accuracy lost on first three samples after switching input to ADC gain stage

- Configuration of PGM and CWCM not as described in XMEGA A Manual

- PWM is not restarted properly after a fault in cycle-by-cycle mode

- BOD will be enabled at any reset

- DAC is nonlinear and inaccurate when reference is above 2.4V or VCC 0.6V

- · DAC has increased INL or noise for some operating conditions

- DAC refresh may be blocked in S/H mode

- Conversion lost on DAC channel B in event triggered mode

- EEPROM page buffer always written when NVM DATA0 is written

- · Pending full asynchronous pin change interrupts will not wake the device

- Pin configuration does not affect Analog Comparator Output

- NMI Flag for Crystal Oscillator Failure automatically cleared

- Writing EEPROM or Flash while reading any of them will not work

- · Crystal start-up time required after power-save even if crystal is source for RTC

- RTC Counter value not correctly read after sleep

- · Pending asynchronous RTC-interrupts will not wake up device

- TWI Transmit collision flag not cleared on repeated start

- Clearing TWI Stop Interrupt Flag may lock the bus

- TWI START condition at bus timeout will cause transaction to be dropped

- TWI Data Interrupt Flag (DIF) erroneously read as set

- WDR instruction inside closed window will not issue reset

- 1. Bandgap voltage input for the ACs cannot be changed when used for both ACs simultaneously

If the Bandgap voltage is selected as input for one Analog Comparator (AC) and then selected/deselected as input for another AC, the first comparator will be affected for up to 1  $\mu$ s and could potentially give a wrong comparison result.

#### Problem fix/Workaround

If the Bandgap is required for both ACs simultaneously, configure the input selection for both ACs before enabling any of them.

#### 2. VCC voltage scaler for AC is non-linear

The 6-bit VCC voltage scaler in the Analog Comparators is non-linear.

#### Problem fix/Workaround

Wait at least one prescaled RTC clock cycle before reading the RTC CNT value.

#### 22. Pending asynchronous RTC-interrupts will not wake up device

Asynchronous Interrupts from the Real-Time-Counter that is pending when the sleep instruction is executed, will be ignored until the device is woken from another source or the source triggers again.

#### Problem fix/Workaround

None.

#### 23. TWI Transmit collision flag not cleared on repeated start

The TWI transmit collision flag should be automatically cleared on start and repeated start, but is only cleared on start.

#### Problem fix/Workaround

Clear the flag in software after address interrupt.

#### 24. Clearing TWI Stop Interrupt Flag may lock the bus

If software clears the STOP Interrupt Flag (APIF) on the same Peripheral Clock cycle as the hardware sets this flag due to a new address received, CLKHOLD is not cleared and the SCL line is not released. This will lock the bus.

#### Problem fix/Workaround

Check if the bus state is IDLE. If this is the case, it is safe to clear APIF. If the bus state is not IDLE, wait for the SCL pin to be low before clearing APIF.

#### Code:

```

/* Only clear the interrupt flag if within a "safe zone". */

while ( /* Bus not IDLE: */

((COMMS TWI.MASTER.STATUS & TWI MASTER BUSSTATE gm) !=

TWI MASTER BUSSTATE IDLE gc)) &&

/* SCL not held by slave: */

! (COMMS TWI.SLAVE.STATUS & TWI SLAVE CLKHOLD bm)

)

{

/* Ensure that the SCL line is low */

if ( !(COMMS_PORT.IN & PIN1_bm) )

if ( !(COMMS PORT.IN & PIN1 bm) )

break;

}

/* Check for an pending address match interrupt */

if ( !(COMMS TWI.SLAVE.STATUS & TWI SLAVE CLKHOLD bm) )

{

/* Safely clear interrupt flag */

COMMS TWI.SLAVE.STATUS |= (uint8 t) TWI SLAVE APIF bm;

}

```

#### 25. TWI START condition at bus timeout will cause transaction to be dropped

If Bus Timeout is enabled and a timeout occurs on the same Peripheral Clock cycle as a START is detected, the transaction will be dropped.

### Problem fix/Workaround

None.

### 26. TWI Data Interrupt Flag erroneously read as set

When issuing the TWI slave response command CMD=0b11, it takes 1 Peripheral Clock cycle to clear the data interrupt flag (DIF). A read of DIF directly after issuing the command will show the DIF still set.

## Problem fix/Workaround

Add one NOP instruction before checking DIF.

## 27. WDR instruction inside closed window will not issue reset

When a WDR instruction is execute within one ULP clock cycle after updating the window control register, the counter can be cleared without giving a system reset.

## Problem fix/Workaround

Wait at least one ULP clock cycle before executing a WDR instruction.

# 36.2 ATxmega192A3, ATxmega128A3, ATxmega64A3

#### 36.2.1 rev. E

- Bandgap voltage input for the ACs can not be changed when used for both ACs simultaneously

- VCC voltage scaler for AC is non-linear

- ADC has increased INL error for some operating conditions

- ADC gain stage output range is limited to 2.4 V

- ADC Event on compare match non-functional

- Bandgap measurement with the ADC is non-functional when VCC is below 2.7V

- Accuracy lost on first three samples after switching input to ADC gain stage

- Configuration of PGM and CWCM not as described in XMEGA A Manual

- PWM is not restarted properly after a fault in cycle-by-cycle mode

- BOD will be enabled at any reset

- DAC is nonlinear and inaccurate when reference is above 2.4V or VCC 0.6V

- DAC has increased INL or noise for some operating conditions

- DAC refresh may be blocked in S/H mode

- Conversion lost on DAC channel B in event triggered mode

- EEPROM page buffer always written when NVM DATA0 is written

- Pending full asynchronous pin change interrupts will not wake the device

- Pin configuration does not affect Analog Comparator Output

- NMI Flag for Crystal Oscillator Failure automatically cleared

- Crystal start-up time required after power-save even if crystal is source for RTC

- RTC Counter value not correctly read after sleep

- Pending asynchronous RTC-interrupts will not wake up device

- TWI Transmit collision flag not cleared on repeated start

- Clearing TWI Stop Interrupt Flag may lock the bus

- TWI START condition at bus timeout will cause transaction to be dropped

- TWI Data Interrupt Flag (DIF) erroneously read as set

- WDR instruction inside closed window will not issue reset

# 1. Bandgap voltage input for the ACs cannot be changed when used for both ACs simultaneously

If the Bandgap voltage is selected as input for one Analog Comparator (AC) and then selected/deselected as input for another AC, the first comparator will be affected for up to 1  $\mu$ s and could potentially give a wrong comparison result.

#### Problem fix/Workaround

If the Bandgap is required for both ACs simultaneously, configure the input selection for both ACs before enabling any of them.

#### 2. VCC voltage scaler for AC is non-linear

The 6-bit VCC voltage scaler in the Analog Comparators is non-linear.

# XMEGA A3

#### 26. WDR instruction inside closed window will not issue reset

When a WDR instruction is execute within one ULP clock cycle after updating the window control register, the counter can be cleared without giving a system reset.

#### Problem fix/Workaround

Wait at least one ULP clock cycle before executing a WDR instruction.

# **37. Datasheet Revision History**

Please note that the referring page numbers in this section are referred to this document. The referring revision in this section are referring to the document revision.

# 37.1 8068U - 06/13

1. Not recommended for new designs - Use XMEGA A3U series.

# 37.2 8068T - 12/10

- 1. Datasheet status changed to complete: Preliminary removed from the front page.

- 2. Updated all tables in the "Electrical Characteristics" .

- 3. Updated "Packaging information" on page 61.

- 4. Replaced Table 34-11 on page 69

- 5. Replaced Table 34-18 on page 71 and added the figure "TOSC input capacitance" on page 71

- 6. Added ERRATA "rev. E" .

- 7. Added ERRATA "rev. B" .

- 8. Updated ERRATA for ADC (ADC has increased INL error for some operating conditions).

- 9. Updated the last page by Atmel new Brand Style Guide.

# 37.3 8068S - 09/10

10. Updated "Errata" on page 93.

# 37.4 8068R - 08/10

- 1. Updated the Footnote 3 of "Ordering Information" on page 2.

- 2. Updated Footnote 2 of Figure 2-1 on page 3.

- 3. Updated "Data Memory Map (Hexadecimal address)" on page 11. 192A3 has 2 KB EEPROM.

- 4. Updated "Features" on page 27. Event Channel 0 output on port pin 7.

- 5. Updated "Absolute Maximum Ratings\*" on page 63 by adding Icc for Flash/EEPROM Programming.

- 6. Added AVCC in "ADC Characteristics" on page 67.

- 7. Updated Start up time in "ADC Characteristics" on page 67.

# XMEGA A3

|    | 29.1Features                                   |    |

|----|------------------------------------------------|----|

|    | 29.20verview                                   | 48 |

|    | 29.3IEEE 1149.1 (JTAG) Boundary-scan           | 48 |

| 30 | Pinout and Pin Functions                       | 49 |

|    | 30.1Alternate Pin Function Description         | 49 |

|    | 30.2Alternate Pin Functions                    | 51 |

| 31 | Peripheral Module Address Map                  | 56 |

| 32 | Instruction Set Summary                        | 57 |

| 33 | Packaging information                          | 61 |

|    | 33.164A                                        | 61 |

|    | 33.264M2                                       | 62 |

| 34 | Electrical Characteristics                     | 63 |

|    | 34.1Absolute Maximum Ratings*                  | 63 |

|    | 34.2DC Characteristics                         | 63 |

|    | 34.3Operating Voltage and Frequency            | 65 |

|    | 34.4Flash and EEPROM Memory Characteristics    | 66 |

|    | 34.5ADC Characteristics                        | 67 |

|    | 34.6DAC Characteristics                        | 68 |

|    | 34.7Analog Comparator Characteristics          | 68 |

|    | 34.8Bandgap Characteristics                    | 68 |

|    | 34.9Brownout Detection Characteristics         | 69 |

|    | 34.10PAD Characteristics                       | 69 |

|    | 34.11POR Characteristics                       | 70 |

|    | 34.12Reset Characteristics                     | 70 |

|    | 34.13Oscillator Characteristics                | 70 |

| 35 | Typical Characteristics                        | 72 |

|    | 35.1Active Supply Current                      | 72 |

|    | 35.2Idle Supply Current                        | 75 |

|    | 35.3Power-down Supply Current                  | 79 |

|    | 35.4Power-save Supply Current                  | 80 |

|    | 35.5Pin Pull-up                                | 80 |

|    | 35.6Pin Output Voltage vs. Sink/Source Current | 82 |

|    | 35.7Pin Thresholds and Hysteresis              | 85 |

|    | 35.8Bod Thresholds                             |    |

#### Headquarters

*Atmel Corporation* 2325 Orchard Parkway San Jose, CA 95131 USA Tel: 1(408) 441-0311 Fax: 1(408) 487-2600

#### International

Atmel Asia Unit 1-5 & 16, 19/F BEA Tower, Millennium City 5 418 Kwun Tong Road Kwun Tong, Kowloon Hong Kong Tel: (852) 2245-6100 Fax: (852) 2722-1369 Atmel Europe Le Krebs 8, Rue Jean-Pierre Timbaud BP 309 78054 Saint-Quentin-en-Yvelines Cedex France Tel: (33) 1-30-60-70-00 Fax: (33) 1-30-60-71-11

#### Atmel Japan

9F, Tonetsu Shinkawa Bldg. 1-24-8 Shinkawa Chuo-ku, Tokyo 104-0033 Japan Tel: (81) 3-3523-3551 Fax: (81) 3-3523-7581

#### **Product Contact**

Web Site www.atmel.com Technical Support avr@atmel.com Sales Contact www.atmel.com/contacts

Literature Requests www.atmel.com/literature

Disclaimer: The information in this document is provided in connection with Atmel products. No license, express or implied, by estoppel or otherwise, to any intellectual property right is granted by this document or in connection with the sale of Atmel products. EXCEPT AS SET FORTH IN ATMEL'S TERMS AND CONDI-TIONS OF SALE LOCATED ON ATMEL'S WEB SITE, ATMEL ASSUMES NO LIABILITY WHATSOEVER AND DISCLAIMS ANY EXPRESS, IMPLIED OR STATUTORY WARRANTY RELATING TO ITS PRODUCTS INCLUDING, BUT NOT LIMITED TO, THE IMPLIED WARRANTY OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE, OR NON-INFRINGEMENT. IN NO EVENT SHALL ATMEL BE LIABLE FOR ANY DIRECT, INDIRECT, CONSEQUENTIAL, PUNITIVE, SPECIAL OR INCIDEN-TAL DAMAGES (INCLUDING, WITHOUT LIMITATION, DAMAGES FOR LOSS OF PROFITS, BUSINESS INTERRUPTION, OR LOSS OF INFORMATION) ARISING OUT OF THE USE OR INABILITY TO USE THIS DOCUMENT, EVEN IF ATMEL HAS BEEN ADVISED OF THE POSSIBILITY OF SUCH DAMAGES. Atmel makes no representations or warranties with respect to the accuracy or completeness of the contents of this document and reserves the right to make changes to specifications and product descriptions at any time without notice. Atmel does not make any commitment to update the information contained herein. Unless specifically provided otherwise, Atmel products are not suitable for, and shall not be used in, automotive applications. Atmel's products are not intended, or warranted for use as components in applications intended to support or sustain life.

© 2009 Atmel Corporation. All rights reserved. Atmel<sup>®</sup>, Atmel<sup>®</sup> logo and combinations thereof, AVR<sup>®</sup>, AVR<sup>®</sup> logo and others are registered trademarks, XMEGA<sup>TM</sup> and others are trademarks of Atmel Corporation or its subsidiaries. Other terms and product names may be trademarks of others.