#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| 2 0 000                    |                                                                       |

|----------------------------|-----------------------------------------------------------------------|

| Product Status             | Obsolete                                                              |

| Core Processor             | ST7                                                                   |

| Core Size                  | 8-Bit                                                                 |

| Speed                      | 8MHz                                                                  |

| Connectivity               | SCI, SPI                                                              |

| Peripherals                | LVD, POR, PWM, WDT                                                    |

| Number of I/O              | 32                                                                    |

| Program Memory Size        | 8KB (8K x 8)                                                          |

| Program Memory Type        | FLASH                                                                 |

| EEPROM Size                | -                                                                     |

| RAM Size                   | 384 x 8                                                               |

| Voltage - Supply (Vcc/Vdd) | 3.8V ~ 5.5V                                                           |

| Data Converters            | A/D 12x10b                                                            |

| Oscillator Type            | Internal                                                              |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                     |

| Mounting Type              | Through Hole                                                          |

| Package / Case             | 42-SDIP (0.600", 15.24mm)                                             |

| Supplier Device Package    | -                                                                     |

| Purchase URL               | https://www.e-xfl.com/product-detail/stmicroelectronics/st72f324bj2b6 |

|                            |                                                                       |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

|        | 10.3.7   | 16-bit timer registers             |

|--------|----------|------------------------------------|

| 10.4   | Serial p | peripheral interface (SPI)         |

|        | 10.4.1   | Introduction                       |

|        | 10.4.2   | Main features                      |

|        | 10.4.3   | General description                |

|        | 10.4.4   | Clock phase and clock polarity     |

|        | 10.4.5   | Error flags                        |

|        | 10.4.6   | Low power modes                    |

|        | 10.4.7   | Interrupts                         |

|        | 10.4.8   | SPI registers                      |

| 10.5   | Serial c | communications interface (SCI) 108 |

|        | 10.5.1   | Introduction                       |

|        | 10.5.2   | Main features                      |

|        | 10.5.3   | General description                |

|        | 10.5.4   | Functional description111          |

|        | 10.5.5   | Low power modes                    |

|        | 10.5.6   | Interrupts                         |

|        | 10.5.7   | SCI registers                      |

| 10.6   | 10-bit A | VD converter (ADC) 128             |

|        | 10.6.1   | Introduction                       |

|        | 10.6.2   | Main features                      |

|        | 10.6.3   | Functional description129          |

|        | 10.6.4   | Low power modes                    |

|        | 10.6.5   | Interrupts                         |

|        | 10.6.6   | ADC registers                      |

| Instru | uction s | set                                |

| 11.1   |          | ddressing modes                    |

|        | 11.1.1   | Inherent                           |

|        | 11.1.2   | Immediate                          |

|        | 11.1.3   | Direct                             |

|        | 11.1.4   | Indexed (no offset, short, long)   |

|        | 11.1.5   | Indirect (short, long)             |

|        | 11.1.6   | Indirect indexed (short, long)     |

|        | 11.1.7   | Relative mode (direct, indirect)   |

| 11.2   | Instruct | tion groups                        |

11

57

| 12 | Elect | rical cha | aracteristics                                     | 141   |

|----|-------|-----------|---------------------------------------------------|-------|

|    | 12.1  | Parame    | eter conditions                                   | 141   |

|    |       | 12.1.1    | Minimum and maximum values                        | . 141 |

|    |       | 12.1.2    | Typical values                                    | . 141 |

|    |       | 12.1.3    | Typical curves                                    | . 141 |

|    |       | 12.1.4    | Loading capacitor                                 | . 141 |

|    |       | 12.1.5    | Pin input voltage                                 | . 142 |

|    | 12.2  | Absolut   | e maximum ratings                                 | 142   |

|    |       | 12.2.1    | Voltage characteristics                           | . 142 |

|    |       | 12.2.2    | Current characteristics                           | . 143 |

|    |       | 12.2.3    | Thermal characteristics                           | . 143 |

|    | 12.3  | Operati   | ng conditions                                     | 144   |

|    | 12.4  | LVD/AV    | D characteristics                                 | 145   |

|    |       | 12.4.1    | Operating conditions with LVD                     | . 145 |

|    |       | 12.4.2    | Auxiliary voltage detector (AVD) thresholds       | . 145 |

|    | 12.5  | Supply    | current characteristics                           | 146   |

|    |       | 12.5.1    | ROM current consumption                           | . 146 |

|    |       | 12.5.2    | Flash current consumption                         | . 147 |

|    |       | 12.5.3    | Supply and clock managers                         | . 148 |

|    |       | 12.5.4    | On-chip peripherals                               | . 148 |

|    | 12.6  | Clock a   | nd timing characteristics                         | 149   |

|    |       | 12.6.1    | General timings                                   | . 149 |

|    |       | 12.6.2    | External clock source                             | . 149 |

|    |       | 12.6.3    | Crystal and ceramic resonator oscillators         | . 150 |

|    |       | 12.6.4    | RC oscillators                                    | . 152 |

|    |       | 12.6.5    | PLL characteristics                               | . 153 |

|    | 12.7  | Memory    | y characteristics                                 | 153   |

|    |       | 12.7.1    | RAM and hardware registers                        | . 153 |

|    |       | 12.7.2    | Flash memory                                      | . 154 |

|    | 12.8  | EMC ch    | naracteristics                                    | 155   |

|    |       | 12.8.1    | Functional electromagnetic susceptibility (EMS)   | . 155 |

|    |       | 12.8.2    | Electromagnetic interference (EMI)                | . 156 |

|    |       | 12.8.3    | Absolute maximum ratings (electrical sensitivity) | . 157 |

|    | 12.9  | I/O port  | t pin characteristics                             | 158   |

|    |       | 12.9.1    | General characteristics                           | . 158 |

|    |       | 12.9.2    | Output driving current                            | . 159 |

|    |       |           |                                                   |       |

### 5.3.1 Accumulator (A)

The Accumulator is an 8-bit general purpose register used to hold operands and the results of the arithmetic and logic calculations and to manipulate data.

### 5.3.2 Index registers (X and Y)

These 8-bit registers are used to create effective addresses or as temporary storage areas for data manipulation. (The Cross-Assembler generates a precede instruction (PRE) to indicate that the following instruction refers to the Y register.)

The Y register is not affected by the interrupt automatic procedures.

### 5.3.3 **Program counter (PC)**

The program counter is a 16-bit register containing the address of the next instruction to be executed by the CPU. It is made of two 8-bit registers PCL (Program Counter Low which is the LSB) and PCH (Program Counter High which is the MSB).

### 5.3.4 Condition Code register (CC)

The 8-bit Condition Code register contains the interrupt masks and four flags representative of the result of the instruction just executed. This register can also be handled by the PUSH and POP instructions. These bits can be individually tested and/or controlled by specific instructions.

| CC |     |     |     |     |     |     | Reset valu | e: 111x1xxx |

|----|-----|-----|-----|-----|-----|-----|------------|-------------|

|    | 7   | 6   | 5   | 4   | 3   | 2   | 1          | 0           |

|    | 1   | 1   | 11  | Н   | 10  | N   | Z          | С           |

|    | R/W        | R/W         |

Table 6.Arithmetic management bits

| Blt | Name | Function                                                                                                                                                                                                                                                                                                                                                                                                                |

|-----|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 4   | н    | <ul> <li>Half carry</li> <li>This bit is set by hardware when a carry occurs between bits 3 and 4 of the ALU during an ADD or ADC instructions. It is reset by hardware during the same instructions.</li> <li>0: No half carry has occurred.</li> <li>1: A half carry has occurred.</li> <li>This bit is tested using the JRH or JRNH instruction. The H bit is useful in BCD arithmetic subroutines.</li> </ul>       |

| 2   | N    | Negative<br>This bit is set and cleared by hardware. It is representative of the result sign of the last<br>arithmetic, logical or data manipulation. It is a copy of the result 7th bit.<br>0: The result of the last operation is positive or null.<br>1: The result of the last operation is negative (that is, the most significant bit is a logic<br>1.<br>This bit is accessed by the JRMI and JRPL instructions. |

#### **Application notes**

The LVDRF flag is not cleared when another reset type occurs (external or watchdog); the LVDRF flag remains set to keep trace of the original failure. In this case, a watchdog reset can be detected by software while an external reset cannot.

**Caution:** When the LVD is not activated with the associated option byte, the WDGRF flag can not be used in the application.

|      | interru |                                |

|------|---------|--------------------------------|

| IS11 | IS10    | External interrupt sensitivity |

| 0    | 0       | Falling edge and low level     |

| 0    | 1       | Rising edge only               |

| 1    | 0       | Falling edge only              |

| 1    | 1       | Rising and falling edge        |

Table 21. Interrupt sensitivity - ei3

### Table 22.Interrupt sensitivity - ei0

| IS21 IS20 | 1600        | External interrupt sensitivity |                            |  |  |

|-----------|-------------|--------------------------------|----------------------------|--|--|

|           | IPA bit = 0 | IPA bit = 1                    |                            |  |  |

| 0         | 0           | Falling edge and low level     | Rising edge and high level |  |  |

| 0         | 1           | Rising edge only               | Falling edge only          |  |  |

| 1         | 0           | Falling edge only              | Rising edge only           |  |  |

| 1         | 1           | Rising and falling edge        |                            |  |  |

#### Table 23. Interrupt sensitivity - ei1

| IS21 | IS20 | External interrupt sensitivity |

|------|------|--------------------------------|

| 0    | 0    | Falling edge and low level     |

| 0    | 1    | Rising edge only               |

| 1    | 0    | Falling edge only              |

| 1    | 1    | Rising and falling edge        |

| Table 24. | Nested interrupts register map and reset values |

|-----------|-------------------------------------------------|

|-----------|-------------------------------------------------|

| Address (Hex.) | Register label       | 7          | 6          | 5          | 4          | 3          | 2          | 1          | 0          |

|----------------|----------------------|------------|------------|------------|------------|------------|------------|------------|------------|

|                |                      | e          | i1         | е          | i0         | MCC        | ; + SI     |            |            |

| 0024h          | ISPR0<br>reset value | l1_3<br>1  | 10_3<br>1  | l1_2<br>1  | 10_2<br>1  | 11_1<br>1  | 10_1<br>1  | 1          | 1          |

|                |                      | S          | PI         |            |            | ei3        |            | ei2        |            |

| 0025h          | ISPR1<br>reset value | 1_7<br>1   | 10_7<br>1  | l1_6<br>1  | 10_6<br>1  | l1_5<br>1  | 10_5<br>1  | 1_4<br>1   | 10_4<br>1  |

|                |                      | AVD        |            | SCI        |            | Timer B    |            | Timer A    |            |

| 0026h          | ISPR2<br>reset value | 11_11<br>1 | 10_11<br>1 | 11_10<br>1 | 10_10<br>1 | l1_9<br>1  | 10_9<br>1  | l1_8<br>1  | 10_8<br>1  |

| 0027h          | ISPR3<br>reset value | 1          | 1          | 1          | 1          | l1_13<br>1 | 10_13<br>1 | 11_12<br>1 | 10_12<br>1 |

| 0028h          | EICR<br>reset value  | IS11<br>0  | IS10<br>0  | IPB<br>0   | IS21<br>0  | IS20<br>0  | IPA<br>0   | 0          | 0          |

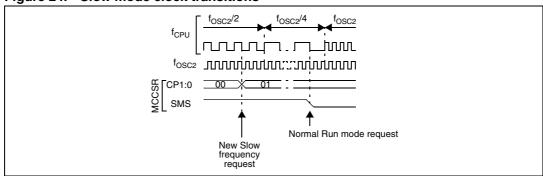

Figure 24. Slow mode clock transitions

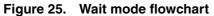

### 8.3 Wait mode

Wait mode places the MCU in a low power consumption mode by stopping the CPU.

This power saving mode is selected by calling the 'WFI' instruction.

All peripherals remain active. During Wait mode, the I[1:0] bits of the CC register are forced to '10', to enable all interrupts. All other registers and memory remain unchanged. The MCU remains in Wait mode until an interrupt or reset occurs, whereupon the Program Counter branches to the starting address of the interrupt or reset service routine. The MCU will remain in Wait mode until a reset or an interrupt occurs, causing it to wake up. Refer to *Figure 25*.

Before servicing an interrupt, the CC register is pushed on the stack. The I[1:0] bits of the CC register are set to the current software priority level of the interrupt routine and recovered when the CC register is popped.

57

| Bit | Name    | Function                                                                                                                                                                                                                                                                                                                                                                                                         |

|-----|---------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 6:5 | CP[1:0] | CPU Clock Prescaler<br>These bits select the CPU clock prescaler which is applied in different slow modes.<br>Their action is conditioned by the setting of the SMS bit. These two bits are set and<br>cleared by software:<br>00: $f_{CPU}$ in Slow mode = $f_{OSC2}/2$<br>01: $f_{CPU}$ in Slow mode = $f_{OSC2}/4$<br>10: $f_{CPU}$ in Slow mode = $f_{OSC2}/8$<br>11: $f_{CPU}$ in Slow mode = $f_{OSC2}/16$ |

| 4   | SMS     | <ul> <li>Slow Mode Select</li> <li>This bit is set and cleared by software.</li> <li>0: Normal mode. f<sub>CPU</sub> = f<sub>OSC2</sub>.</li> <li>1: Slow mode. f<sub>CPU</sub> is given by CP1, CP0.</li> <li>See Section 8.2: Slow mode and Section 10.2: Main clock controller with real-time clock and beeper (MCC/RTC) for more details.</li> </ul>                                                         |

| 3:2 | TB[1:0] | Time Base control<br>These bits select the programmable divider time base. They are set and cleared by<br>software (see <i>Table 40</i> ). A modification of the time base is taken into account at the<br>end of the current period (previously set) to avoid an unwanted time shift. This<br>allows to use this time base as a real-time clock.                                                                |

| 1   | OIE     | Oscillator interrupt Enable<br>This bit set and cleared by software.<br>0: Oscillator interrupt disabled<br>1: Oscillator interrupt enabled<br>This interrupt can be used to exit from Active-halt mode. When this bit is set, calling<br>the ST7 software HALT instruction enters the Active-halt power saving mode.                                                                                            |

| 0   | OIF     | Oscillator interrupt Flag<br>This bit is set by hardware and cleared by software reading the MCCSR register. It<br>indicates when set that the main oscillator has reached the selected elapsed time<br>(TB1:0).<br>0: Timeout not reached<br>1: Timeout reached<br><b>Caution</b> : The BRES and BSET instructions must not be used on the MCCSR<br>register to avoid unintentionally clearing the OIF bit.     |

Table 39.

MCCSR register description (continued)

|  | Table 40. | Time base selection |  |

|--|-----------|---------------------|--|

|--|-----------|---------------------|--|

| Counter prescaler | Time                      | base                      | - TB1 | тво  |

|-------------------|---------------------------|---------------------------|-------|------|

|                   | f <sub>OSC2</sub> = 4 MHz | f <sub>OSC2</sub> = 8 MHz |       | 1 BU |

| 16000             | 4 ms                      | 2 ms                      | 0     | 0    |

| 32000             | 8 ms                      | 4 ms                      | 0     | 1    |

| 80000             | 20 ms                     | 10 ms                     | 1     | 0    |

| 200000            | 50 ms                     | 25 ms                     | 1     | 1    |

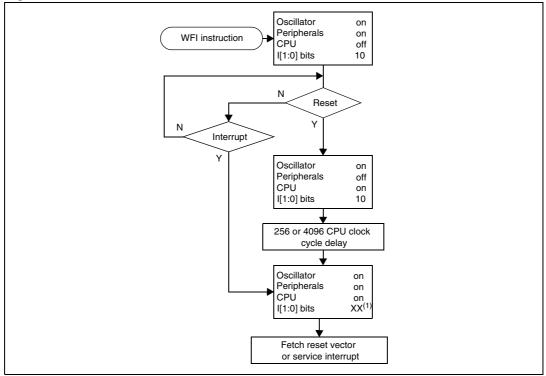

#### 16-bit read sequence

The 16-bit read sequence (from either the Counter register or the Alternate Counter register) is illustrated in the following *Figure 37*.

Figure 37. 16-bit read sequence

The user must first read the MSB, afterwhich the LSB value is automatically buffered.

This buffered value remains unchanged until the 16-bit read sequence is completed, even if the user reads the MSB several times.

After a complete reading sequence, if only the CLR register or ACLR register are read, they return the LSB of the count value at the time of the read.

Whatever the timer mode used (input capture, output compare, one pulse mode or PWM mode) an overflow occurs when the counter rolls over from FFFFh to 0000h then:

- The TOF bit of the SR register is set.

- A timer interrupt is generated if:

- TOIE bit of the CR1 register is set and

- I bit of the CC register is cleared.

If one of these conditions is false, the interrupt remains pending to be issued as soon as they are both true.

Clearing the overflow interrupt request is done in two steps:

- 1. Reading the SR register while the TOF bit is set.

- 2. An access (read or write) to the CLR register.

Note: The TOF bit is not cleared by access to the ACLR register. The advantage of accessing the ACLR register rather than the CLR register is that it allows simultaneous use of the overflow function and reading the free running counter at random times (for example, to measure elapsed time) without the risk of clearing the TOF bit erroneously.

The timer is not affected by Wait mode.

In Halt mode, the counter stops counting until the mode is exited. Counting then resumes from the previous count (MCU awakened by an interrupt) or from the reset count (MCU awakened by a reset).

If the timer clock is an external clock, the formula is:

$$\Delta \text{ OC}i\text{R} = \Delta t \star f_{\text{EXT}}$$

Where:

Clearing the output compare interrupt request (that is, clearing the OCF*i* bit) is done by:

- 1. Reading the SR register while the OCF*i* bit is set.

- 2. An access (read or write) to the OCiLR register.

The following procedure is recommended to prevent the OCF*i* bit from being set between the time it is read and the write to the OC*i*R register:

- Write to the OC*i*HR register (further compares are inhibited).

- Read the SR register (first step of the clearance of the OCF*i* bit, which may be already set).

- Write to the OC*i*LR register (enables the output compare function and clears the OCF*i* bit).

- Note: 1 After a processor write cycle to the OCiHR register, the output compare function is inhibited until the OCiLR register is also written.

- 2 If the OCiE bit is not set, the OCMPi pin is a general I/O port and the OLVLi bit will not appear when a match is found but an interrupt could be generated if the OCIE bit is set.

- 3 In both internal and external clock modes, OCFi and OCMPi are set while the counter value equals the OCiR register value (see Figure 44 on page 83 for an example with f<sub>CPU</sub>/2 and Figure 45 on page 83 for an example with f<sub>CPU</sub>/4). This behavior is the same in OPM or PWM mode.

- 4 The output compare functions can be used both for generating external events on the OCMPi pins even if the input capture mode is also used.

- 5 The value in the 16-bit OCiR register and the OLVi bit should be changed after each successful comparison in order to control an output waveform or establish a new elapsed timeout.

#### Forced output compare capability

When the FOLV*i* bit is set by software, the OLVL*i* bit is copied to the OCMP*i* pin. The OLV*i* bit has to be toggled in order to toggle the OCMP*i* pin when it is enabled (OC*i*E bit = 1). The OCF*i* bit is then not set by hardware, and thus no interrupt request is generated.

The FOLVL*i* bits have no effect in both one pulse mode and PWM mode.

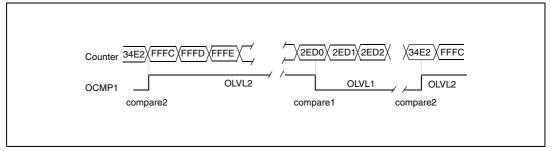

# Figure 48. Pulse width modulation mode timing example with two output compare functions<sup>(1)(2)</sup>

1. OC1R = 2ED0h, OC2R = 34E2, OLVL1 = 0, OLVL2 = 1

2. On timers with only one Output Compare register, a fixed frequency PWM signal can be generated using the output compare and the counter overflow to define the pulse length.

#### **Pulse Width Modulation mode**

Pulse Width Modulation (PWM) mode enables the generation of a signal with a frequency and pulse length determined by the value of the OC1R and OC2R registers.

Pulse Width Modulation mode uses the complete Output Compare 1 function plus the OC2R register, and so this functionality can not be used when PWM mode is activated.

In PWM mode, double buffering is implemented on the output compare registers. Any new values written in the OC1R and OC2R registers are taken into account only at the end of the PWM period (OC2) to avoid spikes on the PWM output pin (OCMP1).

#### Procedure

To use Pulse Width Modulation mode:

- 1. Load the OC2R register with the value corresponding to the period of the signal using the formula below.

- 2. Load the OC1R register with the value corresponding to the period of the pulse if (OLVL1 = 0 and OLVL2 = 1) using the formula in the opposite column.

- 3. Select the following in the CR1 register:

- Using the OLVL1 bit, select the level to be applied to the OCMP1 pin after a successful comparison with the OC1R register.

- Using the OLVL2 bit, select the level to be applied to the OCMP1 pin after a successful comparison with the OC2R register.

- 4. Select the following in the CR2 register:

- Set OC1E bit: the OCMP1 pin is then dedicated to the output compare 1 function.

- Set the PWM bit.

- Select the timer clock (CC[1:0]) (see *Table 50*).

### 10.4.5 Error flags

### Master mode fault (MODF)

Master mode fault occurs when the master device has its  $\overline{\text{SS}}$  pin pulled low.

When a Master mode fault occurs:

- The MODF bit is set and an SPI interrupt request is generated if the SPIE bit is set.

- The SPE bit is reset. This blocks all output from the device and disables the SPI peripheral.

- The MSTR bit is reset, thus forcing the device into slave mode.

Clearing the MODF bit is done through a software sequence:

- 1. A read access to the SPICSR register while the MODF bit is set.

- 2. A write to the SPICR register.

Note: To avoid any conflicts in an application with multiple slaves, the SS pin must be pulled high during the MODF bit clearing sequence. The SPE and MSTR bits may be restored to their original state during or after this clearing sequence.

Hardware does not allow the user to set the SPE and MSTR bits while the MODF bit is set except in the MODF bit clearing sequence.

### **Overrun condition (OVR)**

An overrun condition occurs, when the master device has sent a data byte and the slave device has not cleared the SPIF bit issued from the previously transmitted byte.

When an Overrun occurs the OVR bit is set and an interrupt request is generated if the SPIE bit is set.

In this case, the receiver buffer contains the byte sent after the SPIF bit was last cleared. A read to the SPIDR register returns this byte. All other bytes are lost.

The OVR bit is cleared by reading the SPICSR register.

#### Write collision error (WCOL)

A write collision occurs when the software tries to write to the SPIDR register while a data transfer is taking place with an external device. When this happens, the transfer continues uninterrupted and the software write is unsuccessful.

Write collisions can occur both in master and slave mode. See also *Slave select* management on page 98.

Note: A read collision will never occur since the received data byte is placed in a buffer in which access is always synchronous with the MCU operation.

The WCOL bit in the SPICSR register is set if a write collision occurs.

No SPI interrupt is generated when the WCOL bit is set (the WCOL bit is a status flag only).

A software sequence clears the WCOL bit (see *Figure 55*).

### 10.5.4 Functional description

The block diagram of the serial control interface is shown in *Figure 57*. It contains six dedicated registers:

- 2 control registers (SCICR1 and SCICR2)

- a status register (SCISR)

- a baud rate register (SCIBRR)

- an extended prescaler receiver register (SCIERPR)

- an extended prescaler transmitter register (SCIETPR)

Refer to the register descriptions in Section 10.5.7 for the definitions of each bit.

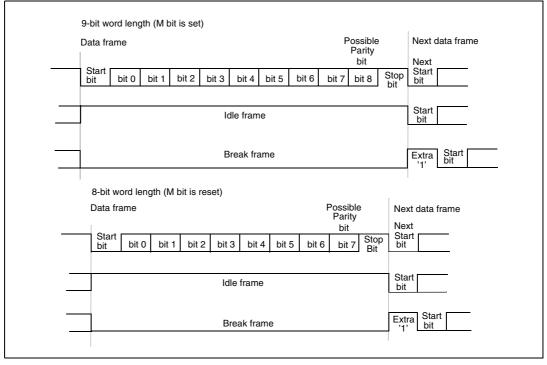

#### Serial data format

Word length may be selected as being either 8 or 9 bits by programming the M bit in the SCICR1 register (see *Figure 57*).

The TDO pin is in low state during the start bit.

The TDO pin is in high state during the stop bit.

An Idle character is interpreted as an entire frame of '1's followed by the start bit of the next frame which contains data.

A Break character is interpreted on receiving '0's for some multiple of the frame period. At the end of the last break frame the transmitter inserts an extra '1' bit to acknowledge the start bit.

Transmission and reception are driven by their own baud rate generator.

#### Figure 58. Word length programming

### 10.5.5 Low power modes

Table 60. Effect of low power modes on SCI

| Mode | Description                                                                                                |  |  |  |  |  |

|------|------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| Wait | No effect on SCI.<br>SCI interrupts cause the device to exit from Wait mode.                               |  |  |  |  |  |

| Halt | SCI registers are frozen.<br>In Halt mode, the SCI stops transmitting/receiving until Halt mode is exited. |  |  |  |  |  |

### 10.5.6 Interrupts

The SCI interrupt events are connected to the same interrupt vector.

These events generate an interrupt if the corresponding Enable Control bit is set and the interrupt mask in the CC register is reset (RIM instruction).

Table 61. SCI interrupt control/wakeup capability

| Interrupt event                | Event flag | Enable control bit | Exit from Wait | Exit from Halt |

|--------------------------------|------------|--------------------|----------------|----------------|

| Transmit data register empty   | TDRE       | TIE                | Yes            | No             |

| Transmission complete          | TC         | TCIE               | Yes            | No             |

| Received data ready to be read | RDRF       | BIE                | Yes            | No             |

| Overrun error detected         | OR         |                    | Yes            | No             |

| Idle line detected             | IDLE       | ILIE               | Yes            | No             |

| Parity error                   | PE         | PIE                | Yes            | No             |

### 10.5.7 SCI registers

### SCI status register (SCISR)

| SCISR |      |    |      |      |    |    | t value: 1100 | 0000 (C0h) |

|-------|------|----|------|------|----|----|---------------|------------|

|       | 7    | 6  | 5    | 4    | 3  | 2  | 1             | 0          |

|       | TDRE | тс | RDRF | IDLE | OR | NF | FE            | PE         |

|       | RO   | RO | RO   | RO   | RO | RO | RO            | RO         |

#### Table 62. SCISR register description

| Bit | Name | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|-----|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7   | TDRE | <ul> <li>Transmit Data Register Empty</li> <li>This bit is set by hardware when the content of the TDR register has been transferred into the shift register. An interrupt is generated if the TIE bit = 1 in the SCICR2 register. It is cleared by a software sequence (an access to the SCISR register followed by a write to the SCIDR register).</li> <li>0: Data is not transferred to the shift register.</li> <li>1: Data is transferred to the shift register.</li> <li>Note: Data will not be transferred to the shift register unless the TDRE bit is cleared.</li> </ul> |

| Bit | Name      | Function                                                                                                                                                                                                                                                                                                                                                                                             |

|-----|-----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:0 | ERPR[7:0] | 8-bit extended receive prescaler register<br>The extended baud rate generator is activated when a value different from 00h<br>is stored in this register. Therefore the clock frequency issued from the 16<br>divider (see <i>Figure 59</i> ) is divided by the binary factor set in the SCIERPR<br>register (in the range 1 to 255).<br>The extended baud rate generator is not used after a reset. |

### SCI extended transmit prescaler division register (SCIETPR)

This register is used to set the External Prescaler rate division factor for the transmit circuit.

SCIETPR

Reset value: 0000 0000 (00h)

7

6

5

4

3

2

1

0

ETPR[7:0]

R/W

#### Table 67. SCIETPR register description

| Bit | Name      | Function                                                                                                                                                                                                                                                                                                                                                                                              |

|-----|-----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:0 | ETPR[7:0] | 8-bit Extended Transmit Prescaler Register<br>The extended baud rate generator is activated when a value different from 00h<br>is stored in this register. Therefore the clock frequency issued from the 16<br>divider (see <i>Figure 59</i> ) is divided by the binary factor set in the SCIETPR<br>register (in the range 1 to 255).<br>The extended baud rate generator is not used after a reset. |

#### Table 68.Baud rate selection

|                                    |                            |                  | Con                      | ditions                                                                                                                                                                                                                                       |                                                                |                                                                                                |      |

|------------------------------------|----------------------------|------------------|--------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------|------------------------------------------------------------------------------------------------|------|

| Symbol                             | Parameter                  | f <sub>CPU</sub> | Accuracy vs.<br>Standard | Prescaler                                                                                                                                                                                                                                     | Standard                                                       | Baud rate                                                                                      | Unit |

| f <sub>Tx</sub><br>f <sub>Rx</sub> | Communication<br>frequency | 8 MHz            | ~0.16%                   | Conventional mode<br>TR (or RR) = 128, PR = 13<br>TR (or RR) = 32, PR = 13<br>TR (or RR) = 16, PR = 13<br>TR (or RR) = 8, PR = 13<br>TR (or RR) = 4, PR = 13<br>TR (or RR) = 16, PR = 3<br>TR (or RR) = 2, PR = 13<br>TR (or RR) = 1, PR = 13 | 300<br>1200<br>2400<br>4800<br>9600<br>10400<br>19200<br>38400 | ~300.48<br>~1201.92<br>~2403.84<br>~4807.69<br>~9615.38<br>~10416.67<br>~19230.77<br>~38461.54 | Hz   |

|                                    |                            |                  | ~0.79%                   | Extended mode<br>ETPR (or ERPR) = 35,<br>TR (or RR)= 1, PR = 1                                                                                                                                                                                | 14400                                                          | ~14285.71                                                                                      |      |

### 11.1.7 Relative mode (direct, indirect)

This addressing mode is used to modify the PC register value, by adding an 8-bit signed offset to it.

| Table 80. | Relative direct and indirect instructions and functions |

|-----------|---------------------------------------------------------|

| 14010 001 |                                                         |

| Available relative direct/indirect instructions | Function         |

|-------------------------------------------------|------------------|

| JRxx                                            | Conditional Jump |

| CALLR                                           | Call Relative    |

The relative addressing mode consists of two submodes:

#### **Relative (direct)**

The offset follows the opcode.

#### **Relative (indirect)**

The offset is defined in the memory, the address of which follows the opcode.

## 11.2 Instruction groups

The ST7 family devices use an Instruction Set consisting of 63 instructions. The instructions may be subdivided into 13 main groups as illustrated in the following table:

Table 81. Instruction groups

| Group                            | Instructions |      |      |      |      |       |     |     |

|----------------------------------|--------------|------|------|------|------|-------|-----|-----|

| Load and transfer                | LD           | CLR  |      |      |      |       |     |     |

| Stack operation                  | PUSH         | POP  | RSP  |      |      |       |     |     |

| Increment/decrement              | INC          | DEC  |      |      |      |       |     |     |

| Compare and tests                | СР           | TNZ  | BCP  |      |      |       |     |     |

| Logical operations               | AND          | OR   | XOR  | CPL  | NEG  |       |     |     |

| Bit operation                    | BSET         | BRES |      |      |      |       |     |     |

| Conditional bit test and branch  | BTJT         | BTJF |      |      |      |       |     |     |

| Arithmetic operations            | ADC          | ADD  | SUB  | SBC  | MUL  |       |     |     |

| Shift and rotates                | SLL          | SRL  | SRA  | RLC  | RRC  | SWAP  | SLA |     |

| Unconditional jump or call       | JRA          | JRT  | JRF  | JP   | CALL | CALLR | NOP | RET |

| Conditional branch               | JRxx         |      |      |      |      |       |     |     |

| Interruption management          | TRAP         | WFI  | HALT | IRET |      |       |     |     |

| Condition code flag modification | SIM          | RIM  | SCF  | RCF  |      |       |     |     |

#### 12.5.2 **Flash current consumption**

| Table 90. | Flash | current | consumption |

|-----------|-------|---------|-------------|

|           |       |         |             |

| Symbol          | Parameter                                          | Conditions                                                                                                                                                                                                                                                                    | 32 Kbyte<br>Flash         |                              | 16/8 Kbyte<br>Flash          |                             | Unit |  |

|-----------------|----------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------|------------------------------|------------------------------|-----------------------------|------|--|

|                 |                                                    |                                                                                                                                                                                                                                                                               | Тур                       | Max <sup>(1)</sup>           | Тур                          | Max <sup>(1)</sup>          |      |  |

|                 | Supply current in Run mode <sup>(2)</sup>          | $      f_{OSC} = 2 \text{ MHz}, \  f_{CPU} = 1 \text{ MHz} $ $      f_{OSC} = 4 \text{ MHz}, \  f_{CPU} = 2 \text{ MHz} $ $      f_{OSC} = 8 \text{ MHz}, \  f_{CPU} = 4 \text{ MHz} $ $      f_{OSC} = 16 \text{ MHz}, \  f_{CPU} = 8 \text{ MHz} $                          | 1.3<br>2.0<br>3.6<br>7.1  | 3.0<br>5.0<br>8.0<br>15.0    | 1<br>1.4<br>2.4<br>4.4       | 2.3<br>3.5<br>5.3<br>7.0    |      |  |

|                 | Supply current in Slow<br>mode <sup>(2)</sup>      | $      f_{OSC} = 2 \text{ MHz}, \      f_{CPU} = 62.5 \text{ kHz} \\       f_{OSC} = 4 \text{ MHz}, \      f_{CPU} = 125 \text{ kHz} \\       f_{OSC} = 8 \text{ MHz}, \      f_{CPU} = 250 \text{ kHz} \\       f_{OSC} = 16 \text{ MHz}, \      f_{CPU} = 500 \text{ kHz} $ | 0.6<br>0.7<br>0.8<br>1.1  | 2.7<br>3.0<br>3.6<br>4.0     | 0.48<br>0.53<br>0.63<br>0.80 | 1<br>1.1<br>1.2<br>1.4      | mA   |  |

| I <sub>DD</sub> | Supply current in Wait mode <sup>(2)</sup>         |                                                                                                                                                                                                                                                                               | 0.8<br>1.2<br>2.0<br>3.5  | 3.0<br>4.0<br>5.0<br>7.0     | 0.6<br>0.9<br>1.3<br>2.3     | 1.8<br>2.2<br>2.6<br>3.6    |      |  |

|                 | Supply current in Slow Wait<br>mode <sup>(2)</sup> | $      f_{OSC} = 2 \text{ MHz}, \  f_{CPU} = 62.5 \text{ kHz} \\       f_{OSC} = 4 \text{ MHz}, \  f_{CPU} = 125 \text{ kHz} \\       f_{OSC} = 8 \text{ MHz}, \  f_{CPU} = 250 \text{ kHz} \\       f_{OSC} = 16 \text{ MHz}, \  f_{CPU} = 500 \text{ kHz} $                 | 580<br>650<br>770<br>1050 | 1200<br>1300<br>1800<br>2000 | 430<br>470<br>530<br>660     | 950<br>1000<br>1050<br>1200 |      |  |

|                 | Supply current in Halt mode <sup>(3)</sup>         | $-40^{\circ}C \le T_A \le +85^{\circ}C$ $-40^{\circ}C \le T_A \le +125^{\circ}C$                                                                                                                                                                                              | <1<br>5                   | 10<br>50                     | <1<br><1                     | 10<br>50                    | μA   |  |

|                 | Supply current in Active-halt mode <sup>(4)</sup>  | $f_{OSC} = 2 \text{ MHz}$<br>$f_{OSC} = 4 \text{ MHz}$<br>$f_{OSC} = 8 \text{ MHz}$<br>$f_{OSC} = 16 \text{ MHz}$                                                                                                                                                             | 365<br>380<br>410<br>500  | 475<br>500<br>550<br>650     | 315<br>330<br>360<br>460     | 425<br>450<br>500<br>600    |      |  |

1. Data based on characterization results, tested in production at  $V_{\text{DD}}$  max. and  $f_{\text{CPU}}$  max.

Measurements are done in the following conditions:

Program executed from RAM, CPU running with RAM access. The increase in consumption when executing from Flash is

- Program executed from HAM, CPO furthing with HAW access. The increase in consumption when executing non-radii 50%. - All I/O pins in input mode with a static value at  $V_{DD}$  or  $V_{SS}$  (no load) - All peripherals in reset state - LVD disabled - Clock input (OSC1) driven by external square wave - In Slow and Slow Wait modes,  $f_{CPU}$  is based on  $f_{OSC}$  divided by 32 - To obtain the total current consumption of the device, add the clock source (*Section 12.6.3*) and the peripheral power consumption (*Section 12.5.4*) consumption (Section 12.5.4).

3. All I/O pins in push-pull 0 mode (when applicable) with a static value at  $V_{DD}$  or  $V_{SS}$  (no load), LVD disabled. Data based on characterization results, tested in production at  $V_{DD}$  max. and  $f_{CPU}$  max.

4. Data based on characterization results, not tested in production. All I/O pins in push-pull 0 mode (when applicable) with a static value at V<sub>DD</sub> or V<sub>SS</sub> (no load); clock input (OSC1) driven by external square wave, LVD disabled. To obtain the total current consumption of the device, add the clock source consumption (*Section 12.6.3*).

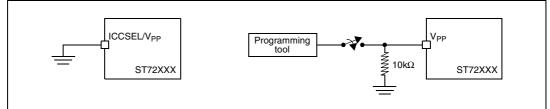

### 12.10.2 ICCSEL/V<sub>PP</sub> pin

Subject to general operating conditions for  $V_{DD}$ ,  $f_{CPU}$ , and  $T_A$  unless otherwise specified.

| Symbol           | Parameter                               | Conditions        | Min                   | Max                   | Unit |  |

|------------------|-----------------------------------------|-------------------|-----------------------|-----------------------|------|--|

| V <sub>IL</sub>  | Input low level voltage <sup>(1)</sup>  | Flash versions    | V <sub>SS</sub>       | 0.2                   |      |  |

|                  | Input low level voltage.                | ROM versions      | V <sub>SS</sub>       | 0.3 x V <sub>DD</sub> | V    |  |

| V <sub>IH</sub>  | Input high level voltage <sup>(1)</sup> | Flash versions    | V <sub>DD</sub> - 0.1 | 12.6                  | v    |  |

|                  | Input high level voltage.               | ROM versions      | 0.7 x V <sub>DD</sub> | V <sub>DD</sub>       |      |  |

| I <sub>lkg</sub> | Input leakage current                   | $V_{IN} = V_{SS}$ |                       | ±1                    | μA   |  |

Table 109. ICCSEL/V<sub>PP</sub> pin

1. Data based on design simulation and/or technology characteristics, not tested in production.

1. When ICC mode is not required by the application ICCSEL/V<sub>PP</sub> pin must be tied to V<sub>SS</sub>.

## 12.11 Timer peripheral characteristics

Subject to general operating conditions for  $V_{\text{DD}},\,f_{\text{OSC}},$  and  $T_{\text{A}}$  unless otherwise specified.

Refer to I/O port characteristics for more details on the input/output alternate function characteristics (output compare, input capture, external clock, PWM output...).

Data based on design simulation and/or characterization results, not tested in production.

### 12.11.1 16-bit timer

| Symbol                 | Parameter                      | Conditions               | Min | Тур | Max                 | Unit             |

|------------------------|--------------------------------|--------------------------|-----|-----|---------------------|------------------|

| t <sub>w(ICAP)in</sub> | Input capture pulse time       |                          | 1   |     |                     | t <sub>CPU</sub> |

| +                      | PWM resolution time            |                          | 2   |     |                     | t <sub>CPU</sub> |

| <sup>I</sup> res(PWM)  |                                | f <sub>CPU</sub> = 8 MHz | 250 |     |                     | ns               |

| f <sub>EXT</sub>       | Timer external clock frequency |                          | 0   |     | f. //               | MHz              |

| f <sub>PWM</sub>       | PWM repetition rate            |                          | 0   |     | f <sub>CPU</sub> /4 |                  |

| Res <sub>PWM</sub>     | PWM resolution                 |                          |     |     | 16                  | bit              |

#### Table 110. 16-bit timer

| Bit  | Name  | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |

|------|-------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| OPT0 | FMP_R | <ul> <li>Flash memory readout protection</li> <li>Readout protection, when selected, provides a protection against program memory content extraction and against write access to Flash memory.</li> <li>Erasing the option bytes when the FMP_R option is selected causes the whole user memory to be erased first, afterwhich the device can be reprogrammed. Refer to <i>Section 4.3.1 on page 24</i> and the <i>ST7 Flash Programming Reference Manual</i> for more details.</li> <li>0: Readout protection enabled</li> <li>1: Readout protection disabled</li> </ul> |  |

Table 120.

Option byte 0 bit description (continued)

#### Table 121. Option byte 1 bit description

| Bit    | Name          | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|--------|---------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| OPT7   | PKG1          | Pin package selection bit<br>This option bit selects the package (see <i>Table 122</i> ).<br>Note: On the chip, each I/O port has eight pads. Pads that are not<br>bonded to external pins are in input pull-up configuration after reset.<br>The configuration of these pads must be kept at reset state to avoid<br>added current consumption.                                                                                                                                               |

| OPT6   | RSTC          | <ul> <li>Reset clock cycle selection</li> <li>This option bit selects the number of CPU cycles applied during the reset phase and when exiting Halt mode. For resonator oscillators, it is advised to select 4096 due to the long crystal stabilization time.</li> <li>0: Reset phase with 4096 CPU cycles</li> <li>1: Reset phase with 256 CPU cycles</li> </ul>                                                                                                                              |

| OPT5:4 | OSCTYPE[1:0]  | Oscillator type<br>These option bits select the ST7 main clock source type.<br>00: Clock source = Resonator oscillator<br>01: Reserved<br>10: Clock source = Internal RC oscillator<br>11: Clock source = External source                                                                                                                                                                                                                                                                      |

| OPT3:1 | OSCRANGE[2:0] | Oscillator range<br>When the resonator oscillator type is selected, these option bits select<br>the resonator oscillator current source corresponding to the frequency<br>range of the used resonator. When the external clock source is<br>selected, these bits are set to medium power (2 ~ 4 MHz).<br>000: Typ. frequency range (LP) = 1 ~ 2 MHz<br>001: Typ. frequency range (MP) = 2 ~ 4 MHz<br>010: Typ. frequency range (MS) = 4 ~ 8 MHz<br>011: Typ. frequency range (HS) = 8 ~ 16 MHz |

Case 1: Writing to PxOR or PxDDR with global interrupts enabled:

```

LD A,#01

LD sema, A; set the semaphore to '1'

LD A, PFDR

AND A,#02

LD X,A; store the level before writing to PxOR/PxDDR

LD A,#$90

LD PFDDR, A ; Write to PFDDR

LD A,#$ff

LD PFOR, A ; Write to PFOR

LD A, PFDR

AND A, #02

LD Y,A; store the level after writing to PxOR/PxDDR

LD A,X; check for falling edge

cp A,#02

jrne OUT

TNZ Y

jrne OUT

LD A, sema ; check the semaphore status if edge is detected

CP A,#01

jrne OUT

call call_routine ; call the interrupt routine

OUT:LD A,#00

LD sema,A

.call_routine ; entry to call_routine

PUSH A

PUSH X

PUSH CC

.ext1_rt ; entry to interrupt routine

LD A,#00

LD sema,A

IRET

Case 2: Writing to PxOR or PxDDR with global interrupts disabled:

SIM ; set the interrupt mask

LD A, PFDR

AND A,#$02

LD X,A ; store the level before writing to PxOR/PxDDR

LD A,#$90

LD PFDDR, A ; Write into PFDDR

LD A,#$ff

LD PFOR, A ; Write to PFOR

LD A, PFDR

AND A,#$02

LD Y,A ; store the level after writing to PxOR/PxDDR

LD A,X ; check for falling edge

cp A,#$02

jrne OUT

TNZ Y

jrne OUT

LD A,#$01

LD sema, A ; set the semaphore to '1' if edge is detected

```

# 16 Revision history

| Table 126. | Document revision history |

|------------|---------------------------|

|------------|---------------------------|

| Date        | Revision | Changes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |

|-------------|----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| 05-May-2004 | 2.0      | Merged ST72F324 Flash with ST72324B ROM datasheet.<br>Vt POR max modified in <i>Section 12.4 on page 145</i><br>Added <i>Figure 79 on page 164</i><br>Modified V <sub>AREF</sub> min in <i>"10-bit ADC characteristics" on page 168</i><br>Modified I INJ for PB0 in <i>Section 12.9 on page 158</i><br>Added <i>"Clearing active interrupts outside interrupt routine" on page 187</i><br>Modified "32K ROM DEVICES ONLY" on page 165                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |

| 30-Mar-2005 | 3        | Removed Clock Security System (CSS) throughout document<br>Added notes on ST72F324B 8K/16K Flash devices in Table 27<br>Corrected MCO description in <i>Section 10.2 on page 69</i><br>Modified VtPOR in <i>Section 12.4 on page 145</i><br>Static current consumption modified in <i>Section 12.9 on page 158</i><br>Updated footnote and <i>Figure 78 on page 163</i> and <i>Figure 79 on page 164</i><br>Modified Soldering information in <i>Section 13.6</i><br>Updated <i>Section 14 on page 178</i><br>Added Table 27<br>Modified <i>Figure 8 on page 25</i> and note 4 in <i>"Flash program memory" on</i><br><i>page 23</i><br>Added limitation on ICC entry mode with 39 pulses to <i>"Known limitations"</i><br><i>on page 185</i><br>Added Section 16 on page 166 for ST72F324B 8K/16K Flash devices<br>Modified "Internal Sales Types on box label" in Table 29 on page 157 |  |

| 12-Sep-2005 | 4        | Removed notes related to ST72F324, refer to datasheet rev 3 for<br>specifications on older devices.<br>Note: This datasheet rev refers only to ST72F324B and ST72324B.<br>Changed character transmission procedure in <i>Section on page 112</i><br>Updated Vt POR max in <i>Section 12.4 on page 145</i><br>Updated Current Consumption for in <i>Section 12.5 on page 146</i><br>Added oscillator diagram and table to <i>Section 12.6.3 on page 150</i><br>Increased Data retention max. parameter in <i>Section 12.7.2 on page 154</i><br>Updated ordering Section 14.3 on page 155 and Section 14.5 on page<br>157<br>Updated Development tools <i>Section 14.3 on page 183</i><br>Added "external interrupt missed" in <i>Section 15.1 on page 185</i>                                                                                                                             |  |

| 06-Feb-2006 | 5        | <ul> <li>Added description of SICSR register at address 2Bh in <i>Table 3 on page 20</i></li> <li>Changed description on port PF2 to add internal pull-up in <i>Section 9.5.1 on page 63</i></li> <li>Highlighted note in SPI <i>"Master mode operation" on page 99</i></li> <li>Changed <i>"Static latch-up" on page 157</i></li> <li>Added note 5 on analog input static current consumption <i>"General characteristics" on page 158</i></li> <li>Updated notes in <i>"Thermal characteristics" on page 177</i></li> </ul>                                                                                                                                                                                                                                                                                                                                                            |  |