Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                                       |

|----------------------------|-----------------------------------------------------------------------|

| Product Status             | Obsolete                                                              |

| Core Processor             | ST7                                                                   |

| Core Size                  | 8-Bit                                                                 |

| Speed                      | 8MHz                                                                  |

| Connectivity               | SCI, SPI                                                              |

| Peripherals                | LVD, POR, PWM, WDT                                                    |

| Number of I/O              | 32                                                                    |

| Program Memory Size        | 32KB (32K x 8)                                                        |

| Program Memory Type        | FLASH                                                                 |

| EEPROM Size                | -                                                                     |

| RAM Size                   | 1K x 8                                                                |

| Voltage - Supply (Vcc/Vdd) | 3.8V ~ 5.5V                                                           |

| Data Converters            | A/D 12x10b                                                            |

| Oscillator Type            | Internal                                                              |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                     |

| Mounting Type              | Through Hole                                                          |

| Package / Case             | 42-SDIP (0.600", 15.24mm)                                             |

| Supplier Device Package    | -                                                                     |

| Purchase URL               | https://www.e-xfl.com/product-detail/stmicroelectronics/st72f324bj6b6 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

Contents ST72324Bxx

# **Contents**

| 1 | Desc  | cription  |                                      | 4 |

|---|-------|-----------|--------------------------------------|---|

| 2 | Pin e | descript  | tion15                               | 5 |

| 3 | Regi  | ister and | d memory map                         | 0 |

| 4 | Flas  | h progra  | am memory                            | 3 |

|   | 4.1   | Introdu   | uction                               | 3 |

|   | 4.2   | Main fe   | eatures 20                           | 3 |

|   | 4.3   | Structu   | ure                                  | 3 |

|   |       | 4.3.1     | Readout protection24                 | 4 |

|   | 4.4   | ICC in    | terface                              | 5 |

|   | 4.5   | ICP (in   | n-circuit programming)26             | 6 |

|   | 4.6   | IAP (in   | n-application programming)           | 6 |

|   | 4.7   | Relate    | d documentation                      | 6 |

|   |       | 4.7.1     | Flash Control/Status Register (FCSR) | 6 |

| 5 | Cent  | tral prod | cessing unit (CPU)27                 | 7 |

|   | 5.1   | Introdu   | uction 27                            | 7 |

|   | 5.2   | Main fe   | eatures 27                           | 7 |

|   | 5.3   | CPU re    | egisters                             | 7 |

|   |       | 5.3.1     | Accumulator (A)                      | 8 |

|   |       | 5.3.2     | Index registers (X and Y)            | 8 |

|   |       | 5.3.3     | Program counter (PC)                 | 8 |

|   |       | 5.3.4     | Condition Code register (CC)         | 8 |

|   |       | 5.3.5     | Stack Pointer register (SP)          | 0 |

| 6 | Sup   | ply, rese | et and clock management              | 1 |

|   | 6.1   | Introdu   | uction 3 <sup>-</sup>                | 1 |

|   | 6.2   | PLL (p    | hase locked loop)                    | 1 |

|   | 6.3   | Multi-o   | oscillator (MO)                      | 2 |

|   |       | 6.3.1     | External clock source                | 2 |

|   |       | 6.3.2     | Crystal/ceramic oscillators          | 3 |

ST72324Bxx Contents

|   |       | 6.3.3    | Internal RC oscillator                                |    |

|---|-------|----------|-------------------------------------------------------|----|

|   | 6.4   |          | sequence manager (RSM)                                |    |

|   |       | 6.4.1    | Asynchronous external RESET pin                       | 34 |

|   | 6.5   | Systen   | m integrity management (SI)                           | 36 |

|   |       | 6.5.1    | LVD (low voltage detector)                            | 36 |

|   |       | 6.5.2    | AVD (auxiliary voltage detector)                      | 37 |

|   |       | 6.5.3    | Low power modes                                       | 38 |

|   |       | 6.5.4    | Interrupts                                            |    |

|   | 6.6   | SI regi  | sters                                                 | 39 |

|   |       | 6.6.1    | System integrity (SI) control/status register (SICSR) | 39 |

| 7 | Inter | rupts .  |                                                       | 41 |

|   | 7.1   | Introdu  | uction                                                | 41 |

|   | 7.2   | Maskir   | ng and processing flow                                | 41 |

|   |       | 7.2.1    | Servicing pending interrupts                          | 42 |

|   |       | 7.2.2    | Different interrupt vector sources                    | 43 |

|   |       | 7.2.3    | Non-maskable sources                                  | 43 |

|   |       | 7.2.4    | Maskable sources                                      | 43 |

|   | 7.3   | Interru  | pts and low power modes                               | 44 |

|   | 7.4   | Concu    | rrent and nested management                           | 44 |

|   | 7.5   | Interru  | pt registers                                          | 45 |

|   |       | 7.5.1    | CPU CC register interrupt bits                        | 45 |

|   |       | 7.5.2    | Interrupt software priority registers (ISPRx)         | 46 |

|   | 7.6   | Extern   | al interrupts                                         | 48 |

|   |       | 7.6.1    | I/O port interrupt sensitivity                        | 48 |

|   |       | 7.6.2    | External interrupt control register (EICR)            | 49 |

| 8 | Pow   | er savin | ng modes                                              | 52 |

|   | 8.1   | Introdu  | uction                                                | 52 |

|   | 8.2   |          | node                                                  |    |

|   | 8.3   |          | node                                                  |    |

|   | 8.4   |          | -halt and Halt modes                                  |    |

|   | 0.4   | 8.4.1    | Active-halt mode                                      |    |

|   |       | 8.4.2    | Halt mode                                             |    |

|   |       |          |                                                       |    |

| 9 | I/O p | orts     | • • • • • • • • • • • • • • • • • • • •               | 58 |

ST72324Bxx Contents

|    |       | 10.3.7   | 16-bit timer registers           | 89  |

|----|-------|----------|----------------------------------|-----|

|    | 10.4  | Serial p | peripheral interface (SPI)       | 96  |

|    |       | 10.4.1   | Introduction                     | 96  |

|    |       | 10.4.2   | Main features                    | 96  |

|    |       | 10.4.3   | General description              | 97  |

|    |       | 10.4.4   | Clock phase and clock polarity   | 101 |

|    |       | 10.4.5   | Error flags                      |     |

|    |       | 10.4.6   | Low power modes                  | 104 |

|    |       | 10.4.7   | Interrupts                       | 104 |

|    |       | 10.4.8   | SPI registers                    | 104 |

|    | 10.5  | Serial o | communications interface (SCI)   | 108 |

|    |       | 10.5.1   | Introduction                     | 108 |

|    |       | 10.5.2   | Main features                    | 108 |

|    |       | 10.5.3   | General description              | 109 |

|    |       | 10.5.4   | Functional description           | 111 |

|    |       | 10.5.5   | Low power modes                  | 120 |

|    |       | 10.5.6   | Interrupts                       | 120 |

|    |       | 10.5.7   | SCI registers                    | 120 |

|    | 10.6  | 10-bit A | A/D converter (ADC)              | 128 |

|    |       | 10.6.1   | Introduction                     | 128 |

|    |       | 10.6.2   | Main features                    | 128 |

|    |       | 10.6.3   | Functional description           | 129 |

|    |       | 10.6.4   | Low power modes                  | 130 |

|    |       | 10.6.5   | Interrupts                       | 130 |

|    |       | 10.6.6   | ADC registers                    | 130 |

| 11 | Instr | uction s | set                              | 133 |

|    | 11.1  |          | ddressing modes                  |     |

|    |       | 11.1.1   | Inherent                         |     |

|    |       | 11.1.2   | Immediate                        |     |

|    |       | 11.1.3   | Direct                           |     |

|    |       | 11.1.4   | Indexed (no offset, short, long) |     |

|    |       | 11.1.5   | Indirect (short, long)           |     |

|    |       | 11.1.6   | Indirect indexed (short, long)   |     |

|    |       | 11.1.7   | Relative mode (direct, indirect) |     |

|    | 11.2  | Instruc  | tion groups                      |     |

|    |       |          |                                  |     |

ST72324Bxx Contents

|    | 12.10 | Control  | pin characteristics                     | 162 |

|----|-------|----------|-----------------------------------------|-----|

|    |       | 12.10.1  | Asynchronous RESET pin                  | 162 |

|    |       | 12.10.2  | ICCSEL/VPP pin                          | 165 |

|    | 12.11 | Timer p  | peripheral characteristics              | 165 |

|    |       | 12.11.1  | 16-bit timer                            | 165 |

|    | 12.12 | Commu    | unication interface characteristics     | 166 |

|    |       | 12.12.1  | Serial peripheral interface (SPI)       | 166 |

|    | 12.13 | 10-bit A | ADC characteristics                     | 168 |

|    |       | 12.13.1  | Analog power supply and reference pins  | 170 |

|    |       | 12.13.2  | General PCB design guidelines           | 170 |

|    |       | 12.13.3  | ADC accuracy                            | 171 |

| 13 | Packa | age cha  | racteristics                            | 172 |

|    | 13.1  | ECOPA    | NCK                                     | 172 |

|    | 13.2  | Packag   | je mechanical data                      | 172 |

|    |       | 13.2.1   | LQFP44 package mechanical data          | 172 |

|    |       | 13.2.2   | SDIP42 package mechanical data          | 173 |

|    |       | 13.2.3   | LQFP32 package mechanical data          | 174 |

|    |       | 13.2.4   | SDIP32 package mechanical data          | 175 |

|    | 13.3  | Therma   | al characteristics                      | 177 |

| 14 | Devic | e confi  | guration and ordering information       | 178 |

|    | 14.1  |          | levices                                 |     |

|    |       | 14.1.1   | Flash configuration                     | 179 |

|    | 14.2  | ROM d    | evices                                  | 181 |

|    |       | 14.2.1   | Transfer of customer code               | 181 |

|    | 14.3  | Develo   | pment tools                             | 183 |

|    |       | 14.3.1   | Introduction                            | 183 |

|    |       | 14.3.2   | Evaluation tools and starter kits       | 183 |

|    |       | 14.3.3   | Development and debugging tools         | 183 |

|    |       | 14.3.4   | Programming tools                       | 183 |

|    |       | 14.3.5   | Socket and emulator adapter information | 184 |

|    | 14.4  | ST7 Ap   | oplication notes                        | 184 |

| 15 | Know  | n limita | ations                                  | 185 |

|    | 15.1  | All Flas | sh and ROM devices                      | 185 |

|    |       |          |                                         |     |

# 4 Flash program memory

#### 4.1 Introduction

The ST7 dual voltage High Density Flash (HDFlash) is a non-volatile memory that can be electrically erased as a single block or by individual sectors and programmed on a byte-by-byte basis using an external V<sub>PP</sub> supply.

The HDFlash devices can be programmed and erased off-board (plugged in a programming tool) or on-board using ICP (in-circuit programming) or IAP (in-application programming).

The array matrix organization allows each sector to be erased and reprogrammed without affecting other sectors.

## 4.2 Main features

- 3 Flash programming modes:

- Insertion in a programming tool. In this mode, all sectors including option bytes can be programmed or erased.

- ICP (in-circuit programming). In this mode, all sectors including option bytes can be programmed or erased without removing the device from the application board.

- IAP (in-application programming). In this mode, all sectors, except Sector 0, can be programmed or erased without removing the device from the application board and while the application is running.

- ICT (in-circuit testing) for downloading and executing user application test patterns in RAM

- Readout protection

- Register Access Security System (RASS) to prevent accidental programming or erasing

#### 4.3 Structure

The Flash memory is organized in sectors and can be used for both code and data storage.

Depending on the overall Flash memory size in the microcontroller device, there are up to three user sectors (see *Table 4*). Each of these sectors can be erased independently to avoid unnecessary erasing of the whole Flash memory when only a partial erasing is required.

The first two sectors have a fixed size of 4 Kbytes (see *Figure 7*). They are mapped in the upper part of the ST7 addressing space so the reset and interrupt vectors are located in Sector 0 (F000h-FFFFh).

Table 4. Sectors available in Flash devices

| Flash size | Available sectors |

|------------|-------------------|

| 4 Kbytes   | Sector 0          |

| 8 Kbytes   | Sectors 0, 1      |

| >8 Kbytes  | Sectors 0, 1, 2   |

**57**

Table 6. Arithmetic management bits (continued)

| Blt | Name | Function                                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |

|-----|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| 1   | Z    | Zero (Arithmetic Management bit)  This bit is set and cleared by hardware. This bit indicates that the result of the last arithmetic, logical or data manipulation is zero.  0: The result of the last operation is different from zero.  1: The result of the last operation is zero.  This bit is accessed by the JREQ and JRNE test instructions.                                                                                   |  |  |

| 0   | С    | Carry/borrow  This bit is set and cleared by hardware and software. It indicates an overflow or an underflow has occurred during the last arithmetic operation.  0: No overflow or underflow has occurred.  1: An overflow or underflow has occurred.  This bit is driven by the SCF and RCF instructions and tested by the JRC and JRNC instructions. It is also affected by the 'bit test and branch', shift and rotate instructions |  |  |

Table 7. Software interrupt bits

| Blt | Name | Function                                                                                                                                       |  |

|-----|------|------------------------------------------------------------------------------------------------------------------------------------------------|--|

| 5   | I1   | Software Interrupt Priority 1  The combination of the I1 and I0 bits determines the current interrupt software priority (see <i>Table 8</i> ). |  |

| 3   | 10   | Software Interrupt Priority 0  The combination of the I1 and I0 bits determines the current interrupt software priority (see <i>Table 8</i> ). |  |

Table 8. Interrupt software priority selection

| Interrupt software priority   | Level | l1 | 10 |

|-------------------------------|-------|----|----|

| Level 0 (main)                | Low   | 1  | 0  |

| Level 1                       |       | 0  | 1  |

| Level 2                       | ↓     | 0  | 0  |

| Level 3 (= interrupt disable) | High  | 1  | 1  |

These two bits are set/cleared by hardware when entering in interrupt. The loaded value is given by the corresponding bits in the interrupt software priority registers (ISPRx). They can be also set/cleared by software with the RIM, SIM, IRET, HALT, WFI and PUSH/POP instructions.

See Section 7: Interrupts on page 41 for more details.

577

Interrupts ST72324Bxx

| Table 14. Interrupt software priorit |

|--------------------------------------|

|--------------------------------------|

| Interrupt software priority   | Level    | l1 | 10 |

|-------------------------------|----------|----|----|

| Level 0 (main)                | Low      | 1  | 0  |

| Level 1                       |          | 0  | 1  |

| Level 2                       | <b>↓</b> | 0  | 0  |

| Level 3 (= interrupt disable) | High     | 1  | 1  |

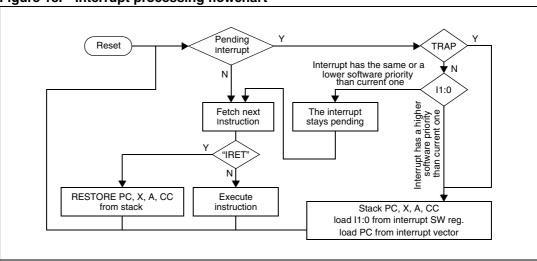

Figure 18. Interrupt processing flowchart

# 7.2.1 Servicing pending interrupts

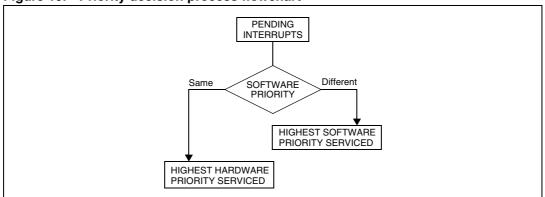

As several interrupts can be pending at the same time, the interrupt to be taken into account is determined by the following two-step process:

- the highest software priority interrupt is serviced,

- if several interrupts have the same software priority then the interrupt with the highest hardware priority is serviced first.

Figure 19 describes this decision process.

Figure 19. Priority decision process flowchart

Interrupts ST72324Bxx

Table 21. Interrupt sensitivity - ei3

| IS11 | IS10 | External interrupt sensitivity |  |

|------|------|--------------------------------|--|

| 0    | 0    | Falling edge and low level     |  |

| 0    | 1    | Rising edge only               |  |

| 1    | 0    | Falling edge only              |  |

| 1    | 1    | Rising and falling edge        |  |

Table 22. Interrupt sensitivity - ei0

| IS21 | IS20 | External interrupt sensitivity     |                            |  |  |  |

|------|------|------------------------------------|----------------------------|--|--|--|

| 1321 | 1320 | IPA bit = 0 IPA bit = 1            |                            |  |  |  |

| 0    | 0    | Falling edge and low level         | Rising edge and high level |  |  |  |

| 0    | 1    | Rising edge only Falling edge only |                            |  |  |  |

| 1    | 0    | Falling edge only Rising edge only |                            |  |  |  |

| 1    | 1    | Rising and falling edge            |                            |  |  |  |

Table 23. Interrupt sensitivity - ei1

| IS21 | IS20 | External interrupt sensitivity |

|------|------|--------------------------------|

| 0    | 0    | Falling edge and low level     |

| 0    | 1    | Rising edge only               |

| 1    | 0    | Falling edge only              |

| 1    | 1    | Rising and falling edge        |

Table 24. Nested interrupts register map and reset values

| Address (Hex.) | Register label       | 7          | 6          | 5          | 4          | 3          | 2          | 1          | 0          |

|----------------|----------------------|------------|------------|------------|------------|------------|------------|------------|------------|

|                |                      | ei1        |            | ei0        |            | MCC + SI   |            |            |            |

| 0024h          | ISPR0<br>reset value | I1_3<br>1  | I0_3<br>1  | l1_2<br>1  | 10_2<br>1  | I1_1<br>1  | I0_1<br>1  | 1          | 1          |

|                |                      | S          | PI         |            |            | е          | i3         | е          | i2         |

| 0025h          | ISPR1 reset value    | I1_7<br>1  | I0_7<br>1  | I1_6<br>1  | I0_6<br>1  | I1_5<br>1  | I0_5<br>1  | I1_4<br>1  | I0_4<br>1  |

|                |                      | AVD        |            | SCI        |            | Timer B    |            | Timer A    |            |

| 0026h          | ISPR2<br>reset value | l1_11<br>1 | I0_11<br>1 | I1_10<br>1 | I0_10<br>1 | I1_9<br>1  | I0_9<br>1  | I1_8<br>1  | I0_8<br>1  |

| 0027h          | ISPR3<br>reset value | 1          | 1          | 1          | 1          | l1_13<br>1 | I0_13<br>1 | l1_12<br>1 | 10_12<br>1 |

| 0028h          | EICR<br>reset value  | IS11<br>0  | IS10<br>0  | IPB<br>0   | IS21<br>0  | IS20<br>0  | IPA<br>0   | 0          | 0          |

ST72324Bxx Power saving modes

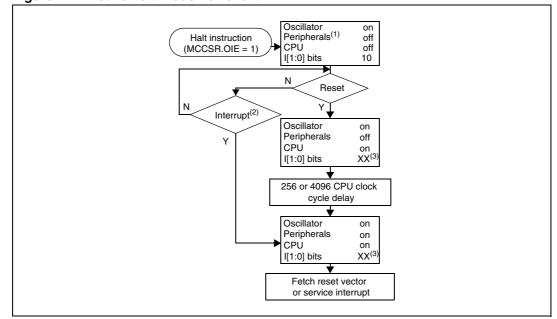

Figure 27. Active-halt mode flowchart

- 1. Peripheral clocked with an external clock source can still be active.

- 2. Only the MCC/RTC interrupt and some specific interrupts can exit the MCU from Active-halt mode (such as external interrupt). Refer to *Table 25: Interrupt mapping on page 51* for more details.

- 3. Before servicing an interrupt, the CC register is pushed on the stack. The I[1:0] bits of the CC register are set to the current software priority level of the interrupt routine and restored when the CC register is popped.

#### 8.4.2 Halt mode

The Halt mode is the lowest power consumption mode of the MCU. It is entered by executing the 'HALT' instruction when the OIE bit of the Main Clock Controller Status register (MCCSR) is cleared (see *Section 10.2: Main clock controller with real-time clock and beeper (MCC/RTC) on page 69* for more details on the MCCSR register).

The MCU can exit Halt mode on reception of either a specific interrupt (see *Table 25: Interrupt mapping*) or a reset. When exiting Halt mode by means of a reset or an interrupt, the oscillator is immediately turned on and the 256 or 4096 CPU cycle delay is used to stabilize the oscillator. After the start up delay, the CPU resumes operation by servicing the interrupt or by fetching the reset vector which woke it up (see *Figure 29*).

When entering Halt mode, the I[1:0] bits in the CC register are forced to '10b' to enable interrupts. Therefore, if an interrupt is pending, the MCU wakes up immediately.

In Halt mode, the main oscillator is turned off causing all internal processing to be stopped, including the operation of the on-chip peripherals. All peripherals are not clocked except the ones which get their clock supply from another clock generator (such as an external or auxiliary oscillator).

The compatibility of Watchdog operation with Halt mode is configured by the "WDGHALT" option bit of the option byte. The HALT instruction when executed while the Watchdog system is enabled, can generate a Watchdog reset (see *Section 14.1 on page 179*) for more details.

5/

On-chip peripherals ST72324Bxx

Reset f<sub>OSC2</sub> MCC/RTC Watchdog Control register (WDGCR) Div 64 T4 T2 ТЗ 6-bit downcounter (CNT) 12-bit MCC WDG prescaler RTC counter TB[1:0] bits div 4 (MCCSR register)

Figure 32. Watchdog block diagram

# 10.1.4 How to program the Watchdog timeout

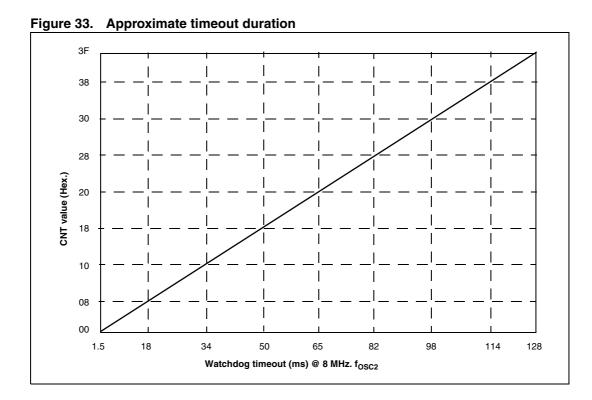

Figure 33 shows the linear relationship between the 6-bit value to be loaded in the Watchdog Counter (CNT) and the resulting timeout duration in milliseconds. This can be used for a quick calculation without taking the timing variations into account. If more precision is needed, use the formulae in Figure 34.

**Caution:** When writing to the WDGCR register, always write 1 in the T6 bit to avoid generating an immediate reset.

On-chip peripherals ST72324Bxx

Table 39. MCCSR register description (continued)

| Bit | Name    | Function                                                                                                                                                                                                                                                                                                                                                                                      |

|-----|---------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 6:5 | CP[1:0] | CPU Clock Prescaler  These bits select the CPU clock prescaler which is applied in different slow modes. Their action is conditioned by the setting of the SMS bit. These two bits are set and cleared by software:  00: $f_{CPU}$ in Slow mode = $f_{OSC2}/2$ 01: $f_{CPU}$ in Slow mode = $f_{OSC2}/4$ 10: $f_{CPU}$ in Slow mode = $f_{OSC2}/8$ 11: $f_{CPU}$ in Slow mode = $f_{OSC2}/16$ |

| 4   | SMS     | Slow Mode Select This bit is set and cleared by software. 0: Normal mode. f <sub>CPU</sub> = f <sub>OSC2</sub> . 1: Slow mode. f <sub>CPU</sub> is given by CP1, CP0. See Section 8.2: Slow mode and Section 10.2: Main clock controller with real-time clock and beeper (MCC/RTC) for more details.                                                                                          |

| 3:2 | TB[1:0] | Time Base control  These bits select the programmable divider time base. They are set and cleared by software (see <i>Table 40</i> ). A modification of the time base is taken into account at the end of the current period (previously set) to avoid an unwanted time shift. This allows to use this time base as a real-time clock.                                                        |

| 1   | OIE     | Oscillator interrupt Enable This bit set and cleared by software. 0: Oscillator interrupt disabled 1: Oscillator interrupt enabled This interrupt can be used to exit from Active-halt mode. When this bit is set, calling the ST7 software HALT instruction enters the Active-halt power saving mode.                                                                                        |

| 0   | OIF     | Oscillator interrupt Flag  This bit is set by hardware and cleared by software reading the MCCSR register. It indicates when set that the main oscillator has reached the selected elapsed time (TB1:0).  0: Timeout not reached 1: Timeout reached Caution: The BRES and BSET instructions must not be used on the MCCSR register to avoid unintentionally clearing the OIF bit.             |

Table 40. Time base selection

| Counter prescaler | Time                      | TB1                       | TB0 |     |

|-------------------|---------------------------|---------------------------|-----|-----|

| Counter prescaler | f <sub>OSC2</sub> = 4 MHz | f <sub>OSC2</sub> = 8 MHz | 161 | 100 |

| 16000             | 4 ms                      | 2 ms                      | 0   | 0   |

| 32000             | 8 ms                      | 4 ms                      | 0   | 1   |

| 80000             | 20 ms                     | 10 ms                     | 1   | 0   |

| 200000            | 50 ms                     | 25 ms                     | 1   | 1   |

The OC1R register value required for a specific timing application can be calculated using the following formula:

$$OCiR$$

value =  $\frac{t * f_{CPU}}{PRESC}$  - 5

Where:

t = Pulse period (in seconds)

f<sub>CPU</sub> = CPU clock frequency (in hertz)

PRESC = Timer prescaler factor (2, 4 or 8 depending on the CC[1:0] bits; see Table 50)

If the timer clock is an external clock the formula is:

$$OCiR = t * f_{EXT} - 5$$

Where:

t = Pulse period (in seconds)

f<sub>EXT</sub> = External timer clock frequency (in hertz)

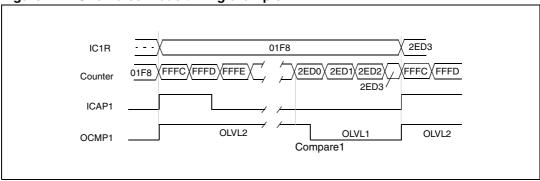

When the value of the counter is equal to the value of the contents of the OC1R register, the OLVL1 bit is output on the OCMP1 pin (see *Figure 47*).

Note:

- 1 The OCF1 bit cannot be set by hardware in one pulse mode but the OCF2 bit can generate an Output Compare interrupt.

- 2 When the Pulse Width Modulation (PWM) and One Pulse Mode (OPM) bits are both set, the PWM mode is the only active one.

- 3 If OLVL1 = OLVL2 a continuous signal will be seen on the OCMP1 pin.

- 4 The ICAP1 pin can not be used to perform input capture. The ICAP2 pin can be used to perform input capture (ICF2 can be set and IC2R can be loaded) but the user must take care that the counter is reset each time a valid edge occurs on the ICAP1 pin and ICF1 can also generates interrupt if ICIE is set.

- When one pulse mode is used OC1R is dedicated to this mode. Nevertheless OC2R and OCF2 can be used to indicate a period of time has been elapsed but cannot generate an output waveform because the level OLVL2 is dedicated to the one pulse mode.

Figure 47. One Pulse mode timing example<sup>(1)</sup>

1. IEDG1 = 1, OC1R = 2ED0h, OLVL1 = 0, OLVL2 = 1

ST72324Bxx On-chip peripherals

# 10.3.6 Summary of timer modes

Table 48. Summary of timer modes

|                               | Timer resources    |                                |                     |                          |  |  |  |

|-------------------------------|--------------------|--------------------------------|---------------------|--------------------------|--|--|--|

| Mode                          | Input<br>Capture 1 | Input<br>Capture 2             | Output<br>Compare 1 | Output<br>Compare 2      |  |  |  |

| Input Capture<br>(1 and/or 2) | V                  | V                              | V                   | V                        |  |  |  |

| Output Compare (1 and/or 2)   | Yes                | Yes                            | Yes                 | Yes                      |  |  |  |

| One Pulse mode                | No                 | Not recommended <sup>(1)</sup> | No                  | Partially <sup>(2)</sup> |  |  |  |

| PWM mode                      | No                 | Not recommended <sup>(3)</sup> | No                  | No                       |  |  |  |

- 1. See note 4 in One Pulse mode on page 84.

- 2. See note 5 in One Pulse mode on page 84.

- 3. See note 4 in Pulse Width Modulation mode on page 86.

## 10.3.7 16-bit timer registers

Each timer is associated with three control and status registers, and with six pairs of data registers (16-bit values) relating to the two input captures, the two output compares, the counter and the alternate counter.

## **Control Register 1 (CR1)**

CR1 Reset value: 0000 0000 (00h) 7 6 5 4 3 2 1 0 ICIE OCIE TOIE FOLV2 FOLV1 OLVL2 IEDG1 OLVL1 R/W R/W R/W R/W R/W R/W R/W R/W

Table 49. CR1 register description

| Bit | Name | Function                                                                                                                                                |

|-----|------|---------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7   | ICIE | Input Capture Interrupt Enable  0: Interrupt is inhibited.  1: A timer interrupt is generated whenever the ICF1 or ICF2 bit of the SR register is set.  |

| 6   | OCIE | Output Compare Interrupt Enable  0: Interrupt is inhibited.  1: A timer interrupt is generated whenever the OCF1 or OCF2 bit of the SR register is set. |

| 5   | TOIE | Timer Overflow Interrupt Enable 0: Interrupt is inhibited. 1: A timer interrupt is enabled whenever the TOF bit of the SR register is set.              |

89/193

ST72324Bxx On-chip peripherals

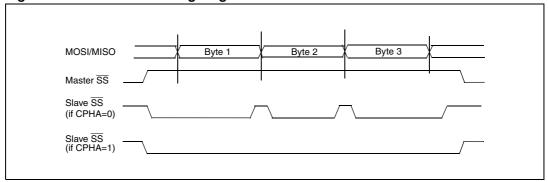

Figure 52. Generic SS timing diagram

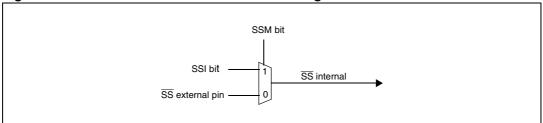

Figure 53. Hardware/software slave select management

#### Master mode operation

In master mode, the serial clock is output on the SCK pin. The clock frequency, polarity and phase are configured by software (refer to the description of the SPICSR register).

Note:

The idle state of SCK must correspond to the polarity selected in the SPICSR register (by pulling up SCK if CPOL = 1 or pulling down SCK if CPOL = 0).

### How to operate the SPI in master mode

To operate the SPI in master mode, perform the following steps in order:

- Write to the SPICR register:

- Select the clock frequency by configuring the SPR[2:0] bits.

- Select the clock polarity and clock phase by configuring the CPOL and CPHA bits.

Figure 54 shows the four possible configurations.

Note: The slave must have the same CPOL and CPHA settings as the master.

- 2. Write to the SPICSR register:

- Either set the SSM bit and set the SSI bit or clear the SSM bit and tie the SS pin high for the complete byte transmit sequence.

- 3. Write to the SPICR register:

- Set the MSTR and SPE bits.

Note: MSTR and SPE bits remain set only if SS is high.

Caution:

If the SPICSR register is not written first, the SPICR register setting (MSTR bit) might not be taken into account.

The transmit sequence begins when software writes a byte in the SPIDR register.

On-chip peripherals ST72324Bxx

#### 10.4.6 Low power modes

Table 53. Effect of low power modes on SPI

| Mode | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Wait | No effect on SPI.<br>SPI interrupt events cause the device to exit from Wait mode.                                                                                                                                                                                                                                                                                                                                                                                               |

| Halt | SPI registers are frozen. In Halt mode, the SPI is inactive. SPI operation resumes when the MCU is woken up by an interrupt with Exit from Halt mode capability. The data received is subsequently read from the SPIDR register when the software is running (interrupt vector fetching). If several data are received before the wakeup event, then an overrun error is generated. This error can be detected after the fetch of the interrupt routine that woke up the device. |

## Using the SPI to wake up the MCU from Halt mode

In slave configuration, the SPI is able to wake up the ST7 device from Halt mode through a SPIF interrupt. The data received is subsequently read from the SPIDR register when the software is running (interrupt vector fetch). If multiple data transfers have been performed before software clears the SPIF bit, then the OVR bit is set by hardware.

Note:

When waking up from Halt mode, if the SPI remains in Slave mode, it is recommended to perform an extra communications cycle to bring the SPI from Halt mode state to normal state. If the SPI exits from Slave mode, it returns to normal state immediately.

Caution:

The SPI can wake up the ST7 from Halt mode only if the Slave Select signal (external  $\overline{SS}$  pin or the SSI bit in the SPICSR register) is low when the ST7 enters Halt mode. Therefore, if Slave selection is configured as external (see <u>Slave select management on page 98</u>), make sure the master drives a low level on the  $\overline{SS}$  pin when the slave enters Halt mode.

#### 10.4.7 Interrupts

Table 54. SPI interrupt control/wakeup capability<sup>(1)</sup>

| Interrupt event           | Event flag | Enable control bit | Exit from Wait | Exit from Halt |  |

|---------------------------|------------|--------------------|----------------|----------------|--|

| SPI end of transfer event | SPIF       |                    |                | Yes            |  |

| Master mode fault event   | MODF       | SPIE               | Yes            | No             |  |

| Overrun error             | OVR        |                    |                | No             |  |

The SPI interrupt events are connected to the same interrupt vector (see <u>Section 7: Interrupts</u>). They

generate an interrupt if the corresponding Enable Control Bit is set and the interrupt mask in the CC

register is reset (RIM instruction).

#### 10.4.8 SPI registers

#### SPI control register (SPICR)

| SPICR Reset value: 0000 xxxx (0xh) |     |      |      |      |      |          |   |

|------------------------------------|-----|------|------|------|------|----------|---|

| 7                                  | 6   | 5    | 4    | 3    | 2    | 1        | 0 |

| SPIE                               | SPE | SPR2 | MSTR | CPOL | СРНА | SPR[1:0] |   |

| R/W                                | R/W | R/W  | R/W  | R/W  | R/W  | R/W      |   |

ST72324Bxx On-chip peripherals

- Parity control

- Transmits parity bit

- Checks parity of received data byte

- Reduced power consumption mode

## 10.5.3 General description

The interface is externally connected to another device by two pins (see *Figure 58*):

- TDO: Transmit Data Output. When the transmitter and the receiver are disabled, the

output pin returns to its I/O port configuration. When the transmitter and/or the receiver

are enabled and nothing is to be transmitted, the TDO pin is at high level.

- RDI: Receive Data Input is the serial data input. Oversampling techniques are used for data recovery by discriminating between valid incoming data and noise.

Through these pins, serial data is transmitted and received as frames comprising:

- an Idle Line prior to transmission or reception

- a start bit

- a data word (8 or 9 bits) least significant bit first

- a Stop bit indicating that the frame is complete

This interface uses two types of baud rate generator:

- a conventional type for commonly-used baud rates

- an extended type with a prescaler offering a very wide range of baud rates even with non-standard oscillator frequencies

109/193

On-chip peripherals ST72324Bxx

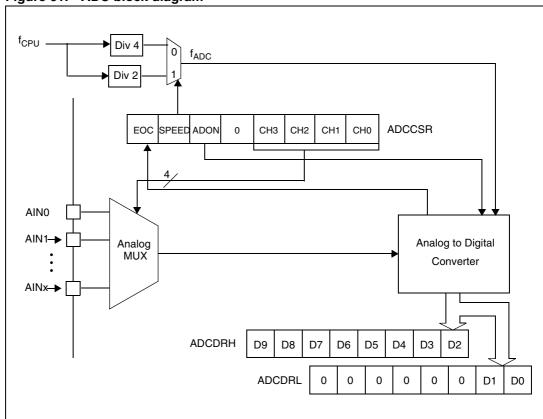

# 10.6 10-bit A/D converter (ADC)

#### 10.6.1 Introduction

The on-chip analog-to-digital converter (ADC) peripheral is a 10-bit, successive approximation converter with internal sample and hold circuitry. This peripheral has up to 16 multiplexed analog input channels (refer to device pin out description) that allow the peripheral to convert the analog voltage levels from up to 16 different sources.

The result of the conversion is stored in a 10-bit Data Register. The A/D converter is controlled through a Control/Status Register.

#### 10.6.2 Main features

- 10-bit conversion

- Up to 16 channels with multiplexed input

- Linear successive approximation

- Data register (DR) which contains the results

- Conversion complete status flag

- On/off bit (to reduce consumption)

The block diagram is shown in Figure 61.

Figure 61. ADC block diagram

#### 12.2.2 Current characteristics

Table 84. Current characteristics

| Symbol                                | Ratings                                                                 | Max value            | Unit  |  |

|---------------------------------------|-------------------------------------------------------------------------|----------------------|-------|--|

| l                                     | Total current into V <sub>DD</sub> power lines (source) <sup>(1)</sup>  |                      | 75    |  |

| I <sub>VDD</sub>                      | Total culterit into V <sub>DD</sub> power lines (source)                | 44-pin devices       | 150   |  |

|                                       | Total current out of V <sub>SS</sub> ground lines (sink) <sup>(1)</sup> | 32-pin devices       | 75    |  |

| I <sub>VSS</sub>                      | Total current out of V <sub>SS</sub> ground lines (Sink).               | 44-pin devices       | 150   |  |

|                                       | Output current sunk by any standard I/O and co                          | 20                   |       |  |

| I <sub>IO</sub>                       | Output current sunk by any high sink I/O pin                            | 40                   |       |  |

|                                       | Output current source by any I/Os and control p                         | - 25                 | mA    |  |

|                                       | Injected current on V <sub>PP</sub> pin                                 | ± 5                  | 111/4 |  |

|                                       | Injected current on RESET pin                                           | ± 5                  |       |  |

| I <sub>INJ(PIN)</sub> (2)(3)          | Injected current on OSC1 and OSC2 pins                                  | ± 5                  |       |  |

| INJ(PIN)` ^` /                        | Injected current on ROM and 32 Kbyte Flash de                           | ± 5                  |       |  |

|                                       | Injected current on 8/16 Kbyte Flash devices PE                         | + 5                  |       |  |

|                                       | Injected current on any other pin <sup>(4)(5)</sup>                     | ± 5                  |       |  |

| ΣI <sub>INJ(PIN)</sub> <sup>(2)</sup> | Total injected current (sum of all I/O and control                      | pins) <sup>(4)</sup> | ± 25  |  |

- 1. All power ( $V_{DD}$ ) and ground ( $V_{SS}$ ) lines must always be connected to the external supply.

- 2. I<sub>INJ(PIN)</sub> must never be exceeded. This is implicitly insured if V<sub>IN</sub> maximum is respected. If V<sub>IN</sub> maximum cannot be respected, the injection current must be limited externally to the I<sub>INJ(PIN)</sub> value. A positive injection is induced by V<sub>IN</sub> < V<sub>DD</sub> while a negative injection is induced by V<sub>IN</sub> < V<sub>SS</sub>. For true open-drain pads, there is no positive injection current, and the corresponding V<sub>IN</sub> maximum must always be respected.

- Negative injection degrades the analog performance of the device. See note in Section 12.13.3: ADC

accuracy on page 171. If the current injection limits given in Table 106: General characteristics on

page 158 are exceeded, general device malfunction may result.

- 4. When several inputs are submitted to a current injection, the maximum SI<sub>INJ(PIN)</sub> is the absolute sum of the positive and negative injected currents (instantaneous values). These results are based on characterization with SI<sub>INJ(PIN)</sub> maximum current injection on four I/O port pins of the device.

- 5. True open drain I/O port pins do not accept positive injection.

### 12.2.3 Thermal characteristics

Table 85. Thermal characteristics

| Symbol           | Ratings                                                                  | Value       | Unit |  |  |

|------------------|--------------------------------------------------------------------------|-------------|------|--|--|

| T <sub>STG</sub> | Storage temperature range                                                | -65 to +150 | °C   |  |  |

| TJ               | Maximum junction temperature (see Section 13.3: Thermal characteristics) |             |      |  |  |

# 12.4 LVD/AVD characteristics

# 12.4.1 Operating conditions with LVD

Subject to general operating conditions for  $T_A$ .

Table 87. Operating conditions with LVD

| Symbol                | Parameter                                               | Conditions                                    | Min                 | Тур  | Max                 | Unit |  |

|-----------------------|---------------------------------------------------------|-----------------------------------------------|---------------------|------|---------------------|------|--|

| V <sub>IT+(LVD)</sub> | Reset release threshold (V <sub>DD</sub> rise)          | VD level = high in option byte                | 4.0 <sup>(1)</sup>  | 4.2  | 4.5                 |      |  |

|                       |                                                         | VD level = med. in option byte <sup>(2)</sup> | 3.55 <sup>(1)</sup> | 3.75 | 4.0 <sup>(1)</sup>  |      |  |

|                       |                                                         | VD level = low in option byte <sup>(2)</sup>  | 2.95 <sup>(1)</sup> | 3.15 | 3.35 <sup>(1)</sup> | V    |  |

| V <sub>IT-(LVD)</sub> | Reset generation threshold (V <sub>DD</sub> fall)       | VD level = high in option byte                | 3.8                 | 4.0  | 4.25 <sup>(1)</sup> |      |  |

|                       |                                                         | VD level = med. in option byte <sup>(2)</sup> | 3.35 <sup>(1)</sup> | 3.55 | 3.75 <sup>(1)</sup> |      |  |

|                       |                                                         | VD level = low in option byte <sup>(2)</sup>  | 2.8 <sup>(1)</sup>  | 3.0  | 3.15 <sup>(1)</sup> |      |  |

| V <sub>hys(LVD)</sub> | LVD voltage threshold hysteresis <sup>(1)</sup>         | V <sub>IT+(LVD)</sub> -V <sub>IT-(LVD)</sub>  | 150                 | 200  | 250                 | mV   |  |

| Vt <sub>POR</sub>     | V <sub>DD</sub> rise time <sup>(1)</sup>                | Flash devices                                 |                     |      | 100ms/V             |      |  |

|                       |                                                         | 8/16 Kbyte ROM devices                        | 6µs/V               |      | 20ms/V              |      |  |

|                       |                                                         | 32 Kbyte ROM devices                          |                     |      | ∞ ms/V              |      |  |

| t <sub>g(VDD)</sub>   | Filtered glitch delay on V <sub>DD</sub> <sup>(1)</sup> | Not detected by the LVD                       |                     |      | 40                  | ns   |  |

<sup>1.</sup> Data based on characterization results, tested in production for ROM devices only.

## 12.4.2 Auxiliary voltage detector (AVD) thresholds

Subject to general operating conditions for  $T_A$ .

Table 88. AVD thresholds

| Symbol                | Parameter                                                           | Conditions                                                   | Min                 | Тур  | Max                 | Unit |  |

|-----------------------|---------------------------------------------------------------------|--------------------------------------------------------------|---------------------|------|---------------------|------|--|

| V <sub>IT+(AVD)</sub> | 1 ⇒0 AVDF flag toggle threshold (V <sub>DD</sub> rise)              | VD level = high in option byte                               | 4.4 <sup>(1)</sup>  | 4.6  | 4.9                 |      |  |

|                       |                                                                     | VD level = med. in option byte                               | 3.95 <sup>(1)</sup> | 4.15 | 4.4 <sup>(1)</sup>  |      |  |

|                       |                                                                     | VD level = low in option byte                                | 3.4 <sup>(1)</sup>  | 3.6  | 3.8 <sup>(1)</sup>  | V    |  |

| V <sub>IT-(AVD)</sub> | $0 \Rightarrow 1$ AVDF flag toggle threshold (V <sub>DD</sub> fall) | VD level = high in option byte                               | 4.2                 | 4.4  | 4.65 <sup>(1)</sup> | V    |  |

|                       |                                                                     | VD level = med. in option byte                               | 3.75 <sup>(1)</sup> | 4.0  | 4.2 <sup>(1)</sup>  |      |  |

|                       |                                                                     | VD level = low in option byte                                | 3.2 <sup>(1)</sup>  | 3.4  | 3.6 <sup>(1)</sup>  |      |  |

| V <sub>hys(AVD)</sub> | AVD voltage threshold hysteresis                                    | V <sub>IT+(AVD)</sub> -V <sub>IT-(AVD)</sub> 200             |                     |      |                     |      |  |

| ΔV <sub>IT-</sub>     | Voltage drop between AVD flag set and LVD reset activated           | ·   V = (\(\lambda\tau_D\) = V = (\(\lambda\tau_D\)   1 45() |                     | 450  |                     | mV   |  |

<sup>1.</sup> Data based on characterization results, tested in production for ROM devices only.

577

<sup>2.</sup> If the medium or low thresholds are selected, the detection may occur outside the specified operating voltage range.

**Emulation Programming** Supported ST7 DVP3 series ST7 EMU3 series products ICC socket **Active probe** board **Emulator Connection kit Emulator** and TEB ST72324BJ, ST7MDT20-ST72F324BJ T44/DVP ST7MDT20-ST7SB20J/xx<sup>(1)</sup> ST7MDT20J-TEB ST7MDT20J-EMU3 DVP3 ST72324BK, ST7MDT20-

Table 123. STMicroelectronics development tools

## 14.3.5 Socket and emulator adapter information

T32/DVP

For information on the type of socket that is supplied with the emulator, refer to the suggested list of sockets in *Table 124*.

Note:

ST72F324BK

Before designing the board layout, it is recommended to check the overall dimensions of the socket as they may be greater than the dimensions of the device.

For footprint and other mechanical information about these sockets and adapters, refer to the manufacturer's datasheet (www.yamaichi.de for LQFP44 10x10 and www.ironwoodelectronics.com for LQFP32 7x7).

Table 124. Suggested list of socket types

| Device       | Socket<br>(supplied with ST7MDT20J-EMU3) | Emulator adapter (supplied with ST7MDT20J-EMU3) |

|--------------|------------------------------------------|-------------------------------------------------|

| LQFP32 7X7   | IRONWOOD SF-QFE32SA-L-01                 | IRONWOOD SK-UGA06/32A-01                        |

| LQFP44 10X10 | YAMAICHI IC149-044-*52-*5                | YAMAICHI ICP-044-5                              |

# 14.4 ST7 Application notes

All relevant ST7 application notes can be found on www.st.com.

<sup>1.</sup> Add suffix /EU, /UK, /US for the power supply of your region.