#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Obsolete                                                              |

|----------------------------|-----------------------------------------------------------------------|

| Core Processor             | ST7                                                                   |

| Core Size                  | 8-Bit                                                                 |

| Speed                      | 8MHz                                                                  |

| Connectivity               | SCI, SPI                                                              |

| Peripherals                | LVD, POR, PWM, WDT                                                    |

| Number of I/O              | 24                                                                    |

| Program Memory Size        | 8KB (8K x 8)                                                          |

| Program Memory Type        | FLASH                                                                 |

| EEPROM Size                | -                                                                     |

| RAM Size                   | 384 x 8                                                               |

| Voltage - Supply (Vcc/Vdd) | 3.8V ~ 5.5V                                                           |

| Data Converters            | A/D 12x10b                                                            |

| Oscillator Type            | Internal                                                              |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                     |

| Mounting Type              | Through Hole                                                          |

| Package / Case             | 32-SDIP (0.400", 10.16mm)                                             |

| Supplier Device Package    | -                                                                     |

| Purchase URL               | https://www.e-xfl.com/product-detail/stmicroelectronics/st72f324bk2b6 |

|                            |                                                                       |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| Table 49.   | CR1 register description                                                   | 80  |

|-------------|----------------------------------------------------------------------------|-----|

| Table 50.   | CR2 register description                                                   |     |

| Table 51.   | CSR register description                                                   |     |

| Table 52.   | 16-bit timer register map and reset values                                 |     |

| Table 53.   | Effect of low power modes on SPI                                           |     |

| Table 54.   | SPI interrupt control/wakeup capability.                                   |     |

| Table 55.   | SPICR register description                                                 |     |

| Table 56.   | SPI master mode SCK frequency.                                             |     |

| Table 57.   | SPICSR register description                                                |     |

| Table 58.   | SPI register map and reset values                                          |     |

| Table 59.   | Frame formats                                                              |     |

| Table 60.   | Effect of low power modes on SCI                                           |     |

| Table 61.   | SCI interrupt control/wakeup capability                                    |     |

| Table 62.   | SCISR register description                                                 |     |

| Table 63.   | SCICR1 register description                                                |     |

| Table 64.   | SCICR2 register description                                                |     |

| Table 65.   | SCIBRR register description                                                |     |

| Table 66.   | SCIERPR register description                                               |     |

| Table 66.   | - · · ·                                                                    |     |

| Table 67.   | SCIETPR register description.                                              |     |

| Table 68.   |                                                                            |     |

| Table 70.   | SCI register map and reset values                                          |     |

|             |                                                                            |     |

| Table 71.   | ADCCSR register description                                                |     |

| Table 72.   |                                                                            |     |

| Table 73.   | ADC register description                                                   |     |

| Table 74.   | ADC register map and reset values                                          |     |

| Table 75.   | Addressing mode groups                                                     |     |

| Table 76.   | CPU addressing mode overview                                               |     |

| Table 77.   |                                                                            |     |

| Table 78.   | Immediate instructions                                                     | 135 |

| Table 79.   | Instructions supporting direct, indexed, indirect and indirect indexed     | 100 |

| Table 00    | addressing modes                                                           |     |

| Table 80.   |                                                                            |     |

| Table 81.   | Instruction groups                                                         |     |

| Table 82.   | Instruction set overview                                                   |     |

| Table 83.   | Voltage characteristics                                                    |     |

| Table 84.   | Current characteristics                                                    |     |

| Table 85.   | Thermal characteristics.                                                   |     |

| Table 86.   | Operating conditions.                                                      |     |

| Table 87.   | Operating conditions with LVD                                              |     |

| Table 88.   | AVD thresholds                                                             |     |

| Table 89.   | ROM current consumption                                                    |     |

| Table 90.   | Flash current consumption                                                  |     |

| Table 91.   | Oscillators, PLL and LVD current consumption                               |     |

| Table 92.   | On-chip peripherals current consumption                                    |     |

| Table 93.   | General timings.                                                           |     |

| Table 94.   | External clock source                                                      | 149 |

| Table 95.   | Crystal and ceramic resonator oscillators (8/16 Kbyte Flash and ROM        | 450 |

| T. 1. 1. 00 |                                                                            |     |

| Table 96.   | Crystal and ceramic resonator oscillators (32 Kbyte Flash and ROM devices) |     |

| Table 97.   | OSCRANGE selection for typical resonators                                  |     |

| Table 98.   | RC oscillators                                                             | 152 |

5

## 5.3.5 Stack Pointer register (SP)

| SP  | SP Reset value: 01 FF |     |     |     |     |     |     | 1 FFh |     |     |     |     |     |     |     |

|-----|-----------------------|-----|-----|-----|-----|-----|-----|-------|-----|-----|-----|-----|-----|-----|-----|

| 15  | 14                    | 13  | 12  | 11  | 10  | 9   | 8   | 7     | 6   | 5   | 4   | 3   | 2   | 1   | 0   |

| 0   | 0                     | 0   | 0   | 0   | 0   | 0   | 1   | SP7   | SP6 | SP5 | SP4 | SP3 | SP2 | SP1 | SP0 |

| R/W | R/W                   | R/W | R/W | R/W | R/W | R/W | R/W | R/W   | R/W | R/W | R/W | R/W | R/W | R/W | R/W |

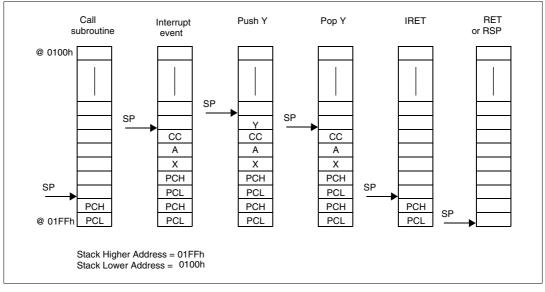

The Stack Pointer is a 16-bit register which is always pointing to the next free location in the stack. It is then decremented after data has been pushed onto the stack and incremented before data is popped from the stack (see *Figure 10*).

Since the stack is 256 bytes deep, the 8 most significant bits are forced by hardware. Following an MCU reset, or after a Reset Stack Pointer instruction (RSP), the Stack Pointer contains its reset value (the SP7 to SP0 bits are set) which is the stack higher address.

The least significant byte of the Stack Pointer (called S) can be directly accessed by an LD instruction.

Note: When the lower limit is exceeded, the Stack Pointer wraps around to the stack upper limit, without indicating the stack overflow. The previously stored information is then overwritten and therefore lost. The stack also wraps in case of an underflow.

The stack is used to save the return address during a subroutine call and the CPU context during an interrupt. The user may also directly manipulate the stack by means of the PUSH and POP instructions. In the case of an interrupt, the PCL is stored at the first location pointed to by the SP. Then the other registers are stored in the next locations as shown in *Figure 10*.

- When an interrupt is received, the SP is decremented and the context is pushed on the stack.

- On return from interrupt, the SP is incremented and the context is popped from the stack.

A subroutine call occupies two locations and an interrupt five locations in the stack area.

#### Figure 10. Stack manipulation example

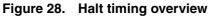

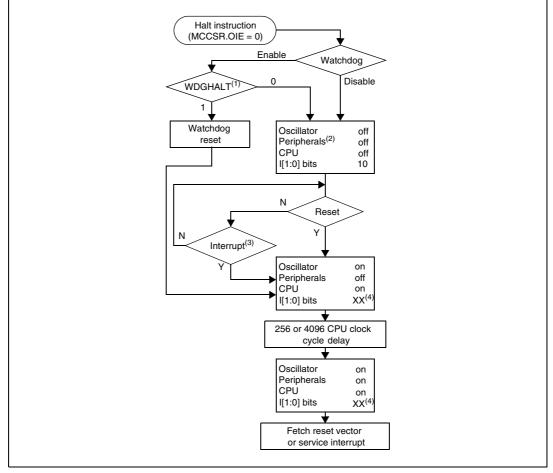

- 1. WDGHALT is an option bit. See *Section 14.1 on page 179* for more details.

- 2. Peripheral clocked with an external clock source can still be active.

- 3. Only some specific interrupts can exit the MCU from Halt mode (such as external interrupt). Refer to *Table 25: Interrupt mapping* for more details.

- Before servicing an interrupt, the CC register is pushed on the stack. The I[1:0] bits of the CC register are set to the current software priority level of the interrupt routine and recovered when the CC register is popped.

#### Analog alternate function

When the pin is used as an ADC input, the I/O must be configured as floating input. The analog multiplexer (controlled by the ADC registers) switches the analog voltage present on the selected pin to the common analog rail which is connected to the ADC input.

It is recommended not to change the voltage level or loading on any port pin while conversion is in progress. Furthermore it is recommended not to have clocking pins located close to a selected analog pin.

Warning: The analog input voltage level must be within the limits stated in the absolute maximum ratings.

## 9.3 I/O port implementation

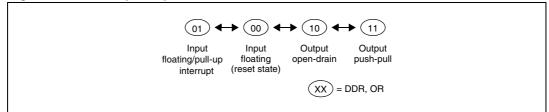

The hardware implementation on each I/O port depends on the settings in the DDR and OR registers and specific feature of the I/O port such as ADC Input or true open drain.

Switching these I/O ports from one state to another should be done in a sequence that prevents unwanted side effects. Recommended safe transitions are illustrated in *Figure 31*. Other transitions are potentially risky and should be avoided, since they are likely to present unwanted side-effects such as spurious interrupt generation.

#### Figure 31. Interrupt I/O port state transitions

## 9.4 Low power modes

#### Table 30. Effect of low power modes on I/O ports

| Mode | Description                                                                          |

|------|--------------------------------------------------------------------------------------|

| Wait | No effect on I/O ports. External interrupts cause the device to exit from Wait mode. |

| Halt | No effect on I/O ports. External interrupts cause the device to exit from Halt mode. |

## 9.5 Interrupts

The external interrupt event generates an interrupt if the corresponding configuration is selected with DDR and OR registers and the interrupt mask in the CC register is not active (RIM instruction).

## 10.1.5 Low power modes

| Mode |                              |                               | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |  |  |  |

|------|------------------------------|-------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| Slow | No effect on Watchdog        |                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |  |  |

| Wait | No effect on Watchdog        |                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |  |  |

|      | OIE bit in<br>MCCSR register | WDGHALT bit in<br>option byte |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |  |  |

| Halt | 0                            | 0                             | No Watchdog reset is generated. The MCU enters<br>Halt mode. The Watchdog counter is decremented<br>once and then stops counting and is no longer able to<br>generate a watchdog reset until the MCU receives an<br>external interrupt or a reset.<br>If an external interrupt is received, the Watchdog<br>restarts counting after 256 or 4096 CPU clocks. If a<br>reset is generated, the Watchdog is disabled (reset<br>state) unless Hardware Watchdog is selected by<br>option byte. For application recommendations, see<br><i>Section 10.1.7</i> below. |  |  |  |  |  |

|      | 0                            | 1                             | A reset is generated.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |  |  |  |  |

|      | 1                            | x                             | No reset is generated. The MCU enters Active-halt<br>mode. The Watchdog counter is not decremented. It<br>stop counting. When the MCU receives an oscillator<br>interrupt or external interrupt, the Watchdog restarts<br>counting immediately. When the MCU receives a<br>reset the Watchdog restarts counting after 256 or<br>4096 CPU clocks.                                                                                                                                                                                                               |  |  |  |  |  |

#### Table 34. Effect of lower power modes on Watchdog

## 10.1.6 Hardware Watchdog option

If Hardware Watchdog is selected by option byte, the watchdog is always active and the WDGA bit in the WDGCR is not used. Refer to the option byte description in *Section 14.1: Flash devices*.

## 10.1.7 Using Halt mode with the WDG (WDGHALT option)

The following recommendation applies if Halt mode is used when the watchdog is enabled: Before executing the HALT instruction, refresh the WDG counter to avoid an unexpected WDG reset immediately after waking up the microcontroller.

## 10.1.8 Interrupts

None.

If the timer clock is an external clock, the formula is:

$$\Delta \text{ OC}i\text{R} = \Delta t \star f_{\text{EXT}}$$

Where:

Clearing the output compare interrupt request (that is, clearing the OCF*i* bit) is done by:

- 1. Reading the SR register while the OCF*i* bit is set.

- 2. An access (read or write) to the OCiLR register.

The following procedure is recommended to prevent the OCF*i* bit from being set between the time it is read and the write to the OC*i*R register:

- Write to the OC*i*HR register (further compares are inhibited).

- Read the SR register (first step of the clearance of the OCF*i* bit, which may be already set).

- Write to the OC*i*LR register (enables the output compare function and clears the OCF*i* bit).

- Note: 1 After a processor write cycle to the OCiHR register, the output compare function is inhibited until the OCiLR register is also written.

- 2 If the OCiE bit is not set, the OCMPi pin is a general I/O port and the OLVLi bit will not appear when a match is found but an interrupt could be generated if the OCIE bit is set.

- 3 In both internal and external clock modes, OCFi and OCMPi are set while the counter value equals the OCiR register value (see Figure 44 on page 83 for an example with f<sub>CPU</sub>/2 and Figure 45 on page 83 for an example with f<sub>CPU</sub>/4). This behavior is the same in OPM or PWM mode.

- 4 The output compare functions can be used both for generating external events on the OCMPi pins even if the input capture mode is also used.

- 5 The value in the 16-bit OCiR register and the OLVi bit should be changed after each successful comparison in order to control an output waveform or establish a new elapsed timeout.

#### Forced output compare capability

When the FOLV*i* bit is set by software, the OLVL*i* bit is copied to the OCMP*i* pin. The OLV*i* bit has to be toggled in order to toggle the OCMP*i* pin when it is enabled (OC*i*E bit = 1). The OCF*i* bit is then not set by hardware, and thus no interrupt request is generated.

The FOLVL*i* bits have no effect in both one pulse mode and PWM mode.

| Bit | Name     | Function                                                                                                                                                                                                                                                                                                                                                                                                                            |

|-----|----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7   | SPIE     | <ul> <li>Serial Peripheral Interrupt Enable</li> <li>This bit is set and cleared by software.</li> <li>0: Interrupt is inhibited.</li> <li>1: An SPI interrupt is generated whenever SPIF = 1, MODF = 1 or OVR = 1 in the SPICSR register.</li> </ul>                                                                                                                                                                               |

| 6   | SPE      | <ul> <li>Serial Peripheral Output Enable</li> <li>This bit is set and cleared by software. It is also cleared by hardware when, in master mode, SS = 0 (see <i>Master mode fault (MODF) on page 102</i>). The SPE bit is cleared by reset, so the SPI peripheral is not initially connected to the external pins.</li> <li>0: I/O pins free for general purpose I/O</li> <li>1: SPI I/O pin alternate functions enabled</li> </ul>  |

| 5   | SPR2     | Divider Enable<br>This bit is set and cleared by software and is cleared by reset. It is used with the<br>SPR[1:0] bits to set the baud rate. Refer to <i>Table 56: SPI master mode SCK</i><br><i>frequency</i> .<br>0: Divider by 2 enabled<br>1: Divider by 2 disabled<br><i>Note: This bit has no effect in slave mode.</i>                                                                                                      |

| 4   | MSTR     | <ul> <li>Master mode</li> <li>This bit is set and cleared by software. It is also cleared by hardware when, in master mode, SS = 0 (see <i>Master mode fault (MODF) on page 102</i>).</li> <li>0: Slave mode</li> <li>1: Master mode. The function of the SCK pin changes from an input to an output and the functions of the MISO and MOSI pins are reversed.</li> </ul>                                                           |

| 3   | CPOL     | <ul> <li>Clock Polarity</li> <li>This bit is set and cleared by software. This bit determines the idle state of the serial Clock. The CPOL bit affects both the master and slave modes.</li> <li>0: SCK pin has a low level idle state</li> <li>1: SCK pin has a high level idle state</li> <li><i>Note: If CPOL is changed at the communication byte boundaries, the SPI must be disabled by resetting the SPE bit.</i></li> </ul> |

| 2   | СРНА     | <ul> <li>Clock Phase</li> <li>This bit is set and cleared by software.</li> <li>0: The first clock transition is the first data capture edge.</li> <li>1: The second clock transition is the first capture edge.</li> <li>Note: The slave must have the same CPOL and CPHA settings as the master.</li> </ul>                                                                                                                       |

| 1:0 | SPR[1:0] | Serial clock frequency<br>These bits are set and cleared by software. Used with the SPR2 bit, they select<br>the baud rate of the SPI serial clock SCK output by the SPI in master mode<br>(see <i>Table 56</i> ).<br><i>Note: These 2 bits have no effect in slave mode.</i>                                                                                                                                                       |

Table 55. SPICR register description

## Table 56. SPI master mode SCK frequency

| Serial clock        | SPR2 | SPR1 | SPR0 |

|---------------------|------|------|------|

| f <sub>CPU</sub> /4 | 1    | 0    | 0    |

| f <sub>CPU</sub> /8 | 0    | 0    | 0    |

| Serial clock          | SPR2 | SPR1 | SPR0 |  |  |  |  |

|-----------------------|------|------|------|--|--|--|--|

| f <sub>CPU</sub> /16  | 0    | 0    | 1    |  |  |  |  |

| f <sub>CPU</sub> /32  | 1    | 1    | 0    |  |  |  |  |

| f <sub>CPU</sub> /64  | 0    | 1    | 0    |  |  |  |  |

| f <sub>CPU</sub> /128 | 0    | 1    | 1    |  |  |  |  |

Table 56.

SPI master mode SCK frequency (continued)

## SPI control/status register (SPICSR)

| SPICSR |      |     |      |          | Rese | et value: 0000 | 0000 (00h) 0000 |

|--------|------|-----|------|----------|------|----------------|-----------------|

| 7      | 6    | 5   | 4    | 3        | 2    | 1              | 0               |

| SPIF   | WCOL | OVR | MODF | Reserved | SOD  | SSM            | SSI             |

| RO     | RO   | RO  | RO   | -        | R/W  | R/W            | R/W             |

## Table 57.SPICSR register description

| Bit | Name | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|-----|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7   | SPIF | <ul> <li>Serial peripheral data transfer flag</li> <li>This bit is set by hardware when a transfer has been completed. An interrupt is generated if SPIE = 1 in the SPICR register. It is cleared by a software sequence (an access to the SPICSR register followed by a write or a read to the SPIDR register).</li> <li>0: Data transfer is in progress or the flag has been cleared</li> <li>1: Data transfer between the device and an external device has been completed. <i>Note: While the SPIF bit is set, all writes to the SPIDR register are inhibited until the SPICSR register is read.</i></li> </ul> |

| 6   | WCOL | <ul> <li>Write collision status</li> <li>This bit is set by hardware when a write to the SPIDR register is done during a transmit sequence. It is cleared by a software sequence (see <i>Figure 55</i>).</li> <li>0: No write collision occurred</li> <li>1: A write collision has been detected.</li> </ul>                                                                                                                                                                                                                                                                                                        |

| 5   | OVR  | <ul> <li>SPI Overrun error</li> <li>This bit is set by hardware when the byte currently being received in the shift register is ready to be transferred into the SPIDR register while SPIF = 1 (see <i>Overrun condition (OVR) on page 102</i>). An interrupt is generated if SPIE = 1 in SPICR register. The OVR bit is cleared by software reading the SPICSR register.</li> <li>0: No overrun error</li> <li>1: Overrun error detected</li> </ul>                                                                                                                                                                |

| 4   | MODF | <ul> <li>Mode fault flag</li> <li>This bit is set by hardware when the SS pin is pulled low in master mode (see <i>Master mode fault (MODF) on page 102</i>). An SPI interrupt can be generated if SPIE = 1 in the SPICSR register. This bit is cleared by a software sequence (An access to the SPICR register while MODF = 1 followed by a write to the SPICR register).</li> <li>0: No master mode fault detected</li> <li>1: A fault in master mode has been detected.</li> </ul>                                                                                                                               |

| 3   | -    | Reserved, must be kept cleared.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

#### **Clock deviation causes**

The causes which contribute to the total deviation are:

- D<sub>TRA</sub>: Deviation due to transmitter error (local oscillator error of the transmitter or the transmitter is transmitting at a different baud rate).

- D<sub>QUANT</sub>: Error due to the baud rate quantization of the receiver.

- D<sub>REC</sub>: Deviation of the local oscillator of the receiver: This deviation can occur during the reception of one complete SCI message assuming that the deviation has been compensated at the beginning of the message.

- D<sub>TCL</sub>: Deviation due to the transmission line (generally due to the transceivers)

All the deviations of the system should be added and compared to the SCI clock tolerance:

$$D_{TRA} + D_{QUANT} + D_{REC} + D_{TCL} < 3.75\%$$

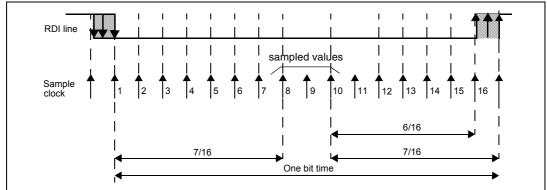

#### Noise error causes

See also the description of Noise error in Receiver on page 113.

#### Start bit

The Noise Flag (NF) is set during start bit reception if one of the following conditions occurs:

- 1. A valid falling edge is not detected. A falling edge is considered to be valid if the three consecutive samples before the falling edge occurs are detected as '1' and, after the falling edge occurs, during the sampling of the 16 samples, if one of the samples numbered 3, 5 or 7 is detected as a '1'.

- 2. During sampling of the 16 samples, if one of the samples numbered 8, 9 or 10 is detected as a '1'.

Therefore, a valid Start bit must satisfy both the above conditions to prevent the Noise Flag from being set.

#### Data bits

The Noise Flag (NF) is set during normal data bit reception if the following condition occurs: During the sampling of 16 samples, if all three samples numbered 8, 9 and 10 are not the same. The majority of the 8th, 9th and 10th samples is considered as the bit value.

Therefore, a valid Data bit must have samples 8, 9 and 10 at the same value to prevent the Noise Flag from being set.

| Bit | Name    | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|-----|---------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 4   | -       | Reserved, must be kept cleared.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| 3:0 | CH[3:0] | Channel selection<br>These bits are set and cleared by software. They select the analog input to convert.<br>0000: Channel pin = AIN0<br>0001: Channel pin = AIN1<br>0010: Channel pin = AIN2<br>0011: Channel pin = AIN3<br>0100: Channel pin = AIN4<br>0101: Channel pin = AIN5<br>0110: Channel pin = AIN5<br>0110: Channel pin = AIN7<br>1000: Channel pin = AIN8<br>1001: Channel pin = AIN9<br>1010: Channel pin = AIN19<br>1010: Channel pin = AIN10<br>1011: Channel pin = AIN12<br>1101: Channel pin = AIN12<br>1101: Channel pin = AIN13<br>1110: Channel pin = AIN14<br>1111: Channel pin = AIN15<br>Note: The number of channels is device dependent. Refer to Section 2: Pin<br>description. |

| Table 71. | ADCCSR | register | description | (continued) |

|-----------|--------|----------|-------------|-------------|

|-----------|--------|----------|-------------|-------------|

## ADC data register high (ADCDRH)

| ADCDRH Reset value: 0000 00 |   |   |   |   |   |   | 0000 (00h) |

|-----------------------------|---|---|---|---|---|---|------------|

| 7                           | 6 | 5 | 4 | 3 | 2 | 1 | 0          |

| D[9:2]                      |   |   |   |   |   |   |            |

| RO                          |   |   |   |   |   |   |            |

## Table 72. ADCDRH register description

| Bit | Name   | Function                      |

|-----|--------|-------------------------------|

| 7:0 | D[9:2] | MSB of converted analog value |

## 11 Instruction set

## 11.1 CPU addressing modes

The CPU features 17 different addressing modes which can be classified in 7 main groups (see *Table 75*).

| Addressing mode | Example         |

|-----------------|-----------------|

| Inherent        | nop             |

| Immediate       | ld A,#\$55      |

| Direct          | ld A,\$55       |

| Indexed         | ld A,(\$55,X)   |

| Indirect        | ld A,([\$55],X) |

| Relative        | jrne loop       |

| Bit operation   | bset byte,#5    |

Table 75.Addressing mode groups

The CPU Instruction Set is designed to minimize the number of bytes required per instruction: To do so, most of the addressing modes may be divided in two submodes called long and short:

- Long addressing mode is more powerful because it can use the full 64 Kbyte address space, however it uses more bytes and more CPU cycles.

- Short addressing mode is less powerful because it can generally only access page zero (0000h - 00FFh range), but the instruction size is more compact, and faster. All memory to memory instructions use short addressing modes only (CLR, CPL, NEG, BSET, BRES, BTJT, BTJF, INC, DEC, RLC, RRC, SLL, SRL, SRA, SWAP)

The ST7 Assembler optimizes the use of long and short addressing modes.

|           | Mode     |         | Syntax            | Destination | Pointer address<br>(Hex.) | Pointer size<br>(Hex.) | Length<br>(bytes) |

|-----------|----------|---------|-------------------|-------------|---------------------------|------------------------|-------------------|

| Inherent  |          |         | nop               |             |                           |                        | + 0               |

| Immediate |          |         | ld A,#\$55        |             |                           |                        | + 1               |

| Short     | Direct   |         | ld A,\$10         | 00FF        |                           |                        | + 1               |

| Long      | Direct   |         | ld A,\$1000       | 0000FFFF    |                           |                        | + 2               |

| No offset | Direct   | Indexed | ld A,(X)          | 00FF        |                           |                        | + 0               |

| Short     | Direct   | Indexed | ld A,(\$10,X)     | 001FE       |                           |                        | + 1               |

| Long      | Direct   | Indexed | ld A,(\$1000,X)   | 0000FFFF    |                           |                        | + 2               |

| Short     | Indirect |         | ld A,[\$10]       | 00FF        | 00FF                      | byte                   | + 2               |

| Long      | Indirect |         | ld A,[\$10.w]     | 0000FFFF    | 00FF                      | word                   | + 2               |

| Short     | Indirect | Indexed | ld A,([\$10],X)   | 001FE       | 00FF                      | byte                   | + 2               |

| Long      | Indirect | Indexed | ld A,([\$10.w],X) | 0000FFFF    | 00FF                      | word                   | + 2               |

Table 76. CPU addressing mode overview

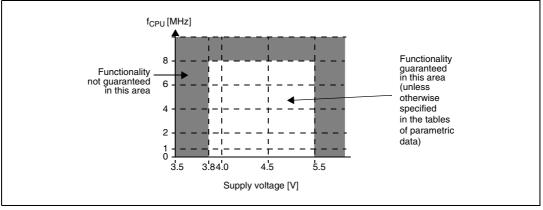

## 12.3 Operating conditions

| Table 86. | Operating | conditions |

|-----------|-----------|------------|

|-----------|-----------|------------|

| Symbol                                                                                                                                                                                                                                                    | Parameter                                    | Conditions                                                                                                                                                                                                                                | Min | Max | Unit |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|-----|------|

| f <sub>CPU</sub>                                                                                                                                                                                                                                          | Internal clock frequency                     |                                                                                                                                                                                                                                           | 0   | 8   | MHz  |

| V                                                                                                                                                                                                                                                         | Operating voltage (except Flash Write/Erase) |                                                                                                                                                                                                                                           | 3.8 | 5.5 | v    |

| ♥ DD                                                                                                                                                                                                                                                      | Operating Voltage for Flash Write/Erase      | V <sub>PP</sub> = 11.4 to 12.6 V                                                                                                                                                                                                          | 4.5 | 5.5 | v    |

| f <sub>CPU</sub> Internal clock frequency         V <sub>DD</sub> Operating voltage (except Flash Write/Erase)         Operating Voltage for Flash Write/Erase       V <sub>F</sub> T <sub>A</sub> Ambient temperature range       6-         7-       7- |                                              | 1-suffix version                                                                                                                                                                                                                          | 0   | 70  |      |

|                                                                                                                                                                                                                                                           | 5-suffix version                             | -10                                                                                                                                                                                                                                       | 85  |     |      |

| T <sub>A</sub>                                                                                                                                                                                                                                            | Ambient temperature range                    | 6-suffix version                                                                                                                                                                                                                          | -40 | 85  | °C   |

| f <sub>CPU</sub> Internal clock freque<br>V <sub>DD</sub> Operating voltage                                                                                                                                                                               |                                              | 7-suffix version                                                                                                                                                                                                                          | -40 | 105 |      |

|                                                                                                                                                                                                                                                           |                                              | Image: optimized state         Image: optimized state           ase)         0 $V_{PP} = 11.4$ to $12.6$ V         4.5           1-suffix version         0           5-suffix version         -10           6-suffix version         -40 | 125 |     |      |

#### Figure 64. f<sub>CPU</sub> max versus V<sub>DD</sub>

#### *Note:* Some temperature ranges are only available with a specific package and memory size. Refer to Section 14: Device configuration and ordering information.

Warning: Do not connect 12 V to  $V_{PP}$  before  $V_{DD}$  is powered on, as this may damage the device.

#### 12.5.2 **Flash current consumption**

| Table 90. | Flash | current | consumption |

|-----------|-------|---------|-------------|

|           |       |         |             |

| Symbol          | Parameter                                          | Conditions                                                                                                                                                                                                                                                                    | 32 Kbyte<br>Flash         |                              | 16/8 Kbyte<br>Flash          |                             | Unit          |  |

|-----------------|----------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------|------------------------------|------------------------------|-----------------------------|---------------|--|

|                 |                                                    |                                                                                                                                                                                                                                                                               | Тур                       | Max <sup>(1)</sup>           | Тур                          | Max <sup>(1)</sup>          |               |  |

| I <sub>DD</sub> | Supply current in Run mode <sup>(2)</sup>          | $      f_{OSC} = 2 \text{ MHz}, \  f_{CPU} = 1 \text{ MHz} $ $      f_{OSC} = 4 \text{ MHz}, \  f_{CPU} = 2 \text{ MHz} $ $      f_{OSC} = 8 \text{ MHz}, \  f_{CPU} = 4 \text{ MHz} $ $      f_{OSC} = 16 \text{ MHz}, \  f_{CPU} = 8 \text{ MHz} $                          | 1.3<br>2.0<br>3.6<br>7.1  | 3.0<br>5.0<br>8.0<br>15.0    | 1<br>1.4<br>2.4<br>4.4       | 2.3<br>3.5<br>5.3<br>7.0    |               |  |

|                 | Supply current in Slow<br>mode <sup>(2)</sup>      | $      f_{OSC} = 2 \text{ MHz}, \      f_{CPU} = 62.5 \text{ kHz} \\       f_{OSC} = 4 \text{ MHz}, \      f_{CPU} = 125 \text{ kHz} \\       f_{OSC} = 8 \text{ MHz}, \      f_{CPU} = 250 \text{ kHz} \\       f_{OSC} = 16 \text{ MHz}, \      f_{CPU} = 500 \text{ kHz} $ | 0.6<br>0.7<br>0.8<br>1.1  | 2.7<br>3.0<br>3.6<br>4.0     | 0.48<br>0.53<br>0.63<br>0.80 | 1<br>1.1<br>1.2<br>1.4      | mA            |  |

|                 | Supply current in Wait mode <sup>(2)</sup>         |                                                                                                                                                                                                                                                                               | 0.8<br>1.2<br>2.0<br>3.5  | 3.0<br>4.0<br>5.0<br>7.0     | 0.6<br>0.9<br>1.3<br>2.3     | 1.8<br>2.2<br>2.6<br>3.6    | <u>2</u><br>6 |  |

|                 | Supply current in Slow Wait<br>mode <sup>(2)</sup> | $      f_{OSC} = 2 \text{ MHz}, \  f_{CPU} = 62.5 \text{ kHz} \\       f_{OSC} = 4 \text{ MHz}, \  f_{CPU} = 125 \text{ kHz} \\       f_{OSC} = 8 \text{ MHz}, \  f_{CPU} = 250 \text{ kHz} \\       f_{OSC} = 16 \text{ MHz}, \  f_{CPU} = 500 \text{ kHz} $                 | 580<br>650<br>770<br>1050 | 1200<br>1300<br>1800<br>2000 | 430<br>470<br>530<br>660     | 950<br>1000<br>1050<br>1200 |               |  |

|                 | Supply current in Halt mode <sup>(3)</sup>         | $-40^{\circ}C \le T_A \le +85^{\circ}C$ $-40^{\circ}C \le T_A \le +125^{\circ}C$                                                                                                                                                                                              | <1<br>5                   | 10<br>50                     | <1<br><1                     | 10<br>50                    | μA            |  |

|                 | Supply current in Active-halt mode <sup>(4)</sup>  | $f_{OSC} = 2 \text{ MHz}$<br>$f_{OSC} = 4 \text{ MHz}$<br>$f_{OSC} = 8 \text{ MHz}$<br>$f_{OSC} = 16 \text{ MHz}$                                                                                                                                                             | 365<br>380<br>410<br>500  | 475<br>500<br>550<br>650     | 315<br>330<br>360<br>460     | 425<br>450<br>500<br>600    |               |  |

1. Data based on characterization results, tested in production at  $V_{\text{DD}}$  max. and  $f_{\text{CPU}}$  max.

Measurements are done in the following conditions:

Program executed from RAM, CPU running with RAM access. The increase in consumption when executing from Flash is

- Program executed from HAM, CPO furthing with HAW access. The increase in consumption when executing non-radii 50%. - All I/O pins in input mode with a static value at  $V_{DD}$  or  $V_{SS}$  (no load) - All peripherals in reset state - LVD disabled - Clock input (OSC1) driven by external square wave - In Slow and Slow Wait modes,  $f_{CPU}$  is based on  $f_{OSC}$  divided by 32 - To obtain the total current consumption of the device, add the clock source (*Section 12.6.3*) and the peripheral power consumption (*Section 12.5.4*) consumption (Section 12.5.4).

3. All I/O pins in push-pull 0 mode (when applicable) with a static value at  $V_{DD}$  or  $V_{SS}$  (no load), LVD disabled. Data based on characterization results, tested in production at  $V_{DD}$  max. and  $f_{CPU}$  max.

4. Data based on characterization results, not tested in production. All I/O pins in push-pull 0 mode (when applicable) with a static value at V<sub>DD</sub> or V<sub>SS</sub> (no load); clock input (OSC1) driven by external square wave, LVD disabled. To obtain the total current consumption of the device, add the clock source consumption (*Section 12.6.3*).

## 12.5.3 Supply and clock managers

The previous current consumption specified for the ST7 functional operating modes over temperature range does not take into account the clock source current consumption. To obtain the total device consumption, the two current values must be added (except for Halt mode).

|                        |                                                          | -             |                                   |     |      |

|------------------------|----------------------------------------------------------|---------------|-----------------------------------|-----|------|

| Symbol                 | Parameter                                                | Conditions    | Тур                               | Мах | Unit |

| I <sub>DD(RCINT)</sub> | Supply current of internal RC oscillator                 |               | 625                               |     |      |

| I <sub>DD(RES)</sub>   | Supply current of resonator oscillator <sup>(1)(2)</sup> |               | see Section 12.6.3<br>on page 150 |     | μA   |

| I <sub>DD(PLL)</sub>   | PLL supply current                                       | V – 5V        | 360                               |     |      |

| I <sub>DD(LVD)</sub>   | LVD supply current                                       | $V_{DD} = 5V$ | 150                               | 300 |      |

Table 91. Oscillators, PLL and LVD current consumption

1. Data based on characterization results done with the external components specified in *Section 12.6.3*, not tested in production.

2. As the oscillator is based on a current source, the consumption does not depend on the voltage.

## 12.5.4 On-chip peripherals

#### Table 92. On-chip peripherals current consumption

| Symbol               | Parameter                                         | Conditions                                                          | Тур | Unit |

|----------------------|---------------------------------------------------|---------------------------------------------------------------------|-----|------|

| I <sub>DD(TIM)</sub> | 16-bit timer supply current <sup>(1)</sup>        |                                                                     | 50  |      |

| I <sub>DD(SPI)</sub> | SPI supply current <sup>(2)</sup>                 | $T_A = 25 \ ^\circ C$ , $f_{CPU} = 4 \ MHz$ ,<br>$V_{DD} = 5.0 \ V$ |     | μA   |

| I <sub>DD(SCI)</sub> | SCI supply current <sup>(3)</sup>                 |                                                                     |     | μΑ   |

| I <sub>DD(ADC)</sub> | ADC supply current when converting <sup>(4)</sup> |                                                                     |     |      |

1. Data based on a differential  $I_{DD}$  measurement between reset configuration (timer counter running at  $f_{CPU}/4$ ) and timer counter stopped (only TIMD bit set). Data valid for one timer.

Data based on a differential I<sub>DD</sub> measurement between reset configuration (SPI disabled) and a permanent SPI master communication at maximum speed (data sent equal to 55h). This measurement includes the pad toggling consumption.

3. Data based on a differential  $I_{DD}$  measurement between SCI low power state (SCID = 1) and a permanent SCI data transmit sequence.

4. Data based on a differential  ${\rm I}_{\rm DD}$  measurement between reset configuration and continuous A/D conversions.

## 12.6 Clock and timing characteristics

Subject to general operating conditions for  $V_{DD}$ ,  $f_{CPU}$ , and  $T_A$ .

## 12.6.1 General timings

### Table 93. General timings

| Symbol               | Parameter                                                           | Conditions               | Min  | Typ <sup>(1)</sup> | Max | Unit             |

|----------------------|---------------------------------------------------------------------|--------------------------|------|--------------------|-----|------------------|

| +                    | Instruction public time                                             |                          | 2    | 3                  | 12  | t <sub>CPU</sub> |

| <sup>t</sup> c(INST) | Instruction cycle time                                              | f <sub>CPU</sub> = 8 MHz | 250  | 375                | -   | ns               |

|                      | Intervent reaction time t $10^{(2)}$                                |                          | 10   |                    | 22  | t <sub>CPU</sub> |

| t <sub>v(IT)</sub>   | Interrupt reaction time $t_{v(IT)} = \Delta t_{c(INST)} + 10^{(2)}$ | f <sub>CPU</sub> = 8 MHz | 1.25 |                    | -   | μs               |

1. Data based on typical application software.

2. Time measured between interrupt event and interrupt vector fetch.  $\Delta t_{c(INST)}$  is the number of  $t_{CPU}$  cycles needed to finish the current instruction execution.

## 12.6.2 External clock source

#### Table 94. External clock source

| Symbol                                         | Parameter                             | Conditions                       | Min                | Тур | Max                | Unit |

|------------------------------------------------|---------------------------------------|----------------------------------|--------------------|-----|--------------------|------|

| V <sub>OSC1H</sub>                             | OSC1 input pin high level voltage     |                                  | V <sub>DD</sub> -1 |     | $V_{DD}$           | v    |

| V <sub>OSC1L</sub>                             | OSC1 input pin low level voltage      |                                  | $V_{SS}$           |     | V <sub>SS</sub> +1 | v    |

| t <sub>w(OSC1H)</sub><br>t <sub>w(OSC1L)</sub> | OSC1 high or low time <sup>(1)</sup>  | See Figure 65.                   | 5                  |     |                    | 20   |

| t <sub>r(OSC1)</sub><br>t <sub>f(OSC1)</sub>   | OSC1 rise or fall time <sup>(1)</sup> |                                  |                    |     | 15                 | ns   |

| I <sub>lkg</sub>                               | OSC1 input leakage current            | $V_{SS} \leq V_{IN} \leq V_{DD}$ |                    |     | ±1                 | μA   |

1. Data based on design simulation and/or technology characteristics, not tested in production.

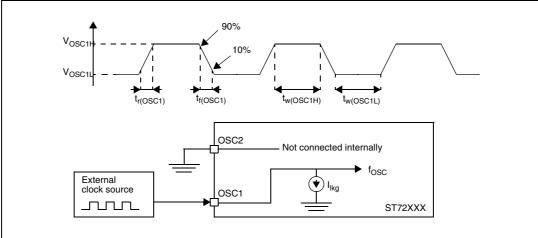

#### Figure 65. Typical application with an external clock source

## 12.6.3 Crystal and ceramic resonator oscillators

The ST7 internal clock can be supplied with four different crystal/ceramic resonator oscillators. All the information given in this paragraph are based on characterization results with specified typical external components. In the application, the resonator and the load capacitors have to be placed as close as possible to the oscillator pins in order to minimize output distortion and start-up stabilization time. Refer to the crystal/ceramic resonator manufacturer for more details (frequency, package, accuracy...).

#### 8/16 Kbyte Flash and ROM devices

|                                    | devices)                                                                                                           |                                                                                                                                                                                                                                            |                      |                         |                          |      |

|------------------------------------|--------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------|-------------------------|--------------------------|------|

| Symbol                             | Parameter                                                                                                          | Conditions                                                                                                                                                                                                                                 |                      | Тур                     | Max                      | Unit |

| fosc                               | Oscillator frequency <sup>(1)</sup>                                                                                | LP: low power oscillator<br>MP: medium power oscillator<br>MS: medium speed oscillator<br>HS: high speed oscillator                                                                                                                        | 1<br>>2<br>>4<br>>8  |                         | 2<br>4<br>8<br>16        | MHz  |

| R <sub>F</sub>                     | Feedback resistor <sup>(2)</sup>                                                                                   |                                                                                                                                                                                                                                            | 20                   |                         | 40                       | kΩ   |

| C <sub>L1</sub><br>C <sub>L2</sub> | Recommended load capacitance versus equivalent serial resistance of the crystal or ceramic resonator $(R_S)^{(3)}$ | $ \begin{array}{ll} R_{S} = 200 \; \Omega & LP \; \text{oscillator} \\ R_{S} = 200 \; \Omega & MP \; \text{oscillator} \\ R_{S} = 200 \; \Omega & MS \; \text{oscillator} \\ R_{S} = 100 \; \Omega & HS \; \text{oscillator} \end{array} $ | 22<br>22<br>18<br>15 |                         | 56<br>46<br>33<br>33     | pF   |

| i <sub>2</sub>                     | OSC2 driving current                                                                                               | V <sub>DD</sub> = 5V, V <sub>IN</sub> = V <sub>SS</sub><br>LP oscillator<br>MP oscillator<br>MS oscillator<br>HS oscillator                                                                                                                |                      | 80<br>160<br>310<br>610 | 150<br>250<br>460<br>910 | μΑ   |

# Table 95. Crystal and ceramic resonator oscillators (8/16 Kbyte Flash and ROM devices)

1. The oscillator selection can be optimized in terms of supply current using an high quality resonator with small R<sub>S</sub> value. Refer to crystal/ceramic resonator manufacturer for more details.

Data based on characterization results, not tested in production. The relatively low value of the RF resistor, offers a good protection against issues resulting from use in a humid environment, due to the induced leakage and the bias condition change. However, it is recommended to take this point into account if the microcontroller is used in tough humidity conditions.

3. For  $C_{L1}$  and  $C_{L2}$  it is recommended to use high-quality ceramic capacitors in the 5 pF to 25 pF range (typ.) designed for high-frequency applications and selected to match the requirements of the crystal or resonator.  $C_{L1}$  and  $C_{L2}$ , are usually the same size. The crystal manufacturer typically specifies a load capacitance which is the series combination of  $C_{L1}$  and  $C_{L2}$ . PCB and MCU pin capacitance must be included when sizing  $C_{L1}$  and  $C_{L2}$  (10 pF can be used as a rough estimate of the combined pin and board capacitance).

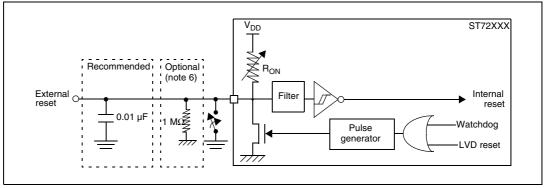

#### **RESET** pin protection when LVD is enabled

When the LVD is enabled, it is recommended to protect the **RESET** pin as shown in *Figure 78* and follow these guidelines:

- 1. The reset network protects the device against parasitic resets.

- 2. The output of the external reset circuit must have an open-drain output to drive the ST7 reset pad. Otherwise the device can be damaged when the ST7 generates an internal reset (LVD or watchdog).

- Whatever the reset source is (internal or external), the user must ensure that the level on the RESET pin can go below the V<sub>IL</sub> max. level specified in *Section 12.10.1*. Otherwise the reset will not be taken into account internally.

- Because the reset circuit is designed to allow the internal RESET to be output in the RESET pin, the user must ensure that the current sunk on the RESET pin (by an external pull-up for example) is less than the absolute maximum value specified for I<sub>INJ(RESET)</sub> in *Section 12.2.2 on page 143*.

- 5. When the LVD is enabled, it is mandatory not to connect a pull-up resistor. A 10nF pulldown capacitor is recommended to filter noise on the reset line.

- 6. In case a capacitive power supply is used, it is recommended to connect a 1M ohm pull-down resistor to the RESET pin to discharge any residual voltage induced by this capacitive power supply (this will add 5  $\mu$ A to the power consumption of the MCU).

#### Tips when using the LVD:

- Check that all recommendations related to reset circuit have been applied (see section above)

- Check that the power supply is properly decoupled (100 nF + 10 μF close to the MCU). Refer to AN1709. If this cannot be done, it is recommended to put a 100 nF + 1 M Ohm pull-down on the RESET pin.

- The capacitors connected on the RESET pin and also the power supply are key to avoiding any start-up marginality. In most cases, steps 1 and 2 above are sufficient for a robust solution. Otherwise: Replace 10 nF pull-down on the RESET pin with a 5 μF to 20 μF capacitor.

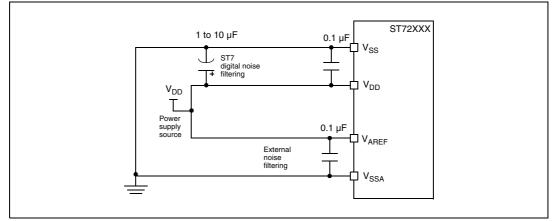

## 12.13.1 Analog power supply and reference pins

Depending on the MCU pin count, the package may feature separate  $V_{AREF}$  and  $V_{SSA}$  analog power supply pins. These pins supply power to the A/D converter cell and function as the high and low reference voltages for the conversion. In some packages,  $V_{AREF}$  and  $V_{SSA}$  pins are not available (refer to *Section 2 on page 15*). In this case the analog supply and reference pads are internally bonded to the  $V_{DD}$  and  $V_{SS}$  pins.

Separation of the digital and analog power pins allow board designers to improve A/D performance. Conversion accuracy can be impacted by voltage drops and noise in the event of heavily loaded or badly decoupled power supply lines (see *Section 12.13.2: General PCB design guidelines*).

## 12.13.2 General PCB design guidelines

To obtain best results, some general design and layout rules should be followed when designing the application PCB to shield the noise-sensitive, analog physical interface from noise-generating CMOS logic signals.

- Use separate digital and analog planes. The analog ground plane should be connected to the digital ground plane via a single point on the PCB.

- Filter power to the analog power planes. It is recommended to connect capacitors, with good high frequency characteristics, between the power and ground lines, placing 0.1μF and optionally, if needed 10 pF capacitors as close as possible to the ST7 power supply pins and a 1 to 10 μF capacitor close to the power source (see *Figure 87*).

- The analog and digital power supplies should be connected in a star network. Do not use a resistor, as V<sub>AREF</sub> is used as a reference voltage by the A/D converter and any resistance would cause a voltage drop and a loss of accuracy.

- Properly place components and route the signal traces on the PCB to shield the analog inputs. Analog signals paths should run over the analog ground plane and be as short as possible. Isolate analog signals from digital signals that may switch while the analog inputs are being sampled by the A/D converter. Do not toggle digital outputs on the same I/O port as the A/D input being converted.

#### Figure 87. Power supply filtering

## 13.3 Thermal characteristics

| Table 118. | Thermal characteristics |

|------------|-------------------------|

|------------|-------------------------|

| Symbol            | Ratings                                                                                                          | Value                | Unit |

|-------------------|------------------------------------------------------------------------------------------------------------------|----------------------|------|

| R <sub>thJA</sub> | Package thermal resistance (junction to ambient):<br>LQFP44 10x10<br>LQFP32 7x7<br>DIP42 600mil<br>SDIP32 200mil | 52<br>70<br>55<br>50 | °C/W |

| P <sub>D</sub>    | Power dissipation <sup>(1)</sup>                                                                                 | 500                  | mW   |

| T <sub>Jmax</sub> | Maximum junction temperature <sup>(2)</sup>                                                                      | 150                  | °C   |

1. The maximum power dissipation is obtained from the formula  $P_D = (T_J - T_A) / R_{thJA}$ . The power dissipation of an application can be defined by the user with the formula:  $P_D = P_{INT} + P_{PORT}$  where  $P_{INT}$  is the chip internal power ( $I_{DD} \times V_{DD}$ ) and  $P_{PORT}$  is the port power dissipation depending on the ports used in the application.

2. The maximum chip-junction temperature is based on technology characteristics.

|                           |                                                                      | ST72324Bxx MICROCO<br>(Last update           |           |                              |               |                      |

|---------------------------|----------------------------------------------------------------------|----------------------------------------------|-----------|------------------------------|---------------|----------------------|

| Customer:                 |                                                                      | · · · · · · · · · · · · · · · · · · ·        |           | ,                            |               |                      |

| Address:                  |                                                                      |                                              |           |                              |               |                      |

| <b>.</b>                  |                                                                      |                                              |           |                              |               |                      |

| Contact:                  |                                                                      | •••••                                        |           |                              |               |                      |

| Phone No:                 |                                                                      |                                              |           |                              |               |                      |

|                           |                                                                      | by STMicroelectronics.                       |           |                              |               |                      |

| ROM code m                | ust be sent in .S19 fo                                               | ormatHex extension can                       | not be pr | ocessed.                     |               |                      |

| Device type/n             |                                                                      | e (check only one option):                   |           |                              |               |                      |

| ROM DEVIC                 | E:                                                                   | 32K                                          | <br>      | <u>16K</u>                   | I             | 8K                   |

| LQF                       | P32: I                                                               | []                                           | 1         | []                           | I             | []                   |

|                           | 32:                                                                  | []                                           |           | []                           | I             | []                   |

|                           | P44 : I                                                              | []                                           |           | []                           | I             | []                   |

| DIP                       | 42:                                                                  | []                                           | I         | []                           | I             | []                   |

| DIE FORM:                 | I                                                                    | 32K                                          |           | 16K                          |               | 8K                   |

|                           | <br>oin:                                                             | []                                           |           | []                           | <br>          | []                   |

| 44-p                      |                                                                      | []                                           | i         | []                           |               | []                   |

|                           |                                                                      |                                              |           |                              |               | 11                   |

|                           |                                                                      |                                              |           |                              |               |                      |

| Packaged product          |                                                                      |                                              |           | Die product (dice tes        | sted at 25 °C | only)                |

|                           |                                                                      | Tray                                         |           | ] Tape & Reel                |               |                      |

| DIP: []T                  | Tube                                                                 |                                              |           | ] Inked wafer                |               |                      |

|                           |                                                                      |                                              | [         | ] Sawn wafer on stie         | cky foil      |                      |

| [] 0 °C<br>[] -10         | (do not check for die<br>C to +70 °C<br>°C to +85 °C<br>°C to +85 °C | product).                                    |           |                              |               |                      |

| [] -40                    | °C to +105 °C<br>°C to +125 °C                                       |                                              |           |                              |               |                      |

| Special marki             | ing: [] No                                                           | [] Yes "<br>digits, '.', '-', '/' and spaces |           | ' (LQFP32 7 char., c         | other pkg. 10 | char. max)           |

| Clock source              |                                                                      | uigits, ., -, / and spaces                   | s only.   |                              |               |                      |

|                           | [] Resonator:                                                        | [] LP: Low power reso                        | onator (* | to 2 MHz)                    |               |                      |

|                           | []                                                                   | [] MP: Medium power                          |           |                              |               |                      |

|                           |                                                                      | [] MS: Medium speed                          |           |                              |               |                      |

|                           |                                                                      | [] HS: High speed res                        |           |                              |               |                      |

|                           | [] Internal RC<br>[] External clock                                  | []                                           |           |                              |               |                      |

| PLL                       |                                                                      | [] Disabled                                  |           | [] Enabled                   |               |                      |

|                           | [] Disabled                                                          | [] High threshold                            |           |                              | ] Low thresh  | old                  |

| Reset Delay               |                                                                      | [] 256 Cycles                                | [] Mec    | [] 4096 Cycles               |               | 1010                 |

| Watchdog se<br>Watchdog R | election:<br>leset on Halt:                                          | [] Software activation<br>[] Reset           |           | [] Hardware a<br>[] No Reset | ctivation     |                      |

| Readout pro               | otection:                                                            | [] Disabled                                  |           | [] Enabled                   |               |                      |

|                           |                                                                      |                                              |           |                              |               |                      |

| Date<br>Signature         |                                                                      |                                              |           |                              |               |                      |

| Signature                 |                                                                      | n hinary value is inverted                   | l hetwee  | n ROM and Flash r            | roducte Th    | ontion byte check-   |