#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                       |

|----------------------------|-----------------------------------------------------------------------|

| Product Status             | Obsolete                                                              |

| Core Processor             | ST7                                                                   |

| Core Size                  | 8-Bit                                                                 |

| Speed                      | 8MHz                                                                  |

| Connectivity               | SCI, SPI                                                              |

| Peripherals                | LVD, POR, PWM, WDT                                                    |

| Number of I/O              | 24                                                                    |

| Program Memory Size        | 16KB (16K x 8)                                                        |

| Program Memory Type        | FLASH                                                                 |

| EEPROM Size                | -                                                                     |

| RAM Size                   | 512 x 8                                                               |

| Voltage - Supply (Vcc/Vdd) | 3.8V ~ 5.5V                                                           |

| Data Converters            | A/D 12x10b                                                            |

| Oscillator Type            | Internal                                                              |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                     |

| Mounting Type              | Surface Mount                                                         |

| Package / Case             | 32-SOIC (0.295", 7.50mm Width)                                        |

| Supplier Device Package    | -                                                                     |

| Purchase URL               | https://www.e-xfl.com/product-detail/stmicroelectronics/st72f324bk4m6 |

|                            |                                                                       |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

57

| Table 99.  | PLL characteristics                                  |

|------------|------------------------------------------------------|

| Table 100. | RAM and hardware registers                           |

| Table 101. | Dual voltage HDFlash memory                          |

| Table 102. | EMS test results                                     |

| Table 103. | EMI emissions                                        |

| Table 104. | Absolute maximum ratings                             |

| Table 105. | Electrical sensitivities                             |

| Table 106. | General characteristics                              |

| Table 107. | Output driving current                               |

| Table 108. | Asynchronous RESET pin                               |

| Table 109. | ICCSEL/V <sub>PP</sub> pin                           |

| Table 110. | 16-bit timer                                         |

| Table 111. | SPI characteristics                                  |

| Table 112. | 10-bit ADC characteristics                           |

| Table 113. | ADC accuracy                                         |

| Table 114. | 44-pin low profile quad flat package mechanical data |

| Table 115. | 42-pin dual in line package mechanical data 173      |

| Table 116. | 32-pin low profile quad flat package mechanical data |

| Table 117. | 32-pin dual in-line package mechanical data 175      |

| Table 118. | Thermal characteristics                              |

| Table 119. | Flash option bytes                                   |

| Table 120. | Option byte 0 bit description                        |

| Table 121. | Option byte 1 bit description                        |

| Table 122. | Package selection (OPT7) 181                         |

| Table 123. | STMicroelectronics development tools                 |

| Table 124. | Suggested list of socket types                       |

| Table 125. | Port A and F configuration                           |

| Table 126. | Document revision history                            |

| Address           | Block                    | Register label | Register name                            | Reset status | Remarks   |

|-------------------|--------------------------|----------------|------------------------------------------|--------------|-----------|

| 0041h             |                          | TBCR2          | Timer B control register 2               | 00h          | R/W       |

| 0042h             |                          | TBCR1          | Timer B control register 1               | 00h          | R/W       |

| 0043h             |                          | TBCSR          | Timer B control/status register          | xxxx x0xxb   | R/W       |

| 0044h             |                          | TBIC1HR        | Timer B input capture 1 high register    | xxh          | Read only |

| 0045h             |                          | TBIC1LR        | Timer B input capture 1 low register     | xxh          | Read only |

| 0046h             |                          | TBOC1HR        | Timer B output compare 1 high register   | 80h          | R/W       |

| 0047h             |                          | TBOC1LR        | Timer B output compare 1 low register    | 00h          | R/W       |

| 0048h             | Timer B                  | TBCHR          | Timer B counter high register            | FFh          | Read only |

| 0049h             |                          | TBCLR          | Timer B counter low register             | FCh          | Read only |

| 004Ah             |                          | TBACHR         | Timer B alternate counter high register  | FFh          | Read only |

| 004Bh             |                          | TBACLR         | Timer B alternate counter low register   | FCh          | Read only |

| 004Ch             |                          | TBIC2HR        | Timer B input capture 2 high register    | xxh          | Read only |

| 004Dh             |                          | TBIC2LR        | Timer B input capture 2 low register     | xxh          | Read only |

| 004Eh             |                          | TBOC2HR        | Timer B output compare 2 high register   | 80h          | R/W       |

| 004Fh             |                          | TBOC2LR        | Timer B output compare 2 low register    | 00h          | R/W       |

| 0050h             |                          | SCISR          | SCI status register                      | C0h          | Read only |

| 0051h             |                          | SCIDR          | SCI data register                        | xxh          | R/W       |

| 0052h             |                          | SCIBRR         | SCI baud rate register                   | 00h          | R/W       |

| 0053h             | SCI                      | SCICR1         | SCI control register 1                   | x000 0000b   | R/W       |

| 0054h             | 301                      | SCICR2         | SCI control register 2                   | 00h          | R/W       |

| 0055h             |                          | SCIERPR        | SCI extended receive prescaler register  | 00h          | R/W       |

| 0056h             |                          |                | Reserved area                            |              |           |

| 0057h             |                          | SCIETPR        | SCI extended transmit prescaler register | 00h          | R/W       |

| 0058h to<br>006Fh |                          |                | Reserved area (24 bytes)                 |              |           |

| 0070h             |                          | ADCCSR         | Control/status register                  | 00h          | R/W       |

| 0071h             | ADC                      | ADCDRH         | Data high register                       | 00h          | Read only |

| 0072h             |                          | ADCDRL         | Data low register                        | 00h          | Read only |

| 0073h<br>007Fh    | Reserved area (13 bytes) |                |                                          |              |           |

#### Table 3. Hardware register map (continued)

1. The bits associated with unavailable pins must always keep their reset value.

2. The contents of the I/O port DR registers are readable only in output configuration. In input configuration, the values of the I/O pins are returned instead of the DR register contents.

Legend: x = undefined, R/W = read/write

# 4.5 ICP (in-circuit programming)

To perform ICP the microcontroller must be switched to ICC (in-circuit communication) mode by an external controller or programming tool.

Depending on the ICP code downloaded in RAM, Flash memory programming can be fully customized (number of bytes to program, program locations, or selection serial communication interface for downloading).

When using an STMicroelectronics or third-party programming tool that supports ICP and the specific microcontroller device, the user needs only to implement the ICP hardware interface on the application board (see *Figure 8*). For more details on the pin locations, refer to the device pinout description.

# 4.6 IAP (in-application programming)

This mode uses a BootLoader program previously stored in Sector 0 by the user (in ICP mode or by plugging the device in a programming tool).

This mode is fully controlled by user software. This allows it to be adapted to the user application, (such as user-defined strategy for entering programming mode, choice of communications protocol used to fetch the data to be stored). For example, it is possible to download code from the SPI, SCI, USB or CAN interface and program it in the Flash. IAP mode can be used to program any of the Flash sectors except Sector 0, which is write/erase protected to allow recovery in case errors occur during the programming operation.

### 4.7 Related documentation

For details on Flash programming and ICC protocol, refer to the *ST7* Flash Programming Reference Manual and to the *ST7* ICC Protocol Reference Manual.

### 4.7.1 Flash Control/Status Register (FCSR)

This register is reserved for use by programming tool software. It controls the Flash programming and erasing operations.

| FCSR |     |     |     |     | Reset | value:0000 | 0000 (00h) |

|------|-----|-----|-----|-----|-------|------------|------------|

| 7    | 6   | 5   | 4   | 3   | 2     | 1          | 0          |

| 0    | 0   | 0   | 0   | 0   | 0     | 0          | 0          |

| R/W  | R/W | R/W | R/W | R/W | R/W   | R/W        | R/W        |

|  | Table 5. | Flash control/status register address and reset value |

|--|----------|-------------------------------------------------------|

|--|----------|-------------------------------------------------------|

| Address (Hex) | Register label   | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

|---------------|------------------|---|---|---|---|---|---|---|---|

| 0029h         | FCSR reset value | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

# 7.5 Interrupt registers

### 7.5.1 CPU CC register interrupt bits

| CPU CC |     |     |     |     | Rese | et value: 111 | x 1010(xAh) |

|--------|-----|-----|-----|-----|------|---------------|-------------|

| 7      | 6   | 5   | 4   | 3   | 2    | 1             | 0           |

| 1      | 1   | 11  | Н   | 10  | N    | Z             | С           |

| R/W    | R/W | R/W | R/W | R/W | R/W  | R/W           | R/W         |

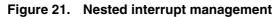

#### Table 15. CPU CC register interrupt bits description

| Bit | Name | Function                      |

|-----|------|-------------------------------|

| 5   | 11   | Software Interrupt Priority 1 |

| 3   | 10   | Software Interrupt Priority 0 |

#### Table 16. Interrupt software priority levels

| Interrupt software priority                  | Level | 11 | 10 |

|----------------------------------------------|-------|----|----|

| Level 0 (main)                               | Low   | 1  | 0  |

| Level 1                                      |       | 0  | 1  |

| Level 2                                      | ↓     | 0  | 0  |

| Level 3 (= interrupt disable) <sup>(1)</sup> | High  | 1  | 1  |

1. TRAP and RESET events can interrupt a level 3 program.

These two bits indicate the current interrupt software priority (see *Table 16*) and are set/cleared by hardware when entering in interrupt. The loaded value is given by the corresponding bits in the interrupt software priority registers (ISPRx).

They can be also set/cleared by software with the RIM, SIM, HALT, WFI, IRET and PUSH/POP instructions (see *Table 18: Dedicated interrupt instruction set*).

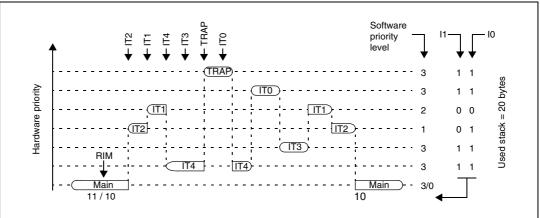

### 10.2.2 Clock-out capability

The clock-out capability is an alternate function of an I/O port pin that outputs the  $f_{CPU}$  clock to drive external devices. It is controlled by the MCO bit in the MCCSR register.

Caution: When selected, the clock out pin suspends the clock during Active-halt mode.

### 10.2.3 Real-time clock (RTC) timer

The counter of the real-time clock timer allows an interrupt to be generated based on an accurate real-time clock. Four different time bases depending directly on  $f_{OSC2}$  are available. The whole functionality is controlled by four bits of the MCCSR register: TB[1:0], OIE and OIF.

When the RTC interrupt is enabled (OIE bit set), the ST7 enters Active-halt mode when the HALT instruction is executed. See *Section 8.4: Active-halt and Halt modes on page 54* for more details.

#### 10.2.4 Beeper

The beep function is controlled by the MCCBCR register. It can output three selectable frequencies on the Beep pin (I/O port alternate function).

### Figure 35. Main clock controller (MCC/RTC) block diagram

# 10.3 16-bit timer

### 10.3.1 Introduction

The timer consists of a 16-bit free-running counter driven by a programmable prescaler.

It may be used for a variety of purposes, including pulse length measurement of up to two input signals (input capture) or generation of up to two output waveforms (output compare and PWM).

Pulse lengths and waveform periods can be modulated from a few microseconds to several milliseconds using the timer prescaler and the CPU clock prescaler.

Some ST7 devices have two on-chip 16-bit timers. They are completely independent, and do not share any resources. They are synchronized after a MCU reset as long as the timer clock frequencies are not modified.

This description covers one or two 16-bit timers. In ST7 devices with two timers, register names are prefixed with TA (Timer A) or TB (Timer B).

### 10.3.2 Main features

- Programmable prescaler: f<sub>CPU</sub> divided by 2, 4 or 8

- Overflow status flag and maskable interrupt

- External clock input (must be at least four times slower than the CPU clock speed) with the choice of active edge

- 1 or 2 output compare functions each with:

- 2 dedicated 16-bit registers

- 2 dedicated programmable signals

- 2 dedicated status flags

- 1 dedicated maskable interrupt

- 1 or 2 input capture functions each with:

- 2 dedicated 16-bit registers

- 2 dedicated active edge selection signals

- 2 dedicated status flags

- 1 dedicated maskable interrupt

- Pulse width modulation mode (PWM)

- One pulse mode

- Reduced power mode

- 5 alternate functions on I/O ports (ICAP1, ICAP2, OCMP1, OCMP2, EXTCLK)<sup>(c)</sup>

The timer block diagram is shown in Figure 36.

c. Some timer pins may not be available (not bonded) in some ST7 devices. Refer to *Section 2: Pin description*. When reading an input signal on a non-bonded pin, the value will always be '1'.

| Table 51. |      | CSA register description (continued)                                                                                                                                                                                                                                                                                                                                                                                                                               |

|-----------|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Bit       | Name | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| 6         | OCF1 | <ul> <li>Output compare flag 1</li> <li>0: No match (reset value).</li> <li>1: The content of the free running counter has matched the content of the OC1R register. To clear this bit, first read the SR register, then read or write the low byte of the OC1R (OC1LR) register.</li> </ul>                                                                                                                                                                       |

| 5         | TOF  | <ul> <li>Timer overflow flag</li> <li>0: No timer overflow (reset value).</li> <li>1: The free running counter rolled over from FFFFh to 0000h. To clear this bit, first read the SR register, then read or write the low byte of the CR (CLR) register.</li> <li><i>Note: Reading or writing the ACLR register does not clear TOF.</i></li> </ul>                                                                                                                 |

| 4         | ICF2 | <ul> <li>Input capture flag 2</li> <li>0: No input capture (reset value).</li> <li>1: An Input Capture has occurred on the ICAP2 pin. To clear this bit, first read the SR register, then read or write the low byte of the IC2R (IC2LR) register.</li> </ul>                                                                                                                                                                                                      |

| 3         | OCF2 | Output compare flag 2<br>0: No match (reset value).<br>1: The content of the free running counter has matched the content of the OC2R<br>register. To clear this bit, first read the SR register, then read or write the low byte of<br>the OC2R (OC2LR) register.                                                                                                                                                                                                 |

| 2         | TIMD | <ul> <li>Timer disable</li> <li>This bit is set and cleared by software. When set, it freezes the timer prescaler and counter and disabled the output functions (OCMP1 and OCMP2 pins) to reduce power consumption. Access to the timer registers is still available, allowing the timer configuration to be changed, or the counter reset, while it is disabled.</li> <li>0: Timer enabled.</li> <li>1: Timer prescaler, counter and outputs disabled.</li> </ul> |

| 1:0       | -    | Reserved, must be kept cleared.                                                                                                                                                                                                                                                                                                                                                                                                                                    |

Table 51.

CSR register description (continued)

### Input capture 1 high register (IC1HR)

This is an 8-bit register that contains the high part of the counter value (transferred by the input capture 1 event).

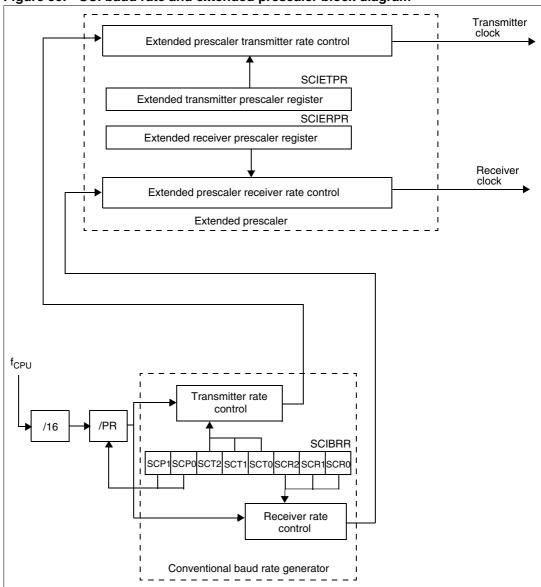

Figure 59. SCI baud rate and extended prescaler block diagram

#### **Framing error**

A framing error is detected when:

- The stop bit is not recognized on reception at the expected time, following either a desynchronization or excessive noise.

- A break is received.

When the framing error is detected:

- the FE bit is set by hardware

- Data is transferred from the Shift register to the SCIDR register.

- No interrupt is generated. However this bit rises at the same time as the RDRF bit which itself generates an interrupt.

The FE bit is reset by a SCISR register read operation followed by a SCIDR register read operation.

#### **Receiver muting and wakeup feature**

In multiprocessor configurations it is often desirable that only the intended message recipient should actively receive the full message contents, thus reducing redundant SCI service overhead for all non-addressed receivers.

The non-addressed devices may be placed in sleep mode by means of the muting function.

Setting the RWU bit by software puts the SCI in sleep mode:

All the reception status bits cannot be set.

All the receive interrupts are inhibited.

A muted receiver may be awakened by one of the following two ways:

- by Idle Line detection if the Wake bit is reset,

- by Address Mark detection if the Wake bit is set.

A receiver wakes up by Idle Line detection when the Receive line has recognized an Idle Frame. Then the RWU bit is reset by hardware but the Idle bit is not set.

A receiver wakes up by Address Mark detection when it received a '1' as the most significant bit of a word, thus indicating that the message is an address. The reception of this particular word wakes up the receiver, resets the RWU bit and sets the RDRF bit, which allows the receiver to receive this word normally and to use it as an address word.

**Caution:** In Mute mode, do not write to the SCICR2 register. If the SCI is in Mute mode during the read operation (RWU = 1) and an address mark wakeup event occurs (RWU is reset) before the write operation, the RWU bit will be set again by this write operation. Consequently the address byte is lost and the SCI is not woken up from Mute mode.

#### **Parity control**

Parity control (generation of parity bit in transmission and parity checking in reception) can be enabled by setting the PCE bit in the SCICR1 register. Depending on the frame length defined by the M bit, the possible SCI frame formats are as listed in *Table 59*.

| M bit | PCE bit SCI frame |                            |  |

|-------|-------------------|----------------------------|--|

| 0     | 0                 | SB   8 bit data   STB      |  |

| 0     | 1                 | SB   7-bit data   PB   STB |  |

| 1     | 0                 | SB   9-bit data   STB      |  |

| 1     | 1                 | SB   8-bit data PB   STB   |  |

Table 59. Frame formats<sup>(1)(2)</sup>

1. SB = Start bit, STB = Stop bit, and PB = Parity bit.

2. In case of wakeup by an address mark, the MSB bit of the data is taken into account and not the Parity bit.

| Bit | Name | me Function                                                                                                                                                                                                                                                                                                                                                 |  |  |  |  |  |

|-----|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| 0   | PE   | <ul> <li>Parity error</li> <li>This bit is set by hardware when a parity error occurs in receiver mode. It is cleared by a software sequence (a read to the status register followed by an access to the SCIDR data register). An interrupt is generated if PIE = 1 in the SCICR1 register.</li> <li>0: No parity error</li> <li>1: Parity error</li> </ul> |  |  |  |  |  |

| Table 62. | SCISR regist | er description | (continued) |

|-----------|--------------|----------------|-------------|

|-----------|--------------|----------------|-------------|

### SCI Control Register 1 (SCICR1)

| SCICR1 |     |      |     |      | Rese | et value: x000 | 0 0000 (x0h) |

|--------|-----|------|-----|------|------|----------------|--------------|

| 7      | 6   | 5    | 4   | 3    | 2    | 1              | 0            |

| R8     | Т8  | SCID | М   | WAKE | PCE  | PS             | PIE          |

| R/W    | R/W | R/W  | R/W | R/W  | R/W  | R/W            | R/W          |

#### Table 63. SCICR1 register description

| Bit | Name | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|-----|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7   | R8   | Receive data bit 8<br>This bit is used to store the 9th bit of the received word when $M = 1$ .                                                                                                                                                                                                                                                                                                                                                                                                               |

| 6   | Т8   | Transmit data bit 8<br>This bit is used to store the 9th bit of the transmitted word when $M = 1$ .                                                                                                                                                                                                                                                                                                                                                                                                           |

| 5   | SCID | <ul> <li>Disabled for low power consumption</li> <li>When this bit is set the SCI prescalers and outputs are stopped and the end of the current byte transfer in order to reduce power consumption. This bit is set and cleared by software.</li> <li>0: SCI enabled</li> <li>1: SCI prescaler and outputs disabled</li> </ul>                                                                                                                                                                                |

| 4   | М    | <ul> <li>Word length</li> <li>This bit determines the word length. It is set or cleared by software.</li> <li>0: 1 Start bit, 8 data bits, 1 Stop bit</li> <li>1: 1 Start bit, 9 data bits, 1 Stop bit</li> <li>Note: The M bit must not be modified during a data transfer (both transmission and reception).</li> </ul>                                                                                                                                                                                     |

| 3   | WAKE | Wakeup method<br>This bit determines the SCI wakeup method, it is set or cleared by software.<br>0: Idle line<br>1: Address mark                                                                                                                                                                                                                                                                                                                                                                              |

| 2   | PCE  | <ul> <li>Parity control enable</li> <li>This bit selects the hardware parity control (generation and detection). When the parity control is enabled, the computed parity is inserted at the MSB position (9th bit if M = 1; 8th bit if M = 0) and parity is checked on the received data. This bit is set and cleared by software. Once it is set, PCE is active after the current byte (in reception and in transmission).</li> <li>0: Parity control disabled</li> <li>1: Parity control enabled</li> </ul> |

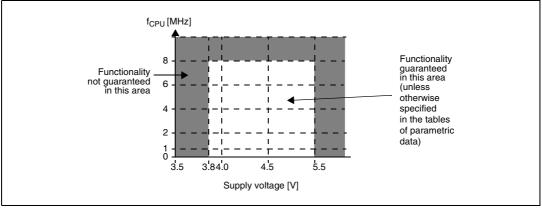

# 12.3 Operating conditions

| Table 86. | Operating | conditions |

|-----------|-----------|------------|

|-----------|-----------|------------|

| Symbol           | Parameter                                    | Conditions                       | Min | Max | Unit |

|------------------|----------------------------------------------|----------------------------------|-----|-----|------|

| f <sub>CPU</sub> | Internal clock frequency                     |                                  | 0   | 8   | MHz  |

| V                | Operating voltage (except Flash Write/Erase) |                                  | 3.8 | 5.5 | v    |

| V <sub>DD</sub>  | Operating Voltage for Flash Write/Erase      | V <sub>PP</sub> = 11.4 to 12.6 V | 4.5 | 5.5 | v    |

|                  |                                              | 1-suffix version                 | 0   | 70  |      |

|                  |                                              | 5-suffix version                 | -10 | 85  |      |

| T <sub>A</sub>   | Ambient temperature range                    | 6-suffix version                 | -40 | 85  | °C   |

|                  |                                              | 7-suffix version                 | -40 | 105 |      |

|                  |                                              | 3-suffix version                 | -40 | 125 |      |

### Figure 64. f<sub>CPU</sub> max versus V<sub>DD</sub>

#### *Note:* Some temperature ranges are only available with a specific package and memory size. Refer to Section 14: Device configuration and ordering information.

Warning: Do not connect 12 V to  $V_{PP}$  before  $V_{DD}$  is powered on, as this may damage the device.

#### **Package characteristics** 13

#### 13.1 ECOPACK

In order to meet environmental requirements, ST offers these devices in different grades of ECOPACK® packages, depending on their level of environmental compliance. ECOPACK® specifications, grade definitions and product status are available at: www.st.com. ECOPACK® is an ST trademark.

#### 13.2 Package mechanical data

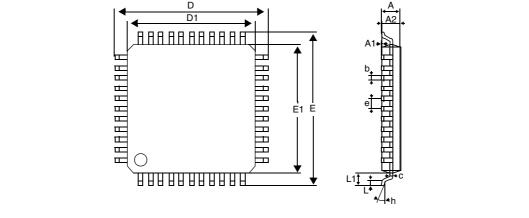

#### 13.2.1 LQFP44 package mechanical data

D D1

Figure 89. 44-pin low profile quad flat package outline

Table 114. 44-pin low profile quad flat package mechanical data

| Dim  |      | mm    |      | inches <sup>(1)</sup> |        |        |  |  |

|------|------|-------|------|-----------------------|--------|--------|--|--|

| Dim. | Min  | Тур   | Max  | Min                   | Тур    | Max    |  |  |

| А    |      |       | 1.60 |                       |        | 0.0630 |  |  |

| A1   | 0.05 |       | 0.15 | 0.0020                |        | 0.0059 |  |  |

| A2   | 1.35 | 1.40  | 1.45 | 0.0531                | 0.0551 | 0.0571 |  |  |

| b    | 0.30 | 0.37  | 0.45 | 0.0118                | 0.0146 | 0.0177 |  |  |

| С    | 0.09 |       | 0.20 | 0.0035                |        | 0.0079 |  |  |

| D    |      | 12.00 |      |                       | 0.4724 |        |  |  |

| D1   |      | 10.00 |      |                       | 0.3937 |        |  |  |

| E    |      | 12.00 |      |                       | 0.4724 |        |  |  |

| Dim  |       | mm    |               | inches <sup>(1)</sup> |        |        |  |  |

|------|-------|-------|---------------|-----------------------|--------|--------|--|--|

| Dim. | Min   | Тур   | Max           | Min                   | Тур    | Max    |  |  |

| Е    | 15.24 |       | 16.00         | 0.6000                |        | 0.6299 |  |  |

| E1   | 12.70 | 13.72 | 14.48         | 0.5000                | 0.5402 | 0.5701 |  |  |

| е    |       | 1.78  |               |                       | 0.0701 |        |  |  |

| eA   |       | 15.24 |               |                       | 0.6000 |        |  |  |

| eB   |       |       | 18.54         |                       |        | 0.7299 |  |  |

| eC   |       |       | 1.52          |                       |        | 0.0598 |  |  |

| L    | 2.54  | 3.30  | 3.56          | 0.1000                | 0.1299 | 0.1402 |  |  |

|      |       | Nu    | umber of pins |                       |        |        |  |  |

| Ν    |       |       | 4             | 2                     |        |        |  |  |

Table 115. 42-pin dual in line package mechanical data

1. Values in inches are converted from mm and rounded to 4 decimal digits.

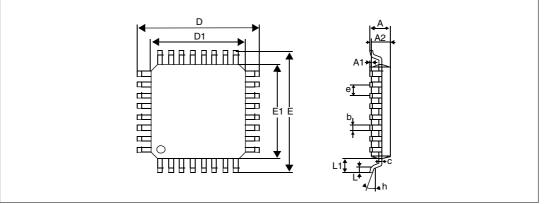

### 13.2.3 LQFP32 package mechanical data

#### Table 116. 32-pin low profile quad flat package mechanical data

| Dim.  |      | mm   |      | inches <sup>(1)</sup> |        |        |  |

|-------|------|------|------|-----------------------|--------|--------|--|

| Dini. | Min  | Тур  | Max  | Min                   | Тур    | Max    |  |

| А     |      |      | 1.60 |                       |        | 0.0630 |  |

| A1    | 0.05 |      | 0.15 | 0.0020                |        | 0.0059 |  |

| A2    | 1.35 | 1.40 | 1.45 | 0.0531                | 0.0551 | 0.0571 |  |

| b     | 0.30 | 0.37 | 0.45 | 0.0118                | 0.0146 | 0.0177 |  |

| С     | 0.09 |      | 0.20 | 0.0035                |        | 0.0079 |  |

| D     |      | 9.00 |      |                       | 0.3543 |        |  |

| D1    |      | 7.00 |      |                       | 0.2756 |        |  |

| Dim  |                | mm    |       | inches <sup>(1)</sup> |        |        |  |

|------|----------------|-------|-------|-----------------------|--------|--------|--|

| Dim. | Min            | Тур   | Max   | Min                   | Тур    | Max    |  |

| Е    | 9.91           | 10.41 | 11.05 | 0.3902                | 0.4098 | 0.4350 |  |

| E1   | 7.62           | 8.89  | 9.40  | 0.3000                | 0.3500 | 0.3701 |  |

| е    |                | 1.78  |       |                       | 0.0701 |        |  |

| eA   |                | 10.16 |       |                       | 0.4000 |        |  |

| eB   |                |       | 12.70 |                       |        | 0.5000 |  |

| eC   |                |       | 1.40  |                       |        | 0.0551 |  |

| L    | 2.54           | 3.05  | 3.81  | 0.1000                | 0.1201 | 0.1500 |  |

|      | Number of pins |       |       |                       |        |        |  |

| Ν    |                | 42    |       |                       |        |        |  |

Table 117. 32-pin dual in-line package mechanical data (continued)

1. Values in inches are converted from mm and rounded to 4 decimal digits.

# 14.1 Flash devices

### 14.1.1 Flash configuration

#### Table 119. Flash option bytes

|         | Static option byte 0 |    |      |   |   |       |       |     |                  | Stati | c optio | on byt | e 1 |      |    |     |

|---------|----------------------|----|------|---|---|-------|-------|-----|------------------|-------|---------|--------|-----|------|----|-----|

|         | 7                    | 6  | 5    | 4 | 3 | 2     | 1     | 0   | 7                | 6     | 5       | 4      | 3   | 2    | 1  | 0   |

|         | WI                   | DG | Res  | V | D | Bosc  | erved | R_R | PKG1             | TC    | OSC     | TYPE   | OS  | CRAN | GE | OFF |

|         | HALT                 | SW | 1103 | 1 | 0 | 11636 | i veu | FMP | i Kui            | RS    | 1       | 0      | 2   | 1    | 0  | PLL |

| Default | 1                    | 1  | 1    | 0 | 0 | 1     | 1     | 1   | See<br>note<br>1 | 1     | 1       | 0      | 0   | 1    | 1  | 1   |

1. Depends on device type as defined in Table 122: Package selection (OPT7) on page 181.

The option bytes allow the hardware configuration of the microcontroller to be selected. They have no address in the memory map and can be accessed only in programming mode (for example using a standard ST7 programming tool). The default content of the Flash is fixed to FFh. To program directly the Flash devices using ICP, Flash devices are shipped to customers with the internal RC clock source. In masked ROM devices, the option bytes are fixed in hardware by the ROM code (see option list).

#### Table 120. Option byte 0 bit description

| Bit    | Name     | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|--------|----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| OPT7   | WDG HALT | <ul> <li>Watchdog reset on Halt</li> <li>This option bit determines if a reset is generated when entering Halt mode while the Watchdog is active.</li> <li>0: No reset generation when entering Halt mode</li> <li>1: Reset generation when entering Halt mode</li> </ul>                                                                                                                                                                                                                                                                                                                                                           |

| OPT6   | WDG SW   | Hardware or software Watchdog<br>This option bit selects the Watchdog type.<br>0: Hardware (Watchdog always enabled)<br>1: Software (Watchdog to be enabled by software)                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| OPT5   | -        | Reserved, must be kept at default value.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| OPT4:3 | VD[1:0]  | Voltage detection<br>These option bits enable the voltage detection block (LVD and AVD)<br>with a selected threshold for the LVD and AVD.<br>00: Selected LVD = Highest threshold ( $V_{DD}$ ~4V).<br>01: Selected LVD = Medium threshold ( $V_{DD}$ ~3.5V).<br>10: Selected LVD = Lowest threshold ( $V_{DD}$ ~3.5V).<br>11: LVD and AVD off<br><b>Caution:</b> If the medium or low thresholds are selected, the detection<br>may occur outside the specified operating voltage range. Below 3.8V,<br>device operation is not guaranteed. For details on the AVD and LVD<br>threshold levels refer to Section 12.4.1 on page 145. |

| OPT2:1 | -        | Reserved, must be kept at default value                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| Bit  | Name    | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|------|---------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| OPT0 | PLL OFF | <ul> <li>PLL activation</li> <li>This option bit activates the PLL which allows multiplication by two of the main input clock frequency. The PLL must not be used with the internal RC oscillator. The PLL is guaranteed only with an input frequency between 2 and 4 MHz.</li> <li>0: PLL x2 enabled</li> <li>1: PLL x2 disabled</li> <li>Caution: The PLL can be enabled only if the "OSCRANGE" (OPT3:1) bits are configured to "MP - 2~4 MHz". Otherwise, the device functionality is not guaranteed.</li> </ul> |

Table 121. Option byte 1 bit description (continued)

#### Table 122. Package selection (OPT7)

| Version | Selected package | PKG1 |

|---------|------------------|------|

| J       | LQFP44/SDIP42    | 1    |

| К       | LQFP32/SDIP32    | 0    |

### 14.2 ROM devices

#### 14.2.1 Transfer of customer code

Customer code is made up of the ROM/FASTROM contents and the list of the selected options (if any). The ROM/FASTROM contents are to be sent with the S19 hexadecimal file generated by the development tool. All unused bytes must be set to FFh. Complete the appended *ST72324Bxx MICROCONTROLLER OPTION LIST on page 182* to communicate the selected options to STMicroelectronics.

Refer to application note AN1635 for information on the counter listing returned by ST after code has been transferred.

*Figure 93: ST72324Bxx ordering information scheme on page 178* serves as a guide for ordering. The STMicroelectronics sales organization will be pleased to provide detailed information on contractual points.

**Caution:** The readout protection binary value is inverted between ROM and Flash products. The option byte checksum differs between ROM and Flash.

#### Nested interrupt context

The symptom does not occur when the interrupts are handled normally, that is, when:

- The interrupt flag is cleared within its own interrupt routine

- The interrupt flag is cleared within any interrupt routine with higher or identical priority level

- The interrupt flag is cleared in any part of the code while this interrupt is disabled

If these conditions are not met, the symptom can be avoided by implementing the following sequence:

- PUSH CC

- SIM

- Reset interrupt flag

- POP CC

#### 15.1.5 16-bit timer PWM mode

In PWM mode, the first PWM pulse is missed after writing the value FFFCh in the OC1R register (OC1HR, OC1LR). It leads to either full or no PWM during a period, depending on the OLVL1 and OLVL2 settings.

### 15.1.6 TIMD set simultaneously with OC interrupt

If the 16-bit timer is disabled at the same time the output compare event occurs then output compare flag gets locked and cannot be cleared before the timer is enabled again.

#### Impact on the application

If output compare interrupt is enabled, then the output compare flag cannot be cleared in the timer interrupt routine. Consequently the interrupt service routine is called repeatedly.

#### Workaround

Disable the timer interrupt before disabling the timer. Again while enabling, first enable the timer then the timer interrupts.

- Perform the following to disable the timer:

- TACR1 or TBCR1 = 0x00h; // Disable the compare interrupt

- TACSR I or TBCSR I = 0x40; // Disable the timer

- Perform the following to enable the timer again:

- TACSR & or TBCSR & = ~0x40; // Enable the timer

- TACR1 or TBCR1 = 0x40; // Enable the compare interrupt

### 15.1.7 SCI wrong break duration

#### Description

A single break character is sent by setting and resetting the SBK bit in the SCICR2 register. In some cases, the break character may have a longer duration than expected:

- 20 bits instead of 10 bits if M = 0

- 22 bits instead of 11 bits if M = 1

| PLL | PA3 | PF4 | PF1 | PF0      | Clock disturbance                                                 |  |

|-----|-----|-----|-----|----------|-------------------------------------------------------------------|--|

| Off | 0   | 1   | 0   | Toggling | Maximum 2 clock cycles lost at each rising or falling edge of PF0 |  |

| On  | 0   | 1   | 0   | 1        | Maximum 1 clock cycle lost out of every 16                        |  |

Table 125. Port A and F configuration

As a consequence, for cycle-accurate operations, these configurations are prohibited in either input or output mode.

#### Workaround

To avoid this from occurring, it is recommended to connect one of these pins to GND (PF4 or PF0) or  $V_{DD}$  (PA3 or PF1).

# 16 Revision history

| Table 126. | Document revision history |

|------------|---------------------------|

|------------|---------------------------|

| Date        | Revision | Changes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |

|-------------|----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| 05-May-2004 | 2.0      | Merged ST72F324 Flash with ST72324B ROM datasheet.<br>Vt POR max modified in <i>Section 12.4 on page 145</i><br>Added <i>Figure 79 on page 164</i><br>Modified V <sub>AREF</sub> min in <i>"10-bit ADC characteristics" on page 168</i><br>Modified I INJ for PB0 in <i>Section 12.9 on page 158</i><br>Added <i>"Clearing active interrupts outside interrupt routine" on page 187</i><br>Modified "32K ROM DEVICES ONLY" on page 165                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |

| 30-Mar-2005 | 3        | Removed Clock Security System (CSS) throughout document<br>Added notes on ST72F324B 8K/16K Flash devices in Table 27<br>Corrected MCO description in <i>Section 10.2 on page 69</i><br>Modified VtPOR in <i>Section 12.4 on page 145</i><br>Static current consumption modified in <i>Section 12.9 on page 158</i><br>Updated footnote and <i>Figure 78 on page 163</i> and <i>Figure 79 on page 164</i><br>Modified Soldering information in <i>Section 13.6</i><br>Updated <i>Section 14 on page 178</i><br>Added Table 27<br>Modified <i>Figure 8 on page 25</i> and note 4 in <i>"Flash program memory" on</i><br><i>page 23</i><br>Added limitation on ICC entry mode with 39 pulses to <i>"Known limitations"</i><br><i>on page 185</i><br>Added Section 16 on page 166 for ST72F324B 8K/16K Flash devices<br>Modified "Internal Sales Types on box label" in Table 29 on page 157 |  |

| 12-Sep-2005 | 4        | Removed notes related to ST72F324, refer to datasheet rev 3 for<br>specifications on older devices.<br>Note: This datasheet rev refers only to ST72F324B and ST72324B.<br>Changed character transmission procedure in <i>Section on page 112</i><br>Updated Vt POR max in <i>Section 12.4 on page 145</i><br>Updated Current Consumption for in <i>Section 12.5 on page 146</i><br>Added oscillator diagram and table to <i>Section 12.6.3 on page 150</i><br>Increased Data retention max. parameter in <i>Section 12.7.2 on page 150</i><br>Updated ordering Section 14.3 on page 155 and Section 14.5 on page<br>157<br>Updated Development tools <i>Section 14.3 on page 183</i><br>Added "external interrupt missed" in <i>Section 15.1 on page 185</i>                                                                                                                             |  |

| 06-Feb-2006 | 5        | Added description of SICSR register at address 2Bh in <i>Table 3 on</i><br>page 20<br>Changed description on port PF2 to add internal pull-up in <i>Section 9.5.1</i><br>on page 63<br>Highlighted note in SPI <i>"Master mode operation" on page 99</i><br>Changed <i>"Static latch-up" on page 157</i><br>Added note 5 on analog input static current consumption <i>"General</i><br><i>characteristics" on page 158</i><br>Updated notes in <i>"Thermal characteristics" on page 177</i>                                                                                                                                                                                                                                                                                                                                                                                              |  |

### Table 126. Document revision history (continued)