#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Obsolete                                                              |

|----------------------------|-----------------------------------------------------------------------|

| Core Processor             | ST7                                                                   |

| Core Size                  | 8-Bit                                                                 |

| Speed                      | 8MHz                                                                  |

| Connectivity               | SCI, SPI                                                              |

| Peripherals                | LVD, POR, PWM, WDT                                                    |

| Number of I/O              | 24                                                                    |

| Program Memory Size        | 32KB (32K x 8)                                                        |

| Program Memory Type        | FLASH                                                                 |

| EEPROM Size                | -                                                                     |

| RAM Size                   | 1K x 8                                                                |

| Voltage - Supply (Vcc/Vdd) | 3.8V ~ 5.5V                                                           |

| Data Converters            | A/D 12x10b                                                            |

| Oscillator Type            | Internal                                                              |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                     |

| Mounting Type              | Through Hole                                                          |

| Package / Case             | 32-SDIP (0.400", 10.16mm)                                             |

| Supplier Device Package    | -                                                                     |

| Purchase URL               | https://www.e-xfl.com/product-detail/stmicroelectronics/st72f324bk6b6 |

|                            |                                                                       |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# Contents

| 1 | Descr                                           | ription .                                                                                                               |                                                                                                                                                                                                                                                                                                                                                                              | 4                                                                       |

|---|-------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------|

| 2 | Pin de                                          | escriptio                                                                                                               | on1                                                                                                                                                                                                                                                                                                                                                                          | 5                                                                       |

| 3 | Regis                                           | ter and                                                                                                                 | memory map                                                                                                                                                                                                                                                                                                                                                                   | 0                                                                       |

| 4 | Flash                                           | progra                                                                                                                  | m memory                                                                                                                                                                                                                                                                                                                                                                     | 3                                                                       |

|   | 4.1                                             | Introduc                                                                                                                | tion                                                                                                                                                                                                                                                                                                                                                                         | 3                                                                       |

|   | 4.2                                             | Main fea                                                                                                                | atures                                                                                                                                                                                                                                                                                                                                                                       | 3                                                                       |

|   | 4.3                                             | Structur                                                                                                                | e                                                                                                                                                                                                                                                                                                                                                                            | 3                                                                       |

|   |                                                 | 4.3.1                                                                                                                   | Readout protection                                                                                                                                                                                                                                                                                                                                                           | 4                                                                       |

|   | 4.4                                             | ICC inte                                                                                                                | rface                                                                                                                                                                                                                                                                                                                                                                        | 5                                                                       |

|   | 4.5                                             | ICP (in-                                                                                                                | circuit programming) 20                                                                                                                                                                                                                                                                                                                                                      | 6                                                                       |

|   | 4.6                                             | IAP (in-a                                                                                                               | application programming) 20                                                                                                                                                                                                                                                                                                                                                  | 6                                                                       |

|   | 4.7                                             | Related                                                                                                                 | documentation                                                                                                                                                                                                                                                                                                                                                                | 6                                                                       |

|   |                                                 | 4.7.1                                                                                                                   | Flash Control/Status Register (FCSR)                                                                                                                                                                                                                                                                                                                                         | 6                                                                       |

|   |                                                 |                                                                                                                         |                                                                                                                                                                                                                                                                                                                                                                              |                                                                         |

| 5 | Centr                                           | al proce                                                                                                                | essing unit (CPU) 27                                                                                                                                                                                                                                                                                                                                                         | 7                                                                       |

| 5 | <b>Centr</b><br>5.1                             | -                                                                                                                       | essing unit (CPU)                                                                                                                                                                                                                                                                                                                                                            |                                                                         |

| 5 |                                                 | Introduc                                                                                                                |                                                                                                                                                                                                                                                                                                                                                                              | 7                                                                       |

| 5 | 5.1                                             | Introduc<br>Main fea                                                                                                    | tion                                                                                                                                                                                                                                                                                                                                                                         | 7<br>7                                                                  |

| 5 | 5.1<br>5.2                                      | Introduc<br>Main fea                                                                                                    | atures                                                                                                                                                                                                                                                                                                                                                                       | 7<br>7<br>7                                                             |

| 5 | 5.1<br>5.2                                      | Introduc<br>Main fea<br>CPU reg                                                                                         | etion                                                                                                                                                                                                                                                                                                                                                                        | 7<br>7<br>8                                                             |

| 5 | 5.1<br>5.2                                      | Introduc<br>Main fea<br>CPU reg<br>5.3.1                                                                                | atures       21         gisters       21         Accumulator (A)       21                                                                                                                                                                                                                                                                                                    | 7<br>7<br>8<br>8                                                        |

| 5 | 5.1<br>5.2                                      | Introduc<br>Main fea<br>CPU reg<br>5.3.1<br>5.3.2                                                                       | atures       21         gisters       21         Accumulator (A)       22         Index registers (X and Y)       24                                                                                                                                                                                                                                                         | 7<br>7<br>8<br>8                                                        |

| 5 | 5.1<br>5.2                                      | Introduc<br>Main fea<br>CPU reg<br>5.3.1<br>5.3.2<br>5.3.3                                                              | atures       21         gisters       21         Accumulator (A)       22         Index registers (X and Y)       24         Program counter (PC)       24                                                                                                                                                                                                                   | 7<br>7<br>8<br>8<br>8                                                   |

| 5 | 5.1<br>5.2<br>5.3                               | Introduc<br>Main fea<br>CPU reg<br>5.3.1<br>5.3.2<br>5.3.3<br>5.3.4<br>5.3.5                                            | atures       21         gisters       21         Accumulator (A)       22         Index registers (X and Y)       22         Program counter (PC)       24         Condition Code register (CC)       24                                                                                                                                                                     | 7<br>7<br>8<br>8<br>8<br>8                                              |

|   | 5.1<br>5.2<br>5.3                               | Introduc<br>Main fea<br>CPU reg<br>5.3.1<br>5.3.2<br>5.3.3<br>5.3.4<br>5.3.5<br><b>y, reset</b>                         | atures       21         gisters       21         Accumulator (A)       22         Index registers (X and Y)       23         Program counter (PC)       24         Condition Code register (CC)       24         Stack Pointer register (SP)       36                                                                                                                        | 7<br>7<br>8<br>8<br>8<br>8<br>8<br>0<br>1                               |

|   | 5.1<br>5.2<br>5.3                               | Introduc<br>Main fea<br>CPU reg<br>5.3.1<br>5.3.2<br>5.3.3<br>5.3.4<br>5.3.5<br><b>y, reset</b><br>Introduc             | atures       21         atures       21         gisters       21         Accumulator (A)       22         Index registers (X and Y)       23         Program counter (PC)       24         Condition Code register (CC)       24         Stack Pointer register (SP)       30         and clock management       31                                                          | 7<br>7<br>8<br>8<br>8<br>8<br>8<br>0<br><b>1</b>                        |

|   | 5.1<br>5.2<br>5.3<br><b>Suppl</b><br>6.1        | Introduc<br>Main fea<br>CPU reg<br>5.3.1<br>5.3.2<br>5.3.3<br>5.3.4<br>5.3.5<br><b>by, reset</b><br>Introduc<br>PLL (ph | atures       21         atures       21         gisters       21         Accumulator (A)       22         Index registers (X and Y)       24         Program counter (PC)       24         Condition Code register (CC)       24         Stack Pointer register (SP)       36         and clock management       37         etion       37                                   | 7<br>7<br>8<br>8<br>8<br>8<br>8<br>0<br><b>1</b><br>1                   |

|   | 5.1<br>5.2<br>5.3<br><b>Suppl</b><br>6.1<br>6.2 | Introduc<br>Main fea<br>CPU reg<br>5.3.1<br>5.3.2<br>5.3.3<br>5.3.4<br>5.3.5<br><b>by, reset</b><br>Introduc<br>PLL (ph | atures       21         atures       21         gisters       21         Accumulator (A)       22         Index registers (X and Y)       24         Program counter (PC)       24         Condition Code register (CC)       24         Stack Pointer register (SP)       36         and clock management       37         etion       37         ase locked loop)       37 | 7<br>7<br>8<br>8<br>8<br>8<br>8<br>8<br>8<br>8<br>8<br>8<br>8<br>0<br>1 |

|    | 9.1  | Introdu  | ction                                                    | 58 |

|----|------|----------|----------------------------------------------------------|----|

|    | 9.2  | Functio  | nal description                                          | 58 |

|    |      | 9.2.1    | Input modes                                              | 58 |

|    |      | 9.2.2    | Output modes                                             | 59 |

|    |      | 9.2.3    | Alternate functions                                      | 59 |

|    | 9.3  | I/O por  | t implementation                                         | 62 |

|    | 9.4  | Low po   | wer modes                                                | 62 |

|    | 9.5  | Interrup | ots                                                      | 62 |

|    |      | 9.5.1    | I/O port implementation                                  | 63 |

| 10 | On-c | hip peri | pherals                                                  | 65 |

|    | 10.1 | Watcho   | dog timer (WDG)                                          | 65 |

|    |      | 10.1.1   | Introduction                                             | 65 |

|    |      | 10.1.2   | Main features                                            | 65 |

|    |      | 10.1.3   | Functional description                                   | 65 |

|    |      | 10.1.4   | How to program the Watchdog timeout                      | 66 |

|    |      | 10.1.5   | Low power modes                                          | 68 |

|    |      | 10.1.6   | Hardware Watchdog option                                 | 68 |

|    |      | 10.1.7   | Using Halt mode with the WDG (WDGHALT option)            | 68 |

|    |      | 10.1.8   | Interrupts                                               | 68 |

|    |      | 10.1.9   | Control register (WDGCR)                                 | 69 |

|    | 10.2 | Main cl  | ock controller with real-time clock and beeper (MCC/RTC) | 69 |

|    |      | 10.2.1   | Programmable CPU clock prescaler                         | 69 |

|    |      | 10.2.2   | Clock-out capability                                     | 70 |

|    |      | 10.2.3   | Real-time clock (RTC) timer                              | 70 |

|    |      | 10.2.4   | Beeper                                                   | 70 |

|    |      | 10.2.5   | Low power modes                                          | 71 |

|    |      | 10.2.6   | Interrupts                                               | 71 |

|    |      | 10.2.7   | MCC registers                                            | 71 |

|    | 10.3 | 16-bit t | imer                                                     | 74 |

|    |      | 10.3.1   | Introduction                                             | 74 |

|    |      | 10.3.2   | Main features                                            | 74 |

|    |      | 10.3.3   | Functional description                                   | 75 |

|    |      | 10.3.4   | Low power modes                                          | 88 |

|    |      | 10.3.5   | Interrupts                                               | 88 |

|    |      | 10.3.6   | Summary of timer modes                                   | 89 |

16

|      | 15.1.1  | Safe connection of OSC1/OSC2 pins                    | 185 |

|------|---------|------------------------------------------------------|-----|

|      | 15.1.2  | External interrupt missed                            | 185 |

|      | 15.1.3  | Unexpected reset fetch                               | 187 |

|      | 15.1.4  | Clearing active interrupts outside interrupt routine | 187 |

|      | 15.1.5  | 16-bit timer PWM mode                                | 188 |

|      | 15.1.6  | TIMD set simultaneously with OC interrupt            | 188 |

|      | 15.1.7  | SCI wrong break duration                             | 188 |

| 15.2 | 8/16 Kt | byte Flash devices only                              | 189 |

|      | 15.2.1  | 39-pulse ICC entry mode                              | 189 |

|      | 15.2.2  | Negative current injection on pin PB0                | 189 |

| 15.3 | 8/16 Kt | byte ROM devices only                                | 189 |

|      | 15.3.1  | Readout protection with LVD                          | 189 |

|      | 15.3.2  | I/O Port A and F configuration                       | 100 |

# 8 Power saving modes

# 8.1 Introduction

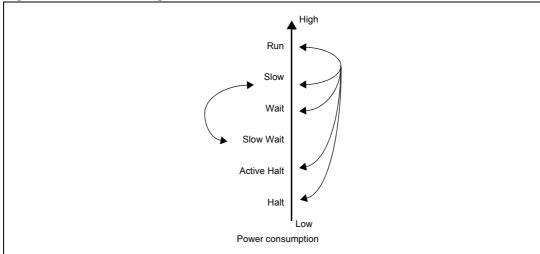

To give a large measure of flexibility to the application in terms of power consumption, four main power saving modes are implemented in the ST7 (see *Figure 23*): Slow, Wait (Slow Wait), Active-halt and Halt.

After a reset the normal operating mode is selected by default (Run mode). This mode drives the device (CPU and embedded peripherals) by means of a master clock which is based on the main oscillator frequency divided or multiplied by 2 (f<sub>OSC2</sub>).

From Run mode, the different power saving modes may be selected by setting the relevant register bits or by calling the specific ST7 software instruction whose action depends on the oscillator status.

Figure 23. Power saving mode transitions

# 8.2 Slow mode

This mode has two targets:

- To reduce power consumption by decreasing the internal clock in the device,

- To adapt the internal clock frequency (f<sub>CPU</sub>) to the available supply voltage.

Slow mode is controlled by three bits in the MCCSR register: the SMS bit which enables or disables Slow mode and two CPx bits which select the internal slow frequency ( $f_{CPU}$ ).

In this mode, the master clock frequency ( $f_{OSC2}$ ) can be divided by 2, 4, 8 or 16. The CPU and peripherals are clocked at this lower frequency ( $f_{CPU}$ ).

Note: Slow-Wait mode is activated when entering the Wait mode while the device is already in Slow mode.

57

| Bit | Name    | Function                                                                                                                                                                                                                                                                                                                                                                                                         |

|-----|---------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 6:5 | CP[1:0] | CPU Clock Prescaler<br>These bits select the CPU clock prescaler which is applied in different slow modes.<br>Their action is conditioned by the setting of the SMS bit. These two bits are set and<br>cleared by software:<br>00: $f_{CPU}$ in Slow mode = $f_{OSC2}/2$<br>01: $f_{CPU}$ in Slow mode = $f_{OSC2}/4$<br>10: $f_{CPU}$ in Slow mode = $f_{OSC2}/8$<br>11: $f_{CPU}$ in Slow mode = $f_{OSC2}/16$ |

| 4   | SMS     | <ul> <li>Slow Mode Select</li> <li>This bit is set and cleared by software.</li> <li>0: Normal mode. f<sub>CPU</sub> = f<sub>OSC2</sub>.</li> <li>1: Slow mode. f<sub>CPU</sub> is given by CP1, CP0.</li> <li>See Section 8.2: Slow mode and Section 10.2: Main clock controller with real-time clock and beeper (MCC/RTC) for more details.</li> </ul>                                                         |

| 3:2 | TB[1:0] | Time Base control<br>These bits select the programmable divider time base. They are set and cleared by<br>software (see <i>Table 40</i> ). A modification of the time base is taken into account at the<br>end of the current period (previously set) to avoid an unwanted time shift. This<br>allows to use this time base as a real-time clock.                                                                |

| 1   | OIE     | Oscillator interrupt Enable<br>This bit set and cleared by software.<br>0: Oscillator interrupt disabled<br>1: Oscillator interrupt enabled<br>This interrupt can be used to exit from Active-halt mode. When this bit is set, calling<br>the ST7 software HALT instruction enters the Active-halt power saving mode.                                                                                            |

| 0   | OIF     | Oscillator interrupt Flag<br>This bit is set by hardware and cleared by software reading the MCCSR register. It<br>indicates when set that the main oscillator has reached the selected elapsed time<br>(TB1:0).<br>0: Timeout not reached<br>1: Timeout reached<br><b>Caution</b> : The BRES and BSET instructions must not be used on the MCCSR<br>register to avoid unintentionally clearing the OIF bit.     |

Table 39.

MCCSR register description (continued)

|  | Table 40. | Time base selection |  |

|--|-----------|---------------------|--|

|--|-----------|---------------------|--|

| Counter prescaler | Time                      | base                      | - TB1 | тво  |

|-------------------|---------------------------|---------------------------|-------|------|

|                   | f <sub>OSC2</sub> = 4 MHz | f <sub>OSC2</sub> = 8 MHz |       | 1 BU |

| 16000             | 4 ms                      | 2 ms                      | 0     | 0    |

| 32000             | 8 ms                      | 4 ms                      | 0     | 1    |

| 80000             | 20 ms                     | 10 ms                     | 1     | 0    |

| 200000            | 50 ms                     | 25 ms                     | 1     | 1    |

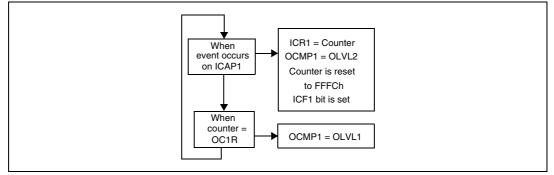

### One Pulse mode

One Pulse mode enables the generation of a pulse when an external event occurs. This mode is selected via the OPM bit in the CR2 register.

The one pulse mode uses the Input Capture1 function and the Output Compare1 function.

### Procedure

To use One Pulse mode:

- 1. Load the OC1R register with the value corresponding to the length of the pulse (see the formula below).

- 2. Select the following in the CR1 register:

- Using the OLVL1 bit, select the level to be applied to the OCMP1 pin after the pulse.

- Using the OLVL2 bit, select the level to be applied to the OCMP1 pin during the pulse.

- Select the edge of the active transition on the ICAP1 pin with the IEDG1 bit (the ICAP1 pin must be configured as floating input).

- 3. Select the following in the CR2 register:

- Set the OC1E bit, the OCMP1 pin is then dedicated to the Output Compare 1 function.

- Set the OPM bit.

- Select the timer clock CC[1:0] (see *Table 50*).

### Figure 46. One pulse mode cycle

Then, on a valid event on the ICAP1 pin, the counter is initialized to FFFCh and OLVL2 bit is loaded on the OCMP1 pin, the ICF1 bit is set and the value FFFDh is loaded in the IC1R register.

Because the ICF1 bit is set when an active edge occurs, an interrupt can be generated if the ICIE bit is set.

Clearing the Input Capture interrupt request (that is, clearing the ICF*i* bit) is done in two steps:

- 1. Reading the SR register while the ICF*i* bit is set.

- 2. An access (read or write) to the IC*i*LR register.

| Address<br>(Hex.)          | Register<br>label    | 7        | 6 | 5 | 4 | 3 | 2 | 1 | 0        |

|----------------------------|----------------------|----------|---|---|---|---|---|---|----------|

| Timer A: 36<br>Timer B: 46 | OC1HR<br>Reset value | MSB<br>1 | 0 | 0 | 0 | 0 | 0 | 0 | LSB<br>0 |

| Timer A: 37<br>Timer B: 47 | OC1LR<br>Reset value | MSB<br>0 | 0 | 0 | 0 | 0 | 0 | 0 | LSB<br>0 |

| Timer A: 3E<br>Timer B: 4E | OC2HR<br>Reset value | MSB<br>1 | 0 | 0 | 0 | 0 | 0 | 0 | LSB<br>0 |

| Timer A: 3F<br>Timer B: 4F | OC2LR<br>Reset value | MSB<br>0 | 0 | 0 | 0 | 0 | 0 | 0 | LSB<br>0 |

| Timer A: 38<br>Timer B: 48 | CHR<br>Reset value   | MSB<br>1 | 1 | 1 | 1 | 1 | 1 | 1 | LSB<br>1 |

| Timer A: 39<br>Timer B: 49 | CLR<br>Reset value   | MSB<br>1 | 1 | 1 | 1 | 1 | 1 | 0 | LSB<br>0 |

| Timer A: 3A<br>Timer B: 4A | ACHR<br>Reset value  | MSB<br>1 | 1 | 1 | 1 | 1 | 1 | 1 | LSB<br>1 |

| Timer A: 3B<br>Timer B: 4B | ACLR<br>Reset value  | MSB<br>1 | 1 | 1 | 1 | 1 | 1 | 0 | LSB<br>0 |

| Timer A: 3C<br>Timer B: 4C | IC2HR<br>Reset value | MSB<br>x | x | x | x | x | x | x | LSB<br>x |

| Timer A: 3D<br>Timer B: 4D | IC2LR<br>Reset value | MSB<br>x | x | x | х | х | x | x | LSB<br>x |

Table 52. 16-bit timer register map and reset values (continued)

# **10.4** Serial peripheral interface (SPI)

### 10.4.1 Introduction

The serial peripheral interface (SPI) allows full-duplex, synchronous, serial communication with external devices. An SPI system may consist of a master and one or more slaves. However, the SPI interface can not be a master in a multi-master system.

# 10.4.2 Main features

- Full duplex synchronous transfers (on 3 lines)

- Simplex synchronous transfers (on 2 lines)

- Master or slave operation

- 6 master mode frequencies (f<sub>CPU</sub>/4 max.)

- f<sub>CPU</sub>/2 max. slave mode frequency (see note)

- SS Management by software or hardware

- Programmable clock polarity and phase

- End of transfer interrupt flag

- Write collision, Master mode fault and Overrun flags

Note: In slave mode, continuous transmission is not possible at maximum frequency due to the software overhead for clearing status flags and to initiate the next transmission sequence.

|                       | 4    |      |      |

|-----------------------|------|------|------|

| Serial clock          | SPR2 | SPR1 | SPR0 |

| f <sub>CPU</sub> /16  | 0    | 0    | 1    |

| f <sub>CPU</sub> /32  | 1    | 1    | 0    |

| f <sub>CPU</sub> /64  | 0    | 1    | 0    |

| f <sub>CPU</sub> /128 | 0    | 1    | 1    |

Table 56.

SPI master mode SCK frequency (continued)

# SPI control/status register (SPICSR)

| SPICSR |      |     |      |          | Rese | et value: 0000 | 0000 (00h) 0000 |

|--------|------|-----|------|----------|------|----------------|-----------------|

| 7      | 6    | 5   | 4    | 3        | 2    | 1              | 0               |

| SPIF   | WCOL | OVR | MODF | Reserved | SOD  | SSM            | SSI             |

| RO     | RO   | RO  | RO   | -        | R/W  | R/W            | R/W             |

# Table 57.SPICSR register description

| Bit | Name | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|-----|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7   | SPIF | <ul> <li>Serial peripheral data transfer flag</li> <li>This bit is set by hardware when a transfer has been completed. An interrupt is generated if SPIE = 1 in the SPICR register. It is cleared by a software sequence (an access to the SPICSR register followed by a write or a read to the SPIDR register).</li> <li>0: Data transfer is in progress or the flag has been cleared</li> <li>1: Data transfer between the device and an external device has been completed. <i>Note: While the SPIF bit is set, all writes to the SPIDR register are inhibited until the SPICSR register is read.</i></li> </ul> |

| 6   | WCOL | <ul> <li>Write collision status</li> <li>This bit is set by hardware when a write to the SPIDR register is done during a transmit sequence. It is cleared by a software sequence (see <i>Figure 55</i>).</li> <li>0: No write collision occurred</li> <li>1: A write collision has been detected.</li> </ul>                                                                                                                                                                                                                                                                                                        |

| 5   | OVR  | <ul> <li>SPI Overrun error</li> <li>This bit is set by hardware when the byte currently being received in the shift register is ready to be transferred into the SPIDR register while SPIF = 1 (see <i>Overrun condition (OVR) on page 102</i>). An interrupt is generated if SPIE = 1 in SPICR register. The OVR bit is cleared by software reading the SPICSR register.</li> <li>0: No overrun error</li> <li>1: Overrun error detected</li> </ul>                                                                                                                                                                |

| 4   | MODF | <ul> <li>Mode fault flag</li> <li>This bit is set by hardware when the SS pin is pulled low in master mode (see <i>Master mode fault (MODF) on page 102</i>). An SPI interrupt can be generated if SPIE = 1 in the SPICSR register. This bit is cleared by a software sequence (An access to the SPICR register while MODF = 1 followed by a write to the SPICR register).</li> <li>0: No master mode fault detected</li> <li>1: A fault in master mode has been detected.</li> </ul>                                                                                                                               |

| 3   | -    | Reserved, must be kept cleared.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

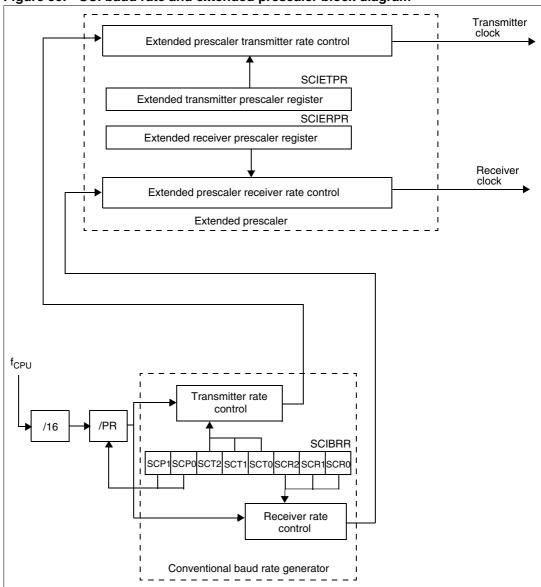

Figure 59. SCI baud rate and extended prescaler block diagram

#### **Framing error**

A framing error is detected when:

- The stop bit is not recognized on reception at the expected time, following either a desynchronization or excessive noise.

- A break is received.

When the framing error is detected:

- the FE bit is set by hardware

- Data is transferred from the Shift register to the SCIDR register.

- No interrupt is generated. However this bit rises at the same time as the RDRF bit which itself generates an interrupt.

The FE bit is reset by a SCISR register read operation followed by a SCIDR register read operation.

### **Clock deviation causes**

The causes which contribute to the total deviation are:

- D<sub>TRA</sub>: Deviation due to transmitter error (local oscillator error of the transmitter or the transmitter is transmitting at a different baud rate).

- D<sub>QUANT</sub>: Error due to the baud rate quantization of the receiver.

- D<sub>REC</sub>: Deviation of the local oscillator of the receiver: This deviation can occur during the reception of one complete SCI message assuming that the deviation has been compensated at the beginning of the message.

- D<sub>TCL</sub>: Deviation due to the transmission line (generally due to the transceivers)

All the deviations of the system should be added and compared to the SCI clock tolerance:

$$D_{TRA} + D_{QUANT} + D_{REC} + D_{TCL} < 3.75\%$$

### Noise error causes

See also the description of Noise error in Receiver on page 113.

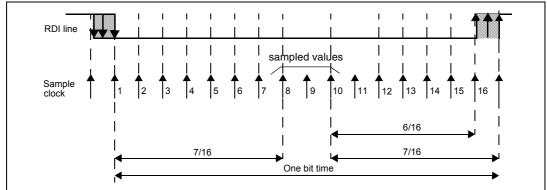

#### Start bit

The Noise Flag (NF) is set during start bit reception if one of the following conditions occurs:

- 1. A valid falling edge is not detected. A falling edge is considered to be valid if the three consecutive samples before the falling edge occurs are detected as '1' and, after the falling edge occurs, during the sampling of the 16 samples, if one of the samples numbered 3, 5 or 7 is detected as a '1'.

- 2. During sampling of the 16 samples, if one of the samples numbered 8, 9 or 10 is detected as a '1'.

Therefore, a valid Start bit must satisfy both the above conditions to prevent the Noise Flag from being set.

#### Data bits

The Noise Flag (NF) is set during normal data bit reception if the following condition occurs: During the sampling of 16 samples, if all three samples numbered 8, 9 and 10 are not the same. The majority of the 8th, 9th and 10th samples is considered as the bit value.

Therefore, a valid Data bit must have samples 8, 9 and 10 at the same value to prevent the Noise Flag from being set.

# 10.5.5 Low power modes

Table 60. Effect of low power modes on SCI

| Mode | Description                                                                                                |

|------|------------------------------------------------------------------------------------------------------------|

| Wait | No effect on SCI.<br>SCI interrupts cause the device to exit from Wait mode.                               |

| Halt | SCI registers are frozen.<br>In Halt mode, the SCI stops transmitting/receiving until Halt mode is exited. |

# 10.5.6 Interrupts

The SCI interrupt events are connected to the same interrupt vector.

These events generate an interrupt if the corresponding Enable Control bit is set and the interrupt mask in the CC register is reset (RIM instruction).

Table 61. SCI interrupt control/wakeup capability

| Interrupt event                | Event flag | Enable control bit | Exit from Wait | Exit from Halt |

|--------------------------------|------------|--------------------|----------------|----------------|

| Transmit data register empty   | TDRE       | TIE                | Yes            | No             |

| Transmission complete          | TC         | TCIE               | Yes            | No             |

| Received data ready to be read | RDRF       | BIE                | Yes            | No             |

| Overrun error detected         | OR         |                    | Yes            | No             |

| Idle line detected             | IDLE       | ILIE               | Yes            | No             |

| Parity error                   | PE         | PIE                | Yes            | No             |

# 10.5.7 SCI registers

### SCI status register (SCISR)

| SCISR Reset value: 1100 0000 (C0h |      |    |      |      |    |    | 0000 (C0h) |    |

|-----------------------------------|------|----|------|------|----|----|------------|----|

|                                   | 7    | 6  | 5    | 4    | 3  | 2  | 1          | 0  |

|                                   | TDRE | тс | RDRF | IDLE | OR | NF | FE         | PE |

|                                   | RO   | RO | RO   | RO   | RO | RO | RO         | RO |

### Table 62. SCISR register description

| Bit | Name | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|-----|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7   | TDRE | <ul> <li>Transmit Data Register Empty</li> <li>This bit is set by hardware when the content of the TDR register has been transferred into the shift register. An interrupt is generated if the TIE bit = 1 in the SCICR2 register. It is cleared by a software sequence (an access to the SCISR register followed by a write to the SCIDR register).</li> <li>0: Data is not transferred to the shift register.</li> <li>1: Data is transferred to the shift register.</li> <li>Note: Data will not be transferred to the shift register unless the TDRE bit is cleared.</li> </ul> |

| Bit | Name | Function                                                                                                                                                                                                                                                                                                                                                    |

|-----|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0   | PE   | <ul> <li>Parity error</li> <li>This bit is set by hardware when a parity error occurs in receiver mode. It is cleared by a software sequence (a read to the status register followed by an access to the SCIDR data register). An interrupt is generated if PIE = 1 in the SCICR1 register.</li> <li>0: No parity error</li> <li>1: Parity error</li> </ul> |

# SCI Control Register 1 (SCICR1)

| SCICR1 |     |      |     |      | Rese | et value: x000 | 0 0000 (x0h) |

|--------|-----|------|-----|------|------|----------------|--------------|

| 7      | 6   | 5    | 4   | 3    | 2    | 1              | 0            |

| R8     | Т8  | SCID | М   | WAKE | PCE  | PS             | PIE          |

| R/W    | R/W | R/W  | R/W | R/W  | R/W  | R/W            | R/W          |

### Table 63. SCICR1 register description

| Bit | Name | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |  |  |  |

|-----|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| 7   | R8   | Receive data bit 8<br>This bit is used to store the 9th bit of the received word when $M = 1$ .                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |  |  |

| 6   | Т8   | Transmit data bit 8<br>This bit is used to store the 9th bit of the transmitted word when $M = 1$ .                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |  |  |

| 5   | SCID | <ul> <li>Disabled for low power consumption</li> <li>When this bit is set the SCI prescalers and outputs are stopped and the end of the current byte transfer in order to reduce power consumption. This bit is set and cleared by software.</li> <li>0: SCI enabled</li> <li>1: SCI prescaler and outputs disabled</li> </ul>                                                                                                                                                                                |  |  |  |  |

| 4   | М    | <ul> <li>Word length</li> <li>This bit determines the word length. It is set or cleared by software.</li> <li>0: 1 Start bit, 8 data bits, 1 Stop bit</li> <li>1: 1 Start bit, 9 data bits, 1 Stop bit</li> <li>Note: The M bit must not be modified during a data transfer (both transmission and reception).</li> </ul>                                                                                                                                                                                     |  |  |  |  |

| 3   | WAKE | Wakeup method<br>This bit determines the SCI wakeup method, it is set or cleared by software.<br>0: Idle line<br>1: Address mark                                                                                                                                                                                                                                                                                                                                                                              |  |  |  |  |

| 2   | PCE  | <ul> <li>Parity control enable</li> <li>This bit selects the hardware parity control (generation and detection). When the parity control is enabled, the computed parity is inserted at the MSB position (9th bit if M = 1; 8th bit if M = 0) and parity is checked on the received data. This bit is set and cleared by software. Once it is set, PCE is active after the current byte (in reception and in transmission).</li> <li>0: Parity control disabled</li> <li>1: Parity control enabled</li> </ul> |  |  |  |  |

### 12.1.5 Pin input voltage

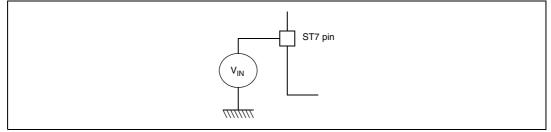

The input voltage measurement on a pin of the device is described in Figure 63.

### Figure 63. Pin input voltage

# 12.2 Absolute maximum ratings

Stresses above those listed as "absolute maximum ratings" may cause permanent damage to the device. This is a stress rating only and functional operation of the device under these conditions is not implied. Exposure to maximum rating conditions for extended periods may affect device reliability.

# 12.2.1 Voltage characteristics

#### Table 83.Voltage characteristics

| Symbol                                    | Ratings                                               | Maximum value                                     | Unit                   |  |  |

|-------------------------------------------|-------------------------------------------------------|---------------------------------------------------|------------------------|--|--|

| V <sub>DD</sub> - V <sub>SS</sub>         | V <sub>DD</sub> - V <sub>SS</sub> Supply voltage      |                                                   |                        |  |  |

| V <sub>PP</sub> - V <sub>SS</sub>         | V <sub>PP</sub> - V <sub>SS</sub> Programming voltage |                                                   | Programming voltage 13 |  |  |

|                                           | Input voltage on true open drain pin                  | V <sub>SS</sub> - 0.3 to 6.5                      | V                      |  |  |

| V <sub>IN</sub> <sup>(1)(2)</sup>         | Input voltage on any other pin                        | V <sub>SS</sub> - 0.3 to<br>V <sub>DD</sub> + 0.3 |                        |  |  |

| $ \Delta V_{DDx} $ and $ \Delta V_{SSx} $ | Variations between different digital power pins       | 50                                                | mV                     |  |  |

| IV <sub>SSA</sub> - V <sub>SSx</sub> I    | Variations between digital and analog ground pins     | 50                                                | IIIV                   |  |  |

| V <sub>ESD(HBM)</sub>                     | Electrostatic discharge voltage (human body model)    | see Section 12.8.                                 | 3 on                   |  |  |

| V <sub>ESD(MM)</sub>                      | Electrostatic discharge voltage (machine model)       | page 157                                          |                        |  |  |

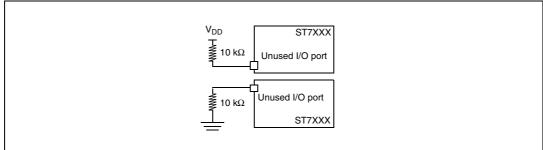

Directly connecting the RESET and I/O pins to V<sub>DD</sub> or V<sub>SS</sub> could damage the device if an unintentional internal reset is generated or an unexpected change of the I/O configuration occurs (for example, due to a corrupted program counter). To guarantee safe operation, this connection has to be done through a pull-up or pull-down resistor (typical: 4.7 kΩ for RESET, 10 kΩ for I/Os). For the same reason, unused I/O pins must not be directly tied to V<sub>DD</sub> or V<sub>SS</sub>.

2.  $I_{INJ(PIN)}$  must never be exceeded. This is implicitly ensured if  $V_{IN}$  maximum is respected. If  $V_{IN}$  maximum cannot be respected, the injection current must be limited externally to the  $I_{INJ(PIN)}$  value. A positive injection is induced by  $V_{IN} > V_{DD}$  while a negative injection is induced by  $V_{IN} < V_{SS}$ . For true open-drain pads, there is no positive injection current, and the corresponding  $V_{IN}$  maximum must always be respected.

### 12.5.3 Supply and clock managers

The previous current consumption specified for the ST7 functional operating modes over temperature range does not take into account the clock source current consumption. To obtain the total device consumption, the two current values must be added (except for Halt mode).

|                        |                                                          | -             |     |                     |      |

|------------------------|----------------------------------------------------------|---------------|-----|---------------------|------|

| Symbol                 | Parameter                                                | Conditions    | Тур | Мах                 | Unit |

| I <sub>DD(RCINT)</sub> | Supply current of internal RC oscillator                 |               | 625 |                     |      |

| I <sub>DD(RES)</sub>   | Supply current of resonator oscillator <sup>(1)(2)</sup> |               |     | on 12.6.3<br>ge 150 | μA   |

| I <sub>DD(PLL)</sub>   | PLL supply current                                       | V – 5V        | 360 |                     |      |

| I <sub>DD(LVD)</sub>   | LVD supply current                                       | $V_{DD} = 5V$ | 150 | 300                 |      |

Table 91. Oscillators, PLL and LVD current consumption

1. Data based on characterization results done with the external components specified in *Section 12.6.3*, not tested in production.

2. As the oscillator is based on a current source, the consumption does not depend on the voltage.

### 12.5.4 On-chip peripherals

#### Table 92. On-chip peripherals current consumption

| Symbol               | Parameter                                         | Conditions                                        | Тур | Unit |

|----------------------|---------------------------------------------------|---------------------------------------------------|-----|------|

| I <sub>DD(TIM)</sub> | 16-bit timer supply current <sup>(1)</sup>        |                                                   | 50  |      |

| I <sub>DD(SPI)</sub> | SPI supply current <sup>(2)</sup>                 | T <sub>A</sub> = 25 °C, f <sub>CPU</sub> = 4 MHz, |     | μA   |

| I <sub>DD(SCI)</sub> | SCI supply current <sup>(3)</sup>                 | V <sub>DD</sub> = 5.0 V                           | 400 | μΑ   |

| I <sub>DD(ADC)</sub> | ADC supply current when converting <sup>(4)</sup> |                                                   |     |      |

1. Data based on a differential  $I_{DD}$  measurement between reset configuration (timer counter running at  $f_{CPU}/4$ ) and timer counter stopped (only TIMD bit set). Data valid for one timer.

Data based on a differential I<sub>DD</sub> measurement between reset configuration (SPI disabled) and a permanent SPI master communication at maximum speed (data sent equal to 55h). This measurement includes the pad toggling consumption.

3. Data based on a differential  $I_{DD}$  measurement between SCI low power state (SCID = 1) and a permanent SCI data transmit sequence.

4. Data based on a differential  ${\rm I}_{\rm DD}$  measurement between reset configuration and continuous A/D conversions.

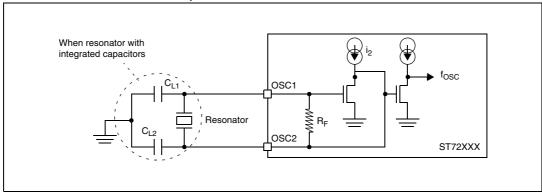

# Figure 66. Typical application with a crystal or ceramic resonator (8/16 Kbyte Flash and ROM devices)

### 32 Kbyte Flash and ROM devices

# Table 96. Crystal and ceramic resonator oscillators (32 Kbyte Flash and ROM devices)

| Symbol                             | Parameter                                                                                                          | Conditions                                                                                                                  | Min                  | Тур                     | Max                      | Unit |

|------------------------------------|--------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------|----------------------|-------------------------|--------------------------|------|

| f <sub>OSC</sub>                   | Oscillator frequency <sup>(1)</sup>                                                                                |                                                                                                                             | 1                    |                         | 16                       | MHz  |

| R <sub>F</sub>                     | Feedback resistor <sup>(2)</sup>                                                                                   |                                                                                                                             | 20                   |                         | 40                       | kΩ   |

| C <sub>L1</sub><br>C <sub>L2</sub> | Recommended load capacitance versus equivalent serial resistance of the crystal or ceramic resonator $(R_S)^{(3)}$ |                                                                                                                             | 20<br>20<br>15<br>15 |                         | 60<br>50<br>35<br>35     | pF   |

| i <sub>2</sub>                     | OSC2 driving current                                                                                               | V <sub>DD</sub> = 5V, V <sub>IN</sub> = V <sub>SS</sub><br>LP oscillator<br>MP oscillator<br>MS oscillator<br>HS oscillator |                      | 80<br>160<br>310<br>610 | 150<br>250<br>460<br>910 | μΑ   |

1. The oscillator selection can be optimized in terms of supply current using an high quality resonator with small RS value. Refer to crystal/ceramic resonator manufacturer for more details.

- Data based on characterization results, not tested in production. The relatively low value of the RF resistor, offers a good protection against issues resulting from use in a humid environment, due to the induced leakage and the bias condition change. However, it is recommended to take this point into account if the microcontroller is used in tough humidity conditions.

- 3. For  $C_{L1}$  and  $C_{L2}$  it is recommended to use high-quality ceramic capacitors in the 5-pF to 25-pF range (typ.) designed for high-frequency applications and selected to match the requirements of the crystal or resonator.  $C_{L1}$  and  $C_{L2}$ , are usually the same size. The crystal manufacturer typically specifies a load capacitance which is the series combination of  $C_{L1}$  and  $C_{L2}$ . PCB and MCU pin capacitance must be included when sizing  $C_{L1}$  and  $C_{L2}$  (10 pF can be used as a rough estimate of the combined pin and board capacitance).

1. I/O can be left unconnected if it is configured as output (0 or 1) by the software. This has the advantage of greater EMC robustness and lower cost.

## 12.9.2 Output driving current

Subject to general operating conditions for  $V_{\text{DD}},\,f_{\text{CPU}},$  and  $T_{\text{A}}$  unless otherwise specified.

| Table 107. | Output | driving | current |

|------------|--------|---------|---------|

|------------|--------|---------|---------|

| Symbol                         | Parameter                                                                                                                  | Cor                  | nditions                                                                                  | Min                                            | Max        | Unit |

|--------------------------------|----------------------------------------------------------------------------------------------------------------------------|----------------------|-------------------------------------------------------------------------------------------|------------------------------------------------|------------|------|

|                                | Output low level voltage for a standard I/O pin when 8 pins are sunk at same time                                          |                      | I <sub>IO</sub> = +5 mA                                                                   |                                                | 1.2        |      |

|                                | (see <i>Figure 72</i> )                                                                                                    |                      | $I_{IO} = +2 \text{ mA}$                                                                  |                                                | 0.5        |      |

| V <sub>OL</sub> <sup>(1)</sup> | Output low level voltage for a high sink I/O<br>pin when 4 pins are sunk at same time                                      | V <sub>DD</sub> = 5V | $I_{IO} = +20 \text{ mA}$<br>$T_A \le 85 \ ^\circ\text{C}$<br>$T_A > 85 \ ^\circ\text{C}$ |                                                | 1.3<br>1.5 | v    |

|                                | (see Figure 73 and Figure 75)                                                                                              | •00=0•               | I <sub>IO</sub> = +8 mA                                                                   |                                                | 0.6        |      |

|                                | Output high level voltage for an I/O pin when 4 pins are sourced at same time (see <i>Figure 74</i> and <i>Figure 77</i> ) |                      | I <sub>IO</sub> = -5 mA,<br>T <sub>A</sub> ≤ 85 °C<br>T <sub>A</sub> > 85 °C              | V <sub>DD</sub> - 1.4<br>V <sub>DD</sub> - 1.6 |            |      |

|                                | (See rigule /4 and rigule //)                                                                                              |                      | I <sub>IO</sub> = -2 mA                                                                   | V <sub>DD</sub> - 0.7                          |            |      |

The I<sub>IO</sub> current sunk must always respect the absolute maximum rating specified in Section 12.2.2 and the sum of I<sub>IO</sub> (I/O ports and control pins) must not exceed I<sub>VSS</sub>.

2. The I<sub>IO</sub> current sourced must always respect the absolute maximum rating specified in Section 12.2.2 and the sum of I<sub>IO</sub> (I/O ports and control pins) must not exceed I<sub>VDD</sub>. True open drain I/O pins do not have V<sub>OH</sub>.

# **12.12** Communication interface characteristics

# 12.12.1 Serial peripheral interface (SPI)

The following characteristics are ubject to general operating conditions for  $V_{DD}$ ,  $f_{CPU}$ , and  $T_A$  unless otherwise specified. The data is based on design simulation and/or characterization results, not tested in production.

When no communication is on-going the data output line of the SPI (MOSI in master mode, MISO in slave mode) has its alternate function capability released. In this case, the pin status depends on the I/O port configuration. Refer to the I/O port characteristics for more details on the input/output alternate function characteristics (SS, SCK, MOSI, MISO).

| Symbol                                                                   | Parameter                    | Conditions                      | Min                            | Мах                 | Unit |  |

|--------------------------------------------------------------------------|------------------------------|---------------------------------|--------------------------------|---------------------|------|--|

| f <sub>SCK</sub>                                                         | SPI clock frequency          | Master f <sub>CPU</sub> = 8 MHz | f <sub>CPU</sub> /128 = 0.0625 | $f_{CPU}/4 = 2$     | MHz  |  |

| 1/t <sub>c(SCK)</sub>                                                    | SPI Clock frequency          | Slave f <sub>CPU</sub> = 8 MHz  | 0                              | $f_{CPU}/2 = 4$     |      |  |

| t <sub>r(SCK)</sub><br>t <sub>f(SCK)</sub>                               | SPI clock rise and fall time |                                 | see I/O po                     | ort pin description |      |  |

| $t_{su(\overline{SS})}^{(1)}$                                            | SS setup time <sup>(2)</sup> | Slave                           | t <sub>CPU</sub> + 50          |                     |      |  |

| $t_{h(\overline{SS})}^{(1)}$                                             | SS hold time                 | Slave                           | 120                            |                     |      |  |

| t <sub>w(SCKH)</sub> (1)<br>t <sub>w(SCKL)</sub> (1)                     | SCK high and low time        | Master                          | 100                            |                     |      |  |

|                                                                          | 5                            | Slave                           | 90                             |                     | -    |  |

| t <sub>su(MI)</sub> <sup>(1)</sup><br>t <sub>su(SI)</sub> <sup>(1)</sup> | Data input setup time        | Master<br>Slave                 | 100<br>100                     |                     |      |  |

| $\frac{t_{h(MI)}^{(1)}}{t_{h(SI)}^{(1)}}$                                | Data input hold time         | Master<br>Slave                 | 100<br>100                     |                     | ns   |  |

| $t_{a(SO)}^{(1)}$                                                        | Data output access time      | Slave                           | 0                              | 120                 |      |  |

| t <sub>dis(SO)</sub> <sup>(1)</sup>                                      | Data output disable time     | Slave                           |                                | 240                 |      |  |

| t <sub>v(SO)</sub> <sup>(1)</sup>                                        | Data output valid time       | Slove (after enable edge)       |                                | 120                 |      |  |

| t <sub>h(SO)</sub> <sup>(1)</sup>                                        | Data output hold time        | Slave (after enable edge)       | 0                              |                     |      |  |

| t <sub>v(MO)</sub> <sup>(1)</sup>                                        | Data output valid time       | Master (after enable edge)      |                                | 120                 |      |  |

| t <sub>h(MO)</sub> <sup>(1)</sup>                                        | Data output hold time        | Master (after enable edge)      | 0                              |                     |      |  |

Table 111.

SPI characteristics

1. Data based on design simulation and/or characterization results, not tested in production.

2. Depends on  $f_{CPU}$ . For example, if  $f_{CPU} = 8$  MHz, then  $t_{CPU} = 1 / f_{CPU} = 125$  ns and  $t_{su(SS)} = 175$  ns.

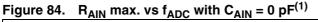

| Symbol           | Parameter                                                                              | Conditions | Min | Тур     | Max | Unit               |

|------------------|----------------------------------------------------------------------------------------|------------|-----|---------|-----|--------------------|

| t <sub>ADC</sub> | Conversion time (Sample + Hold)<br>$f_{CPU} = 8 MHz$ , Speed = 0,<br>$f_{ADC} = 2 MHz$ |            |     | 7.5     |     | μs                 |

|                  | No. of sample capacitor loading cycles<br>No. of Hold conversion cycles                |            |     | 4<br>11 |     | 1/f <sub>ADC</sub> |

Any added external serial resistor will downgrade the ADC accuracy (especially for resistance greater than 10kΩ). Data based on characterization results, not tested in production.

2. Injecting negative current on adjacent pins may result in increased leakage currents. Software filtering of the converted analog value is recommended.

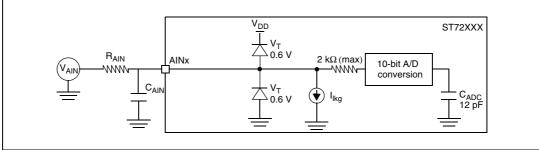

C<sub>PARASITIC</sub> represents the capacitance of the PCB (dependent on soldering and PCB layout quality) plus the pad capacitance (3 pF). A high C<sub>PARASITIC</sub> value will downgrade conversion accuracy. To remedy this, f<sub>ADC</sub> should be reduced.

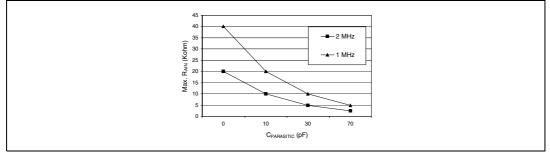

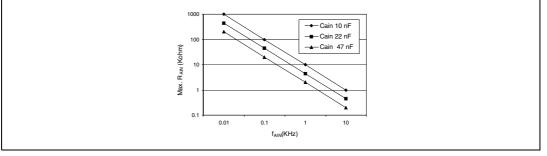

# Figure 85. Recommended $C_{AIN}$ and $R_{AIN}$ values<sup>(1)</sup>

1. This graph shows that, depending on the input signal variation ( $f_{AIN}$ ),  $C_{AIN}$  can be increased for stabilization time and decreased to allow the use of a larger serial resistor ( $R_{AIN}$ ).

### Figure 86. Typical A/D converter application

| Dim            |      | mm    |       | inches <sup>(1)</sup> |        |        |  |  |  |

|----------------|------|-------|-------|-----------------------|--------|--------|--|--|--|

| Dim.           | Min  | Тур   | Max   | Min                   | Тур    | Max    |  |  |  |

| Е              | 9.91 | 10.41 | 11.05 | 0.3902                | 0.4098 | 0.4350 |  |  |  |

| E1             | 7.62 | 8.89  | 9.40  | 0.3000                | 0.3500 | 0.3701 |  |  |  |

| е              |      | 1.78  |       |                       | 0.0701 |        |  |  |  |

| eA             |      | 10.16 |       |                       | 0.4000 |        |  |  |  |

| eB             |      |       | 12.70 |                       |        | 0.5000 |  |  |  |

| eC             |      |       | 1.40  |                       |        | 0.0551 |  |  |  |

| L              | 2.54 | 3.05  | 3.81  | 0.1000                | 0.1201 | 0.1500 |  |  |  |

| Number of pins |      |       |       |                       |        |        |  |  |  |

| Ν              | 42   |       |       |                       |        |        |  |  |  |

Table 117. 32-pin dual in-line package mechanical data (continued)

1. Values in inches are converted from mm and rounded to 4 decimal digits.

# 14.1 Flash devices

# 14.1.1 Flash configuration

### Table 119. Flash option bytes

|         | Static option byte 0 |    |      |   |   |          |       |             |                  |         | Stati | c optio  | on byt | e 1 |     |     |

|---------|----------------------|----|------|---|---|----------|-------|-------------|------------------|---------|-------|----------|--------|-----|-----|-----|

|         | 7                    | 6  | 5    | 4 | 3 | 2        | 1     | 0           | 7                | 6       | 5     | 4        | 3      | 2   | 1   | 0   |

|         | WI                   | DG | Res  | V | D | Reserved |       | ⊈<br>∟ PKG1 | TC               | OSCTYPE |       | OSCRANGE |        |     | OFF |     |

|         | HALT                 | SW | 1103 | 1 | 0 | 11636    | i veu | FMP         | i Kui            | RS      | 1     | 0        | 2      | 1   | 0   | PLL |

| Default | 1                    | 1  | 1    | 0 | 0 | 1        | 1     | 1           | See<br>note<br>1 | 1       | 1     | 0        | 0      | 1   | 1   | 1   |

1. Depends on device type as defined in Table 122: Package selection (OPT7) on page 181.

The option bytes allow the hardware configuration of the microcontroller to be selected. They have no address in the memory map and can be accessed only in programming mode (for example using a standard ST7 programming tool). The default content of the Flash is fixed to FFh. To program directly the Flash devices using ICP, Flash devices are shipped to customers with the internal RC clock source. In masked ROM devices, the option bytes are fixed in hardware by the ROM code (see option list).

### Table 120. Option byte 0 bit description

| Bit    | Name     | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|--------|----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| OPT7   | WDG HALT | <ul> <li>Watchdog reset on Halt</li> <li>This option bit determines if a reset is generated when entering Halt mode while the Watchdog is active.</li> <li>0: No reset generation when entering Halt mode</li> <li>1: Reset generation when entering Halt mode</li> </ul>                                                                                                                                                                                                                                                                                                                                                           |

| OPT6   | WDG SW   | Hardware or software Watchdog<br>This option bit selects the Watchdog type.<br>0: Hardware (Watchdog always enabled)<br>1: Software (Watchdog to be enabled by software)                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| OPT5   | -        | Reserved, must be kept at default value.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |