Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                        |

|----------------------------|---------------------------------------------------------------|

| Core Processor             | XCore                                                         |

| Core Size                  | 32-Bit 8-Core                                                 |

| Speed                      | 400MIPS                                                       |

| Connectivity               | Configurable                                                  |

| Peripherals                | -                                                             |

| Number of I/O              | 64                                                            |

| Program Memory Size        | 64KB (16K x 32)                                               |

| Program Memory Type        | SRAM                                                          |

| EEPROM Size                | -                                                             |

| RAM Size                   | -                                                             |

| Voltage - Supply (Vcc/Vdd) | 0.95V ~ 3.6V                                                  |

| Data Converters            | -                                                             |

| Oscillator Type            | External                                                      |

| Operating Temperature      | 0°C ~ 70°C (TA)                                               |

| Mounting Type              | Surface Mount                                                 |

| Package / Case             | 128-TQFP Exposed Pad                                          |

| Supplier Device Package    | 128-TQFP (14x14)                                              |

| Purchase URL               | https://www.e-xfl.com/product-detail/xmos/xs1-l8a-64-tq128-c4 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# **Table of Contents**

| 1   | xCORE Multicore Microcontrollers |

|-----|----------------------------------|

| 2   | XS1-L8A-64-TQ128 Features        |

| 3   | Pin Configuration                |

| 4   | Signal Description               |

| 5   | Product Overview                 |

| 6   | PLL                              |

| 7   | Boot Procedure                   |

| 8   | Memory                           |

| 9   | JTAG                             |

| 10  | Board Integration                |

| 11  | DC and Switching Characteristics |

| 12  | Package Information              |

| 13  | Ordering Information             |

| App | endices                          |

| Α   | Configuration of the XS1         |

| В   | Processor Status Configuration   |

| С   | Tile Configuration               |

| D   | Node Configuration               |

| E   | XMOS USB Interface               |

| F   | Device Errata                    |

| G   | JTAG, xSCOPE and Debugging       |

| Н   | Schematics Design Check List 57  |

| 1   | PCB Layout Design Check List     |

| J   | Associated Design Documentation  |

| K   | Related Documentation            |

| L   | Revision History                 |

#### TO OUR VALUED CUSTOMERS

It is our intention to provide you with accurate and comprehensive documentation for the hardware and software components used in this product. To subscribe to receive updates, visit <a href="http://www.xmos.com/">http://www.xmos.com/</a>.

XMOS Ltd. is the owner or licensee of the information in this document and is providing it to you "AS IS" with no warranty of any kind, express or implied and shall have no liability in relation to its use. XMOS Ltd. makes no representation that the information, or any particular implementation thereof, is or will be free from any claims of infringement and again, shall have no liability in relation to any such claims.

XMOS and the XMOS logo are registered trademarks of XMOS Ltd in the United Kingdom and other countries, and may not be used without written permission. Company and product names mentioned in this document are the trademarks or registered trademarks of their respective owners.

# 4 Signal Description

This section lists the signals and I/O pins available on the XS1-L8A-64-TQ128. The device provides a combination of 1 bit, 4bit, 8bit and 16bit ports, as well as wider ports that are fully or partially (gray) bonded out. All pins of a port provide either output or input, but signals in different directions cannot be mapped onto the same port.

Pins may have one or more of the following properties:

PD/PU: The IO pin a weak pull-down or pull-up resistor. On GPIO pins this resistor can be enabled.

|          | Power pins (8)          |       |            |  |  |  |  |  |  |  |  |  |  |

|----------|-------------------------|-------|------------|--|--|--|--|--|--|--|--|--|--|

| Signal   | Function                | Туре  | Properties |  |  |  |  |  |  |  |  |  |  |

| GND      | Digital ground          | GND   |            |  |  |  |  |  |  |  |  |  |  |

| OTP_VCC  | OTP power supply        | PWR   |            |  |  |  |  |  |  |  |  |  |  |

| OTP_VPP  | OTP programming voltage | PWR   |            |  |  |  |  |  |  |  |  |  |  |

| PLL_AGND | Analog ground for PLL   | GND   |            |  |  |  |  |  |  |  |  |  |  |

| PLL_AVDD | Analog PLL power        | PWR   |            |  |  |  |  |  |  |  |  |  |  |

| RST_N    | Global reset input      | Input |            |  |  |  |  |  |  |  |  |  |  |

| VDD      | Digital tile power      | PWR   |            |  |  |  |  |  |  |  |  |  |  |

| VDDIO    | Digital I/O power       | PWR   |            |  |  |  |  |  |  |  |  |  |  |

ST: The IO pin has a Schmitt Trigger on its input.

| Clocks pins (2) |                     |       |            |  |  |  |  |  |  |  |  |  |

|-----------------|---------------------|-------|------------|--|--|--|--|--|--|--|--|--|

| Signal          | Function            | Туре  | Properties |  |  |  |  |  |  |  |  |  |

| CLK             | PLL reference clock | Input | PD, ST     |  |  |  |  |  |  |  |  |  |

| MODE[3:0]       | Boot mode select    | Input | PU, ST     |  |  |  |  |  |  |  |  |  |

|         | JTAG pins (6)    |        |            |  |  |  |  |  |  |  |  |  |  |  |

|---------|------------------|--------|------------|--|--|--|--|--|--|--|--|--|--|--|

| Signal  | Function         | Туре   | Properties |  |  |  |  |  |  |  |  |  |  |  |

| DEBUG_N | Multi-chip debug | I/0    | PU         |  |  |  |  |  |  |  |  |  |  |  |

| тск     | Test clock       | Input  | PU, ST     |  |  |  |  |  |  |  |  |  |  |  |

| TDI     | Test data input  | Input  | PU, ST     |  |  |  |  |  |  |  |  |  |  |  |

| TDO     | Test data output | Output | PD, OT     |  |  |  |  |  |  |  |  |  |  |  |

| TMS     | Test mode select | Input  | PU, ST     |  |  |  |  |  |  |  |  |  |  |  |

| TRST_N  | Test reset input | Input  | PU, ST     |  |  |  |  |  |  |  |  |  |  |  |

-XMOS<sup>®</sup>

6

|        | I/O pins (64)                                                                                      |      |                                  |

|--------|----------------------------------------------------------------------------------------------------|------|----------------------------------|

| Signal | Function                                                                                           | Туре | Properties                       |

| X0D00  | 1A <sup>0</sup>                                                                                    | I/O  | PD <sub>S</sub> , R <sub>S</sub> |

| X0D01  | XLA <sup>4</sup> <sub>out</sub> 1B <sup>0</sup>                                                    | I/O  | PD <sub>S</sub> , R <sub>S</sub> |

| X0D02  | XLA <sup>3</sup> <sub>out</sub> 4A <sup>0</sup> 8A <sup>0</sup> 16A <sup>0</sup> 32A <sup>20</sup> | I/O  | PD <sub>S</sub> , R <sub>U</sub> |

| X0D03  | XLA <sup>2</sup> <sub>out</sub> 4A <sup>1</sup> 8A <sup>1</sup> 16A <sup>1</sup> 32A <sup>21</sup> | I/O  | PDs, Ru                          |

| X0D04  | XLA <sup>1</sup> <sub>out</sub> 4B <sup>0</sup> 8A <sup>2</sup> 16A <sup>2</sup> 32A <sup>22</sup> | I/O  | PD <sub>S</sub> , R <sub>U</sub> |

| X0D05  | XLA <sup>0</sup> <sub>out</sub> 4B <sup>1</sup> 8A <sup>3</sup> 16A <sup>3</sup> 32A <sup>23</sup> | I/O  | PD <sub>S</sub> , R <sub>U</sub> |

| X0D06  | $XLA_{in}^{0}$ $4B^{2}$ $8A^{4}$ $16A^{4}$ $32A^{24}$                                              | I/O  | PD <sub>S</sub> , R <sub>U</sub> |

| X0D07  | $XLA_{in}^{1}$ $4B^{3}$ $8A^{5}$ $16A^{5}$ $32A^{25}$                                              | I/O  | PD <sub>S</sub> , R <sub>U</sub> |

| X0D08  | $XLA_{in}^2$ $4A^2$ $8A^6$ $16A^6$ $32A^{26}$                                                      | I/O  | PD <sub>S</sub> , R <sub>U</sub> |

| X0D09  | XLA <sup>3</sup> <sub>in</sub> 4A <sup>3</sup> 8A <sup>7</sup> 16A <sup>7</sup> 32A <sup>27</sup>  | I/O  | PDs, Ru                          |

| X0D10  | XLA <sup>4</sup> <sub>in</sub> 1C <sup>0</sup>                                                     | I/O  | PD <sub>S</sub> , R <sub>S</sub> |

| X0D11  | 1 D <sup>0</sup>                                                                                   | I/O  | PD <sub>S</sub> , R <sub>S</sub> |

| X0D12  | 1 E <sup>0</sup>                                                                                   | I/0  | PD <sub>S</sub> , R <sub>U</sub> |

| X0D13  | XLB <sup>4</sup> <sub>out</sub> 1F <sup>0</sup>                                                    | I/O  | PD <sub>S</sub> , R <sub>U</sub> |

| X0D14  | $XLB_{out}^3$ $4C^0$ $8B^0$ $16A^8$ $32A^{28}$                                                     | I/O  | PDs, Ru                          |

| X0D15  | $XLB_{out}^2$ 4C <sup>1</sup> 8B <sup>1</sup> 16A <sup>9</sup> 32A <sup>29</sup>                   | I/O  | PDs, Ru                          |

| X0D16  | $XLB_{out}^{1}$ $4D^{0}$ $8B^{2}$ $16A^{10}$                                                       | I/O  | PD <sub>S</sub> , R <sub>U</sub> |

| X0D17  | $XLB_{out}^{0}$ 4D <sup>1</sup> 8B <sup>3</sup> 16A <sup>11</sup>                                  | I/O  | PD <sub>S</sub> , R <sub>U</sub> |

| X0D18  | $XLB_{in}^{0}$ $4D^{2}$ $8B^{4}$ $16A^{12}$                                                        | I/O  | PD <sub>S</sub> , R <sub>U</sub> |

| X0D19  | XLB <sup>1</sup> <sub>in</sub> 4D <sup>3</sup> 8B <sup>5</sup> 16A <sup>13</sup>                   | I/O  | PD <sub>S</sub> , R <sub>U</sub> |

| X0D20  | $XLB_{in}^2$ $4C^2$ $8B^6$ $16A^{14}$ $32A^{30}$                                                   | I/O  | PDs, Ru                          |

| X0D21  | $XLB_{in}^{3}$ 4C <sup>3</sup> 8B <sup>7</sup> 16A <sup>15</sup> 32A <sup>31</sup>                 | I/O  | PDs, Ru                          |

| X0D22  | XLB <sup>4</sup> <sub>in</sub> 1G <sup>0</sup>                                                     | I/O  | PD <sub>S</sub> , R <sub>U</sub> |

| X0D23  | 1H <sup>0</sup>                                                                                    | I/O  | PD <sub>S</sub> , R <sub>U</sub> |

| X0D24  | 110                                                                                                | I/O  | PDs                              |

| X0D25  | ۱J <sup>0</sup>                                                                                    | I/O  | PDs                              |

| X0D26  | 4E <sup>0</sup> 8C <sup>0</sup> 16B <sup>0</sup>                                                   | I/O  | PDs, Ru                          |

| X0D27  | 4E <sup>1</sup> 8C <sup>1</sup> 16B <sup>1</sup>                                                   | I/O  | PD <sub>S</sub> , R <sub>U</sub> |

| X0D28  | 4F <sup>0</sup> 8C <sup>2</sup> 16B <sup>2</sup>                                                   | I/O  | PD <sub>S</sub> , R <sub>U</sub> |

| X0D29  | 4F <sup>1</sup> 8C <sup>3</sup> 16B <sup>3</sup>                                                   | I/O  | PD <sub>S</sub> , R <sub>U</sub> |

| X0D30  | 4F <sup>2</sup> 8C <sup>4</sup> 16B <sup>4</sup>                                                   | I/O  | PD <sub>S</sub> , R <sub>U</sub> |

| X0D31  | 4F <sup>3</sup> 8C <sup>5</sup> 16B <sup>5</sup>                                                   | I/0  | PD <sub>S</sub> , R <sub>U</sub> |

| X0D32  | 4E <sup>2</sup> 8C <sup>6</sup> 16B <sup>6</sup>                                                   | I/0  | PDs, Ru                          |

| X0D33  | 4E <sup>3</sup> 8C <sup>7</sup> 16B <sup>7</sup>                                                   | I/O  | PD <sub>S</sub> , R <sub>U</sub> |

| X0D34  | 1K <sup>0</sup>                                                                                    | I/0  | PDs                              |

| X0D35  | 1L <sup>0</sup>                                                                                    | I/O  | PDs                              |

| X0D36  | 1M <sup>0</sup> 8D <sup>0</sup> 16B <sup>8</sup>                                                   | I/O  | PDs                              |

| X0D37  | 1N <sup>0</sup> 8D <sup>1</sup> 16B <sup>9</sup>                                                   | I/0  | PD <sub>S</sub> , R <sub>U</sub> |

| X0D38  | 10 <sup>0</sup> 8D <sup>2</sup> 16B <sup>10</sup>                                                  | I/O  | PDs, Ru                          |

| X0D39  | 1P <sup>0</sup> 8D <sup>3</sup> 16B <sup>11</sup>                                                  | I/0  | PD <sub>S</sub> , R <sub>U</sub> |

| X0D40  | 8D <sup>4</sup> 16B <sup>12</sup>                                                                  | I/0  | PD <sub>S</sub> , R <sub>U</sub> |

|        |                                                                                                    |      | (continued)                      |

-XMOS<sup>®</sup>

XS1-L8A-64-TQ128

# 5 Product Overview

The XS1-L8A-64-TQ128 is a powerful device that consists of a single xCORE Tile, which comprises a flexible logical processing cores with tightly integrated I/O and on-chip memory.

## 5.1 Logical cores

MIPS

**400 MIPS**

**500 MIPS**

Frequency

400 MHz

500 MHz

1

100

125

Speed

grade

4

5

The tile has 8 active logical cores, which issue instructions down a shared fourstage pipeline. Instructions from the active cores are issued round-robin. If up to four logical cores are active, each core is allocated a quarter of the processing cycles. If more than four logical cores are active, each core is allocated at least 1/ncycles (for *n* cores). Figure 2 shows the guaranteed core performance depending on the number of cores used.

2

100

125

3

100

125

Minimum MIPS per core (for *n* cores)

5

80

100

6

67

83

7

57

71

8

50

63

4

100

125

Figure 2: Logical core performance

There is no way that the performance of a logical core can be reduced below these predicted levels. Because cores may be delayed on I/O, however, their unused processing cycles can be taken by other cores. This means that for more than four logical cores, the performance of each core is often higher than the predicted minimum but cannot be guaranteed.

The logical cores are triggered by events instead of interrupts and run to completion. A logical core can be paused to wait for an event.

## 5.2 xTIME scheduler

The xTIME scheduler handles the events generated by xCORE Tile resources, such as channel ends, timers and I/O pins. It ensures that all events are serviced and synchronized, without the need for an RTOS. Events that occur at the I/O pins are handled by the Hardware-Response ports and fed directly to the appropriate xCORE Tile. An xCORE Tile can also choose to wait for a specified time to elapse, or for data to become available on a channel.

Tasks do not need to be prioritised as each of them runs on their own logical xCORE. It is possible to share a set of low priority tasks on a single core using cooperative multitasking.

## 5.3 Hardware Response Ports

Hardware Response ports connect an xCORE tile to one or more physical pins and as such define the interface between hardware attached to the XS1-L8A-64-TQ128, and the software running on it. A combination of 1 bit, 4 bit, 8 bit, 16 bit and 32 bit ports are available. All pins of a port provide either output or input. Signals in different directions cannot be mapped onto the same port.

- A 32-bit program size *s* in words.

- Program consisting of  $s \times 4$  bytes.

- A 32-bit CRC, or the value 0x0D15AB1E to indicate that no CRC check should be performed.

The program size and CRC are stored least significant byte first. The program is loaded into the lowest memory address of RAM, and the program is started from that address. The CRC is calculated over the byte stream represented by the program size and the program itself. The polynomial used is 0xEDB88320 (IEEE 802.3); the CRC register is initialized with 0xFFFFFFFF and the residue is inverted to produce the CRC.

#### 7.1 Boot from SPI master

If set to boot from SPI master, the processor enables the four pins specified in Figure 9, and drives the SPI clock at 2.5 MHz (assuming a 400 MHz core clock). A READ command is issued with a 24-bit address 0x000000. The clock polarity and phase are 0 / 0.

Figure 9: SPI master pins

PinSignalDescriptionX0D00MISOMaster In Slave Out (Data)9:X0D01SSSlave Select2rX0D10SCLKClockSX0D11MOSIMaster Out Slave In (Data)

The xCORE Tile expects each byte to be transferred with the *least-significant bit first*. Programmers who write bytes into an SPI interface using the most significant bit first may have to reverse the bits in each byte of the image stored in the SPI device.

If a large boot image is to be read in, it is faster to first load a small boot-loader that reads the large image using a faster SPI clock, for example 50 MHz or as fast as the flash device supports.

The pins used for SPI boot are hardcoded in the boot ROM and cannot be changed. If required, an SPI boot program can be burned into OTP that uses different pins.

#### 7.2 Boot from xConnect Link

If set to boot from an xConnect Link, the processor enables Link B around 200 ns after the boot process starts. Enabling the Link switches off the pull-down on resistors X0D16..X0D19, drives X0D16 and X0D17 low (the initial state for the Link), and monitors pins X0D18 and X0D19 for boot-traffic. X0D18 and X0D19 must be low at this stage. If the internal pull-down is too weak to drain any residual charge, external pull-downs of 10K may be required on those pins.

-XM()S

The boot-rom on the core will then:

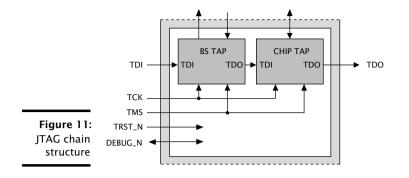

The JTAG chain structure is illustrated in Figure 11. Directly after reset, two TAP controllers are present in the JTAG chain: the boundary scan TAP and the chip TAP. The boundary scan TAP is a standard 1149.1 compliant TAP that can be used for boundary scan of the I/O pins. The chip TAP provides access into the xCORE Tile, switch and OTP for loading code and debugging.

The TRST\_N pin must be asserted low during and after power up for 100 ns. If JTAG is not required, the TRST\_N pin can be tied to ground to hold the JTAG module in reset.

The DEBUG\_N pin is used to synchronize the debugging of multiple xCORE Tiles. This pin can operate in both output and input mode. In output mode and when configured to do so, DEBUG\_N is driven low by the device when the processor hits a debug break point. Prior to this point the pin will be tri-stated. In input mode and when configured to do so, driving this pin low will put the xCORE Tile into debug mode. Software can set the behavior of the xCORE Tile based on this pin. This pin should have an external pull up of  $4K7-47K\Omega$  or left not connected in single core applications.

The JTAG device identification register can be read by using the IDCODE instruction. Its contents are specified in Figure 12.

Figure 12: IDCODE return value

| Bit: | 31   |                                          |   |     |   |   |   |     |   |   |   | D | evice | e Ide | ntifi | catio | on R | egis | ter |   |   |   |   |   |   |   |   |   |   | E | lit0 |

|------|------|------------------------------------------|---|-----|---|---|---|-----|---|---|---|---|-------|-------|-------|-------|------|------|-----|---|---|---|---|---|---|---|---|---|---|---|------|

|      | Vers | ersion Part Number Manufacturer Identity |   |     |   |   |   |     |   |   |   |   |       |       | 1     |       |      |      |     |   |   |   |   |   |   |   |   |   |   |   |      |

| 0    | 0    | 0                                        | 0 | 0   | 0 | 0 | 0 | 0   | 0 | 0 | 0 | 0 | 0     | 0     | 0     | 0     | 0    | 1    | 0   | 0 | 1 | 1 | 0 | 0 | 0 | 1 | 1 | 0 | 0 | 1 | 1    |

|      | (    | )                                        |   | 0 0 |   |   |   | 0 2 |   |   |   |   |       | 6 3   |       |       |      |      |     |   |   |   |   |   |   |   |   |   |   |   |      |

The JTAG usercode register can be read by using the USERCODE instruction. Its contents are specified in Figure 13. The OTP User ID field is read from bits [22:31] of the security register , *see* §8.1 (all zero on unprogrammed devices).

| Figure 13:   |  |

|--------------|--|

| USERCODE     |  |

| return value |  |

| 12.       | Bit31 Usercode Register |   |               |   |      |      |    |   |   |        |   |   |   | BitO             |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |

|-----------|-------------------------|---|---------------|---|------|------|----|---|---|--------|---|---|---|------------------|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| 13:       |                         |   |               | 0 | TP U | lser | ID |   |   | Unused |   |   |   | Silicon Revision |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |

| DE<br>lue | 0                       | 0 | 0             | 0 | 0    | 0    | 0  | 0 | 0 | 0      | 0 | 0 | 0 | 0                | 1 | 0 | 1 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

| lue       |                         | ( | 0 0 0 2 8 0 0 |   |      |      |    |   |   | )      |   |   | ( | )                |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |

## 10.1 Land patterns and solder stencils

The land pattern recommendations in this document are based on a RoHS compliant process and derived, where possible, from the nominal *Generic Requirements for Surface Mount Design and Land Pattern Standards* IPC-7351B specifications. This standard aims to achieve desired targets of heel, toe and side fillets for solderjoints.

Solder paste and ground via recommendations are based on our engineering and development kit board production. They have been found to work and optimized as appropriate to achieve a high yield. The size, type and number of vias used in the center pad affects how much solder wicks down the vias during reflow. This in turn, along with solder paster coverage, affects the final assembled package height. These factors should be taken into account during design and manufacturing of the PCB.

The following land patterns and solder paste contains recommendations. Final land pattern and solder paste decisions are the responsibility of the customer. These should be tuned during manufacture to suit the manufacturing process.

The package is a 128 pin Thin Quad Flat Pack package with exposed heat slug on a 0.4mm pitch. An example land pattern is shown in Figure 14.

Pad widths and spacings are such that solder mask can still be applied between the pads using standard design rules. This is recommended to reduce solder shorts.

The center pad solder paste level needs to be controlled so the device sits the correct height from the circuit board. For the 128 pin TQFP package, a 3x3 array of squares for solder paste is recommended as shown in Figure 15. This gives a paste level of 56%.

## 10.2 Ground and Thermal Vias

Vias under the heat slug into the ground plane of the PCB are recommended for a low inductance ground connection and good thermal performance. A  $3 \times 3$  grid of vias, with a 0.6mm diameter annular ring and a 0.3mm drill, equally spaced across the heat slug, would be suitable.

## 10.3 Moisture Sensitivity

XMOS devices are, like all semiconductor devices, susceptible to moisture absorption. When removed from the sealed packaging, the devices slowly absorb moisture from the surrounding environment. If the level of moisture present in the device is too high during reflow, damage can occur due to the increased internal vapour pressure of moisture. Example damage can include bond wire damage, die lifting, internal or external package cracks and/or delamination.

All XMOS devices are Moisture Sensitivity Level (MSL) 3 - devices have a shelf life of 168 hours between removal from the packaging and reflow, provided they are stored below 30C and 60% RH. If devices have exceeded these values or an included moisture indicator card shows excessive levels of moisture, then the parts should be baked as appropriate before use. This is based on information from *Joint*

# 11 DC and Switching Characteristics

| Symbol   | Parameter                                                | MIN  | TYP  | MAX  | UNITS | Notes |

|----------|----------------------------------------------------------|------|------|------|-------|-------|

| VDD      | Tile DC supply voltage                                   | 0.95 | 1.00 | 1.05 | V     |       |

| VDDIO    | I/O supply voltage                                       | 3.00 | 3.30 | 3.60 | V     |       |

| PLL_AVDD | PLL analog supply                                        | 0.95 | 1.00 | 1.05 | V     |       |

| OTP_VCC  | OTP supply voltage                                       | 3.00 | 3.30 | 3.60 | V     |       |

| OTP_VPP  | OTP external programming voltage (optional program only) | 6.18 | 6.50 | 6.83 | V     |       |

| CI       | xCORE Tile I/O load<br>capacitance                       |      |      | 25   | pF    |       |

| Та       | Ambient operating<br>temperature (Commercial)            | 0    |      | 70   | °C    |       |

|          | Ambient operating<br>temperature (Industrial)            | -40  |      | 85   | °C    |       |

| Tj       | Junction temperature                                     |      |      | 125  | °C    |       |

| Tstg     | Storage temperature                                      | -65  |      | 150  | °C    |       |

## 11.1 Operating Conditions

Figure 16: Operating conditions

# 11.2 DC Characteristics

| Symbol | Parameter            | MIN   | ТҮР | MAX  | UNITS | Notes |

|--------|----------------------|-------|-----|------|-------|-------|

| V(IH)  | Input high voltage   | 2.00  |     | 3.60 | V     | A     |

| V(IL)  | Input low voltage    | -0.30 |     | 0.70 | V     | A     |

| V(OH)  | Output high voltage  | 2.00  |     |      | V     | B, C  |

| V(OL)  | Output low voltage   |       |     | 0.60 | V     | B, C  |

| R(PU)  | Pull-up resistance   |       | 35K |      | Ω     | D     |

| R(PD)  | Pull-down resistance |       | 35K |      | Ω     | D     |

Figure 17: DC characteristics

A All pins except power supply pins.

B Ports 1A, 1D, 1E, 1H, 1I, 1J, 1K and 1L are nominal 8 mA drivers, the remainder of the general-purpose I/Os are 4 mA.

C Measured with 4 mA drivers sourcing 4 mA, 8 mA drivers sourcing 8 mA.

D Used to guarantee logic state for an I/O when high impedance. The internal pull-ups/pull-downs should not be used to pull external circuitry.

# 11.3 ESD Stress Voltage

Figure 18 ESD stress voltage

| 18: | Symbol | Parameter        | MIN   | TYP | MAX  | UNITS | Notes |

|-----|--------|------------------|-------|-----|------|-------|-------|

| ess | HBM    | Human body model | -2.00 |     | 2.00 | KV    |       |

| age | MM     | Machine model    | -200  |     | 200  | V     |       |

-XMOS

## 11.6 Clock

| Symbol | Parameter                                    | MIN  | ТҮР | MAX | UNITS | Notes |

|--------|----------------------------------------------|------|-----|-----|-------|-------|

| f      | Frequency                                    | 4.22 | 20  | 100 | MHz   |       |

| SR     | Slew rate                                    | 0.10 |     |     | V/ns  |       |

| TJ(LT) | Long term jitter (pk-pk)                     |      |     | 2   | %     | А     |

| f(MAX) | Processor clock frequency (Speed<br>Grade 4) |      |     | 400 | MHz   | В     |

|        | Processor clock frequency (Speed<br>Grade 5) |      |     | 500 | MHz   | В     |

Figure 21: Clock

A Percentage of CLK period.

B Assumes typical tile and I/O voltages with nominal activity.

Further details can be found in the XS1-L Clock Frequency Control document, X1433.

The OTP may be programmed using its internal charge pump or by supplying a 6.5V VPP programming voltage on the OTP\_VPP pin. Unless a programming cycle is underway the OTP\_VPP pins should be left undriven.

## 11.7 xCORE Tile I/O AC Characteristics

Figure 22: I/O AC characteristics

|     | Symbol       | Parameter                                                           | MIN | TYP | MAX | UNITS | Notes |

|-----|--------------|---------------------------------------------------------------------|-----|-----|-----|-------|-------|

|     | T(XOVALID)   | Input data valid window                                             | 8   |     |     | ns    |       |

| 22: | T(XOINVALID) | Output data invalid window                                          | 9   |     |     | ns    |       |

| ics | T(XIFMAX)    | Rate at which data can be sampled with respect to an external clock |     |     | 60  | MHz   |       |

The input valid window parameter relates to the capability of the device to capture data input to the chip with respect to an external clock source. It is calculated as the sum of the input setup time and input hold time with respect to the external clock as measured at the pins. The output invalid window specifies the time for which an output is invalid with respect to the external clock. Note that these parameters are specified as a window rather than absolute numbers since the device provides functionality to delay the incoming clock with respect to the incoming data.

Information on interfacing to high-speed synchronous interfaces can be found in the XS1 Port I/O Timing document, X5821.

The response to a write message comprises either control tokens 3 and 1 (for success), or control tokens 4 and 1 (for failure).

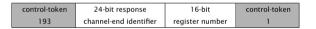

A read message comprises the following:

| control-token | 24-bit response        | 16-bit          | control-token |

|---------------|------------------------|-----------------|---------------|

| 193           | channel-end identifier | register number | 1             |

The response to the read message comprises either control token 3, 32-bit of data, and control-token 1 (for success), or control tokens 4 and 1 (for failure).

#### A.3 Accessing node configuration

Node configuration registers can be accessed through the interconnect using the functions write\_node\_config\_reg(device, ...) and read\_node\_config\_reg(device, ...), where device is the name of the node. These functions implement the protocols described below.

Instead of using the functions above, a channel-end can be allocated to communicate with the node configuration registers. The destination of the channel-end should be set to 0xnnnnC30C where nnnn is the node-identifier.

A write message comprises the following:

| control-token | 24-bit response        | 16-bit          | 32-bit | control-token |

|---------------|------------------------|-----------------|--------|---------------|

| 192           | channel-end identifier | register number | data   | 1             |

The response to a write message comprises either control tokens 3 and 1 (for success), or control tokens 4 and 1 (for failure).

A read message comprises the following:

$-X \wedge ()S$

The response to a read message comprises either control token 3, 32-bit of data, and control-token 1 (for success), or control tokens 4 and 1 (for failure).

29

| Bits  | Perm | Init | Description                                                                        |

|-------|------|------|------------------------------------------------------------------------------------|

| 31:24 | RO   | -    | Reserved                                                                           |

| 23:16 | RO   |      | xCORE tile number on the switch.                                                   |

| 15:9  | RO   | -    | Reserved                                                                           |

| 8     | RO   |      | Set to 1 if boot from OTP is enabled.                                              |

| 7:0   | RO   |      | The boot mode pins MODE0, MODE1,, specifying the boot frequency, boot source, etc. |

0x03: xCORE Tile boot status

## **B.5** Security configuration: 0x05

Copy of the security register as read from OTP.

0x05: Security configuration

| Bits | Perm | Init | Description |  |  |  |

|------|------|------|-------------|--|--|--|

| 31:0 | RO   |      | Value.      |  |  |  |

## B.6 Ring Oscillator Control: 0x06

There are four free-running oscillators that clock four counters. The oscillators can be started and stopped using this register. The counters should only be read when the ring oscillator is stopped. The counter values can be read using four subsequent registers. The ring oscillators are asynchronous to the xCORE tile clock and can be used as a source of random bits.

**0x06** Ring Oscillator Control

| -       | Bits | Perm | Init | Description                                        |  |  |

|---------|------|------|------|----------------------------------------------------|--|--|

| 6:      | 31:2 | RO   | -    | Reserved                                           |  |  |

| g<br>or | 1    | RW   | 0    | Set to 1 to enable the xCORE tile ring oscillators |  |  |

| ol      | 0    | RW   | 0    | Set to 1 to enable the peripheral ring oscillators |  |  |

## B.7 Ring Oscillator Value: 0x07

This register contains the current count of the xCORE Tile Cell ring oscillator. This value is not reset on a system reset.

**0x07:** Ring Oscillator Value

|   | Bits  | Perm | Init | Description                   |

|---|-------|------|------|-------------------------------|

|   | 31:16 | RO   | -    | Reserved                      |

| l | 15:0  | RO   | -    | Ring oscillator counter data. |

| 0x11:     | Bits | Perm | Init | Description |

|-----------|------|------|------|-------------|

| Debug SPC | 31:0 | DRW  |      | Value.      |

#### B.13 Debug SSP: 0x12

This register contains the value of the SSP register when the debugger was called.

| 0x12:     | Bits | Perm | Init | Description |

|-----------|------|------|------|-------------|

| Debug SSP | 31:0 | DRW  |      | Value.      |

#### B.14 DGETREG operand 1: 0x13

The resource ID of the logical core whose state is to be read.

| 0x13:     | Bits | Perm | Init | Description              |

|-----------|------|------|------|--------------------------|

| DGETREG   | 31:8 | RO   | -    | Reserved                 |

| operand 1 | 7:0  | DRW  |      | Thread number to be read |

#### B.15 DGETREG operand 2: 0x14

Register number to be read by DGETREG

**0x14:** DGETREG operand 2

| Bits | Perm | Init | Description                |

|------|------|------|----------------------------|

| 31:5 | RO   | -    | Reserved                   |

| 4:0  | DRW  |      | Register number to be read |

## B.16 Debug interrupt type: 0x15

Register that specifies what activated the debug interrupt.

·XMC

#### B.19 Debug scratch: 0x20 .. 0x27

A set of registers used by the debug ROM to communicate with an external debugger, for example over JTAG. This is the same set of registers as the Debug Scratch registers in the xCORE tile configuration.

0x20 .. 0x27: Debug scratch

| 0x27:<br>ebug | Bits | Perm | Init | Description |

|---------------|------|------|------|-------------|

| atch          | 31:0 | DRW  |      | Value.      |

## B.20 Instruction breakpoint address: 0x30 .. 0x33

This register contains the address of the instruction breakpoint. If the PC matches this address, then a debug interrupt will be taken. There are four instruction breakpoints that are controlled individually.

0x30 .. 0x33: Instruction breakpoint address

| ction |      |      |      |             |

|-------|------|------|------|-------------|

| point | Bits | Perm | Init | Description |

| dress | 31:0 | DRW  |      | Value.      |

## B.21 Instruction breakpoint control: 0x40 .. 0x43

This register controls which logical cores may take an instruction breakpoint, and under which condition.

| Bits  | Perm | Init | Description                                                                                                                                                                                 |

|-------|------|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 31:24 | RO   | -    | Reserved                                                                                                                                                                                    |

| 23:16 | DRW  | 0    | A bit for each logical core in the tile allowing the breakpoint to be enabled individually for each logical core.                                                                           |

| 15:2  | RO   | -    | Reserved                                                                                                                                                                                    |

| 1     | DRW  | 0    | Set to 1 to cause an instruction breakpoint if the PC is not<br>equal to the breakpoint address. By default, the breakpoint is<br>triggered when the PC is equal to the breakpoint address. |

| 0     | DRW  | 0    | When 1 the instruction breakpoint is enabled.                                                                                                                                               |

0x40 .. 0x43: Instruction breakpoint control

## B.22 Data watchpoint address 1: 0x50 ... 0x53

This set of registers contains the first address for the four data watchpoints.

XMOS

0x80 .. 0x83: Resources breakpoint mask

| urces<br>point | Bits | Perm | Init | Description |

|----------------|------|------|------|-------------|

| mask           | 31:0 | DRW  |      | Value.      |

## B.26 Resources breakpoint value: 0x90 .. 0x93

This set of registers contains the value for the four resource watchpoints.

0x90 .. 0x93: Resources breakpoint value

| rces<br>oint | Bits | Perm | Init | Description |

|--------------|------|------|------|-------------|

| alue         | 31:0 | DRW  |      | Value.      |

## B.27 Resources breakpoint control register: 0x9C .. 0x9F

This set of registers controls each of the four resource watchpoints.

|                                                  | Bits  | Perm | Init | Description                                                                                                                                                                                                                          |

|--------------------------------------------------|-------|------|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                                  | 31:24 | RO   | -    | Reserved                                                                                                                                                                                                                             |

|                                                  | 23:16 | DRW  | 0    | A bit for each logical core in the tile allowing the breakpoint to be enabled individually for each logical core.                                                                                                                    |

|                                                  | 15:2  | RO   | -    | Reserved                                                                                                                                                                                                                             |

| 0x9C 0x9F:<br>Resources<br>breakpoint<br>control | 1     | DRW  | 0    | By default, resource watchpoints trigger when the resource id<br>masked with the set Mask equals the Value. If set to 1, resource<br>watchpoints trigger when the resource id masked with the set<br>Mask is not equal to the Value. |

| register                                         | 0     | DRW  | 0    | When 1 the instruction breakpoint is enabled.                                                                                                                                                                                        |

-XMOS°

| Bits  | Perm | Init | Description                                                                                                    |

|-------|------|------|----------------------------------------------------------------------------------------------------------------|

| 31:26 | RO   | -    | Reserved                                                                                                       |

| 25:24 | RO   |      | 00 - ChannelEnd, 01 - ERROR, 10 - PSCTL, 11 - Idle.                                                            |

| 23:16 | RO   |      | Based on SRC_TARGET_TYPE value, it represents channelEnd ID or Idle status.                                    |

| 15:6  | RO   | -    | Reserved                                                                                                       |

| 5:4   | RO   |      | Two-bit network identifier                                                                                     |

| 3     | RO   | -    | Reserved                                                                                                       |

| 2     | RO   |      | 1 when the current packet is considered junk and will be thrown away.                                          |

| 1     | RO   | 0    | Set to 1 if the switch is routing data into the link, and if a route exists from another link.                 |

| 0     | RO   | 0    | Set to 1 if the link is routing data into the switch, and if a route is created to another link on the switch. |

0x10 .. 0x13: PLink status

# C.9 Debug scratch: 0x20 .. 0x27

A set of registers used by the debug ROM to communicate with an external debugger, for example over the switch. This is the same set of registers as the Debug Scratch registers in the processor status.

0x20 .. 0x27 Debug scratch

| 0 0x27:<br>Debug | Bits | Perm | Init | Description |

|------------------|------|------|------|-------------|

| scratch          | 31:0 | CRW  |      | Value.      |

# C.10 PC of logical core 0: 0x40

Value of the PC of logical core 0.

**0x40** PC of logical core 0

| al | Bits | Perm | Init | Description |

|----|------|------|------|-------------|

| 0  | 31:0 | RO   |      | Value.      |

|                        | Bits  | Perm | Init | Description                                        |

|------------------------|-------|------|------|----------------------------------------------------|

|                        | 31:24 | RO   | -    | Reserved                                           |

| <b>0x01:</b><br>System | 23:16 | RO   |      | Number of links on the switch.                     |

| switch                 | 15:8  | RO   |      | Number of cores that are connected to this switch. |

| description            | 7:0   | RO   |      | Number of links per processor.                     |

## D.3 Switch configuration: 0x04

This register enables the setting of two security modes (that disable updates to the PLL or any other registers) and the header-mode.

| Bits | Perm | Init | Description                                                                                        |

|------|------|------|----------------------------------------------------------------------------------------------------|

| 31   | RO   | 0    | Set to 1 to disable any write access to the configuration registers in this switch.                |

| 30:9 | RO   | -    | Reserved                                                                                           |

| 8    | RO   | 0    | Set to 1 to disable updates to the PLL configuration register.                                     |

| 7:1  | RO   | -    | Reserved                                                                                           |

| 0    | RO   | 0    | Header mode. Set to 1 to enable 1-byte headers. This must be performed on all nodes in the system. |

**0x04:** Switch configuration

## D.4 Switch node identifier: 0x05

This register contains the node identifier.

0x05 Switch node identifier

|               | Bits  | Perm | Init | Description                                                                                                                            |

|---------------|-------|------|------|----------------------------------------------------------------------------------------------------------------------------------------|

| -             | 31:16 | RO   | -    | Reserved                                                                                                                               |

| 5:<br>e<br>er | 15:0  | RW   | 0    | The unique 16-bit ID of this node. This ID is matched most-<br>significant-bit first with incoming messages for routing pur-<br>poses. |

## D.5 PLL settings: 0x06

An on-chip PLL multiplies the input clock up to a higher frequency clock, used to clock the I/O, processor, and switch, see Oscillator. Note: a write to this register will cause the tile to be reset.

-XMOS

| Bits  | Perm | Init | Description                                                                            |

|-------|------|------|----------------------------------------------------------------------------------------|

| 31:26 | RO   | -    | Reserved                                                                               |

| 25:23 | RW   |      | OD: Output divider value<br>The initial value depends on pins MODE0 and MODE1.         |

| 22:21 | RO   | -    | Reserved                                                                               |

| 20:8  | RW   |      | F: Feedback multiplication ratio<br>The initial value depends on pins MODE0 and MODE1. |

| 7     | RO   | -    | Reserved                                                                               |

| 6:0   | RW   |      | R: Oscilator input divider value<br>The initial value depends on pins MODE0 and MODE1. |

0x06: PLL settings

## D.6 System switch clock divider: 0x07

Sets the ratio of the PLL clock and the switch clock.

**0x07** System switch clock divider

| 07:        | Bits  | Perm | Init | Description                                                                                            |

|------------|-------|------|------|--------------------------------------------------------------------------------------------------------|

| em         | 31:16 | RO   | -    | Reserved                                                                                               |

| ock<br>der | 15:0  | RW   | 0    | Switch clock divider. The PLL clock will be divided by this value plus one to derive the switch clock. |

## D.7 Reference clock: 0x08

Sets the ratio of the PLL clock and the reference clock used by the node.

**0x08:** Reference clock

| Bits  | Perm | Init | Description                                                                                                                       |

|-------|------|------|-----------------------------------------------------------------------------------------------------------------------------------|

| 31:16 | RO   | -    | Reserved                                                                                                                          |

| 15:0  | RW   | 3    | Architecture reference clock divider. The PLL clock will be divided by this value plus one to derive the 100 MHz reference clock. |

# D.8 Directions 0-7: 0x0C

This register contains eight directions, for packets with a mismatch in bits 7..0 of the node-identifier. The direction in which a packet will be routed is goverened by the most significant mismatching bit.

-XMOS-

# H Schematics Design Check List

✓ This section is a checklist for use by schematics designers using the XS1-L8A-64-TQ128. Each of the following sections contains items to check for each design.

#### H.1 Power supplies

- □ VDDIO and OTP\_VCC supply is within specification before the VDD (core) supply is turned on. Specifically, the VDDIO and OTP\_VCC supply is within specification before VDD (core) reaches 0.4V (Section 10).

- The VDD (core) supply ramps monotonically (rises constantly) from 0V to its final value (0.95V 1.05V) within 10ms (Section 10).

- $\Box$  The VDD (core) supply is capable of supplying 300mA (Section 10).

- PLL\_AVDD is filtered with a low pass filter, for example an RC filter, see Section 10

## H.2 Power supply decoupling

- The design has multiple decoupling capacitors per supply, for example at least four0402 or 0603 size surface mount capacitors of 100nF in value, per supply (Section 10).

- □ A bulk decoupling capacitor of at least 10uF is placed on each supply (Section 10).

#### H.3 Power on reset

The RST\_N and TRST\_N pins are asserted (low) during or after power up. The device is not used until these resets have taken place. As the errata in the datasheets show, the internal pull-ups on these two pins can occasionally provide stronger than normal pull-up currents. For this reason, an RC type reset circuit is discouraged as behavior would be unpredictable. A voltage supervisor type reset device is recommended to guarantee a good reset. This also has the benefit of resetting the system should the relevant supply go out of specification.

#### H.4 Clock

The CLK input pin is supplied with a clock with monotonic rising edges and low jitter.

Pins MODE0 and MODE1 are set to the correct value for the chosen oscillator frequency. The MODE settings are shown in the Oscillator section, Section 6. If you have a choice between two values, choose the value with the highest multiplier ratio since that will boot faster.

#### H.5 USB ULPI Mode

This section can be skipped if you do not have an external USB PHY.

- □ If using ULPI, the ULPI signals are connected to specific ports as shown in Section E.

- □ If using ULPI, the ports that are used internally are not connected, see Section E. (Note that this limitation only applies when the ULPI is enabled, they can still be used before or after the ULPI is being used.)

#### H.6 Boot

- □ The device is connected to a SPI flash for booting, connected to X0D0, X0D01, X0D10, and X0D11 (Section 7). If not, you must boot the device through OTP or JTAG.

- □ The device that is connected to flash has both MODE2 and MODE3 connected to pin 3 on the xSYS Header (MSEL). If no debug adapter connection is supported (not recommended) MODE2 and MODE3 are to be left NC (Section 7).

- ☐ The SPI flash that you have chosen is supported by **xflash**, or you have created a specification file for it.

#### H.7 JTAG, XScope, and debugging

- $\Box$  You have decided as to whether you need an XSYS header or not (Section G)

- □ If you included an XSYS header, you connected pin 3 to any MODE2/MODE3 pin that would otherwise be NC (Section G).

- ☐ If you have not included an XSYS header, you have devised a method to program the SPI-flash or OTP (Section G).

#### H.8 GPIO

You have not mapped both inputs and outputs to the same multi-bit port.

# I PCB Layout Design Check List

This section is a checklist for use by PCB designers using the XS1-L8A-64-TQ128. Each of the following sections contains items to check for each design.

## I.1 Ground Plane

- □ Multiple vias (eg, 9) have been used to connect the center pad to the PCB ground plane. These minimize impedance and conduct heat away from the device. (Section 10.2).

- Other than ground vias, there are no (or only a few) vias underneath or closely around the device. This create a good, solid, ground plane.

## I.2 Power supply decoupling

- $\Box$  The decoupling capacitors are all placed close to a supply pin (Section 10).

- $\Box$  The decoupling capacitors are spaced around the device (Section 10).

- The ground side of each decoupling capacitor has a direct path back to the center ground of the device.

## I.3 PLL\_AVDD

The PLL\_AVDD filter (especially the capacitor) is placed close to the PLL\_AVDD pin (Section 10).