Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                        |

|----------------------------|---------------------------------------------------------------|

| Core Processor             | XCore                                                         |

| Core Size                  | 32-Bit 8-Core                                                 |

| Speed                      | 500MIPS                                                       |

| Connectivity               | Configurable                                                  |

| Peripherals                | <u>.</u>                                                      |

| Number of I/O              | 64                                                            |

| Program Memory Size        | 64KB (16K x 32)                                               |

| Program Memory Type        | SRAM                                                          |

| EEPROM Size                | <u>.</u>                                                      |

| RAM Size                   | -                                                             |

| Voltage - Supply (Vcc/Vdd) | 0.95V ~ 3.6V                                                  |

| Data Converters            | -                                                             |

| Oscillator Type            | External                                                      |

| Operating Temperature      | 0°C ~ 70°C (TA)                                               |

| Mounting Type              | Surface Mount                                                 |

| Package / Case             | 128-TQFP Exposed Pad                                          |

| Supplier Device Package    | 128-TQFP (14x14)                                              |

| Purchase URL               | https://www.e-xfl.com/product-detail/xmos/xs1-l8a-64-tq128-c5 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

|        | I/O pins (64)                                                                                      |      |                                  |

|--------|----------------------------------------------------------------------------------------------------|------|----------------------------------|

| Signal | Function                                                                                           | Туре | Properties                       |

| X0D00  | 1A <sup>0</sup>                                                                                    | I/O  | PD <sub>S</sub> , R <sub>S</sub> |

| X0D01  | XLA <sup>4</sup> <sub>out</sub> 1B <sup>0</sup>                                                    | I/O  | PD <sub>S</sub> , R <sub>S</sub> |

| X0D02  | XLA <sup>3</sup> <sub>out</sub> 4A <sup>0</sup> 8A <sup>0</sup> 16A <sup>0</sup> 32A <sup>20</sup> | I/O  | PD <sub>S</sub> , R <sub>U</sub> |

| X0D03  | XLA <sup>2</sup> <sub>out</sub> 4A <sup>1</sup> 8A <sup>1</sup> 16A <sup>1</sup> 32A <sup>21</sup> | I/O  | PDs, Ru                          |

| X0D04  | XLA <sup>1</sup> <sub>out</sub> 4B <sup>0</sup> 8A <sup>2</sup> 16A <sup>2</sup> 32A <sup>22</sup> | I/O  | PD <sub>S</sub> , R <sub>U</sub> |

| X0D05  | XLA <sup>0</sup> <sub>out</sub> 4B <sup>1</sup> 8A <sup>3</sup> 16A <sup>3</sup> 32A <sup>23</sup> | I/O  | PD <sub>S</sub> , R <sub>U</sub> |

| X0D06  | $XLA_{in}^{0}$ $4B^{2}$ $8A^{4}$ $16A^{4}$ $32A^{24}$                                              | I/O  | PD <sub>S</sub> , R <sub>U</sub> |

| X0D07  | $XLA_{in}^{1}$ $4B^{3}$ $8A^{5}$ $16A^{5}$ $32A^{25}$                                              | I/O  | PD <sub>S</sub> , R <sub>U</sub> |

| X0D08  | $XLA_{in}^2$ $4A^2$ $8A^6$ $16A^6$ $32A^{26}$                                                      | I/O  | PD <sub>S</sub> , R <sub>U</sub> |

| X0D09  | XLA <sup>3</sup> <sub>in</sub> 4A <sup>3</sup> 8A <sup>7</sup> 16A <sup>7</sup> 32A <sup>27</sup>  | I/O  | PDs, Ru                          |

| X0D10  | XLA <sup>4</sup> <sub>in</sub> 1C <sup>0</sup>                                                     | I/O  | PD <sub>S</sub> , R <sub>S</sub> |

| X0D11  | 1 D <sup>0</sup>                                                                                   | I/O  | PD <sub>S</sub> , R <sub>S</sub> |

| X0D12  | 1 E <sup>0</sup>                                                                                   | I/0  | PD <sub>S</sub> , R <sub>U</sub> |

| X0D13  | XLB <sup>4</sup> <sub>out</sub> 1F <sup>0</sup>                                                    | I/O  | PD <sub>S</sub> , R <sub>U</sub> |

| X0D14  | $XLB_{out}^3$ 4C <sup>0</sup> 8B <sup>0</sup> 16A <sup>8</sup> 32A <sup>28</sup>                   | I/O  | PDs, Ru                          |

| X0D15  | $XLB_{out}^2$ 4C <sup>1</sup> 8B <sup>1</sup> 16A <sup>9</sup> 32A <sup>29</sup>                   | I/O  | PDs, Ru                          |

| X0D16  | $XLB_{out}^{1}$ $4D^{0}$ $8B^{2}$ $16A^{10}$                                                       | I/O  | PD <sub>S</sub> , R <sub>U</sub> |

| X0D17  | $XLB_{out}^{0}$ 4D <sup>1</sup> 8B <sup>3</sup> 16A <sup>11</sup>                                  | I/O  | PD <sub>S</sub> , R <sub>U</sub> |

| X0D18  | $XLB_{in}^{0}$ $4D^{2}$ $8B^{4}$ $16A^{12}$                                                        | I/O  | PD <sub>S</sub> , R <sub>U</sub> |

| X0D19  | XLB <sup>1</sup> <sub>in</sub> 4D <sup>3</sup> 8B <sup>5</sup> 16A <sup>13</sup>                   | I/O  | PD <sub>S</sub> , R <sub>U</sub> |

| X0D20  | $XLB_{in}^2$ $4C^2$ $8B^6$ $16A^{14}$ $32A^{30}$                                                   | I/O  | PDs, Ru                          |

| X0D21  | $XLB_{in}^{3}$ 4C <sup>3</sup> 8B <sup>7</sup> 16A <sup>15</sup> 32A <sup>31</sup>                 | I/O  | PDs, Ru                          |

| X0D22  | XLB <sup>4</sup> <sub>in</sub> 1G <sup>0</sup>                                                     | I/O  | PD <sub>S</sub> , R <sub>U</sub> |

| X0D23  | 1H <sup>0</sup>                                                                                    | I/O  | PD <sub>S</sub> , R <sub>U</sub> |

| X0D24  | 110                                                                                                | I/O  | PDs                              |

| X0D25  | ۱J <sup>0</sup>                                                                                    | I/O  | PDs                              |

| X0D26  | 4E <sup>0</sup> 8C <sup>0</sup> 16B <sup>0</sup>                                                   | I/O  | PDs, Ru                          |

| X0D27  | 4E <sup>1</sup> 8C <sup>1</sup> 16B <sup>1</sup>                                                   | I/O  | PD <sub>S</sub> , R <sub>U</sub> |

| X0D28  | 4F <sup>0</sup> 8C <sup>2</sup> 16B <sup>2</sup>                                                   | I/O  | PD <sub>S</sub> , R <sub>U</sub> |

| X0D29  | 4F <sup>1</sup> 8C <sup>3</sup> 16B <sup>3</sup>                                                   | I/O  | PD <sub>S</sub> , R <sub>U</sub> |

| X0D30  | 4F <sup>2</sup> 8C <sup>4</sup> 16B <sup>4</sup>                                                   | I/O  | PD <sub>S</sub> , R <sub>U</sub> |

| X0D31  | 4F <sup>3</sup> 8C <sup>5</sup> 16B <sup>5</sup>                                                   | I/0  | PD <sub>S</sub> , R <sub>U</sub> |

| X0D32  | 4E <sup>2</sup> 8C <sup>6</sup> 16B <sup>6</sup>                                                   | I/0  | PDs, Ru                          |

| X0D33  | 4E <sup>3</sup> 8C <sup>7</sup> 16B <sup>7</sup>                                                   | I/O  | PD <sub>S</sub> , R <sub>U</sub> |

| X0D34  | 1K <sup>0</sup>                                                                                    | I/0  | PDs                              |

| X0D35  | 1L <sup>0</sup>                                                                                    | I/O  | PDs                              |

| X0D36  | 1M <sup>0</sup> 8D <sup>0</sup> 16B <sup>8</sup>                                                   | I/O  | PDs                              |

| X0D37  | 1N <sup>0</sup> 8D <sup>1</sup> 16B <sup>9</sup>                                                   | I/0  | PD <sub>S</sub> , R <sub>U</sub> |

| X0D38  | 10 <sup>0</sup> 8D <sup>2</sup> 16B <sup>10</sup>                                                  | I/O  | PDs, Ru                          |

| X0D39  | 1P <sup>0</sup> 8D <sup>3</sup> 16B <sup>11</sup>                                                  | I/0  | PD <sub>S</sub> , R <sub>U</sub> |

| X0D40  | 8D <sup>4</sup> 16B <sup>12</sup>                                                                  | I/0  | PD <sub>S</sub> , R <sub>U</sub> |

|        |                                                                                                    |      | (continued)                      |

-XMOS<sup>®</sup>

XS1-L8A-64-TQ128

| Signal | Function                          |                   | Туре | Properties                       |

|--------|-----------------------------------|-------------------|------|----------------------------------|

| X0D41  | 8D <sup>5</sup> 16B <sup>13</sup> |                   | I/O  | PD <sub>S</sub> , R <sub>U</sub> |

| X0D42  | 8D <sup>6</sup> 16B <sup>14</sup> |                   | I/O  | PD <sub>S</sub> , R <sub>U</sub> |

| X0D43  | 8D <sup>7</sup> 16B <sup>15</sup> |                   | I/O  | PU <sub>S</sub> , R <sub>U</sub> |

| X0D49  | XLC <sup>4</sup> <sub>out</sub>   | 32A <sup>0</sup>  | I/O  | PDs                              |

| X0D50  | XLC <sup>3</sup> <sub>out</sub>   | 32A <sup>1</sup>  | I/O  | PDs                              |

| X0D51  | XLC <sup>2</sup> <sub>out</sub>   | 32A <sup>2</sup>  | I/O  | PDs                              |

| X0D52  | XLC <sup>1</sup> <sub>out</sub>   | 32A <sup>3</sup>  | I/O  | PDs                              |

| X0D53  | XLC <sup>0</sup> <sub>out</sub>   | 32A <sup>4</sup>  | I/O  | PDs                              |

| X0D54  | XLC <sup>0</sup> <sub>in</sub>    | 32A <sup>5</sup>  | I/O  | PDs                              |

| X0D55  | XLC <sup>1</sup> <sub>in</sub>    | 32A <sup>6</sup>  | I/O  | PDs                              |

| X0D56  | XLC <sup>2</sup> <sub>in</sub>    | 32A <sup>7</sup>  | I/O  | PDs                              |

| X0D57  | XLC <sup>3</sup> <sub>in</sub>    | 32A <sup>8</sup>  | I/O  | PDs                              |

| X0D58  | XLC <sup>4</sup> <sub>in</sub>    | 32A <sup>9</sup>  | I/O  | PDs                              |

| X0D61  | XLD <sup>4</sup> <sub>out</sub>   | 32A <sup>10</sup> | I/O  | PDs                              |

| X0D62  | XLD <sup>3</sup> <sub>out</sub>   | 32A <sup>11</sup> | I/O  | PDs                              |

| X0D63  | XLD <sup>2</sup> <sub>out</sub>   | 32A <sup>12</sup> | I/O  | PDs                              |

| X0D64  | XLD <sup>1</sup> <sub>out</sub>   | 32A <sup>13</sup> | I/O  | PDs                              |

| X0D65  | XLD <sup>0</sup> <sub>out</sub>   | 32A <sup>14</sup> | I/O  | PDs                              |

| X0D66  | XLD <sup>0</sup> <sub>in</sub>    | 32A <sup>15</sup> | I/O  | PDs                              |

| X0D67  | XLD <sup>1</sup> <sub>in</sub>    | 32A <sup>16</sup> | I/O  | PDs                              |

| X0D68  | XLD <sup>2</sup> <sub>in</sub>    | 32A <sup>17</sup> | I/O  | PDs                              |

| X0D69  | XLD <sup>3</sup> <sub>in</sub>    | 32A <sup>18</sup> | I/O  | PDs                              |

| X0D70  | XLD <sup>4</sup> <sub>in</sub>    | 32A <sup>19</sup> | I/O  | PDs                              |

-XMOS<sup>®</sup>-

| Feature              | Bit  | Description                                                                                                                                                                                                                                |

|----------------------|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Disable JTAG         | 0    | The JTAG interface is disabled, making it impossible<br>for the tile state or memory content to be accessed<br>via the JTAG interface.                                                                                                     |

| Disable Link access  | 1    | Other tiles are forbidden access to the processor state<br>via the system switch. Disabling both JTAG and Link<br>access transforms an xCORE Tile into a "secure island"<br>with other tiles free for non-secure user application<br>code. |

| Secure Boot          | 5    | The xCORE Tile is forced to boot from address 0 of the OTP, allowing the xCORE Tile boot ROM to be bypassed ( <i>see</i> §7).                                                                                                              |

| Redundant rows       | 7    | Enables redundant rows in OTP.                                                                                                                                                                                                             |

| Sector Lock 0        | 8    | Disable programming of OTP sector 0.                                                                                                                                                                                                       |

| Sector Lock 1        | 9    | Disable programming of OTP sector 1.                                                                                                                                                                                                       |

| Sector Lock 2        | 10   | Disable programming of OTP sector 2.                                                                                                                                                                                                       |

| Sector Lock 3        | 11   | Disable programming of OTP sector 3.                                                                                                                                                                                                       |

| OTP Master Lock      | 12   | Disable OTP programming completely: disables up-<br>dates to all sectors and security register.                                                                                                                                            |

| Disable JTAG-OTP     | 13   | Disable all (read & write) access from the JTAG inter-<br>face to this OTP.                                                                                                                                                                |

| Disable Global Debug | 14   | Disables access to the DEBUG_N pin.                                                                                                                                                                                                        |

|                      | 2115 | General purpose software accessable security register available to end-users.                                                                                                                                                              |

|                      | 3122 | General purpose user programmable JTAG UserID code extension.                                                                                                                                                                              |

Figure 10: Security register features

port with resource ID 0x200100, and the OTP control is on a 16-bit port with ID 0x100300. Programming is performed through libotp and xburn.

### 8.2 SRAM

The xCORE Tile integrates a single 64KBSRAM bank for both instructions and data. All internal memory is 32 bits wide, and instructions are either 16-bit or 32-bit. Byte (8-bit), half-word (16-bit) or word (32-bit) accesses are supported and are executed within one tile clock cycle. There is no dedicated external memory interface, although data memory can be expanded through appropriate use of the ports.

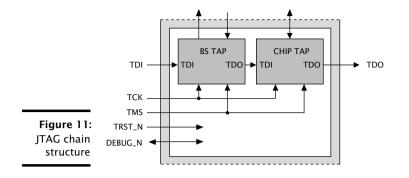

# 9 JTAG

The JTAG module can be used for loading programs, boundary scan testing, incircuit source-level debugging and programming the OTP memory.

The JTAG chain structure is illustrated in Figure 11. Directly after reset, two TAP controllers are present in the JTAG chain: the boundary scan TAP and the chip TAP. The boundary scan TAP is a standard 1149.1 compliant TAP that can be used for boundary scan of the I/O pins. The chip TAP provides access into the xCORE Tile, switch and OTP for loading code and debugging.

The TRST\_N pin must be asserted low during and after power up for 100 ns. If JTAG is not required, the TRST\_N pin can be tied to ground to hold the JTAG module in reset.

The DEBUG\_N pin is used to synchronize the debugging of multiple xCORE Tiles. This pin can operate in both output and input mode. In output mode and when configured to do so, DEBUG\_N is driven low by the device when the processor hits a debug break point. Prior to this point the pin will be tri-stated. In input mode and when configured to do so, driving this pin low will put the xCORE Tile into debug mode. Software can set the behavior of the xCORE Tile based on this pin. This pin should have an external pull up of  $4K7-47K\Omega$  or left not connected in single core applications.

The JTAG device identification register can be read by using the IDCODE instruction. Its contents are specified in Figure 12.

Figure 12: IDCODE return value

| Bit: | 31   |      |   |   |   |   |   |   |   |    |      | D   | evice | e Ide | ntifi | catio | on R | egis | ter |   |   |   |     |      |      |       |       |   |   | E | lit0 |

|------|------|------|---|---|---|---|---|---|---|----|------|-----|-------|-------|-------|-------|------|------|-----|---|---|---|-----|------|------|-------|-------|---|---|---|------|

|      | Vers | sion |   |   |   |   |   |   |   | Pa | rt N | umb | er    |       |       |       |      |      |     |   |   |   | Man | ufac | ture | r Ide | ntity | / |   |   | 1    |

| 0    | 0    | 0    | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0  | 0    | 0   | 0     | 0     | 0     | 0     | 0    | 1    | 0   | 0 | 1 | 1 | 0   | 0    | 0    | 1     | 1     | 0 | 0 | 1 | 1    |

|      | (    | )    |   |   | ( | ) |   |   | 0 | )  |      |     | (     | )     |       |       | 1    | 2    |     |   | ( | 5 |     |      | 1    | 3     |       |   |   | 3 |      |

The JTAG usercode register can be read by using the USERCODE instruction. Its contents are specified in Figure 13. The OTP User ID field is read from bits [22:31] of the security register , *see* §8.1 (all zero on unprogrammed devices).

| Figure 13:   |  |

|--------------|--|

| USERCODE     |  |

| return value |  |

| 12.       | Bit | 31 |   |   |      |      |    |   |   |     |   |     |      | ι | Jser | code | Reg | iste | r |   |   |       |      |       |     |   |   |   |   |   | В | Bit0 |

|-----------|-----|----|---|---|------|------|----|---|---|-----|---|-----|------|---|------|------|-----|------|---|---|---|-------|------|-------|-----|---|---|---|---|---|---|------|

| 13:       |     |    |   | 0 | TP U | lser | ID |   |   |     |   | Unu | ised |   |      |      |     |      |   |   |   | Silio | on I | Revis | ion |   |   |   |   |   |   |      |

| DE<br>lue | 0   | 0  | 0 | 0 | 0    | 0    | 0  | 0 | 0 | 0   | 0 | 0   | 0    | 0 | 1    | 0    | 1   | 0    | 0 | 0 | 0 | 0     | 0    | 0     | 0   | 0 | 0 | 0 | 0 | 0 | 0 | 0    |

| lue       |     | (  | ) |   |      | (    | )  |   |   | . ( | ) |     |      | 2 | 2    |      |     | 8    | 3 |   |   | (     | )    |       |     | ( | ) |   |   | ( | ) |      |

# 11 DC and Switching Characteristics

| Symbol   | Parameter                                                | MIN  | TYP  | MAX  | UNITS | Notes |

|----------|----------------------------------------------------------|------|------|------|-------|-------|

| VDD      | Tile DC supply voltage                                   | 0.95 | 1.00 | 1.05 | V     |       |

| VDDIO    | I/O supply voltage                                       | 3.00 | 3.30 | 3.60 | V     |       |

| PLL_AVDD | PLL analog supply                                        | 0.95 | 1.00 | 1.05 | V     |       |

| OTP_VCC  | OTP supply voltage                                       | 3.00 | 3.30 | 3.60 | V     |       |

| OTP_VPP  | OTP external programming voltage (optional program only) | 6.18 | 6.50 | 6.83 | V     |       |

| CI       | xCORE Tile I/O load<br>capacitance                       |      |      | 25   | pF    |       |

| Та       | Ambient operating<br>temperature (Commercial)            | 0    |      | 70   | °C    |       |

|          | Ambient operating<br>temperature (Industrial)            | -40  |      | 85   | °C    |       |

| Tj       | Junction temperature                                     |      |      | 125  | °C    |       |

| Tstg     | Storage temperature                                      | -65  |      | 150  | °C    |       |

### 11.1 Operating Conditions

Figure 16: Operating conditions

### 11.2 DC Characteristics

| Symbol | Parameter            | MIN   | ТҮР | MAX  | UNITS | Notes |

|--------|----------------------|-------|-----|------|-------|-------|

| V(IH)  | Input high voltage   | 2.00  |     | 3.60 | V     | A     |

| V(IL)  | Input low voltage    | -0.30 |     | 0.70 | V     | A     |

| V(OH)  | Output high voltage  | 2.00  |     |      | V     | B, C  |

| V(OL)  | Output low voltage   |       |     | 0.60 | V     | B, C  |

| R(PU)  | Pull-up resistance   |       | 35K |      | Ω     | D     |

| R(PD)  | Pull-down resistance |       | 35K |      | Ω     | D     |

Figure 17: DC characteristics

A All pins except power supply pins.

B Ports 1A, 1D, 1E, 1H, 1I, 1J, 1K and 1L are nominal 8 mA drivers, the remainder of the general-purpose I/Os are 4 mA.

C Measured with 4 mA drivers sourcing 4 mA, 8 mA drivers sourcing 8 mA.

D Used to guarantee logic state for an I/O when high impedance. The internal pull-ups/pull-downs should not be used to pull external circuitry.

## 11.3 ESD Stress Voltage

Figure 18 ESD stress voltage

| 18: | Symbol | Parameter        | MIN   | TYP | MAX  | UNITS | Notes |

|-----|--------|------------------|-------|-----|------|-------|-------|

| ess | HBM    | Human body model | -2.00 |     | 2.00 | KV    |       |

| age | MM     | Machine model    | -200  |     | 200  | V     |       |

### 11.4 Reset Timing

Figure 19: Reset timing

| Symbol  | Parameters          | MIN | ТҮР | MAX | UNITS | Notes |

|---------|---------------------|-----|-----|-----|-------|-------|

| T(RST)  | Reset pulse width   | 5   |     |     | us    |       |

| T(INIT) | Initialization time |     |     | 150 | μs    | А     |

A Shows the time taken to start booting after RST\_N has gone high.

#### 11.5 Power Consumption

| S  | ymbol   | Parameter                          | MIN | ТҮР | MAX | UNITS   | Notes      |

|----|---------|------------------------------------|-----|-----|-----|---------|------------|

| I( | DDCQ)   | Quiescent VDD current              |     | 14  |     | mA      | A, B, C    |

| P  | D       | Tile power dissipation             |     | 450 |     | µW/MIPS | A, D, E, F |

| IC | DD      | Active VDD current (Speed Grade 4) |     | 160 | 300 | mA      | A, G       |

|    |         | Active VDD current (Speed Grade 5) |     | 200 | 375 | mA      | А, Н       |

| I( | ADDPLL) | PLL_AVDD current                   |     |     | 7   | mA      | I          |

Figure 20: xCORE Tile currents

A Use for budgetary purposes only.

B Assumes typical tile and I/O voltages with no switching activity.

C Includes PLL current.

D Assumes typical tile and I/O voltages with nominal switching activity.

E Assumes 1 MHz = 1 MIPS.

F PD(TYP) value is the usage power consumption under typical operating conditions.

-XM()S

G Measurement conditions: VDD = 1.0 V, VDDIO = 3.3 V, 25 °C, 400 MHz, average device resource usage.

H Measurement conditions: VDD = 1.0 V, VDDIO = 3.3 V, 25 °C, 500 MHz, average device resource usage.

I PLL\_AVDD = 1.0 V

The tile power consumption of the device is highly application dependent and should be used for budgetary purposes only.

More detailed power analysis can be found in the XS1-L Power Consumption document, X2999.

|     | Symbol     | Parameter                      | MIN | ТҮР | MAX | UNITS  | Notes |

|-----|------------|--------------------------------|-----|-----|-----|--------|-------|

| _   | B(2blinkP) | 2b link bandwidth (packetized) |     |     | 87  | MBit/s | А, В  |

| 23: | B(5blinkP) | 5b link bandwidth (packetized) |     |     | 217 | MBit/s | А, В  |

| nk  | B(2blinkS) | 2b link bandwidth (streaming)  |     |     | 100 | MBit/s | В     |

| ce  | B(5blinkS) | 5b link bandwidth (streaming)  |     |     | 250 | MBit/s | В     |

### 11.8 xConnect Link Performance

Figure 23: Link performance

A Assumes 32-byte packet in 3-byte header mode. Actual performance depends on size of the header and payload.

B 7.5 ns symbol time.

The asynchronous nature of links means that the relative phasing of CLK clocks is not important in a multi-clock system, providing each meets the required stability criteria.

### 11.9 JTAG Timing

| Symbol   | Parameter                     | MIN | ТҮР | MAX | UNITS | Notes |

|----------|-------------------------------|-----|-----|-----|-------|-------|

| f(TCK_D) | TCK frequency (debug)         |     |     | 18  | MHz   |       |

| f(TCK_B) | TCK frequency (boundary scan) |     |     | 10  | MHz   |       |

| T(SETUP) | TDO to TCK setup time         | 5   |     |     | ns    | A     |

| T(HOLD)  | TDO to TCK hold time          | 5   |     |     | ns    | А     |

| T(DELAY) | TCK to output delay           |     |     | 15  | ns    | В     |

Figure 24: JTAG timing

A Timing applies to TMS and TDI inputs.

B Timing applies to TDO output from negative edge of TCK.

All JTAG operations are synchronous to TCK apart from the global asynchronous reset TRST\_N.

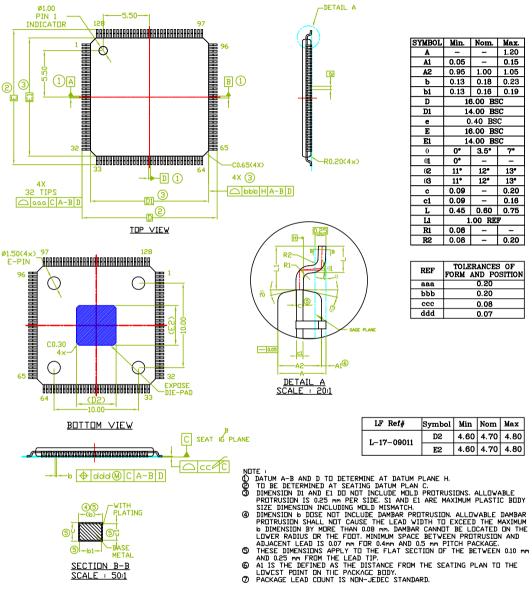

#### **Package Information** 12

| SYMBOL    | Min.      | Nom.    | Max. |  |  |  |

|-----------|-----------|---------|------|--|--|--|

| A         | -         | -       | 1.20 |  |  |  |

| A1        | 0.05      | -       | 0.15 |  |  |  |

| A2        | 0.95      | 1.00    | 1.05 |  |  |  |

| b         | 0.13      | 0.18    | 0.23 |  |  |  |

| b1        | 0.13      | 0.16    | 0.19 |  |  |  |

| D         | 10        | 3.00 BS | SC   |  |  |  |

| D1        | 14.00 BSC |         |      |  |  |  |

| e         | 0.40 BSC  |         |      |  |  |  |

| E         | 16.00 BSC |         |      |  |  |  |

| E1        | 14.00 BSC |         |      |  |  |  |

| θ         | 0"        | 3.5*    | 7°   |  |  |  |

| <b>61</b> | 0*        | -       | -    |  |  |  |

| <b>62</b> | 11•       | 12*     | 13*  |  |  |  |

| <b>63</b> | 11*       | 12*     | 13*  |  |  |  |

| С         | 0.09      | -       | 0.20 |  |  |  |

| c1        | 0.09      | -       | 0.16 |  |  |  |

| L         | 0.45      | 0.60    | 0.75 |  |  |  |

| 11        | 1.00 REF  |         |      |  |  |  |

| R1        | 0.08      | -       | -    |  |  |  |

| R2        | 0.08      | -       | 0.20 |  |  |  |

|           |           |         |      |  |  |  |

| REF | TOLERANCES OF<br>FORM AND POSITION |

|-----|------------------------------------|

| aaa | 0.20                               |

| bbb | 0.20                               |

| ccc | 0.08                               |

| ddd | 0.07                               |

| LF Ref#    | Symbol | Min  | Nom  | Max  |

|------------|--------|------|------|------|

| L-17-09011 | D2     | 4.60 | 4.70 | 4.80 |

| 1-11-09011 | E2     | 4.60 | 4.70 | 4.80 |

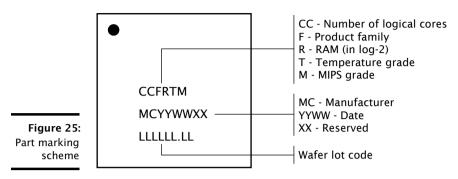

### 12.1 Part Marking

# 13 Ordering Information

|              | Product Code        | Marking | Qualification | Speed Grade |

|--------------|---------------------|---------|---------------|-------------|

|              | XS1-L8A-64-TQ128-C4 | 8L6C4   | Commercial    | 400 MIPS    |

| Figure 26:   | XS1-L8A-64-TQ128-C5 | 8L6C5   | Commercial    | 500 MIPS    |

| Orderable    | XS1-L8A-64-TQ128-I4 | 8L6I4   | Industrial    | 400 MIPS    |

| part numbers | XS1-L8A-64-TQ128-I5 | 8L6I5   | Industrial    | 500 MIPS    |

# **B** Processor Status Configuration

The processor status control registers can be accessed directly by the processor using processor status reads and writes (use getps(reg) and setps(reg,value) for reads and writes).

| Number    | Perm | Description                           |  |

|-----------|------|---------------------------------------|--|

| 0x00      | RW   | RAM base address                      |  |

| 0x01      | RW   | Vector base address                   |  |

| 0x02      | RW   | xCORE Tile control                    |  |

| 0x03      | RO   | xCORE Tile boot status                |  |

| 0x05      | RO   | Security configuration                |  |

| 0x06      | RW   | Ring Oscillator Control               |  |

| 0x07      | RO   | Ring Oscillator Value                 |  |

| 0x08      | RO   | Ring Oscillator Value                 |  |

| 0x09      | RO   | Ring Oscillator Value                 |  |

| 0x0A      | RO   | Ring Oscillator Value                 |  |

| 0x10      | DRW  | Debug SSR                             |  |

| 0x11      | DRW  | Debug SPC                             |  |

| 0x12      | DRW  | Debug SSP                             |  |

| 0x13      | DRW  | DGETREG operand 1                     |  |

| 0x14      | DRW  | DGETREG operand 2                     |  |

| 0x15      | DRW  | Debug interrupt type                  |  |

| 0x16      | DRW  | Debug interrupt data                  |  |

| 0x18      | DRW  | Debug core control                    |  |

| 0x20 0x27 | DRW  | Debug scratch                         |  |

| 0x30 0x33 | DRW  | Instruction breakpoint address        |  |

| 0x40 0x43 | DRW  | Instruction breakpoint control        |  |

| 0x50 0x53 | DRW  | Data watchpoint address 1             |  |

| 0x60 0x63 | DRW  | Data watchpoint address 2             |  |

| 0x70 0x73 | DRW  | Data breakpoint control register      |  |

| 0x80 0x83 | DRW  | Resources breakpoint mask             |  |

| 0x90 0x93 | DRW  | Resources breakpoint value            |  |

| 0x9C 0x9F | DRW  | Resources breakpoint control register |  |

-XMOS<sup>®</sup>

Figure 28: Summary

| Bits  | Perm | Init | Description                                                                        |

|-------|------|------|------------------------------------------------------------------------------------|

| 31:24 | RO   | -    | Reserved                                                                           |

| 23:16 | RO   |      | xCORE tile number on the switch.                                                   |

| 15:9  | RO   | -    | Reserved                                                                           |

| 8     | RO   |      | Set to 1 if boot from OTP is enabled.                                              |

| 7:0   | RO   |      | The boot mode pins MODE0, MODE1,, specifying the boot frequency, boot source, etc. |

0x03: xCORE Tile boot status

### **B.5** Security configuration: 0x05

Copy of the security register as read from OTP.

0x05: Security configuration

| Bits | Perm | Init | Description |  |

|------|------|------|-------------|--|

| 31:0 | RO   |      | Value.      |  |

### B.6 Ring Oscillator Control: 0x06

There are four free-running oscillators that clock four counters. The oscillators can be started and stopped using this register. The counters should only be read when the ring oscillator is stopped. The counter values can be read using four subsequent registers. The ring oscillators are asynchronous to the xCORE tile clock and can be used as a source of random bits.

**0x06** Ring Oscillator Control

| -       | Bits | Perm | Init | Description                                        |

|---------|------|------|------|----------------------------------------------------|

| 6:      | 31:2 | RO   | -    | Reserved                                           |

| g<br>or | 1    | RW   | 0    | Set to 1 to enable the xCORE tile ring oscillators |

| ol      | 0    | RW   | 0    | Set to 1 to enable the peripheral ring oscillators |

### B.7 Ring Oscillator Value: 0x07

This register contains the current count of the xCORE Tile Cell ring oscillator. This value is not reset on a system reset.

**0x07:** Ring Oscillator Value

|   | Bits  | Perm | Init | Description                   |  |

|---|-------|------|------|-------------------------------|--|

|   | 31:16 | RO   | -    | Reserved                      |  |

| l | 15:0  | RO   | -    | Ring oscillator counter data. |  |

| 0x11:     | Bits | Perm | Init | Description |

|-----------|------|------|------|-------------|

| Debug SPC | 31:0 | DRW  |      | Value.      |

#### B.13 Debug SSP: 0x12

This register contains the value of the SSP register when the debugger was called.

| 0x12:     | Bits | Perm | Init | Description |

|-----------|------|------|------|-------------|

| Debug SSP | 31:0 | DRW  |      | Value.      |

#### B.14 DGETREG operand 1: 0x13

The resource ID of the logical core whose state is to be read.

| 0x13:     | Bits | Perm | Init | Description              |

|-----------|------|------|------|--------------------------|

| DGETREG   | 31:8 | RO   | -    | Reserved                 |

| operand 1 | 7:0  | DRW  |      | Thread number to be read |

#### B.15 DGETREG operand 2: 0x14

Register number to be read by DGETREG

**0x14:** DGETREG operand 2

| Bits | Perm | Init | Description                |

|------|------|------|----------------------------|

| 31:5 | RO   | -    | Reserved                   |

| 4:0  | DRW  |      | Register number to be read |

### B.16 Debug interrupt type: 0x15

Register that specifies what activated the debug interrupt.

·XMC

| Bits  | Perm | Init | Description                                                                                                                                                                                                                                       |

|-------|------|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 31:18 | RO   | -    | Reserved                                                                                                                                                                                                                                          |

| 17:16 | DRW  |      | If the debug interrupt was caused by a hardware breakpoint<br>or hardware watchpoint, this field contains the number of the<br>breakpoint or watchpoint. If multiple breakpoints or watch-<br>points trigger at once, the lowest number is taken. |

| 15:8  | DRW  |      | If the debug interrupt was caused by a logical core, this field contains the number of that core. Otherwise this field is 0.                                                                                                                      |

| 7:3   | RO   | -    | Reserved                                                                                                                                                                                                                                          |

| 2:0   | DRW  | 0    | Indicates the cause of the debug interrupt<br>1: Host initiated a debug interrupt through JTAG<br>2: Program executed a DCALL instruction<br>3: Instruction breakpoint<br>4: Data watch point<br>5: Resource watch point                          |

**0x15:** Debug interrupt type

### B.17 Debug interrupt data: 0x16

On a data watchpoint, this register contains the effective address of the memory operation that triggered the debugger. On a resource watchpoint, it countains the resource identifier.

0x16 Debug interrupt data

| <b>0x16:</b><br>Debug | Bits | Perm | Init | Description |

|-----------------------|------|------|------|-------------|

| ot data               | 31:0 | DRW  |      | Value.      |

### B.18 Debug core control: 0x18

This register enables the debugger to temporarily disable logical cores. When returning from the debug interrupts, the cores set in this register will not execute. This enables single stepping to be implemented.

**0x18:** Debug core control

| Bits | Perm | Init | Description                                                                                                                                                   |

|------|------|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 31:8 | RO   | -    | Reserved                                                                                                                                                      |

| 7:0  | DRW  |      | 1-hot vector defining which logical cores are stopped when not<br>in debug mode. Every bit which is set prevents the respective<br>logical core from running. |

0x50 .. 0x53: Data watchpoint address 1

| Data<br>Ipoint | Bits | Perm | Init | Description |

|----------------|------|------|------|-------------|

| ress 1         | 31:0 | DRW  |      | Value.      |

#### B.23 Data watchpoint address 2: 0x60 .. 0x63

This set of registers contains the second address for the four data watchpoints.

**0x60 .. 0x63:** Data watchpoint address 2

| ita<br>int | Bits | Perm | Init | Description |

|------------|------|------|------|-------------|

| 5 2        | 31:0 | DRW  |      | Value.      |

### B.24 Data breakpoint control register: 0x70 .. 0x73

This set of registers controls each of the four data watchpoints.

|        | Bits  | Perm | Init | Description                                                                                                                                                                                                                                                                                       |

|--------|-------|------|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|        | 31:24 | RO   | -    | Reserved                                                                                                                                                                                                                                                                                          |

|        | 23:16 | DRW  | 0    | A bit for each logical core in the tile allowing the breakpoint to be enabled individually for each logical core.                                                                                                                                                                                 |

|        | 15:3  | RO   | -    | Reserved                                                                                                                                                                                                                                                                                          |

|        | 2     | DRW  | 0    | Set to 1 to enable breakpoints to be triggered on loads. Breakpoints always trigger on stores.                                                                                                                                                                                                    |

| •<br>• | 1     | DRW  | 0    | By default, data watchpoints trigger if memory in the range [Address1Address2] is accessed (the range is inclusive of Address1 and Address2). If set to 1, data watchpoints trigger if memory outside the range (Address2Address1) is accessed (the range is exclusive of Address2 and Address1). |

|        | 0     | DRW  | 0    | When 1 the instruction breakpoint is enabled.                                                                                                                                                                                                                                                     |

0x70 .. 0x73: Data breakpoint control register

### B.25 Resources breakpoint mask: 0x80 .. 0x83

This set of registers contains the mask for the four resource watchpoints.

-XMOS

37

# C Tile Configuration

The xCORE Tile control registers can be accessed using configuration reads and writes (use write\_tile\_config\_reg(tileref, ...) and read\_tile\_config\_reg(tileref,  $\rightarrow$  ...) for reads and writes).

| Number    | Perm | Description                                    |

|-----------|------|------------------------------------------------|

| 0x00      | RO   | Device identification                          |

| 0x01      | RO   | xCORE Tile description 1                       |

| 0x02      | RO   | xCORE Tile description 2                       |

| 0x04      | CRW  | Control PSwitch permissions to debug registers |

| 0x05      | CRW  | Cause debug interrupts                         |

| 0x06      | RW   | xCORE Tile clock divider                       |

| 0x07      | RO   | Security configuration                         |

| 0x10 0x13 | RO   | PLink status                                   |

| 0x20 0x27 | CRW  | Debug scratch                                  |

| 0x40      | RO   | PC of logical core 0                           |

| 0x41      | RO   | PC of logical core 1                           |

| 0x42      | RO   | PC of logical core 2                           |

| 0x43      | RO   | PC of logical core 3                           |

| 0x44      | RO   | PC of logical core 4                           |

| 0x45      | RO   | PC of logical core 5                           |

| 0x46      | RO   | PC of logical core 6                           |

| 0x47      | RO   | PC of logical core 7                           |

| 0x60      | RO   | SR of logical core 0                           |

| 0x61      | RO   | SR of logical core 1                           |

| 0x62      | RO   | SR of logical core 2                           |

| 0x63      | RO   | SR of logical core 3                           |

| 0x64      | RO   | SR of logical core 4                           |

| 0x65      | RO   | SR of logical core 5                           |

| 0x66      | RO   | SR of logical core 6                           |

| 0x67      | RO   | SR of logical core 7                           |

| 0x80 0x9F | RO   | Chanend status                                 |

-XMOS

Figure 29: Summary 0x04: Control PSwitch permissions to debug registers

| Bits | Perm | Init | Description                                                                                                 |

|------|------|------|-------------------------------------------------------------------------------------------------------------|

| 31:1 | RO   | -    | Reserved                                                                                                    |

| 0    | CRW  |      | Set to 1 to restrict PSwitch access to all CRW marked registers to become read-only rather than read-write. |

### C.5 Cause debug interrupts: 0x05

This register can be used to raise a debug interrupt in this xCORE tile.

**0x05:** Cause debug interrupts

| Bits | Perm | Init | Description                                             |

|------|------|------|---------------------------------------------------------|

| 31:2 | RO   | -    | Reserved                                                |

| 1    | RO   | 0    | Set to 1 when the processor is in debug mode.           |

| 0    | CRW  | 0    | Set to 1 to request a debug interrupt on the processor. |

### C.6 xCORE Tile clock divider: 0x06

This register contains the value used to divide the PLL clock to create the xCORE tile clock. The divider is enabled under control of the tile control register

0x06: xCORE Tile clock divider

| 6: | Bits | Perm | Init | Description                           |

|----|------|------|------|---------------------------------------|

| le | 31:8 | RO   | -    | Reserved                              |

| er | 7:0  | RW   |      | Value of the clock divider minus one. |

### C.7 Security configuration: 0x07

Copy of the security register as read from OTP.

0x07: Security configuration

|   | Bits | Perm | Init | Description |

|---|------|------|------|-------------|

| n | 31:0 | RO   |      | Value.      |

### C.8 PLink status: 0x10 .. 0x13

Status of each of the four processor links; connecting the xCORE tile to the switch.

| Bits  | Perm | Init | Description                                                                                                    |  |

|-------|------|------|----------------------------------------------------------------------------------------------------------------|--|

| 31:26 | RO   | -    | Reserved                                                                                                       |  |

| 25:24 | RO   |      | 00 - ChannelEnd, 01 - ERROR, 10 - PSCTL, 11 - Idle.                                                            |  |

| 23:16 | RO   |      | Based on SRC_TARGET_TYPE value, it represents channelEnd ID or Idle status.                                    |  |

| 15:6  | RO   | -    | Reserved                                                                                                       |  |

| 5:4   | RO   |      | Two-bit network identifier                                                                                     |  |

| 3     | RO   | -    | Reserved                                                                                                       |  |

| 2     | RO   |      | 1 when the current packet is considered junk and will be thrown away.                                          |  |

| 1     | RO   | 0    | Set to 1 if the switch is routing data into the link, and if a route exists from another link.                 |  |

| 0     | RO   | 0    | Set to 1 if the link is routing data into the switch, and if a route is created to another link on the switch. |  |

0x10 .. 0x13: PLink status

### C.9 Debug scratch: 0x20 .. 0x27

A set of registers used by the debug ROM to communicate with an external debugger, for example over the switch. This is the same set of registers as the Debug Scratch registers in the processor status.

0x20 .. 0x27 Debug scratch

| 0 0x27:<br>Debug | Bits | Perm | Init | Description |

|------------------|------|------|------|-------------|

| scratch          | 31:0 | CRW  |      | Value.      |

### C.10 PC of logical core 0: 0x40

Value of the PC of logical core 0.

**0x40** PC of logical core 0

| al | Bits | Perm | Init | Description |

|----|------|------|------|-------------|

| 0  | 31:0 | RO   |      | Value.      |

### C.11 PC of logical core 1: 0x41

0x41: Bits PC of logical core 1

Perm Init Description 31:0 RO Value.

### C.12 PC of logical core 2: 0x42

| <b>0x42:</b><br>PC of logical | Bits | Perm | Init | Description |

|-------------------------------|------|------|------|-------------|

| core 2                        | 31:0 | RO   |      | Value.      |

### C.13 PC of logical core 3: 0x43

| 0x43:         |      |      |      |             |

|---------------|------|------|------|-------------|

| PC of logical | Bits | Perm | Init | Description |

| core 3        | 31:0 | RO   |      | Value.      |

### C.14 PC of logical core 4: 0x44

0x44: PC of logical core 4

Bits

31:0

| Perm | Init | Description |

|------|------|-------------|

| RO   |      | Value.      |

### C.15 PC of logical core 5: 0x45

| 0x45:         |      |      |      |             |

|---------------|------|------|------|-------------|

| PC of logical | Bits | Perm | Init | Description |

| core 5        | 31:0 | RO   |      | Value.      |

|                        | Bits  | Perm | Init | Description                                        |

|------------------------|-------|------|------|----------------------------------------------------|

|                        | 31:24 | RO   | -    | Reserved                                           |

| <b>0x01:</b><br>System | 23:16 | RO   |      | Number of links on the switch.                     |

| switch                 | 15:8  | RO   |      | Number of cores that are connected to this switch. |

| description            | 7:0   | RO   |      | Number of links per processor.                     |

### D.3 Switch configuration: 0x04

This register enables the setting of two security modes (that disable updates to the PLL or any other registers) and the header-mode.

| Bits | Perm | Init | Description                                                                                        |  |

|------|------|------|----------------------------------------------------------------------------------------------------|--|

| 31   | RO   | 0    | Set to 1 to disable any write access to the configuration registers in this switch.                |  |

| 30:9 | RO   | -    | Reserved                                                                                           |  |

| 8    | RO   | 0    | Set to 1 to disable updates to the PLL configuration register.                                     |  |

| 7:1  | RO   | -    | Reserved                                                                                           |  |

| 0    | RO   | 0    | Header mode. Set to 1 to enable 1-byte headers. This must be performed on all nodes in the system. |  |

**0x04:** Switch configuration

### D.4 Switch node identifier: 0x05

This register contains the node identifier.

0x05 Switch node identifier

|               | Bits  | Perm | Init | Description                                                                                                                            |

|---------------|-------|------|------|----------------------------------------------------------------------------------------------------------------------------------------|

| -             | 31:16 | RO   | -    | Reserved                                                                                                                               |

| 5:<br>e<br>er | 15:0  | RW   | 0    | The unique 16-bit ID of this node. This ID is matched most-<br>significant-bit first with incoming messages for routing pur-<br>poses. |

### D.5 PLL settings: 0x06

An on-chip PLL multiplies the input clock up to a higher frequency clock, used to clock the I/O, processor, and switch, see Oscillator. Note: a write to this register will cause the tile to be reset.

Pins MODE0 and MODE1 are set to the correct value for the chosen oscillator frequency. The MODE settings are shown in the Oscillator section, Section 6. If you have a choice between two values, choose the value with the highest multiplier ratio since that will boot faster.

#### H.5 USB ULPI Mode

This section can be skipped if you do not have an external USB PHY.

- □ If using ULPI, the ULPI signals are connected to specific ports as shown in Section E.

- □ If using ULPI, the ports that are used internally are not connected, see Section E. (Note that this limitation only applies when the ULPI is enabled, they can still be used before or after the ULPI is being used.)

#### H.6 Boot

- □ The device is connected to a SPI flash for booting, connected to X0D0, X0D01, X0D10, and X0D11 (Section 7). If not, you must boot the device through OTP or JTAG.

- □ The device that is connected to flash has both MODE2 and MODE3 connected to pin 3 on the xSYS Header (MSEL). If no debug adapter connection is supported (not recommended) MODE2 and MODE3 are to be left NC (Section 7).

- ☐ The SPI flash that you have chosen is supported by **xflash**, or you have created a specification file for it.

#### H.7 JTAG, XScope, and debugging

- $\Box$  You have decided as to whether you need an XSYS header or not (Section G)

- □ If you included an XSYS header, you connected pin 3 to any MODE2/MODE3 pin that would otherwise be NC (Section G).

- ☐ If you have not included an XSYS header, you have devised a method to program the SPI-flash or OTP (Section G).

#### H.8 GPIO

You have not mapped both inputs and outputs to the same multi-bit port.

-XM()S