# E·XFL

Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

# Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                 |

|----------------------------|------------------------------------------------------------------------|

| Core Processor             | CIP-51 8051                                                            |

| Core Size                  | 8-Bit                                                                  |

| Speed                      | 25MHz                                                                  |

| Connectivity               | I <sup>2</sup> C, SMBus, SPI, UART/USART                               |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                  |

| Number of I/O              | 16                                                                     |

| Program Memory Size        | 4KB (4K x 8)                                                           |

| Program Memory Type        | FLASH                                                                  |

| EEPROM Size                | -                                                                      |

| RAM Size                   | 512 x 8                                                                |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                            |

| Data Converters            | A/D 9x12b                                                              |

| Oscillator Type            | Internal                                                               |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                      |

| Mounting Type              | Surface Mount                                                          |

| Package / Case             | 20-UFQFN Exposed Pad                                                   |

| Supplier Device Package    | 20-QFN (3x3)                                                           |

| Purchase URL               | https://www.e-xfl.com/product-detail/silicon-labs/efm8sb10f4g-a-qfn20r |

|                            |                                                                        |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# 1. Feature List

The EFM8SB1 highlighted features are listed below.

- Core:

- Pipelined CIP-51 Core

- · Fully compatible with standard 8051 instruction set

- · 70% of instructions execute in 1-2 clock cycles

- 25 MHz maximum operating frequency

- Memory:

- Up to 8 kB flash memory, in-system re-programmable from firmware.

- Up to 512 bytes RAM (including 256 bytes standard 8051 RAM and 256 bytes on-chip XRAM)

- · Power:

- · Internal LDO regulator for CPU core voltage

- · Power-on reset circuit and brownout detectors

- I/O: Up to 17 total multifunction I/O pins:

- Flexible peripheral crossbar for peripheral routing

- 5 mA source, 12.5 mA sink allows direct drive of LEDs

- · Clock Sources:

- Internal 20 MHz low power oscillator with ±10% accuracy

- Internal 24.5 MHz precision oscillator with ±2% accuracy

- Internal 16.4 kHz low-frequency oscillator or RTC 32 kHz crystal (RTC crystal not available on CSP16 packages)

- External crystal, RC, C, and CMOS clock options

- Timers/Counters and PWM:

- 32-bit Real Time Clock (RTC)

- 3-channel Programmable Counter Array (PCA) supporting PWM, capture/compare, and frequency output modes with watchdog timer function

- 4 x 16-bit general-purpose timers

- Communications and Digital Peripherals:

- UART

- SPI<sup>™</sup> Master / Slave

- SMBus™ / I2C™ Master / Slave

- 16-bit CRC unit, supporting automatic CRC of flash at 256byte boundaries

- Analog:

- Capacitive Sense (CS0)

- Programmable current reference (IREF0)

- 12-Bit Analog-to-Digital Converter (ADC0)

- 1 x Low-current analog comparator

- On-Chip, Non-Intrusive Debugging

- · Full memory and register inspection

- Four hardware breakpoints, single-stepping

- · Pre-loaded UART bootloader

- Temperature range -40 to 85 °C

- Single power supply 1.8 to 3.6 V

- · QSOP24, QFN24, QFN20, and CSP16 packages

With on-chip power-on reset, voltage supply monitor, watchdog timer, and clock oscillator, the EFM8SB1 devices are truly standalone system-on-a-chip solutions. The flash memory is reprogrammable in-circuit, providing non-volatile data storage and allowing field upgrades of the firmware. The on-chip debugging interface (C2) allows non-intrusive (uses no on-chip resources), full speed, in-circuit debugging using the production MCU installed in the final application. This debug logic supports inspection and modification of memory and registers, setting breakpoints, single stepping, and run and halt commands. All analog and digital peripherals are fully functional while debugging. Each device is specified for 1.8 to 3.6 V operation. Devices are AEC-Q100 qualified (Grade 3) and are available in 16-pin CSP, 20-pin QFN, 24-pin QFN, or 24-pin QSOP packages. All package options are lead-free and RoHS compliant.

**Note:** CSP devices can be handled and soldered using industry standard surface mount assembly techniques. However, because CSP devices are essentially a piece of silicon and are not encapsulated in plastic, they are susceptible to mechanical damage and may be sensitive to light. When CSP packages must be used in an environment exposed to light, it may be necessary to cover the top and sides with an opaque material.

#### 3.4 Clocking

The CPU core and peripheral subsystem may be clocked by both internal and external oscillator resources. By default, the system clock comes up running from the 20 MHz low power oscillator divided by 8.

- Provides clock to core and peripherals.

- 20 MHz low power oscillator (LPOSC0), accurate to ±10% over supply and temperature corners.

- 24.5 MHz internal oscillator (HFOSC0), accurate to ±2% over supply and temperature corners.

- 16.4 kHz low-frequency oscillator (LFOSC0) or external RTC 32 kHz crystal.

- · External RC, C, CMOS, and high-frequency crystal clock options (EXTCLK).

- Clock divider with eight settings for flexible clock scaling: Divide the selected clock source by 1, 2, 4, 8, 16, 32, 64, or 128.

#### 3.5 Counters/Timers and PWM

#### Real Time Clock (RTC0)

The RTC is an ultra low power, 36 hour 32-bit independent time-keeping Real Time Clock with alarm. The RTC has a dedicated 32 kHz oscillator. No external resistor or loading capacitors are required, and a missing clock detector features alerts the system if the external crystal fails. The on-chip loading capacitors are programmable to 16 discrete levels allowing compatibility with a wide range of crystals.

The RTC module includes the following features:

- Up to 36 hours (32-bit) of independent time keeping.

- Support for internal 16.4 kHz low frequency oscillator (LFOSC0) or external 32 kHz crystal (crystal not available on CSP16 packages).

- · Internal crystal loading capacitors with 16 levels.

- · Operation in the lowest power mode and across the full supported voltage range.

- · Alarm and oscillator failure events to wake from the lowest power mode or reset the device.

- · Buffered clock output available for other system devices even in the lowest power mode.

# Programmable Counter Array (PCA0)

The programmable counter array (PCA) provides multiple channels of enhanced timer and PWM functionality while requiring less CPU intervention than standard counter/timers. The PCA consists of a dedicated 16-bit counter/timer and one 16-bit capture/compare module for each channel. The counter/timer is driven by a programmable timebase that has flexible external and internal clocking options. Each capture/compare module may be configured to operate independently in one of five modes: Edge-Triggered Capture, Software Timer, High-Speed Output, Frequency Output, or Pulse-Width Modulated (PWM) Output. Each capture/compare module has its own associated I/O line (CEXn) which is routed through the crossbar to port I/O when enabled.

- · 16-bit time base.

- · Programmable clock divisor and clock source selection.

- · Up to three independently-configurable channels

- 8, 9, 10, 11 and 16-bit PWM modes (edge-aligned operation).

- · Frequency output mode.

- · Capture on rising, falling or any edge.

- · Compare function for arbitrary waveform generation.

- Software timer (internal compare) mode.

- Integrated watchdog timer.

| EFM8SB1 Data Sheet               |

|----------------------------------|

| <b>Electrical Specifications</b> |

Units

Max

| Parameter |

|-----------|

| Note:     |

Symbol Conditions Min

Тур

1. Based on device characterization data; Not production tested.

- 2. SYSCLK must be at least 32 kHz to enable debugging.

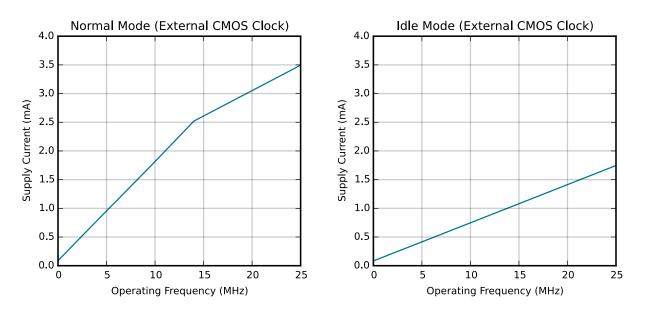

- 3. Digital Supply Current depends upon the particular code being executed. The values in this table are obtained with the CPU executing an "simp \$" loop, which is the compiled form of a while(1) loop in C. One iteration requires 3 CPU clock cycles, and the flash memory is read on each cycle. The supply current will vary slightly based on the physical location of the simp instruction and the number of flash address lines that toggle as a result. In the worst case, current can increase by up to 30% if the simp loop straddles a 64-byte flash address boundary (e.g., 0x007F to 0x0080). Real-world code with larger loops and longer linear sequences will have few transitions across the 64-byte address boundaries.

- 4. Includes supply current from regulator and oscillator source (24.5 MHz high-frequency oscillator, 20 MHz low-power oscillator, 1 MHz external oscillator, or 32.768 kHz RTC oscillator).

- 5. IDD can be estimated for frequencies < 14 MHz by simply multiplying the frequency of interest by the frequency sensitivity number for that range, then adding an offset of 84 µA. When using these numbers to estimate I<sub>DD</sub> for > 14 MHz, the estimate should be the current at 25 MHz minus the difference in current indicated by the frequency sensitivity number. For example: V<sub>DD</sub> = 3.0 V; F = 20 MHz, I<sub>DD</sub> = 3.6 mA - (25 MHz - 20 MHz) x 0.088 mA/MHz = 3.16 mA assuming the same oscillator setting.

- 6. Idle IDD can be estimated by taking the current at 25 MHz minus the difference in current indicated by the frequency sensitivity number. For example: V<sub>DD</sub> = 3.0 V; F = 5 MHz, Idle I<sub>DD</sub> = 1.75 mA – (25 MHz – 5 MHz) x 0.067 mA/MHz = 0.41 mA.

- 7. ADC0 always-on power excludes internal reference supply current.

- 8. The internal reference is enabled as-needed when operating the ADC in burst mode to save power.

- 9. Includes only current from regulator, CS module, and MCU in suspend mode.

10. IREF0 supply current only. Does not include current sourced or sunk from IREF0 output pin.

# 4.1.3 Reset and Supply Monitor

| Parameter                                                            | Symbol            | Test Condition                                          | Min  | Тур  | Max  | Unit |

|----------------------------------------------------------------------|-------------------|---------------------------------------------------------|------|------|------|------|

| VDD Supply Monitor Threshold                                         | V <sub>VDDM</sub> | Reset Trigger                                           | 1.7  | 1.75 | 1.8  | V    |

|                                                                      | V <sub>WARN</sub> | Early Warning                                           | 1.8  | 1.85 | 1.9  | V    |

| VDD Supply Monitor Turn-On Time                                      | t <sub>MON</sub>  |                                                         | _    | 300  | _    | ns   |

| Power-On Reset (POR) Monitor                                         | V <sub>POR</sub>  | Rising Voltage on V <sub>DD</sub>                       | _    | 1.75 | _    | V    |

| Threshold                                                            |                   | Falling Voltage on V <sub>DD</sub>                      | 0.75 | 1.0  | 1.3  | V    |

| V <sub>DD</sub> Ramp Time                                            | t <sub>RMP</sub>  | Time to $V_{DD} \ge 1.8 V$                              | _    |      | 3    | ms   |

| Reset Delay from non-POR source                                      | t <sub>RST</sub>  | Time between release of reset source and code execution | -    | 10   | _    | μs   |

| Reset Delay from POR                                                 | t <sub>POR</sub>  | Relative to V <sub>DD</sub> > V <sub>POR</sub>          | 3    | 10   | 31   | ms   |

| RST Low Time to Generate Reset                                       | t <sub>RSTL</sub> |                                                         | 15   | _    | _    | μs   |

| Missing Clock Detector Response<br>Time (final rising edge to reset) | t <sub>MCD</sub>  | F <sub>SYSCLK</sub> > 1 MHz                             | 100  | 650  | 1000 | μs   |

| Missing Clock Detector Trigger<br>Frequency                          | F <sub>MCD</sub>  |                                                         | _    | 7    | 10   | kHz  |

# Table 4.3. Reset and Supply Monitor

#### 4.1.4 Flash Memory

#### Table 4.4. Flash Memory

| Parameter                      | Symbol             | Test Condition     | Min  | Тур   | Max | Units  |

|--------------------------------|--------------------|--------------------|------|-------|-----|--------|

| Write Time <sup>1</sup>        | t <sub>WRITE</sub> | One Byte           | 57   | 64    | 71  | μs     |

| Erase Time <sup>1</sup>        | t <sub>ERASE</sub> | One Page           | 28   | 32    | 36  | ms     |

| Endurance (Write/Erase Cycles) | N <sub>WE</sub>    |                    | 20 k | 100 k | —   | Cycles |

| CRC Calculation Time           | t <sub>CRC</sub>   | One 256-Byte Block |      | 21.5  | _   | μs     |

|                                |                    | SYSCLK = 24.5 MHz  |      |       |     |        |

#### Note:

1. Does not include sequencing time before and after the write/erase operation, which may be multiple SYSCLK cycles.

2. Data Retention Information is published in the Quarterly Quality and Reliability Report.

## 4.1.5 Power Management Timing

## Table 4.5. Power Management Timing

| Parameter                 | Symbol                      | Test Condition                               | Min | Тур | Max | Units   |

|---------------------------|-----------------------------|----------------------------------------------|-----|-----|-----|---------|

| Idle Mode Wake-up Time    | t <sub>IDLEWK</sub>         |                                              | 2   | _   | 3   | SYSCLKs |

| Suspend Mode Wake-up Time | t <sub>SUS-</sub><br>PENDWK | CLKDIV = 0x00<br>Low Power or Precision Osc. | _   | 400 | _   | ns      |

| Sleep Mode Wake-up Time   | t <sub>SLEEPWK</sub>        |                                              |     | 2   |     | μs      |

# 4.1.6 Internal Oscillators

#### Table 4.6. Internal Oscillators

| Parameter                       | Symbol             | Test Condition                    | Min  | Тур  | Max  | Unit |

|---------------------------------|--------------------|-----------------------------------|------|------|------|------|

| High Frequency Oscillator 0 (24 | .5 MHz)            |                                   |      |      |      |      |

| Oscillator Frequency            | fHFOSC0            | Full Temperature and Supply Range | 24   | 24.5 | 25   | MHz  |

| Low Power Oscillator (20 MHz)   | I                  |                                   |      | 1    | 1    | 1    |

| Oscillator Frequency            | f <sub>LPOSC</sub> | Full Temperature and Supply Range | 18   | 20   | 22   | MHz  |

| Low Frequency Oscillator (16.4  | kHz internal       | RTC oscillator)                   |      |      |      |      |

| Oscillator Frequency            | f <sub>LFOSC</sub> | Full Temperature and Supply Range | 13.1 | 16.4 | 19.7 | kHz  |

# 4.1.7 Crystal Oscillator

| Parameter             | Symbol            | Test Condition | Min  | Тур | Мах | Unit |

|-----------------------|-------------------|----------------|------|-----|-----|------|

| Crystal Frequency     | f <sub>XTAL</sub> |                | 0.02 | —   | 25  | MHz  |

| Crystal Drive Current | I <sub>XTAL</sub> | XFCN = 0       | _    | 0.5 | _   | μA   |

|                       |                   | XFCN = 1       | _    | 1.5 | _   | μA   |

|                       |                   | XFCN = 2       | _    | 4.8 | _   | μA   |

|                       |                   | XFCN = 3       | —    | 14  | _   | μA   |

|                       |                   | XFCN = 4       | _    | 40  | _   | μA   |

|                       |                   | XFCN = 5       | —    | 120 | _   | μA   |

|                       |                   | XFCN = 6       | —    | 550 | _   | μA   |

|                       |                   | XFCN = 7       | _    | 2.6 | —   | mA   |

# Table 4.7. Crystal Oscillator

# 4.1.8 External Clock Input

# Table 4.8. External Clock Input

| Parameter                             | Symbol             | Test Condition | Min | Тур | Max | Unit |

|---------------------------------------|--------------------|----------------|-----|-----|-----|------|

| External Input CMOS Clock             | f <sub>CMOS</sub>  |                | 0   | _   | 25  | MHz  |

| Frequency (at EXTCLK pin)             |                    |                |     |     |     |      |

| External Input CMOS Clock High Time   | t <sub>CMOSH</sub> |                | 18  | _   | _   | ns   |

| External Input CMOS Clock Low<br>Time | t <sub>CMOSL</sub> |                | 18  |     | _   | ns   |

# 4.1.12 Comparators

| Parameter                      | Symbol             | Test Condition       | Min | Тур  | Max | Unit |

|--------------------------------|--------------------|----------------------|-----|------|-----|------|

| Response Time, CPMD = 00       | t <sub>RESP0</sub> | +100 mV Differential | _   | 120  | _   | ns   |

| (Highest Speed)                |                    | -100 mV Differential | _   | 110  | _   | ns   |

| Response Time, CPMD = 11 (Low- | t <sub>RESP3</sub> | +100 mV Differential |     | 1.25 | _   | μs   |

| est Power)                     |                    | –100 mV Differential | _   | 3.2  | _   | μs   |

| Positive Hysterisis            | HYS <sub>CP+</sub> | CPHYP = 00           |     | 0.4  | _   | mV   |

| Mode 0 (CPMD = 00)             |                    | CPHYP = 01           |     | 8    | _   | mV   |

|                                |                    | CPHYP = 10           | _   | 16   | _   | mV   |

|                                |                    | CPHYP = 11           |     | 32   | _   | mV   |

| Negative Hysterisis            | HYS <sub>CP-</sub> | CPHYN = 00           | _   | -0.4 | _   | mV   |

| Mode 0 (CPMD = 00)             |                    | CPHYN = 01           | _   | -8   | _   | mV   |

|                                |                    | CPHYN = 10           |     | -16  | _   | mV   |

|                                |                    | CPHYN = 11           | _   | -32  | _   | mV   |

| Positive Hysterisis            | HYS <sub>CP+</sub> | CPHYP = 00           |     | 0.5  | _   | mV   |

| Mode 1 (CPMD = 01)             |                    | CPHYP = 01           | _   | 6    | _   | mV   |

|                                |                    | CPHYP = 10           | _   | 12   | _   | mV   |

|                                |                    | CPHYP = 11           |     | 24   | _   | mV   |

| Negative Hysterisis            | HYS <sub>CP-</sub> | CPHYN = 00           | _   | -0.5 | _   | mV   |

| Mode 1 (CPMD = 01)             |                    | CPHYN = 01           | _   | -6   | _   | mV   |

|                                |                    | CPHYN = 10           |     | –12  | _   | mV   |

|                                |                    | CPHYN = 11           | _   | -24  | _   | mV   |

| Positive Hysterisis            | HYS <sub>CP+</sub> | CPHYP = 00           |     | 0.7  | _   | mV   |

| Mode 2 (CPMD = 10)             |                    | CPHYP = 01           | _   | 4.5  | _   | mV   |

|                                |                    | CPHYP = 10           |     | 9    | _   | mV   |

|                                |                    | CPHYP = 11           | _   | 18   | _   | mV   |

| Negative Hysterisis            | HYS <sub>CP-</sub> | CPHYN = 00           | _   | -0.6 | _   | mV   |

| Mode 2 (CPMD = 10)             |                    | CPHYN = 01           | _   | -4.5 | _   | mV   |

|                                |                    | CPHYN = 10           | _   | -9   | _   | mV   |

|                                |                    | CPHYN = 11           | _   | -18  | _   | mV   |

| Positive Hysteresis            | HYS <sub>CP+</sub> | CPHYP = 00           |     | 1.5  | _   | mV   |

| Mode 3 (CPMD = 11)             |                    | CPHYP = 01           |     | 4    | _   | mV   |

|                                |                    | CPHYP = 10           | _   | 8    | _   | mV   |

|                                |                    | CPHYP = 11           |     | 16   | _   | mV   |

## Table 4.12. Comparators

# 4.1.16 SMBus

| Parameter                                       | Symbol               | Test Condition | Min              | Тур | Max              | Unit |

|-------------------------------------------------|----------------------|----------------|------------------|-----|------------------|------|

| Standard Mode (100 kHz Class)                   |                      |                |                  |     |                  |      |

| I2C Operating Frequency                         | f <sub>I2C</sub>     |                | 0                | _   | 70 <sup>2</sup>  | kHz  |

| SMBus Operating Frequency                       | f <sub>SMB</sub>     |                | 40 <sup>1</sup>  | _   | 70 <sup>2</sup>  | kHz  |

| Bus Free Time Between STOP and START Conditions | t <sub>BUF</sub>     |                | 9.4              | _   | _                | μs   |

| Hold Time After (Repeated)<br>START Condition   | t <sub>HD:STA</sub>  |                | 4.7              | _   | -                | μs   |

| Repeated START Condition Setup<br>Time          | t <sub>SU:STA</sub>  |                | 9.4              |     | _                | μs   |

| STOP Condition Setup Time                       | t <sub>SU:STO</sub>  |                | 9.4              | _   | _                | μs   |

| Data Hold Time                                  | t <sub>HD:DAT</sub>  |                | 489 <sup>3</sup> | _   | _                | ns   |

| Data Setup Time                                 | t <sub>SU:DAT</sub>  |                | 448 <sup>3</sup> |     | _                | ns   |

| Detect Clock Low Timeout                        | t <sub>TIMEOUT</sub> |                | 25               |     | _                | ms   |

| Clock Low Period                                | t <sub>LOW</sub>     |                | 4.7              | _   | _                | μs   |

| Clock High Period                               | t <sub>HIGH</sub>    |                | 9.4              | _   | 50 <sup>4</sup>  | μs   |

| Fast Mode (400 kHz Class)                       | I                    |                |                  |     |                  |      |

| I2C Operating Frequency                         | f <sub>l2C</sub>     |                | 0                | —   | 255 <sup>2</sup> | kHz  |

| SMBus Operating Frequency                       | f <sub>SMB</sub>     |                | 40 <sup>1</sup>  |     | 255 <sup>2</sup> | kHz  |

| Bus Free Time Between STOP and START Conditions | t <sub>BUF</sub>     |                | 2.6              | _   | -                | μs   |

| Hold Time After (Repeated)<br>START Condition   | t <sub>HD:STA</sub>  |                | 1.3              | _   | -                | μs   |

| Repeated START Condition Setup<br>Time          | t <sub>SU:STA</sub>  |                | 2.6              |     | _                | μs   |

| STOP Condition Setup Time                       | t <sub>su:sтo</sub>  |                | 2.6              |     | _                | μs   |

| Data Hold Time                                  | t <sub>HD:DAT</sub>  |                | 489 <sup>3</sup> | _   | _                | ns   |

| Data Setup Time                                 | t <sub>SU:DAT</sub>  |                | 448 <sup>3</sup> |     | _                | ns   |

| Detect Clock Low Timeout                        | t <sub>TIMEOUT</sub> |                | 25               |     | _                | ms   |

| Clock Low Period                                | t <sub>LOW</sub>     |                | 1.3              |     | _                | μs   |

| Clock High Period                               | t <sub>HIGH</sub>    |                | 2.6              |     | 50 <sup>4</sup>  | μs   |

# Table 4.16. SMBus Peripheral Timing Performance (Master Mode)

# 4.2 Thermal Conditions

#### Table 4.18. Thermal Conditions

| Parameter                             | Symbol             | Test Condition                       | Min       | Тур | Max | Unit |

|---------------------------------------|--------------------|--------------------------------------|-----------|-----|-----|------|

| Thermal Resistance* θ <sub>JA</sub>   | θ <sub>JA</sub>    | QFN-24 Packages                      | _         | 35  | _   | °C/W |

|                                       |                    | QFN-20 Packages                      | _         | 60  | _   | °C/W |

|                                       |                    | QSOP-24 Packages                     | _         | 65  | _   | °C/W |

| Note:<br>1. Thermal resistance assume | es a multi-layer l | PCB with any exposed pad soldered to | a PCB pad |     | 1   | 1    |

## 4.3 Absolute Maximum Ratings

Stresses above those listed in Table 4.19 Absolute Maximum Ratings on page 28 may cause permanent damage to the device. This is a stress rating only and functional operation of the devices at those or any other conditions above those indicated in the operation listings of this specification is not implied. Exposure to maximum rating conditions for extended periods may affect device reliability. For more information on the available quality and reliability data, see the Quality and Reliability Monitor Report at http://www.silabs.com/support/quality/pages/default.aspx.

| Parameter                                         | Symbol             | Test Condition | Min     | Мах                   | Unit |

|---------------------------------------------------|--------------------|----------------|---------|-----------------------|------|

| Ambient Temperature Under Bias                    | T <sub>BIAS</sub>  |                | -55     | 125                   | °C   |

| Storage Temperature                               | T <sub>STG</sub>   |                | -65     | 150                   | °C   |

| Voltage on V <sub>DD</sub>                        | V <sub>DD</sub>    |                | GND-0.3 | 4.0                   | V    |

| Voltage on I/O pins or RSTb                       | V <sub>IN</sub>    |                | GND-0.3 | V <sub>DD</sub> + 0.3 | V    |

| Total Current Sunk into Supply Pin                | I <sub>VDD</sub>   |                | _       | 400                   | mA   |

| Total Current Sourced out of Ground<br>Pin        | I <sub>GND</sub>   |                | 400     | —                     | mA   |

| Current Sourced or Sunk by Any I/O<br>Pin or RSTb | I <sub>IO</sub>    |                | -100    | 100                   | mA   |

| Maximum Total Current through all<br>Port Pins    | I <sub>IOTOT</sub> |                | _       | 200                   | mA   |

| Operating Junction Temperature                    | TJ                 |                | -40     | 105                   | °C   |

#### Table 4.19. Absolute Maximum Ratings

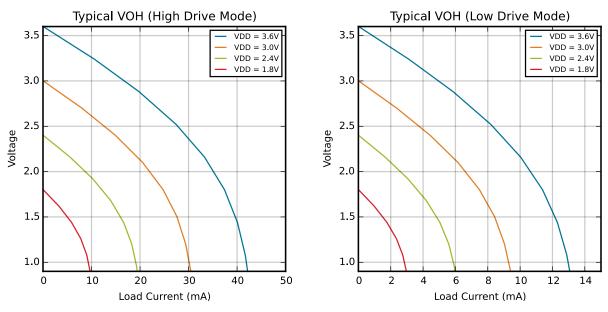

## 4.4 Typical Performance Curves

Figure 4.2. Typical Operating Supply Current (full supply voltage range)

| Pin<br>Number | Pin Name | Description       | Crossbar Capability | Additional Digital<br>Functions | Analog Functions |

|---------------|----------|-------------------|---------------------|---------------------------------|------------------|

| 22            | P0.2     | Multifunction I/O | Yes                 | P0MAT.2                         | ADC0.2           |

|               |          |                   |                     | RTCOUT                          | CS0.2            |

|               |          |                   |                     | INT0.2                          | XTAL1            |

|               |          |                   |                     | INT1.2                          |                  |

| 23            | P0.1     | Multifunction I/O | Yes                 | P0MAT.1                         | ADC0.1           |

|               |          |                   |                     | INT0.1                          | CS0.1            |

|               |          |                   |                     | INT1.1                          | AGND             |

| 24            | P0.0     | Multifunction I/O | Yes                 | P0MAT.0                         | CS0.0            |

|               |          |                   |                     | INT0.0                          | VREF             |

|               |          |                   |                     | INT1.0                          |                  |

| Center        | GND      | Ground            |                     |                                 |                  |

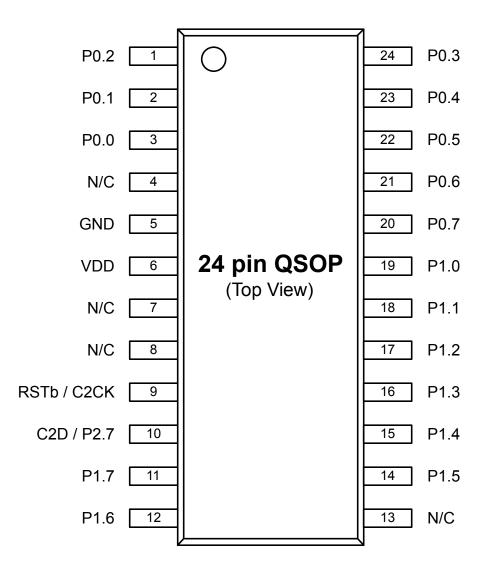

Figure 6.3. EFM8SB1x-QSOP24 Pinout

| Table 6.3. | Pin Definitions | for EFM8SB1x-QSOP24 |

|------------|-----------------|---------------------|

|------------|-----------------|---------------------|

| Pin<br>Number | Pin Name | Description       | Crossbar Capability | Additional Digital<br>Functions | Analog Functions |

|---------------|----------|-------------------|---------------------|---------------------------------|------------------|

| 1             | P0.2     | Multifunction I/O | Yes                 | P0MAT.2                         | ADC0.2           |

|               |          |                   |                     | RTCOUT                          | CS0.2            |

|               |          |                   |                     | INT0.2                          | XTAL1            |

|               |          |                   |                     | INT1.2                          |                  |

| 2             | P0.1     | Multifunction I/O | Yes                 | P0MAT.1                         | ADC0.1           |

|               |          |                   |                     | INT0.1                          | CS0.1            |

|               |          |                   |                     | INT1.1                          | AGND             |

| Pin<br>Number | Pin Name | Description       | Crossbar Capability | Additional Digital<br>Functions | Analog Functions |

|---------------|----------|-------------------|---------------------|---------------------------------|------------------|

| 23            | P0.4     | Multifunction I/O | Yes                 | P0MAT.4                         | ADC0.4           |

|               |          |                   |                     | INT0.4                          | CS0.4            |

|               |          |                   |                     | INT1.4                          |                  |

| 24            | P0.3     | Multifunction I/O | Yes                 | P0MAT.3                         | ADC0.3           |

|               |          |                   |                     | EXTCLK                          | CS0.3            |

|               |          |                   |                     | WAKEOUT                         | XTAL2            |

|               |          |                   |                     | INT0.3                          |                  |

|               |          |                   |                     | INT1.3                          |                  |

| Pin<br>Number | Pin Name | Description         | Crossbar Capability | Additional Digital<br>Functions | Analog Functions |

|---------------|----------|---------------------|---------------------|---------------------------------|------------------|

| A4            | P0.0     | Multifunction I/O   | Yes                 | P0MAT.0                         | CS0.0            |

|               |          |                     |                     | INT0.0                          | VREF             |

|               |          |                     |                     | INT1.0                          |                  |

| B1            | P1.0     | Multifunction I/O   | Yes                 | P1MAT.0                         | CMP0P.4          |

|               |          |                     |                     |                                 | CS0.8            |

| B2            | P0.3     | Multifunction I/O   | Yes                 | P0MAT.3                         | ADC0.3           |

|               |          |                     |                     | EXTCLK                          | CS0.3            |

|               |          |                     |                     | WAKEOUT                         | XTAL2            |

|               |          |                     |                     | INT0.3                          |                  |

|               |          |                     |                     | INT1.3                          |                  |

| B3            | P0.2     | Multifunction I/O   | Yes                 | P0MAT.2                         | ADC0.2           |

|               |          |                     |                     | RTCOUT                          | CS0.2            |

|               |          |                     |                     | INT0.2                          | XTAL1            |

|               |          |                     |                     | INT1.2                          |                  |

| B4            | GND      | Ground              |                     |                                 |                  |

| C1            | P1.3     | Multifunction I/O   | Yes                 | P1MAT.3                         | ADC0.11          |

|               |          |                     |                     |                                 | CS0.11           |

| C2            | P0.6     | Multifunction I/O   | Yes                 | P0MAT.6                         | ADC0.6           |

|               |          |                     |                     | CNVSTR                          | CS0.6            |

|               |          |                     |                     | INT0.6                          |                  |

|               |          |                     |                     | INT1.6                          |                  |

| C3            | P0.1     | Multifunction I/O   | Yes                 | P0MAT.1                         | ADC0.1           |

|               |          |                     |                     | INT0.1                          | CS0.1            |

|               |          |                     |                     | INT1.1                          | AGND             |

| C4            | VDD      | Supply Power Input  |                     |                                 |                  |

| D1            | P1.1     | Multifunction I/O   | Yes                 | P1MAT.1                         | CMP0N.4          |

|               |          |                     |                     |                                 | CS0.9            |

| D2            | P1.4     | Multifunction I/O   | Yes                 | P1MAT.4                         | ADC0.12          |

|               |          |                     |                     |                                 | CS0.12           |

| D3            | RSTb /   | Active-low Reset /  |                     |                                 |                  |

|               | C2CK     | C2 Debug Clock      |                     |                                 |                  |

| D4            | P2.7 /   | Multifunction I/O / |                     |                                 |                  |

|               | C2D      | C2 Debug Data       |                     |                                 |                  |

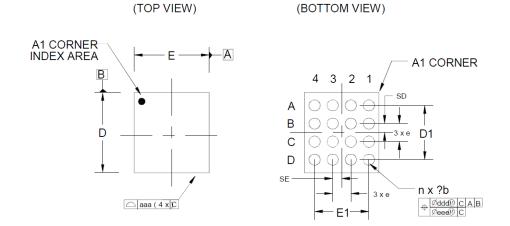

# 7. CSP16 Package Specifications

# 7.1 CSP16 Package Dimensions

**Note:** CSP devices can be handled and soldered using industry standard surface mount assembly techniques. However, because CSP devices are essentially a piece of silicon and are not encapsulated in plastic, they are susceptible to mechanical damage and may be sensitive to light. When CSP packages must be used in an environment exposed to light, it may be necessary to cover the top and sides with an opaque material.

Figure 7.1. CSP16 Package Drawing

Table 7.1. CSP16 Package Dimensions

| Dimension | Min       | Тур      | Мах    |  |

|-----------|-----------|----------|--------|--|

| A         | 0.491     | 0.55     | 0.609  |  |

| A1        | 0.17      | —        | 0.23   |  |

| A2        | 0.036     | 0.040    | 0.044  |  |

| b         | 0.23      | —        | 0.29   |  |

| S         | 0.3075    | 0.31     | 0.3125 |  |

| D         | 1.781 BSC |          |        |  |

| E         | 1.659 BSC |          |        |  |

| е         | 0.40 BSC  |          |        |  |

| D1        |           | 1.20 BSC |        |  |

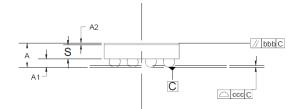

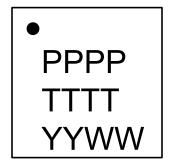

## 7.3 CSP16 Package Marking

# Figure 7.3. CSP16 Package Marking

The package marking consists of:

- PPPP The part number designation.

- TTTT A trace or manufacturing code.

- YY The last 2 digits of the assembly year.

- WW The 2-digit workweek when the device was assembled.

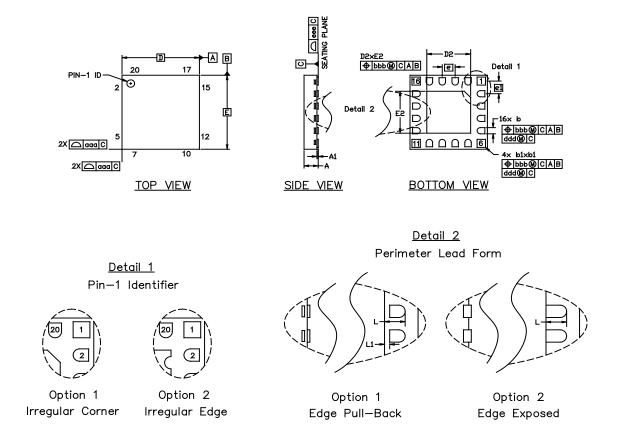

# 8. QFN20 Package Specifications

# 8.1 QFN20 Package Dimensions

# Table 8.1. QFN20 Package Dimensions

| Dimension | Min       | Тур   | Мах   |

|-----------|-----------|-------|-------|

| A         | 0.50      | 0.55  | 0.60  |

| A1        | 0.00      | —     | 0.05  |

| b         | 0.20      | 0.25  | 0.30  |

| b1        | 0.275     | 0.325 | 0.375 |

| D         | 3.00 BSC  |       |       |

| D2        | 1.6       | 1.70  | 1.80  |

| e         | 0.50 BSC  |       |       |

| e1        | 0.513 BSC |       |       |

| E         | 3.00 BSC  |       |       |

| E2        | 1.60      | 1.70  | 1.80  |

| L         | 0.35      | 0.40  | 0.45  |

| Dimension | Min  | Тур  | Мах  |

|-----------|------|------|------|

| L1        | 0.00 | —    | 0.10 |

| ааа       | _    | 0.10 | —    |

| bbb       | _    | 0.10 | —    |

| ddd       | _    | 0.05 | —    |

| eee       | _    | —    | 0.08 |

Note:

1. All dimensions shown are in millimeters (mm) unless otherwise noted.

2. Dimensioning and Tolerancing per ANSI Y14.5M-1994.

3. This drawing is based upon JEDEC Solid State Product Outline MO-248 but includes custom features which are toleranced per supplier designation.

4. Recommended card reflow profile is per the JEDEC/IPC J-STD-020 specification for Small Body Components.

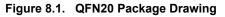

# 9. QFN24 Package Specifications

# 9.1 QFN24 Package Dimensions

Figure 9.1. QFN24 Package Drawing

| Table 9.1. | QFN24 | Package  | Dimensions |

|------------|-------|----------|------------|

|            |       | . aonago |            |

| Dimension | Min      | Тур      | Мах  |

|-----------|----------|----------|------|

| A         | 0.70     | 0.75     | 0.80 |

| A1        | 0.00     | _        | 0.05 |

| b         | 0.18     | 0.25     | 0.30 |

| D         |          | 4.00 BSC |      |

| D2        | 2.35     | 2.45     | 2.55 |

| е         | 0.50 BSC |          |      |

| E         |          | 4.00 BSC |      |

| E2        | 2.35     | 2.45     | 2.55 |

| L         | 0.30     | 0.40     | 0.50 |

| ааа       | —        | _        | 0.10 |

| bbb       | —        | —        | 0.10 |

| ссс       | _        | —        | 0.08 |

| ddd       | _        | _        | 0.10 |

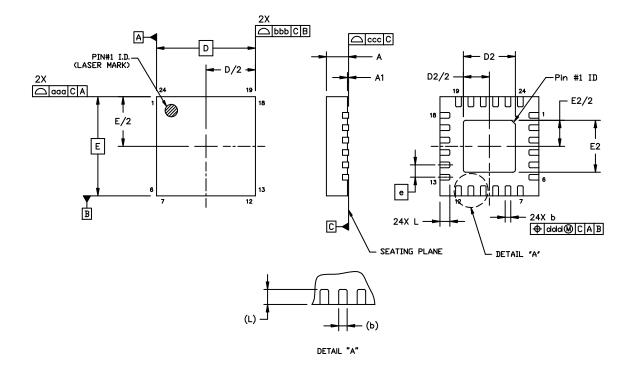

## 9.2 QFN24 PCB Land Pattern

Figure 9.2. QFN24 PCB Land Pattern Drawing

| Table 9.2. QFN24 PCB Land Pattern Dimension |

|---------------------------------------------|

|---------------------------------------------|

| Dimension | Min  | Мах  |

|-----------|------|------|

| C1        | 3.90 | 4.00 |

| C2        | 3.90 | 4.00 |

| E         | 0.50 | BSC  |

| X1        | 0.20 | 0.30 |

| X2        | 2.70 | 2.80 |

| Y1        | 0.65 | 0.75 |

| Y2        | 2.70 | 2.80 |

|     | 6.1   | EFM8SB1x-QFN20 Pin Definitions |    |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   | .33 |

|-----|-------|--------------------------------|----|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|-----|

|     | 6.2   | EFM8SB1x-QFN24 Pin Definitions |    |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   | .36 |

|     | 6.3   | EFM8SB1x-QSOP24 Pin Definition | าร |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   | .39 |

|     | 6.4   | EFM8SB1x-CSP16 Pin Definitions |    |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   | .42 |

| 7.  | CSF   | 16 Package Specifications.     |    |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   | 44  |

|     |       | CSP16 Package Dimensions       |    |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |     |

|     | 7.2   | CSP16 PCB Land Pattern         |    |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   | .46 |

|     | 7.3   | CSP16 Package Marking          |    |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   | .47 |

| 8.  | QFN   | I20 Package Specifications.    |    |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   | 48  |

| -   | 8.1   | QFN20 Package Dimensions       |    |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |     |

|     | 8.2   | QFN20 PCB Land Pattern         |    |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |     |

|     |       | QFN20 Package Marking          |    |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |     |

| 9   |       | I24 Package Specifications.    |    |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |     |

| ν.  |       | QFN24 Package Dimensions.      |    |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |     |

|     |       | QFN24 PCB Land Pattern         |    |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |     |

|     |       | QFN24 Package Marking          |    |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |     |

| 40  |       |                                |    |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |     |

| 10. |       | OP24 Package Specifications    |    |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |     |

|     | 10.1  |                                |    |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |     |

|     | 10.2  |                                |    |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |     |

|     | 10.3  | 3 QSOP24 Package Marking       | •  |   | • | • | • | • | • | • |   | • | • | • | • | • | • | • | • | • | • | • | .59 |

| 11. | Re    | vision History                 |    | • |   |   |   |   |   |   | • |   | • |   |   | • | • | • | • |   |   |   | 60  |

|     | 11.1  | 1 Revision 1.3                 |    |   |   |   |   |   | • |   |   |   |   |   |   |   |   |   |   |   |   |   | .60 |

|     | 11.2  | 2 Revision 1.2                 |    |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   | .60 |

|     | 11.3  | 3 Revision 1.1                 |    |   |   |   |   |   | • |   |   |   |   |   |   |   |   |   |   |   |   |   | .60 |

| Та  | ble c | of Contents                    |    |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   | 61  |