Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Product Status             | Active                                                                      |

|----------------------------|-----------------------------------------------------------------------------|

| Core Processor             | F <sup>2</sup> MC-16F                                                       |

| Core Size                  | 16-Bit                                                                      |

| Speed                      | 16MHz                                                                       |

| Connectivity               | EBI/EMI, UART/USART                                                         |

| Peripherals                | POR, PWM, WDT                                                               |

| Number of I/O              | 102                                                                         |

| Program Memory Size        | 64KB (64K x 8)                                                              |

| Program Memory Type        | Mask ROM                                                                    |

| EEPROM Size                | -                                                                           |

| RAM Size                   | 3K x 8                                                                      |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 5.5V                                                                   |

| Data Converters            | A/D 16x10b                                                                  |

| Oscillator Type            | External                                                                    |

| Operating Temperature      | -40°C ~ 105°C (TA)                                                          |

| Mounting Type              | Surface Mount                                                               |

| Package / Case             | 120-BQFP                                                                    |

| Supplier Device Package    | 120-QFP (28x28)                                                             |

| Purchase URL               | https://www.e-xfl.com/product-detail/infineon-technologies/mb90223pf-gt-372 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

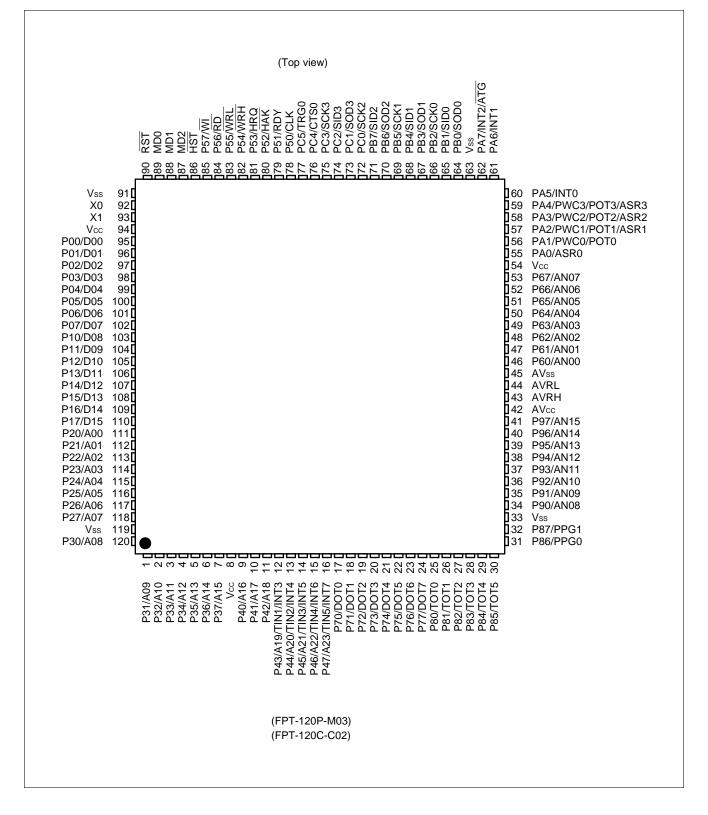

#### PIN ASSIGNMENT

| Pin no. | Pin name | Circuit | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|---------|----------|---------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| QFP*    |          | type    |                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 62      | INT2     | В       | DTP/External interrupt request input pin<br>When DTP/external interrupts are enabled, these inputs may be used<br>suddenly at any time; therefore, it is necessary to stop output by other<br>functions on these pins, except when using them for output<br>deliberately.<br>When these pins are open in input mode, through current may leak in<br>stop mode/reset mode, be sure to fix these pins to Vcc/Vss level to<br>use these pins in input mode. |

|         | ATG      |         | 10-bit A/D converter external trigger input pin When these pins are open in input mode, through current may leak in stop mode/reset mode, be sure to fix these pins to $V_{CC}/V_{SS}$ level to use these pins in input mode.                                                                                                                                                                                                                            |

| 64      | PB0      | С       | General-purpose I/O port<br>This function is valid when the UART0 (ch.0) serial data output<br>specification is "disabled".                                                                                                                                                                                                                                                                                                                              |

|         | SOD0     |         | UART0 (ch.0) serial data output<br>This function is valid when the UART0 (ch.0) serial data output<br>specification is "enabled".                                                                                                                                                                                                                                                                                                                        |

| 65      | PB1      | С       | General-purpose I/O port<br>This function is always valid.                                                                                                                                                                                                                                                                                                                                                                                               |

|         | SIDO     |         | UART0 (ch.0) serial data input pin<br>During UART0 (ch.0) input operations, this input may be used<br>suddenly at any time; therefore, it is necessary to stop output by other<br>functions on this pin, except when using it for output deliberately.                                                                                                                                                                                                   |

| 66      | PB2      | С       | General-purpose output port<br>This function is valid when the UART0 (ch.0) clock output<br>specification is "disabled".                                                                                                                                                                                                                                                                                                                                 |

|         | SCK0     |         | UART0 (ch.0) clock output pin<br>The clock output function is valid when the UART0 (ch.0) clock output<br>specification is "enabled".<br>UART0 (ch.0) external clock input pin. This function is valid when the<br>port is in input mode and the UART0 (ch.0) specification is external<br>clock mode.                                                                                                                                                   |

| 67      | PB3      | С       | General-purpose I/O port<br>This function is valid when the UART0 (ch.1) serial data output<br>specification is "disabled".                                                                                                                                                                                                                                                                                                                              |

|         | SOD1     |         | UART0 (ch.1) serial data output pin<br>This function is valid when the UART0 (ch.1) serial data output<br>specification is "enabled".                                                                                                                                                                                                                                                                                                                    |

| 68      | PB4      | С       | General-purpose I/O port<br>This function is always valid.                                                                                                                                                                                                                                                                                                                                                                                               |

|         | SID1     |         | UART0 (ch.1) serial data input pin<br>During UART0 (ch.1) input operations, this input may be used<br>suddenly at any time; therefore, it is necessary to stop output by other<br>functions on this pin, except when using it for output deliberately.                                                                                                                                                                                                   |

\* : FPT-120P-M03, FPT-120C-C02

(Continued)

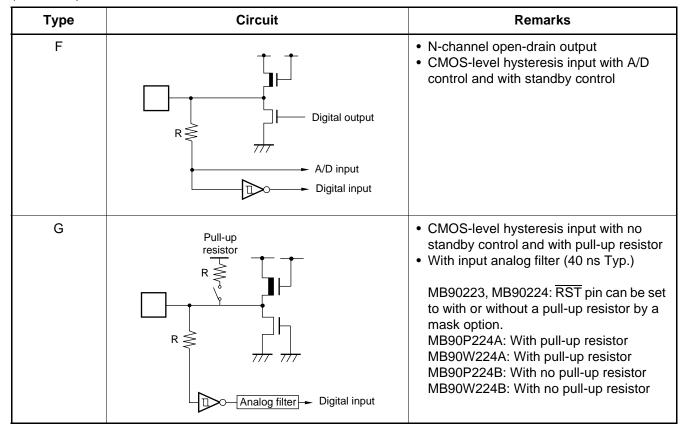

□ - P-type transistor

- N-type transistor

Note: The pull-up and pull-down resistors are always connected, regardless of the state.

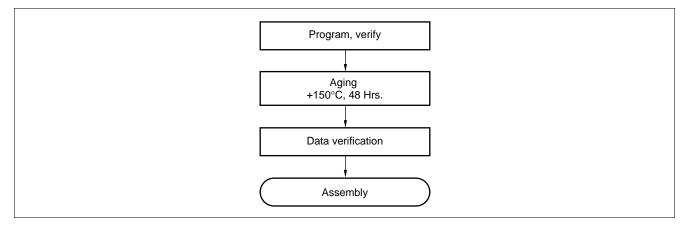

## 5. Recommended Screening Conditions

High temperature aging is recommended as the pre-assembly screening procedure.

### 6. Programming Yeild

MB90P224A/P224B cannot be write-tested for all bits due to their nature. Therefore the write yield cannot always be guaranteed to be 100%.

### 7. Pin Assignments in EPROM Mode

#### (1) Pins Compatible with MBM27C1000

| MBM2    | BM27C1000 MB90P224A/P224B/<br>MB90W224A/W224B |                |           | MBM     | 27C1000  | MB90P224A/P224B/<br>MB90W224A/W224B |          |  |

|---------|-----------------------------------------------|----------------|-----------|---------|----------|-------------------------------------|----------|--|

| Pin no. | Pin name                                      | Pin no.        | Pin name  | Pin no. | Pin name | Pin no.                             | Pin name |  |

| 1       | Vpp                                           | 87             | MD2 (VPP) | 32      | Vcc      | 8, 54, 94                           | Vcc      |  |

| 2       | OE                                            | 83             | P55       | 31      | PGM      | 84                                  | P56      |  |

| 3       | A15                                           | 7              | P37       | 30      | N.C.     |                                     | _        |  |

| 4       | A12                                           | 4              | P34       | 29      | A14      | 6                                   | P36      |  |

| 5       | A07                                           | 118            | P27       | 28      | A13      | 5                                   | P35      |  |

| 6       | A06                                           | 117            | P26       | 27      | A08      | 120                                 | P30      |  |

| 7       | A05                                           | 116            | P25       | 26      | A09      | 1                                   | P31      |  |

| 8       | A04                                           | 115            | P24       | 25      | A11      | 3                                   | P33      |  |

| 9       | A03                                           | 114            | P23       | 24      | A16      | 9                                   | P40      |  |

| 10      | A02                                           | 113            | P22       | 23      | A10      | 2                                   | P32      |  |

| 11      | A01                                           | 112            | P21       | 22      | CE       | 82                                  | P54      |  |

| 12      | A00                                           | 111            | P20       | 21      | D07      | 102                                 | P07      |  |

| 13      | D00                                           | 95             | P00       | 20      | D06      | 101                                 | P06      |  |

| 14      | D01                                           | 96             | P01       | 19      | D05      | 100                                 | P05      |  |

| 15      | D02                                           | 97             | P02       | 18      | D04      | 99                                  | P04      |  |

| 16      | GND                                           | 33, 63, 91,119 | Vss       | 17      | D03      | 98                                  | P03      |  |

| Address           | Register                             | Register<br>name | Access    | Resouce<br>name         | Initial value |

|-------------------|--------------------------------------|------------------|-----------|-------------------------|---------------|

| 000062н           | OCU0 control register 01             | CCR01            | R/W       | OCU (Output             | 11110000      |

| 000063н           |                                      | CCRUT            |           | Compare Unit)           | 0000          |

| 000064н           |                                      |                  |           |                         |               |

| 000065н           |                                      | (Reserved        | 1 aroa)*1 |                         |               |

| 000066н           |                                      |                  | alea)     |                         |               |

| 000067н           |                                      |                  |           |                         |               |

| 000068н           | OCU0 control register 10             | CCR10 R/W        |           | 0000                    |               |

| 000069н           |                                      |                  | L/ AA     | OCU (Output             | 00000000      |

| 00006Ан           | OCU0 control register 11             | CCR11            | R/W       | Compare Unit)           | 0000          |

| 00006Вн           |                                      | CONTI            | D/ VV     |                         | 00000000      |

| 00006Сн           |                                      |                  | 1         |                         |               |

| 00006Dн           |                                      | (Reserved        | area)*1   |                         |               |

| 00006Ен           |                                      | (Reserved        | i alea) ' |                         |               |

| 00006Fн           | -                                    |                  |           |                         |               |

| 000070н           | Free run timer centrel register      | TCCR R/W         |           |                         | 11000000      |

| 000071н           | - Free-run timer control register    |                  | r///      |                         | 111111        |

| 000072н           | Free-run timer lower-order data      | TCRL             |           | 24-bit timer<br>counter | 00000000      |

| 000073н           | register                             |                  | R         |                         | 00000000      |

| 000074н           | Free-run timer upper-order data      | тори             | ĸ         |                         | 00000000      |

| 000075н           | register                             | TCRH             |           |                         | 00000000      |

| 000076н           |                                      | 1                |           | 1                       | 1             |

| 000077н           |                                      | (Decention       | aree)*1   |                         |               |

| 000078н           |                                      | (Reserved        | i alea) ' |                         |               |

| 000079н           |                                      |                  |           |                         |               |

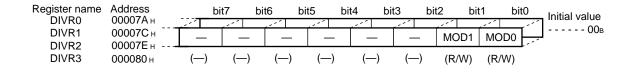

| 00007Ан           | PWC divider ratio control register 0 | DIVR0            | R/W       | PWC timer 0             | 00            |

| 00007Вн           | Reserved area <sup>*1</sup>          |                  | +         |                         |               |

| 00007Сн           | PWC divider ratio control register 1 | DIVR1            | R/W       | PWC timer 1             | 00            |

| 00007DH           | Reserved area*1                      | J                | 1         | 1                       |               |

| 00007Ен           | PWC divider ratio control register 2 | DIVR2            | R/W       | PWC timer 2             | 00            |

| 00007Fн           | Reserved area <sup>*1</sup>          | 4                | 1         | 1                       |               |

| 000080н           | PWC divider ratio control register 3 | DIVR3            | R/W       | PWC timer 3             | 00            |

| 000081н<br>to 8Dн |                                      | (Reserved        | area)*1   | 1                       | 1             |

(Continued)

| Address           | Register                                               | Register<br>name | Access    | Resouce<br>name                         | Initial value |

|-------------------|--------------------------------------------------------|------------------|-----------|-----------------------------------------|---------------|

| 00008Eн           | WI control register                                    | WICR             | R/W       | Write-inhibit<br>RAM                    | X             |

| 00008Fн           |                                                        |                  |           |                                         |               |

| 000090н<br>to 9Eн |                                                        | (Reserved        | l area)*1 |                                         |               |

| 00009Fн           | Delay interrupt source generation<br>/release register | DIRR             | R/W       | Delay interrupt<br>generation<br>module | 0             |

| 0000А0н           | Standby control register                               | STBYC            | R/W       | Low power consumption                   | 0001***       |

| 0000АЗн           | Address mid-order control register                     | MACR             | W         | External pin                            | #######       |

| 0000А4н           | Address higher-order control register                  | HACR             | W         | External pin                            | ########      |

| 0000А5н           | External pin control register                          | EPCR             | W         | External pin                            | ##0-0#00      |

| 0000А8н           | Watchdog timer control register                        | WDTC             | R/W       | Watchdog<br>timer                       | xxxxxxxx      |

| 0000А9н           | Timebase timer control register                        | TBTC             | R/W       | Timebase<br>timer                       | 00000         |

| 0000В0н           | Interrupt control register 00                          | ICR00            | R/W       |                                         | 00000111      |

| 0000B1н           | Interrupt control register 01                          | ICR01            | R/W       | _                                       | 00000111      |

| 0000B2н           | Interrupt control register 02                          | ICR02            | R/W       |                                         | 00000111      |

| 0000ВЗн           | Interrupt control register 03                          | ICR03            | R/W       | _                                       | 00000111      |

| 0000B4н           | Interrupt control register 04                          | ICR04            | R/W       | _                                       | 00000111      |

| 0000В5н           | Interrupt control register 05                          | ICR05            | R/W       |                                         | 00000111      |

| 0000В6н           | Interrupt control register 06                          | ICR06            | R/W       |                                         | 00000111      |

| 0000 <b>B7</b> н  | Interrupt control register 07                          | ICR07            | R/W       | Interrupt                               | 00000111      |

| 0000 <b>В</b> 8н  | Interrupt control register 08                          | ICR08            | R/W       | controller                              | 00000111      |

| 0000В9н           | Interrupt control register 09                          | ICR09            | R/W       | _                                       | 00000111      |

| 0000ВАн           | Interrupt control register 10                          | ICR10            | R/W       |                                         | 00000111      |

| 0000BBн           | Interrupt control register 11                          | ICR11            | R/W       |                                         | 00000111      |

| 0000BCH           | Interrupt control register 12                          | ICR12            | R/W       | _                                       | 00000111      |

| 0000BDH           | Interrupt control register 13                          | ICR13            | R/W       |                                         | 00000111      |

| 0000BEн           | Interrupt control register 14                          | ICR14            | R/W       |                                         | 00000111      |

| 0000BFн           | Interrupt control register 15                          | ICR15            | R/W       |                                         | 00000111      |

| 0000C0н<br>to FFн |                                                        | (External        | area)*2   |                                         |               |

| 001F00н           | DWC data buffer register 0                             |                  |           | DWC time = 0                            | 00000000      |

| 001F01н           | PWC data buffer register 0                             | PWCR0            | R/W       | PWC timer 0                             | 00000000      |

(Continued)

(Continued)

| Address             | Register                           | Register<br>name | Access   | Resouce<br>name   | Initial value |

|---------------------|------------------------------------|------------------|----------|-------------------|---------------|

| 001F48н             | DDC such actting register 0        | DCCDA            | W        |                   | XXXXXXXX      |

| 001F49н             | PPG cycle setting register 0       | PCSR0            | vv       | 16-bit PPG        | XXXXXXXX      |

| 001F4Aн             |                                    | PDUT0            | W        | timer 0           | XXXXXXXX      |

| 001F4Bн             | PPG duty setting register 0        | 1 DOTO           |          |                   | XXXXXXXX      |

| 001F4Cн             | DDC such softing register 1        | D00D4            | W        |                   | XXXXXXXX      |

| 001F4Dн             | PPG cycle setting register 1       | PCSR1            |          | 16-bit PPG        | XXXXXXXX      |

| 001F4Eн             | PPG duty setting register 1        | PDUT1            | 10/      | timer 1           | XXXXXXXX      |

| 001F4Fн             | - FFG duty setting register 1      | PDUTT            | W        |                   | XXXXXXXX      |

| 001F50н             |                                    |                  |          | XXXXXXXX          |               |

| 001F51н             | - ICU lower-order data register 0  | ICRL0            | R        | Input capture 0   | XXXXXXXX      |

| 001F52н             | ICI L higher order data register 0 | ICRH0            | R        |                   | XXXXXXXX      |

| 001F53н             | - ICU higher-order data register 0 | ICKHU            | ĸ        |                   | 00000000      |

| 001F54н             | ICU lower-order data register 1    | ICRL1            | R        |                   | XXXXXXXX      |

| 001F55н             |                                    |                  |          | Input capture 1   | XXXXXXXX      |

| 001F56н             | ICU higher-order data register 1   | ICRH1            | R        |                   | XXXXXXXX      |

| <b>001F57</b> н     |                                    | ICKIII           | N        |                   | 00000000      |

| 001F58н             | ICU lower-order data register 2    | ICRL2            | R        |                   | XXXXXXXX      |

| 001F59н             |                                    | IGREZ            | К        | Input capture 2   | XXXXXXXX      |

| 001F5Ан             | ICU higher-order data register 2   | ICRH2            | R        | - Input capture 2 | XXXXXXXX      |

| 001F5Bн             |                                    | ICKHZ            | N        |                   | 00000000      |

| 001F5Cн             | ICI I lower order data register 2  | ICRL3            | R        |                   | XXXXXXXX      |

| 001F5Dн             | - ICU lower-order data register 3  | IUKLJ            | ĸ        | - Input capture 3 | XXXXXXXX      |

| 001F5Eн             | ICI L higher order data register 2 | ICRH3            | R        |                   | XXXXXXXX      |

| 001F5Fн             | - ICU higher-order data register 3 |                  | 00000000 |                   |               |

| 001F60н<br>to 1FFFн |                                    | (Reserved        | area)*1  | •                 | •             |

Initial value

0: The initial value of this bit is "0".

- 1: The initial value of this bit is "1".

- X: The initial value of this bit is undefined.

- -: This bit is not used. The initial value is undefined.

- \*: The initial value of this bit varies with the reset source.

- #: The initial value of this bit varies with the operation mode.

- \*1: Access prohibited

- \*2: Only this area is open to external access in the area below address 0000FF<sub>H</sub> (inclusive). All addresses which are not described in the table are reserved areas, and accesses to these areas are handled in the same manner as for internal areas. The access signal for the external bus is not generated.

- \*3: When an external bus is enable mode, never access to resisters which are not used as general ports in areas address 000000H to 000005H or 000010H to 000015H.

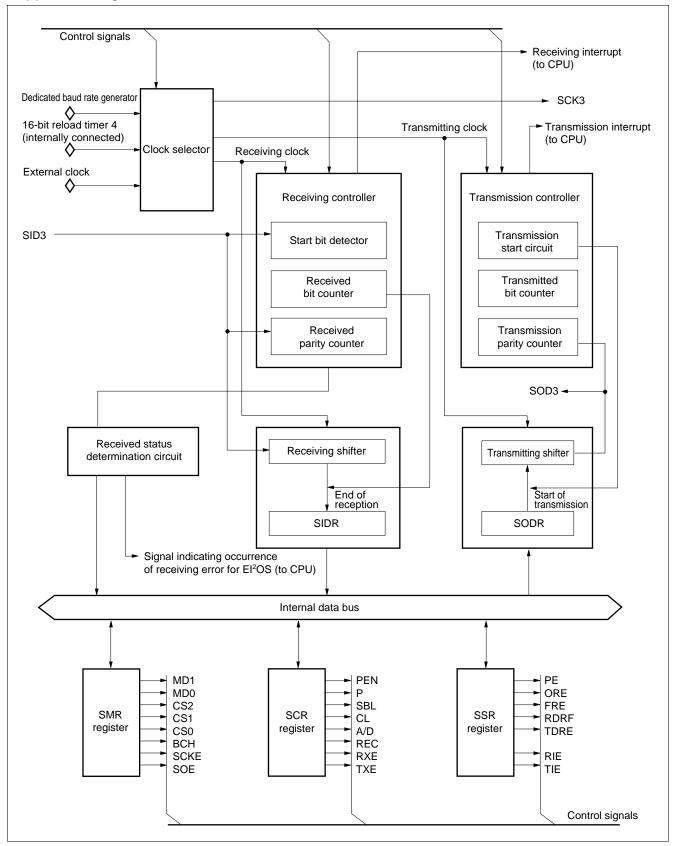

#### (2) Block Diagram

### 5. 10-bit A/D Converter

The 10-bit A/D converter converts analog input voltage into a digital value. The features of this module are described below:

- Conversion time: 6.125 μs/channel (min.) (with machine clock running at 16 MHz)

- · Uses RC-type sequential comparison and conversion method with built-in sample and hold circuit

- 10-bit resolution

| Analog input can be selected b | by software from among 16 channels                                            |

|--------------------------------|-------------------------------------------------------------------------------|

| Single-conversion mode:        | Selects and converts one channel.                                             |

| Scan conversion mode:          | Converts several consecutive channels (up to 16 can be programmed).           |

| One-shot mode:                 | Converts the specified channel once and terminates.                           |

| Continuous conversion mode:    | Repeatedly converts the specified channel.                                    |

| Stop conversion mode:          | Pauses after converting one channel and waits until the next startup (permits |

|                                | synchronization of start of conversion).                                      |

- When A/D conversion is completed, an "A/D conversion complete" interrupt request can be issued to the CPU. Because the generation of this interrupt can be used to start up the EI<sup>2</sup>OS and transfer the A/D conversion results to memory, this function is suitable for continuous processing.

- Startup triggers can be selected from among software, an external trigger (falling edge), and a timer (rising edge).

#### (1) Register Configuration

#### • A/D Channel Setting Register (ADCH)

This register specfies the A/D converter conversion channel.

| Register name | Address | bit7  | bit6  | bit5  | bit4  | bit3  | bit2  | bit1  | bit0  | Initial value |

|---------------|---------|-------|-------|-------|-------|-------|-------|-------|-------|---------------|

| ADCH          | 000032н | ANS3  | ANS2  | ANS1  | ANS0  | ANE3  | ANE2  | ANE1  | ANE0  | 00000000 в    |

|               |         | (R/W) |               |

#### • A/D Mode Register (ADMD)

This register specfies the A/D converter operation mode and the startup source.

| Register name Add | dress   | bit15 | bit14 | bit13 | bit12    | bit11 | bit10 | bit9  | bit8  | Initial value |

|-------------------|---------|-------|-------|-------|----------|-------|-------|-------|-------|---------------|

| ADMD 000          | 0033н [ |       | —     | _     | Reserved | MOD1  | MOD0  | STS1  | STS0  | Х0000 в       |

|                   | -       | (—)   | (—)   | (—)   | (W)      | (R/W) | (R/W) | (R/W) | (R/W) |               |

Note: Program "0" to bit 12 when write. Read value is indeterminated.

#### • A/D Control Status Register (ADCS)

This register is the A/D converter control and status register.

| Register name |         | bit7  | bit6  | bit5  | bit4  | bit3 | bit2 | bit1 | bit0     | Initial value |

|---------------|---------|-------|-------|-------|-------|------|------|------|----------|---------------|

| ADCS          | 000034н | BUSY  | INT   | INTE  | PAUS  |      | _    | STRT | Reserved | 0000 00 в     |

|               |         | (R/W) | (R/W) | (R/W) | (R/W) | (—)  | (—)  | (W)  | (R/W)    |               |

#### A/D Data Register (ADCD)

This register stores the A/D converter conversion data.

| Register name Address | bit7 | bit6 | bit5 | bit4 | bit3 | bit2 | bit1 | bit0 | Initial value |

|-----------------------|------|------|------|------|------|------|------|------|---------------|

| ADCD 000036H          | D7   | D6   | D5   | D4   | D3   | D2   | D1   | D0   | XXXXXXXX в    |

|                       | (R)  | -             |

#### • PWC Division Ratio Control Register 0 to 3 (DIVR0 to DIVR3)

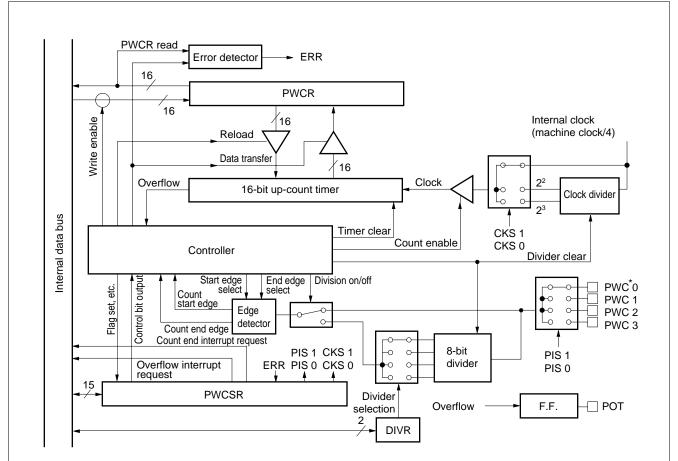

#### (2) Block Diagram

\*: In the MB90220 series, only the module input PWC 0 of each channel is connected to the respective external pins.

| Channel   | POT pin                |

|-----------|------------------------|

| PWC ch. 0 | PA 1/PWC 0/POT 0       |

| PWC ch. 1 | PA 2/PWC 1/POT 1/ASR 1 |

| PWC ch. 2 | PA 3/PWC 2/POT 2/ASR 2 |

| PWC ch. 3 | PA 4/PWC 3POT 3/ASR 3  |

### 8. 24-bit Timer Counter

The 24-bit timer counter consists of a 24-bit up-counter, an 8-bit output buffer register, and a control register. The count value output by this timer counter is used to generate the base time used for input capture and output compare.

The interrupt functions provided are timer overflow interrupts and timer intermediate bit interrupts. The intermediate bit interrupt permits four time settings.

The 24-bit timer counter value is cleared to all zeroes by a reset.

#### (1) Register Configuration

#### • Free-run Timer Control Register (TCCR)

| Register name | Address | bit15 | bit14 | bit13    | bit12    | bit11    | bit10    | bit9     | bit8  | Initial value |

|---------------|---------|-------|-------|----------|----------|----------|----------|----------|-------|---------------|

| TCCR          | 000071н | —     | _     | Reserved | Reserved | Reserved | Reserved | Reserved | PR0   | 111111в       |

|               | •       | (—)   | (—)   | (W)      | (W)      | (R/W)    | (R/W)    | (R/W)    | (R/W) |               |

| Register name | -       | bit7  | bit6  | bit5     | bit4     | bit3     | bit2     | bit1     | bit0  | Initial value |

| TCCR          | 000070н | CLR2  | CLR   | IVF      | IVFE     | TIM      | TIME     | TIS1     | TIS0  | 1100000в      |

|               |         | (W)   | (W)   | (R/W)    | (R/W)    | (R/W)    | (R/W)    | (R/W)    | (R/W) |               |

#### • Free-run Timer Low-order Data Register (TCRL)

| Register name | Address  | bit15 |      | bit0 |                      |

|---------------|----------|-------|------|------|----------------------|

| TCRL          | 000072 н |       | TCRL |      | Initial value Access |

|               | 000073н  |       | ICRL |      | 0000000 в К          |

#### • Free-run Timer High-order Data Register (TCRH)

| Register name | Address            | bit15 | bit8 bit7 | bit0 |                                      |

|---------------|--------------------|-------|-----------|------|--------------------------------------|

| TCRH          | 000074н<br>000075н | —     | TCRH      |      | Initial value Access<br>00000000 B R |

#### (Continued)

| Parameter            | Symbol | Pin name | Condition     |      | Value |                 | Unit | Remarks      |

|----------------------|--------|----------|---------------|------|-------|-----------------|------|--------------|

| Farameter            | Symbol | Fin name | Condition     | Min. | Тур.  | Max.            | Unit | Remarks      |

| Analog power         | la     | AVcc     | fc = 16 MHz*9 |      | 3     | 7               | mA   |              |

| supply voltage       | Іан    | AVCC     |               | —    | —     | 5 <sup>*6</sup> | μA   | At stop mode |

| Input<br>capacitance | CIN    | *7       | _             |      | 10    | _               | pF   |              |

### \*1: <u>Hysteresis</u> input pins

RST, HST, P00 to P07, P10 to P17, P20 to P27, P30 to P37, P40 to P47, P50 to P57, P60 to P67, P80 to P87, P90 to P97, PA0 to PA7, PB0 to PB7, PC0 to PC5

#### \*2: Ouput pins P00 to P07, P10 to P17, P20 to P27, P30 to P37, P40 to P47, P50 to P57, P70 to P77, P80 to P87, PA0 to PA7, PB0 to PB7, PC0 to PC5

\*3: Output pins P00 to P07, P10 to P17, P20 to P27, P30 to P37, P40 to P47, P50 to P57, P60 to P67, P70 to P77, P80 to P87, P90 to P97, PA0 to PA7, PB0 to PB7, PC0 to PC5

### \*4: A list of availabilities of pull-up/pull-down resistors

| Pin name | MB90223/224                                              | MB90P224A/W224A             | MB90P224B/W224B |

|----------|----------------------------------------------------------|-----------------------------|-----------------|

| RST      | Availability of pull-up resistors is optionally defined. | Pull-up resistors available | Unavailable     |

| MD1      | Pull-up resistors available                              | Unavailable                 | Unavailable     |

| MD0, MD2 | Pull-up resistors available                              | Unavailable                 | Unavailable     |

\*5: Vcc = +5.0 V, Vss = 0.0 V, TA = +25°C, Fc = 16 MHz

\*6: The current value applies to the CPU stop mode with A/D converter inactive ( $V_{CC} = AV_{CC} = AVRH = +5.5 V$ ).

\*7: Other than Vcc, Vss, AVcc and AVss

\*8: Measurement condition of power supply current; external clock pin and output pin are open. Measurement condition of Vcc; see the table above mentioned.

\*9: Fc = 12 MHz for MB90223

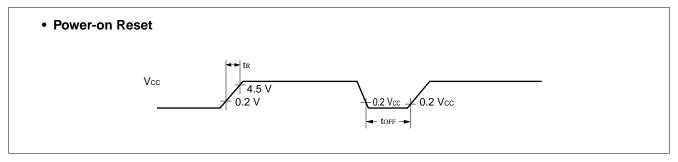

#### (4) Power on Supply Specifications (Power-on Reset)

|                           | $ MB90223/224/P224B/W224B: (V_{CC} = +4.5 V \text{ to } +5.5 V, V_{SS} = 0.0 V, T_A = -40^{\circ}\text{C to } +105^{\circ}\text{C} ) $ $ MB90P224A/W224A : (V_{CC} = +4.5 V \text{ to } +5.5 V, V_{SS} = 0.0 V, T_A = -40^{\circ}\text{C to } +85^{\circ}\text{C} ) $ |          |             |           |            |            |             |               |  |  |  |  |

|---------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|-------------|-----------|------------|------------|-------------|---------------|--|--|--|--|

| External bus mode         |                                                                                                                                                                                                                                                                       |          | : (Vcc = +4 | .5 V to + | 5.5 V, Vss | s = 0.0 V, | $T_A = -40$ | )°C to +70°C) |  |  |  |  |

| Parameter                 | Symbol                                                                                                                                                                                                                                                                | Pin name | Condition   |           | Value      |            | Unit        | Remarks       |  |  |  |  |

| Falameter                 | Symbol                                                                                                                                                                                                                                                                |          | Condition   | Min.      | Тур.       | Max.       | Unit        | Remains       |  |  |  |  |

| Power supply rising time  | tR                                                                                                                                                                                                                                                                    | Vcc      |             | _         | —          | 30         | ms          | *             |  |  |  |  |

| Power supply cut-off time | toff                                                                                                                                                                                                                                                                  | Vcc      | _           | 1         | _          | _          | ms          |               |  |  |  |  |

\* : Before power supply rising, it is required to be  $V_{CC} < 0.2$  V.

Notes: • Power-on reset assumes the above values.

- Whether the power-on reset is required or not, turn the power on according to these characteristics and trigger the power-on reset.

- There are internal registers (STBYC, etc.) which is initialized only by the power-on reset in the device.

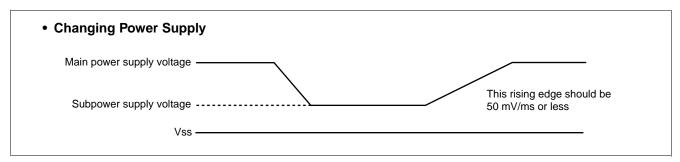

Note: Note on changing power supply

Even if above characteristics are not insufficient, abrupt changes in power supply voltage may cause a poweron reset. Therefore, at the time of a momentary changes such as when power is turned on, rise the power smoothly as shown below.

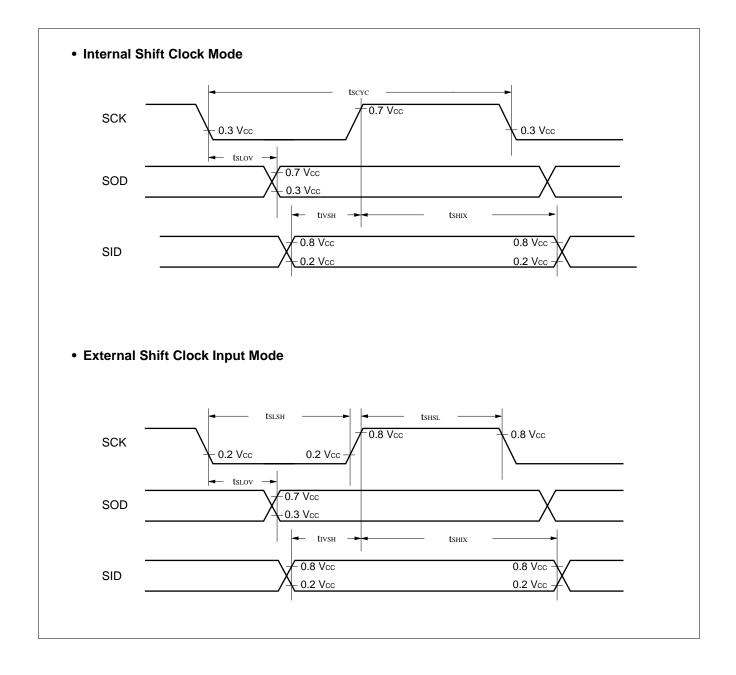

### (9) UART Timing

| Single-chip modeMB90223/224/P224B/W224B: (Vcc = +4.5 V to +5.5 V, Vss = 0.0 V, T_A = -40°C to +105°C)<br>$MB90P224A/W224A$ : (Vcc = +4.5 V to +5.5 V, Vss = 0.0 V, T_A = -40°C to +85°C)<br>$: (Vcc = +4.5 V to +5.5 V, Vss = 0.0 V, T_A = -40°C to +70°C)$ External bus mode: (Vcc = +4.5 V to +5.5 V, Vss = 0.0 V, T_A = -40°C to +70°C) |               |      |                          |               |      |      |                         |  |  |  |  |  |  |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------|------|--------------------------|---------------|------|------|-------------------------|--|--|--|--|--|--|

| Parameter                                                                                                                                                                                                                                                                                                                                  | Symbol        | Pin  | Condition                | Va            | lue  | Unit | Remarks                 |  |  |  |  |  |  |

| Parameter                                                                                                                                                                                                                                                                                                                                  | Symbol        | name | Condition                | Min.          | Max. | Unit | Remarks                 |  |  |  |  |  |  |

| Serial clock cycle time                                                                                                                                                                                                                                                                                                                    | tscyc         | _    |                          | <b>8</b> tcyc |      | ns   | Internal                |  |  |  |  |  |  |

| $SCLK \downarrow \to SOUT \text{ delay time}$                                                                                                                                                                                                                                                                                              | <b>t</b> slov | _    | Load condition:          | -80           | 80   | ns   | clock                   |  |  |  |  |  |  |

| Valid SIN $\rightarrow$ SCLK $\uparrow$                                                                                                                                                                                                                                                                                                    | <b>t</b> ivsh | —    | 80 pF                    | 100           | _    | ns   | operation<br>output pin |  |  |  |  |  |  |

| SCLK $\uparrow \rightarrow$ Valid SIN hold time                                                                                                                                                                                                                                                                                            | <b>t</b> shix | —    |                          | 60            | _    | ns   | output pin              |  |  |  |  |  |  |

| Serial clock "H" pulse width                                                                                                                                                                                                                                                                                                               | <b>t</b> shsl | _    |                          | 4 tcyc        | —    | ns   |                         |  |  |  |  |  |  |

| Serial clock "L" pulse width                                                                                                                                                                                                                                                                                                               | <b>t</b> slsh | _    |                          | 4 tcyc        | —    | ns   | External                |  |  |  |  |  |  |

| $SCLK \downarrow \to SOUT$ delay time                                                                                                                                                                                                                                                                                                      | <b>t</b> slov | _    | Load condition:<br>80 pF |               | 150  | ns   | clock<br>operation      |  |  |  |  |  |  |

| $Valid\;SIN\toSCLK\;\uparrow$                                                                                                                                                                                                                                                                                                              | <b>t</b> ivsh | —    |                          | 60            | —    | ns   | output pin              |  |  |  |  |  |  |

| SCLK $\uparrow \rightarrow$ valid SIN hold time                                                                                                                                                                                                                                                                                            | <b>t</b> shix |      |                          | 60            | _    | ns   |                         |  |  |  |  |  |  |

Notes: • These AC characteristics assume in CLK synchronization mode. • "tcvc" is the machine cycle (unit: ns).

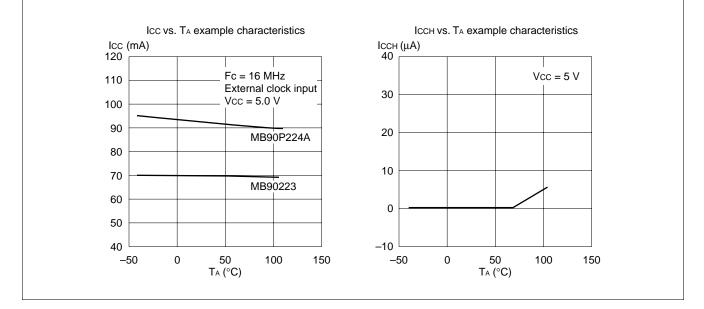

## ■ EXAMPLE CHARACTERISTICS

### (1) Power Supply Current

Note: These are not assured value of characteristics but example characteristics.

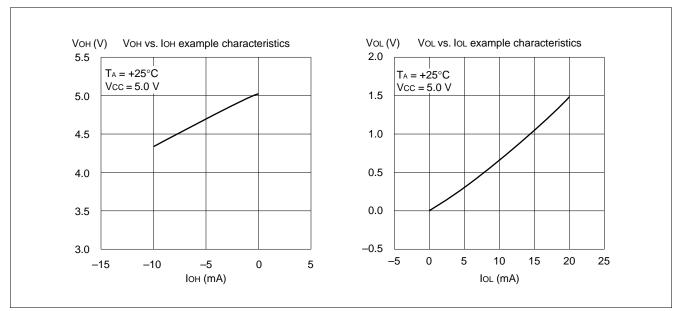

#### (2) Output Voltage

Note: These are not assured value of characteristics but example characteristics.

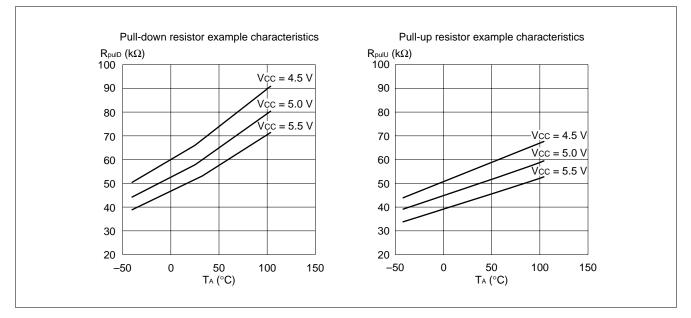

### (3) Pull-up/Pull-down Resistor

Note: These are not assured value of characteristics but example characteristics.

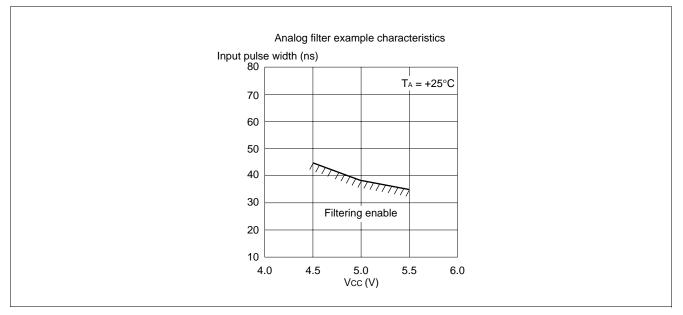

### (4) Analog Filter

| Mn           | emonic     | #       | cycles      | В           | Operation                                                            | LH     | AH     | Ι      | S      | Т | Ν | Ζ | ۷ | С | RMW |

|--------------|------------|---------|-------------|-------------|----------------------------------------------------------------------|--------|--------|--------|--------|---|---|---|---|---|-----|

| INC<br>INC   | ear<br>eam | 2<br>2+ | 2<br>3+ (a) | 0<br>2× (b) | byte (ear) ← (ear) +1<br>byte (eam) ← (eam) +1                       | -      | _      | _      | _      | _ | * | * | * |   | *   |

| DEC<br>DEC   | ear<br>eam | 2<br>2+ | 2<br>3+ (a) | 0<br>2× (b) | byte (ear) ← (ear) −1<br>byte (eam) ← (eam) −1                       | -      | _<br>_ | -      | -      | - | * | * | * |   | *   |

| INCW<br>INCW | ear<br>eam | 2<br>2+ | 2<br>3+ (a) | 0<br>2× (c) | word (ear) $\leftarrow$ (ear) +1<br>word (eam) $\leftarrow$ (eam) +1 | -      | _      | _      | _      | _ | * | * | * |   | *   |

| DECW<br>DECW | ear<br>eam | 2<br>2+ | 2<br>3+ (a) | 0<br>2× (c) | word (ear) $\leftarrow$ (ear) –1<br>word (eam) $\leftarrow$ (eam) –1 | -      | -      | _      | _      | - | * | * | * | - | *   |

| INCL<br>INCL | ear<br>eam | 2<br>2+ | 4<br>5+ (a) | 0<br>2× (d) | long (ear) $\leftarrow$ (ear) +1<br>long (eam) $\leftarrow$ (eam) +1 | _<br>_ | _      | _      | _      | _ | * | * | * | _ | *   |

| DECL<br>DECL | ear<br>eam | 2<br>2+ | 4<br>5+ (a) | 0<br>2× (d) | long (ear) ← (ear) −1<br>long (eam) ← (eam) −1                       | -      |        | _<br>_ | _<br>_ | - | * | * | * |   | *   |

Table 10 Increment and Decrement Instructions (Byte/Word/Long Word) [12 Instructions]

For an explanation of "(a)", "(b)", "(c)" and "(d)", refer to Table 4, "Number of Execution Cycles for Each Form of Addressing," and Table 5, "Correction Values for Number of Cycles Used to Calculate Number of Actual Cycles."

Table 11 Compare Instructions (Byte/Word/Long Word) [11 Instructions]

| Mn   | emonic    | #  | cycles | В   | Operation        | LH | AH | I | S | Т | Ν | Ζ | ۷ | С | RMW |

|------|-----------|----|--------|-----|------------------|----|----|---|---|---|---|---|---|---|-----|

| CMP  | А         | 1  | 2      | 0   | byte (AH) – (AL) | -  | -  | - | - | - | * | * | * | * | _   |

| CMP  | A, ear    | 2  | 2      | 0   | byte (A) – (ear) | —  | _  | _ | _ | _ | * | * | * | * | -   |

| CMP  | A, eam    | 2+ | 2+ (a) | (b) | byte (A) – (eam) | _  | _  | _ | _ | _ | * | * | * | * | -   |

| CMP  | A, #imm8  | 2  | 2      | `Ó  | byte (A) – imm8  | -  | -  | — | _ | - | * | * | * | * | —   |

| CMPW | А         | 1  | 2      | 0   | word (AH) – (AL) | -  | _  | Ι | _ | _ | * | * | * | * | _   |

| CMPW | A, ear    | 2  | 2      | 0   | word (A) – (ear) | —  | —  | _ | _ | — | * | * | * | * | -   |

| CMPW | A, eam    | 2+ | 2+ (a) | (c) | word (A) – (eam) | —  | —  | _ | _ | — | * | * | * | * | -   |

| CMPW | A, #imm16 | 3  | 2      | 0   | word (A) – imm16 | -  | -  | — | — | - | * | * | * | * | -   |

| CMPL | A, ear    | 2  | 3      | 0   | long (A) – (ear) | -  | _  | Ι | _ | _ | * | * | * | * | _   |

| CMPL | A, eam    | 2+ | 4+ (a) | (d) | long (A) – (eam) | -  | —  | — | — | - | * | * | * | * | —   |

| CMPL | A, #imm32 | 5  | 3      | 0   | long (A) – imm32 | -  | —  |   | — | - | * | * | * | * | —   |

For an explanation of "(a)", "(b)", "(c)" and "(d)", refer to Table 4, "Number of Execution Cycles for Each Form of Addressing," and Table 5, "Correction Values for Number of Cycles Used to Calculate Number of Actual Cycles."

| Mn           | emonic           | #       | cycles      | В        | Operation                                                                  | LH     | AH | I | S      | Т | Ν | Ζ | ۷      | С | RMW |

|--------------|------------------|---------|-------------|----------|----------------------------------------------------------------------------|--------|----|---|--------|---|---|---|--------|---|-----|

| ANDL<br>ANDL | A, ear<br>A, eam | 2<br>2+ | 5<br>6+ (a) |          | long (A) $\leftarrow$ (A) and (ear)<br>long (A) $\leftarrow$ (A) and (eam) |        |    | _ | -      | - | * | * | R<br>R | - |     |

| ORL<br>ORL   | A, ear<br>A, eam | 2<br>2+ | 5<br>6+ (a) |          | long (A) $\leftarrow$ (A) or (ear)<br>long (A) $\leftarrow$ (A) or (eam)   | _<br>_ | -  | _ | _      | - | * | * | R<br>R |   |     |

| XORL<br>XORL | A, ear<br>A, eam | 2<br>2+ | 5<br>6+ (a) | 0<br>(d) | long (A) $\leftarrow$ (A) xor (ear)<br>long (A) $\leftarrow$ (A) xor (eam) | _<br>_ | -  | _ | _<br>_ |   | * | * | R<br>R |   |     |

Table 15 Logical 2 Instructions (Long Word) [6 Instructions]

For an explanation of "(a)" and "(d)", refer to Table 4, "Number of Execution Cycles for Each Form of Addressing," and Table 5, "Correction Values for Number of Cycles Used to Calculate Number of Actual Cycles."

| Table 16 | Sign Inversion | Instructions | (Byte/Word) | [6 Instructions] |

|----------|----------------|--------------|-------------|------------------|

|----------|----------------|--------------|-------------|------------------|

| Mn           | emonic     | #       | cycles      | В           | Operation                                                              | LH | AH     | I | S      | Т      | Ν   | Ζ   | ۷   | С   | RMW |

|--------------|------------|---------|-------------|-------------|------------------------------------------------------------------------|----|--------|---|--------|--------|-----|-----|-----|-----|-----|

| NEG          | А          | 1       | 2           | 0           | byte (A) $\leftarrow$ 0 – (A)                                          | Х  | _      | - | _      | _      | *   | *   | *   | *   | _   |

| NEG<br>NEG   | ear<br>eam | 2<br>2+ | 2<br>3+ (a) |             | byte (ear) $\leftarrow$ 0 – (ear)<br>byte (eam) $\leftarrow$ 0 – (eam) | -  | _<br>_ | - |        | _<br>_ | *   | *   | *   | *   | *   |

| NEGW         | А          | 1       | 2           | 0           | word (A) $\leftarrow$ 0 – (A)                                          | -  | -      | Ι | -      | -      | *   | *   | *   | *   | _   |

| NEGW<br>NEGW |            | 2<br>2+ | 2<br>3+ (a) | 0<br>2× (c) | word (ear) $\leftarrow$ 0 – (ear)<br>word (eam) $\leftarrow$ 0 – (eam) | -  | _<br>_ |   | _<br>_ | _<br>_ | * * | * * | * * | * * | *   |

For an explanation of "(a)", "(b)" and "(c)" and refer to Table 4, "Number of Execution Cycles for Each Form of Addressing," and Table 5, "Correction Values for Number of Cycles Used to Calculate Number of Actual Cycles."

| Table 17 | Absolute Value Instructions | (Byte/Word/Long | Word) [3 Insturctions] |

|----------|-----------------------------|-----------------|------------------------|

|----------|-----------------------------|-----------------|------------------------|

| Mnemonic | # | cycles | В | Operation                                | LH | AH | Ι | S | Т | Ν | Ζ | ۷ | С | RMW |

|----------|---|--------|---|------------------------------------------|----|----|---|---|---|---|---|---|---|-----|

| ABS A    | 2 | 2      | 0 | byte (A) $\leftarrow$ absolute value (A) | Ζ  | -  | - | _ | Ι | * | * | * | - | _   |

| ABSW A   | 2 | 2      | 0 | word $(A) \leftarrow absolute value (A)$ | _  | —  | _ | _ | — | * | * | * | — | -   |

| ABSL A   | 2 | 4      | 0 | long $(A) \leftarrow absolute value (A)$ | —  | -  | - | — | - | * | * | * | — | -   |

| Table 18 | Normalize Instructions | (Long Word) [ˈ | 1 Instruction] |

|----------|------------------------|----------------|----------------|

|----------|------------------------|----------------|----------------|

| Mne  | emonic  | # | cycles | В | Operation                                                                                                          | LH | AH | I | S | Т | Ν | Ζ | ۷ | С | RMW |

|------|---------|---|--------|---|--------------------------------------------------------------------------------------------------------------------|----|----|---|---|---|---|---|---|---|-----|

| NRML | - A, R0 | 2 | *      |   | long (A) $\leftarrow$ Shifts to the position at which "1" was set first byte (R0) $\leftarrow$ current shift count | -  | -  | - | - | * | - | _ | - | - | -   |

\*: 5 when the contents of the accumulator are all zeroes, 5 + (R0) in all other cases.

| Mnemonic                                                         |                            | cycles                        | В                          | Operation                                                                                                                                                                                                                                                                        | LH          | AH          | Ι           | S                   | Т                | Ν                | Ζ                   | V                | С           | RMW         |

|------------------------------------------------------------------|----------------------------|-------------------------------|----------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|-------------|-------------|---------------------|------------------|------------------|---------------------|------------------|-------------|-------------|

| PUSHW A<br>PUSHW AH<br>PUSHW PS<br>PUSHW rlst                    | 1<br>1<br>1<br>2           | 3<br>3<br>3<br>* <sup>3</sup> | (C)<br>(C)<br>(C)<br>*4    | word (SP) $\leftarrow$ (SP) -2, ((SP)) $\leftarrow$ (A)<br>word (SP) $\leftarrow$ (SP) -2, ((SP)) $\leftarrow$ (AH)<br>word (SP) $\leftarrow$ (SP) -2, ((SP)) $\leftarrow$ (PS)<br>(SP) $\leftarrow$ (SP) -2n, ((SP)) $\leftarrow$ (rlst)                                        |             | -<br>-<br>- | -<br>-<br>- | _<br>_<br>_<br>_    | _<br>_<br>_<br>_ | <br>             | <br>                | <br><br>         | -<br>-<br>- | -<br>-<br>- |

| POPW A<br>POPW AH<br>POPW PS<br>POPW rlst                        | 1<br>1<br>1<br>2           | 3<br>3<br>3<br>*2             | (C)<br>(C)<br>(C)<br>*4    | $\begin{array}{l} \text{word} (A) \leftarrow ((SP)), (SP) \leftarrow (SP) + 2\\ \text{word} (AH) \leftarrow ((SP)), (SP) \leftarrow (SP) + 2\\ \text{word} (PS) \leftarrow ((SP)), (SP) \leftarrow (SP) + 2\\ (\text{rlst}) \leftarrow ((SP)), (SP) \leftarrow (SP) \end{array}$ | <br>        | *           | <br>  *<br> | *                   | _<br>*<br>_      | *                | *                   | _<br>*<br>_      | *           | <br> <br>   |

| JCTX @A                                                          | 1                          | 9                             | 6× (c)                     | Context switch instruction                                                                                                                                                                                                                                                       | _           | _           | *           | *                   | *                | *                | *                   | *                | *           | -           |

| AND CCR, #imm<br>OR CCR, #imm                                    |                            | 3<br>3                        | 0<br>0                     | byte (CCR) $\leftarrow$ (CCR) and imm8<br>byte (CCR) $\leftarrow$ (CCR) or imm8                                                                                                                                                                                                  | _           | -           | *           | *                   | *                | *                | *                   | *                | *           | _<br>_      |

| MOV RP, #imm8<br>MOV ILM, #imm8                                  | 2<br>2                     | 2<br>2                        | 0<br>0                     | byte (RP) ←imm8<br>byte (ILM) ←imm8                                                                                                                                                                                                                                              | _           | -           | -           |                     | -                | _<br>_           | _<br>_              | _<br>_           | _           | _           |

| MOVEA RWi, ear<br>MOVEA RWi, eam<br>MOVEA A, ear<br>MOVEA A, eam | 2<br>2+<br>2<br>2+         | 2                             | 0                          | word (RWi) ←ear<br>word (RWi) ←eam<br>word(A) ←ear<br>word (A) ←eam                                                                                                                                                                                                              | <br><br>    | *           |             | _<br>_<br>_         | -<br>-<br>-      | _<br>_<br>_<br>_ | _<br>_<br>_         | _<br>_<br>_      |             | <br> <br>   |

| ADDSP #imm8<br>ADDSP #imm16                                      | 2<br>3                     | 3<br>3                        | 0<br>0                     | word (SP) $\leftarrow$ ext (imm8)<br>word (SP) $\leftarrow$ imm16                                                                                                                                                                                                                | _           |             |             |                     | -                |                  |                     | _<br>_           |             | _           |

| MOV A, brgl<br>MOV brg2, A<br>MOV brg2, #imm8                    | 2<br>2<br>3                | *1<br>1<br>2                  | 0<br>0<br>0                | byte (A) $\leftarrow$ (brgl)<br>byte (brg2) $\leftarrow$ (A)<br>byte (brg2) $\leftarrow$ imm8                                                                                                                                                                                    | Z<br>-<br>- | *           |             | _<br>_<br>_         | -<br>-<br>-      | *<br>*<br>*      | *<br>*<br>*         | _<br>_<br>_      | -<br>-<br>- | -<br>-<br>- |

| NOP<br>ADB<br>DTB<br>PCB<br>SPB<br>NCC<br>CMR                    | 1<br>1<br>1<br>1<br>1<br>1 | 1<br>1<br>1<br>1<br>1<br>1    | 0<br>0<br>0<br>0<br>0<br>0 | No operation<br>Prefix code for AD space access<br>Prefix code for DT space access<br>Prefix code for PC space access<br>Prefix code for SP space access<br>Prefix code for no flag change<br>Prefix code for the common<br>register bank                                        |             |             |             | <br> <br> <br> <br> | -<br>-<br>-<br>- | -<br>-<br>-<br>- | <br> <br> <br> <br> | -<br>-<br>-<br>- |             |             |

| MOVW SPCU, #imm1<br>MOVW SPCL, #imm1<br>SETSPC<br>CLRSPC         |                            | 2<br>2<br>2<br>2              | 0<br>0<br>0<br>0           | word (SPCU) $\leftarrow$ (imm16)<br>word (SPCL) $\leftarrow$ (imm16)<br>Stack check ooperation enable<br>Stack check ooperation disable                                                                                                                                          | <br><br>    |             | _<br>_<br>_ | _<br>_<br>_         | -<br>-<br>-      | _<br>_<br>_      | _<br>  _<br>  _     | _<br>_<br>_<br>_ | -<br>-<br>- | -<br>-<br>- |

| BTSCN A<br>BTSCNS A<br>BTSCND A                                  | 2<br>2<br>2                | *5<br>*6<br>*7                | 0<br>0<br>0                | byte (A) $\leftarrow$ position of "1" bit in word (A)<br>byte (A) $\leftarrow$ position of "1" bit in word (A) $\times 2$<br>byte (A) $\leftarrow$ position of "1" bit in word (A) $\times 4$                                                                                    | Z<br>Z<br>Z | _<br>_<br>_ | _<br>_<br>_ | _<br>_<br>_         | -<br>-<br>-      | _<br>_<br>_      | *<br>*<br>*         | _<br>_<br>_      | -<br>-<br>- | -<br>-<br>- |

#### Table 22 Other Control Instructions (Byte/Word/Long Word) [36 Instructions]

For an explanation of "(a)" and "(c)", refer to Tables 4 and 5.

- \*1: PCB, ADB, SSB, USB, and SPB: 1 cycle

- DTB: 2 cycles

- DPR: 3 cycles

- \*6

- \*2:  $3 + 4 \times (pop count)$

- \*3:  $3 + 4 \times (push count)$

- \*4: Pop count  $\times$  (c), or push count  $\times$  (c)

- \*5: 3 when AL is 0, 5 when AL is not 0.

- \*6: 4 when AL is 0, 6 when AL is not 0.

- \*7: 5 when AL is 0, 7 when AL is not 0.