Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Product Status             | Active                                                                      |

|----------------------------|-----------------------------------------------------------------------------|

| Core Processor             | F <sup>2</sup> MC-16F                                                       |

| Core Size                  | 16-Bit                                                                      |

| Speed                      | 16MHz                                                                       |

| Connectivity               | EBI/EMI, UART/USART                                                         |

| Peripherals                | POR, PWM, WDT                                                               |

| Number of I/O              | 102                                                                         |

| Program Memory Size        | 96KB (96K x 8)                                                              |

| Program Memory Type        | Mask ROM                                                                    |

| EEPROM Size                | -                                                                           |

| RAM Size                   | 4.5K x 8                                                                    |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 5.5V                                                                   |

| Data Converters            | A/D 16x10b                                                                  |

| Oscillator Type            | External                                                                    |

| Operating Temperature      | -40°C ~ 105°C (TA)                                                          |

| Mounting Type              | Surface Mount                                                               |

| Package / Case             | 120-BQFP                                                                    |

| Supplier Device Package    | 120-QFP (28x28)                                                             |

| Purchase URL               | https://www.e-xfl.com/product-detail/infineon-technologies/mb90224pf-gt-368 |

|                            |                                                                             |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

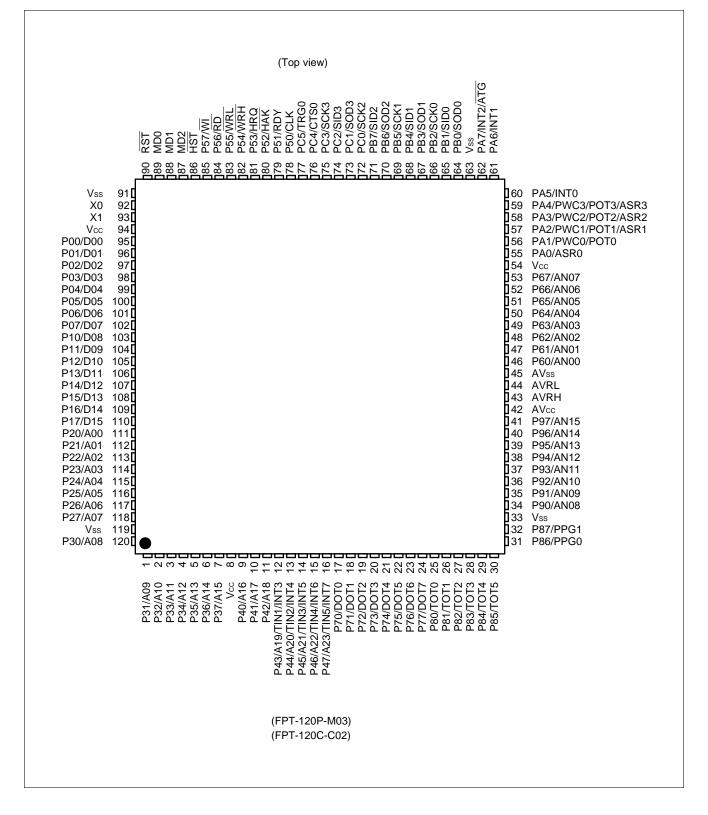

#### PIN ASSIGNMENT

### ■ PIN DESCRIPTION

| Pin no.        | Pin name           | Circuit | Function                                                                                                                                                                                                          |

|----------------|--------------------|---------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| QFP*           | Finname            | type    | Function                                                                                                                                                                                                          |

| 92,<br>93      | X0,<br>X1          | A       | Crystal oscillation pins (16 MHz)                                                                                                                                                                                 |

| 89 to 87       | MD0 to MD2         | D       | Operation mode specification input pins<br>Connect directly to Vcc or Vss.                                                                                                                                        |

| 90             | RST                | G       | External reset request input                                                                                                                                                                                      |

| 86             | HST                | E       | Hardware standby input pin                                                                                                                                                                                        |

| 95 to 102      | P00 to P07         | С       | General-purpose I/O ports<br>This function is valid only in single-chip mode.                                                                                                                                     |

|                | D00 to D07         |         | Output pins for low-order 8 bits of the external address bus.<br>This function is valid only in modes where the external bus is<br>enabled.                                                                       |

| 103 to 110     | P10 to P17         | С       | General-purpose I/O ports<br>This function is valid only in single-chip mode or when the external bus<br>is enabled and the 8-bit data bus specification has been made.                                           |

|                | D08 to D15         |         | I/O pins for higher-order 8 bits of the external data bus<br>This function is valid only when the external bus is enabled and the<br>16-bit bus specification has been made.                                      |

| 111 to 118     | P20 to P27         | С       | General-purpose I/O ports<br>This function is valid only in single-chip mode.                                                                                                                                     |

|                | A00 to A07         |         | Output pins for lower-order 8 bits of the external address bus<br>This function is valid only in modes where the external bus is<br>enabled.                                                                      |

| 120,<br>1 to 7 | P30,<br>P31 to P37 | С       | General-purpose I/O ports<br>This function is valid either in single-chip mode or when the address<br>mid-order control register specification is "port".                                                         |

|                | A08,<br>A09 to A15 |         | Output pins for mid-order 8 bits of the external address bus<br>This function is valid in modes where the external bus is enabled and<br>the address mid-order control register specification is "address".       |

| 9 to 11        | P40 to P42         | С       | General-purpose I/O ports<br>This function is valid either in single-chip mode or when the address<br>high-order control register specification is "port".                                                        |

|                | A16 to A18         |         | Output pins for higher-order 8 bits of the external address bus<br>This function is valid in modes where the external bus is enabled and<br>the address high-order control register specification is "address".   |

| 12 to 16       | P43 to P47         | С       | General-purpose I/O ports<br>This function is valid when either single-chip mode is enabled or the<br>address higher-order control register specification is "port".                                              |

|                | A19 to A23         |         | Output pins for higher-order 8 bits of the external address bus<br>This function is valid in modes where the external bus is enabled and<br>the address higher-order control register specification is "address". |

|                | TIN1 to TIN5       |         | 16-bit reload timer input pins<br>This function is valid when the timer input specification is "enabled".<br>The data on the pins is read as timer input (TIN1 to TIN5).                                          |

\* : FPT-120P-M03, FPT-120C-C02

-

| Pin no.  | – Pin name   | Circuit | Function                                                                                                                                                                                                                                                                                                                            |

|----------|--------------|---------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| QFP*     | Tinname      | type    | i unction                                                                                                                                                                                                                                                                                                                           |

| 12 to 16 | INT3 to INT7 | С       | External interrupt request input pins<br>When external interrupts are enabled, these inputs may be used<br>suddenly at any time; therefore, it is necessary to stop output by other<br>functions on these pins, except when using them for output<br>deliberately.                                                                  |

| 78       | P50          | С       | General-purpose I/O port<br>This function is valid in single-chip mode and when the CLK output<br>specification is disabled.                                                                                                                                                                                                        |

|          | CLK          |         | CLK output pin<br>This function is valid in modes where the external bus is enabled and<br>the CLK output specification is enabled.                                                                                                                                                                                                 |

| 79       | P51          | С       | General-purpose I/O port<br>This function is valid in single-chip mode or when the ready function<br>is disabled.                                                                                                                                                                                                                   |

|          | RDY          |         | Ready input pin<br>This function is valid in modes where the external bus is enabled and<br>the ready function is enabled.                                                                                                                                                                                                          |

| 80       | P52          | С       | General-purpose I/O port<br>This function is valid in single-chip mode or when the hold function is<br>disabled.                                                                                                                                                                                                                    |

|          | HAK          |         | Hold acknowledge output pin<br>This function is valid in modes where the external bus is enabled and<br>the hold function is enabled.                                                                                                                                                                                               |

| 81       | P53          | С       | General-purpose I/O port<br>This function is valid in single-chip mode or external bus mode and<br>when the hold function is disabled.                                                                                                                                                                                              |

|          | HRQ          | -       | Hold request input pin<br>This function is valid in modes where the external bus is enabled and<br>the hold function is enabled.<br>During this operation, the input may be used suddenly at any time;<br>therefore, it is necessary to stop output by other fuctions on this pin,<br>except when using it for output deliberately. |

| 82       | P54          | С       | General-purpose I/O port<br>This function is valid in single-chip mode, when the external bus is in<br>8-bit mode, or when WRH pin output is disabled.                                                                                                                                                                              |

|          | WRH          |         | Write strobe output pin for the high-order 8 bits of the data bus<br>This function is valid in modes where the external bus is enabled, the<br>external bus is in 16-bit mode, and WRH pin output is enabled.                                                                                                                       |

| 83       | P55          | С       | General-purpose I/O port This function is valid in single-chip mode or when $\overline{\text{WRL}}$ pin output is disabled.                                                                                                                                                                                                         |

|          | WRL          |         | Write strobe output pin for the low-order 8 bits of the data bus<br>This function is valid in modes where the external bus is enabled and<br>WRL pin output is enabled.                                                                                                                                                             |

\* : FPT-120P-M03, FPT-120C-C02

(Continued)

| Pin no. | Pin name | Circuit | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|---------|----------|---------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| QFP*    |          | type    |                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 62      | INT2     | В       | DTP/External interrupt request input pin<br>When DTP/external interrupts are enabled, these inputs may be used<br>suddenly at any time; therefore, it is necessary to stop output by other<br>functions on these pins, except when using them for output<br>deliberately.<br>When these pins are open in input mode, through current may leak in<br>stop mode/reset mode, be sure to fix these pins to Vcc/Vss level to<br>use these pins in input mode. |

|         | ATG      |         | 10-bit A/D converter external trigger input pin When these pins are open in input mode, through current may leak in stop mode/reset mode, be sure to fix these pins to $V_{CC}/V_{SS}$ level to use these pins in input mode.                                                                                                                                                                                                                            |

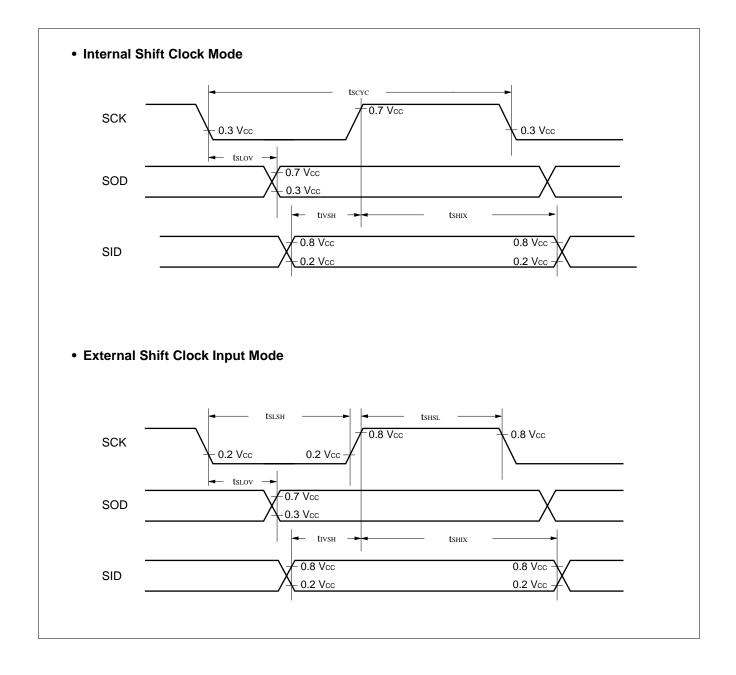

| 64      | PB0      | С       | General-purpose I/O port<br>This function is valid when the UART0 (ch.0) serial data output<br>specification is "disabled".                                                                                                                                                                                                                                                                                                                              |

|         | SOD0     |         | UART0 (ch.0) serial data output<br>This function is valid when the UART0 (ch.0) serial data output<br>specification is "enabled".                                                                                                                                                                                                                                                                                                                        |

| 65      | PB1      | С       | General-purpose I/O port<br>This function is always valid.                                                                                                                                                                                                                                                                                                                                                                                               |

|         | SIDO     |         | UART0 (ch.0) serial data input pin<br>During UART0 (ch.0) input operations, this input may be used<br>suddenly at any time; therefore, it is necessary to stop output by other<br>functions on this pin, except when using it for output deliberately.                                                                                                                                                                                                   |

| 66      | PB2      | С       | General-purpose output port<br>This function is valid when the UART0 (ch.0) clock output<br>specification is "disabled".                                                                                                                                                                                                                                                                                                                                 |

|         | SCK0     |         | UART0 (ch.0) clock output pin<br>The clock output function is valid when the UART0 (ch.0) clock output<br>specification is "enabled".<br>UART0 (ch.0) external clock input pin. This function is valid when the<br>port is in input mode and the UART0 (ch.0) specification is external<br>clock mode.                                                                                                                                                   |

| 67      | PB3      | С       | General-purpose I/O port<br>This function is valid when the UART0 (ch.1) serial data output<br>specification is "disabled".                                                                                                                                                                                                                                                                                                                              |

|         | SOD1     |         | UART0 (ch.1) serial data output pin<br>This function is valid when the UART0 (ch.1) serial data output<br>specification is "enabled".                                                                                                                                                                                                                                                                                                                    |

| 68      | PB4      | С       | General-purpose I/O port<br>This function is always valid.                                                                                                                                                                                                                                                                                                                                                                                               |

|         | SID1     |         | UART0 (ch.1) serial data input pin<br>During UART0 (ch.1) input operations, this input may be used<br>suddenly at any time; therefore, it is necessary to stop output by other<br>functions on this pin, except when using it for output deliberately.                                                                                                                                                                                                   |

\* : FPT-120P-M03, FPT-120C-C02

(Continued)

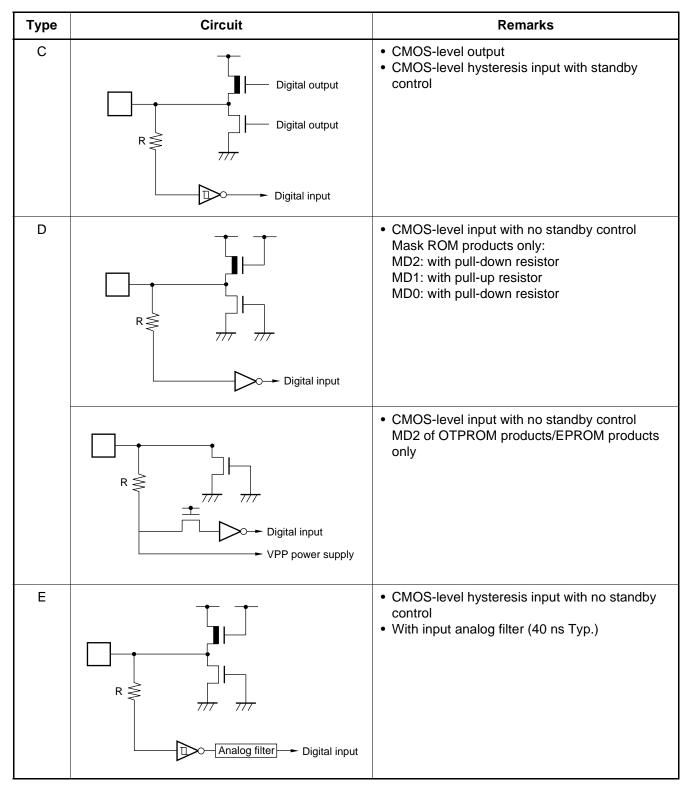

Note: The pull-up and pull-down resistors are always connected, regardless of the state.

(Continued)

### ■ HANDLING DEVICES

#### 1. Preventing Latchup

CMOS ICs may cause latchup when a voltage higher than  $V_{cc}$  or lower than  $V_{ss}$  is applied to input or output pins other than medium-and high-voltage pins, or when a voltage exceeding the rating is applied between  $V_{cc}$  and  $V_{ss}$ .

If latch-up occurs, the power supply current increases rapidly, sometimes resulting in thermal breakdown of the device. Use meticulous care not to let any voltage exceed the maximum rating.

Also, take care to prevent the analog power supply (AV<sub>cc</sub> and AVRH) and analog input from exceeding the digital power supply (V<sub>cc</sub>) when the analog system power supply is turned on and off.

#### 2. Treatment of Unused Input Pins

Leaving unused input pins open could cause malfunctions. They should be connected to a pull-up or pull-down resistor.

#### 3. Treatment of Pins when A/D is not Used

Connect to be AVcc = AVRH = Vcc and AVss = AVRL = Vss even if the A/D converter is not in use.

#### 4. Precautions when Using an External Input

To reset the internal circuit properly by the "L" level input to the  $\overline{RST}$  pin, the "L" level input to the  $\overline{RST}$  pin must be maintained for at least five machine cycles. Pay attention to it if the chip uses external clock input.

#### 5. Vcc and Vss Pins

Apply equal potential to the Vcc and Vss pins.

#### 6. Supply Voltage Variation

The operation assurance range for the V<sub>cc</sub> supply voltage is as given in the ratings. However, sudden changes in the supply voltage can cause misoperation, even if the voltage remains within the rated range. Therefore, it is important to supply a stable voltage to the IC. The recommended power supply control guidelines are that the commercial frequency (50 to 60 Hz) ripple variation (P-P value) on V<sub>cc</sub> should be less than 10% of the standard V<sub>cc</sub> value and that the transient rate of change during sudden changes, such as during power supply switching, should be less than 0.1 V/ms.

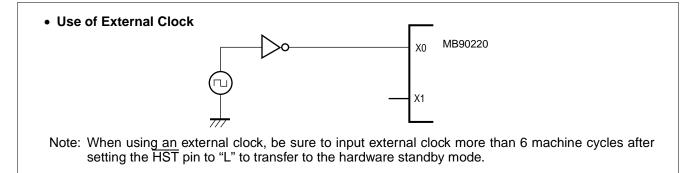

### 7. Notes on Using an External Clock

When using an external clock, drive the X0 pin as illustrated below. When an external clock is used, oscillation stabilization time is required even for power-on reset and wake-up from stop mode.

### ■ PERIPHERAL RESOURCES

### **1. Parallel Ports**

The MB90220 series has 86 I/O pins and 16 open-drain I/O pins.

#### (1) Register Configuration

### • Port 0 to C Data Register (PDR0 to PDRC)

| Register name<br>PDR1<br>PDR3<br>PDR5<br>PDR7 | Address<br>000001 н<br>000003 н<br>000005 н<br>000007 н | bit15 bit14 bit13 bit12 bit11 bit10 bit9 bit8 Initial value<br>PD x 7 PD x 6 PD x 5 PD x 4 PD x 3 PD x 2 PD x 1 PD x 0 XXXXXXX B |  |

|-----------------------------------------------|---------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------|--|

| PDR9                                          | 000009 н                                                | (R/W) (R/W) (R/W) (R/W) (R/W) (R/W) (R/W) (R/W) (PDR9 only: 1111111)                                                             |  |

| PDRB                                          | 00000Вн                                                 | PDR7 only: (R) (R) (R) (R) (R) (R) (R)                                                                                           |  |

| Register name                                 | Address                                                 |                                                                                                                                  |  |

| PDR0                                          | 00000 н                                                 |                                                                                                                                  |  |

| PDR2                                          | 000002 н                                                |                                                                                                                                  |  |

| PDR4                                          | 000004 н                                                | bit7 bit6 bit5 bit 4 bit3 bit2 bit1 bit0 Initial value                                                                           |  |

| PDR6                                          | 00006 н                                                 |                                                                                                                                  |  |

| PDR8                                          | 000008 н                                                | PD x 7 PD x 6 PD x 5 PD x 4 PD x 3 PD x 2 PD x 1 PD x 0 XXXXXXXX                                                                 |  |

| PDRA<br>PDRC                                  | 00000Ан<br>00000Сн                                      | (R/W) (R/W) (R/W) (R/W) (R/W) (R/W) (R/W) (R/W) (PDR6 only: 1111111)                                                             |  |

Note: There are no register bits for bits 7 and 6 of port C.

#### • Port 0 to C Data Register (PDR0 to PDRC)

| Register name<br>DDR1<br>DDR3<br>DDR5<br>DDR7 | Address<br>000011 н<br>000013 н<br>000015 н<br>000017 н | bit15 bit14 bit13 bit12 bit11 bit10 bit9 bit8 Initial value<br>$\begin{bmatrix} DD x 7 & DD x 6 & DD x 5 & DD x 4 & DD x 3 & DD x 2 & DD x 1 & DD x 0 & \hline \\ DD x 7 & DD x 6 & DD x 5 & DD x 4 & DD x 3 & DD x 2 & DD x 1 & DD x 0 & \hline \\ DD x 7 & DD x 6 & DD x 5 & DD x 4 & DD x 0 & DD x 0 & \hline \\ DD x 7 & DD x 6 & DD x 5 & DD x 4 & DD x 0 & DD x 0 & \hline \\ DD x 7 & DD x 6 & DD x 5 & DD x 4 & DD x 0 & DD x 0 & \hline \\ DD x 7 & DD x 6 & DD x 5 & DD x 4 & DD x 0 & DD x 0 & DD x 0 & \hline \\ DD x 7 & DD x 6 & DD x 5 & DD x 4 & DD x 0 & DD x 0 & \hline \\ DD x 7 & DD x 6 & DD x 5 & DD x 4 & DD x 0 & DD x 0 & DD x 0 & \hline \\ DD x 7 & DD x 6 & DD x 5 & DD x 4 & DD x 0 & DD x 0 & \hline \\ DD x 7 & DD x 6 & DD x 5 & DD x 4 & DD x 0 & DD x 0 & DD x 0 & \hline \\ DD x 7 & DD x 6 & DD x 5 & DD x 4 & DD x 0 & DD x 0 & DD x 0 & \hline \\ DD x 7 & DD x 6 & DD x 5 & DD x 4 & DD x 0 & DD x 0 & DD x 0 & D0 & \hline \\ DD x 7 & DD x 6 & DD x 5 & DD x 4 & DD x 0 & DD x 0 & D0 & \hline \\ DD x 7 & DD x 6 & DD x 5 & DD x 4 & DD x 0 & D0 & D0 & \hline \\ DD x 7 & DD x 6 & DD x 5 & DD x 4 & DD x 0 & D0 & D0 & D0 & \hline \\ DD x 7 & DD x 6 & DD x 5 & DD x 4 & DD x 0 & D0 & D0 & D0 & \hline \\ DD x 7 & DD x 6 & DD x 5 & DD x 4 & DD x 0 & D0 & D0 & D0 & \hline \\ DD x 7 & DD x 6 & DD x 5 & DD x 4 & DD x 0 & D0 & D0 & D0 & D0 & \hline \\ DD x 7 & DD x 0 & D0 & D0 & D0 & D0 & D0 & D0 $ |

|-----------------------------------------------|---------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| DDRB                                          | 00001Вн                                                 | (R/W) (R/W) (R/W) (R/W) (R/W) (R/W) (R/W) (R/W) (PDR7 only: 1111111)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| Register name<br>DDR0<br>DDR2<br>DDR4         | Address<br>000010 н<br>000012 н<br>000014 н             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| DDR4<br>DDR8                                  | 000014н<br>000018н                                      | bit7 bit6 bit5 bit 4 bit3 bit2 bit1 bit0 Initial value                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| DDRO                                          | 000018н<br>00001Ан                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| DDRA                                          | 00001Aн<br>00001Cн -                                    | DD x 7 DD x 6 DD x 5 DD x 4 DD x 3 DD x 2 DD x 1 DD x 0 0000000 B                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| -                                             |                                                         | (R/W) (R/W) (R/W) (R/W) (R/W) (R/W) (R/W) (R/W)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

Note: There are no register bits for bits 7 and 6 of port C.

#### • Port 6, 9 Analog Input Enable Register (ADER0, ADER1)

| Register name Address<br>ADER0 000016 н |                     | bit7  | bit6  | bit5  | bit 4 | bit3  | bit2  | bit1  | bit0  | Initial value |

|-----------------------------------------|---------------------|-------|-------|-------|-------|-------|-------|-------|-------|---------------|

|                                         | 0000101             | AE07  | AE06  | AE05  | AE04  | AE03  | AE02  | AE01  | AE00  | 11111111 в    |

|                                         |                     | (R/W) |               |

| Register name<br>ADER1                  | Address<br>000019 H | bit7  | bit6  | bit5  | bit 4 | bit3  | bit2  | bit1  | bit0  | Initial value |

| ADEINI                                  | 0000198             | AE15  | AE14  | AE13  | AE12  | AE11  | AE10  | AE09  | AE08  | 11111111 в    |

|                                         |                     | (R/W) |               |

#### (2) Block Diagram

#### (2) Block Diagram

### 5. 10-bit A/D Converter

The 10-bit A/D converter converts analog input voltage into a digital value. The features of this module are described below:

- Conversion time: 6.125 μs/channel (min.) (with machine clock running at 16 MHz)

- · Uses RC-type sequential comparison and conversion method with built-in sample and hold circuit

- 10-bit resolution

| Analog input can be selected b | by software from among 16 channels                                            |

|--------------------------------|-------------------------------------------------------------------------------|

| Single-conversion mode:        | Selects and converts one channel.                                             |

| Scan conversion mode:          | Converts several consecutive channels (up to 16 can be programmed).           |

| One-shot mode:                 | Converts the specified channel once and terminates.                           |

| Continuous conversion mode:    | Repeatedly converts the specified channel.                                    |

| Stop conversion mode:          | Pauses after converting one channel and waits until the next startup (permits |

|                                | synchronization of start of conversion).                                      |

- When A/D conversion is completed, an "A/D conversion complete" interrupt request can be issued to the CPU. Because the generation of this interrupt can be used to start up the EI<sup>2</sup>OS and transfer the A/D conversion results to memory, this function is suitable for continuous processing.

- Startup triggers can be selected from among software, an external trigger (falling edge), and a timer (rising edge).

#### (1) Register Configuration

#### • A/D Channel Setting Register (ADCH)

This register specfies the A/D converter conversion channel.

| Register name | Address | bit7  | bit6  | bit5  | bit4  | bit3  | bit2  | bit1  | bit0  | Initial value |

|---------------|---------|-------|-------|-------|-------|-------|-------|-------|-------|---------------|

| ADCH          | 000032н | ANS3  | ANS2  | ANS1  | ANS0  | ANE3  | ANE2  | ANE1  | ANE0  | 00000000 в    |

|               |         | (R/W) |               |

#### • A/D Mode Register (ADMD)

This register specfies the A/D converter operation mode and the startup source.

| Register name Add | dress   | bit15 | bit14 | bit13 | bit12    | bit11 | bit10 | bit9  | bit8  | Initial value |

|-------------------|---------|-------|-------|-------|----------|-------|-------|-------|-------|---------------|

| ADMD 000          | 0033н [ |       | —     | _     | Reserved | MOD1  | MOD0  | STS1  | STS0  | Х0000 в       |

|                   | -       | (—)   | (—)   | (—)   | (W)      | (R/W) | (R/W) | (R/W) | (R/W) |               |

Note: Program "0" to bit 12 when write. Read value is indeterminated.

#### • A/D Control Status Register (ADCS)

This register is the A/D converter control and status register.

| Register name |         | bit7  | bit6  | bit5  | bit4  | bit3 | bit2 | bit1 | bit0     | Initial value |

|---------------|---------|-------|-------|-------|-------|------|------|------|----------|---------------|

| ADCS          | 000034н | BUSY  | INT   | INTE  | PAUS  | _    | _    | STRT | Reserved | 0000 00 в     |

|               |         | (R/W) | (R/W) | (R/W) | (R/W) | (—)  | (—)  | (W)  | (R/W)    |               |

#### A/D Data Register (ADCD)

This register stores the A/D converter conversion data.

| Register name Address | bit7 | bit6 | bit5 | bit4 | bit3 | bit2 | bit1 | bit0 | Initial value |

|-----------------------|------|------|------|------|------|------|------|------|---------------|

| ADCD 000036H          | D7   | D6   | D5   | D4   | D3   | D2   | D1   | D0   | XXXXXXXX в    |

|                       | (R)  | -             |

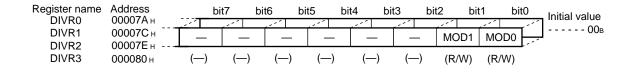

#### • PWC Division Ratio Control Register 0 to 3 (DIVR0 to DIVR3)

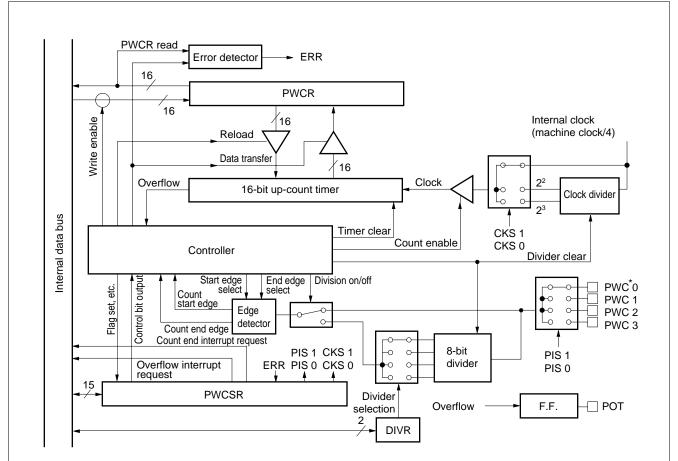

#### (2) Block Diagram

\*: In the MB90220 series, only the module input PWC 0 of each channel is connected to the respective external pins.

| Channel   | POT pin                |

|-----------|------------------------|

| PWC ch. 0 | PA 1/PWC 0/POT 0       |

| PWC ch. 1 | PA 2/PWC 1/POT 1/ASR 1 |

| PWC ch. 2 | PA 3/PWC 2/POT 2/ASR 2 |

| PWC ch. 3 | PA 4/PWC 3POT 3/ASR 3  |

### ■ INSTRUCTION SET (412 INSTRUCTIONS)

| Table 1 | Explanation of Items in Table of Instructions |

|---------|-----------------------------------------------|

|---------|-----------------------------------------------|

| Item      | Explanation                                                                                                                                                                                                                                                                                                                                                                                                                        |

|-----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Mnemonic  | Upper-case letters and symbols: Represented as they appear in assembler<br>Lower-case letters: Replaced when described in assembler.<br>Numbers after lower-case letters: Indicate the bit width within the instruction.                                                                                                                                                                                                           |

| #         | Indicates the number of bytes.                                                                                                                                                                                                                                                                                                                                                                                                     |

| ~         | Indicates the number of cycles.<br>See Table 4 for details about meanings of letters in items.                                                                                                                                                                                                                                                                                                                                     |

| В         | Indicates the correction value for calculating the number of actual cycles during execution of instruction.<br>The number of actual cycles during execution of instruction is summed with the value in the "cycles" column.                                                                                                                                                                                                        |

| Operation | Indicates operation of instruction.                                                                                                                                                                                                                                                                                                                                                                                                |

| LH        | Indicates special operations involving the bits 15 through 08 of the accumulator.<br>Z: Transfers "0".<br>X: Extends before transferring.<br>—: Transfers nothing.                                                                                                                                                                                                                                                                 |

| AH        | Indicates special operations involving the high-order 16 bits in the accumulator.<br>*: Transfers from AL to AH.<br>—: No transfer.<br>Z: Transfers 00 <sub>H</sub> to AH.<br>X: Transfers 00 <sub>H</sub> or FF <sub>H</sub> to AH by extending AL.                                                                                                                                                                               |

| I         | Indicates the status of each of the following flags: I (interrupt enable), S (stack), T (sticky                                                                                                                                                                                                                                                                                                                                    |

| S         | <ul> <li>bit), N (negative), Z (zero), V (overflow), and C (carry).</li> <li>*: Changes due to execution of instruction.</li> </ul>                                                                                                                                                                                                                                                                                                |

| Т         | —: No change.                                                                                                                                                                                                                                                                                                                                                                                                                      |

| N         | <ul> <li>Set by execution of instruction.</li> <li>R: Reset by execution of instruction.</li> </ul>                                                                                                                                                                                                                                                                                                                                |

| Z         | ,                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| V         |                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| С         |                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| RMW       | Indicates whether the instruction is a read-modify-write instruction (a single instruction<br>that reads data from memory, etc., processes the data, and then writes the result to<br>memory.).<br>*: Instruction is a read-modify-write instruction<br>—: Instruction is not a read-modify-write instruction<br>Note: Cannot be used for addresses that have different meanings depending on<br>whether they are read or written. |

(Continued)

|     | Mnemonic | #  | cycles | В      | Operation                         | LH | AH | I | S | Т | Ν | Ζ | ۷ | С | RMW |

|-----|----------|----|--------|--------|-----------------------------------|----|----|---|---|---|---|---|---|---|-----|

| XCH | A, ear   | 2  | 3      | 0      | byte (A) $\leftrightarrow$ (ear)  | Ζ  | _  | _ | - | - | - | - | - | _ | -   |

| XCH | A, eam   | 2+ | 3+ (a) | 2×(b)  | byte (A) $\leftrightarrow$ (eam)  | Z  | —  | _ | — | _ | _ | _ | _ | — | -   |

| XCH | Ri, ear  | 2  | 4      | 0      | byte (Ri) $\leftrightarrow$ (ear) | -  | —  | _ | — | — | _ | — | _ | _ | -   |

| XCH | Ri, eam  | 2+ | 5+ (a) | 2× (b) | byte (Ri) $\leftrightarrow$ (eam) | -  | —  | - | - | - | - | - | - | _ | -   |

For an explanation of "(a)" and "(b)", refer to Table 4, "Number of Execution Cycles for Each Form of Addressing," and Table 5, "Correction Values for Number of Cycles Used to Calculate Number of Actual Cycles."

| Mnemonic                 | #       | cycles   | В       | Operation                                                                                                                                                                                                                                                                                                                                                                                                                                                 | LH | AH | I | S | Т | Ν | Ζ | ۷ | С   | RMW |

|--------------------------|---------|----------|---------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|----|---|---|---|---|---|---|-----|-----|

| DIV A                    | 2       | *1       | 0       | word (AH) /byte (AL)                                                                                                                                                                                                                                                                                                                                                                                                                                      | Ζ  | _  | _ | _ | - | _ | _ | * | *   | -   |

| DIV A, ear               | 2       | *2       | 0       | Quotient $\rightarrow$ byte (AL) Remainder $\rightarrow$ byte (AH)<br>word (A)/byte (ear)<br>Quotient $\rightarrow$ byte (A) Remainder $\rightarrow$ byte (ear)                                                                                                                                                                                                                                                                                           | z  | _  | _ | _ | _ | _ | _ | * | *   | _   |

| DIV A, eam               | 2+      | *3       | *6      | word (A)/byte (eam)                                                                                                                                                                                                                                                                                                                                                                                                                                       | Ζ  | _  | _ | _ | - | _ | _ | * | *   | -   |

| DIVWA, ear<br>DIVWA, eam | 2<br>2+ | *4<br>*5 | 0<br>*7 | $\begin{array}{l} \mbox{Quotient} \rightarrow \mbox{byte (A)} \ \mbox{Remainder} \rightarrow \mbox{byte (eam)} \\ \mbox{long (A)/word (ear)} \\ \mbox{Quotient} \rightarrow \mbox{word (A)} \ \mbox{Remainder} \rightarrow \mbox{word (ear)} \\ \mbox{Quotient} \rightarrow \mbox{word (A)} \ \mbox{Remainder} \rightarrow \mbox{word (eam)} \\ \mbox{Quotient} \rightarrow \mbox{word (A)} \ \mbox{Remainder} \rightarrow \mbox{word (eam)} \end{array}$ | _  | _  |   | _ | _ | _ | _ | * | * * | -   |

| MUL A                    | 2       | *8       | 0       | byte (AH) $\times$ byte (AL) $\rightarrow$ word (A)                                                                                                                                                                                                                                                                                                                                                                                                       | _  | _  | _ | _ | - | _ | _ | _ | _   | -   |

| MUL A, ear               | 2       | *9       | 0       | byte (A) $\times$ byte (ear) $\rightarrow$ word (A)                                                                                                                                                                                                                                                                                                                                                                                                       | —  | —  | — | — | - | — | — | — | —   | —   |

| MUL A, eam               | 2+      | *10      | (b)     | byte (A) $\times$ byte (eam) $\rightarrow$ word (A)                                                                                                                                                                                                                                                                                                                                                                                                       | -  | —  | — | — | - | — | — | — | —   | —   |

| MULW A                   | 2       | *11      | 0       | word (AH) $\times$ word (AL) $\rightarrow$ long (A)                                                                                                                                                                                                                                                                                                                                                                                                       | -  | —  | — | — | - | — | — | — | —   | —   |

| MULW A, ear              | 2       | *12      | 0       | word (A) $\times$ word (ear) $\rightarrow$ long (A)                                                                                                                                                                                                                                                                                                                                                                                                       | -  | —  | — | — | - | — | — | — | —   | —   |

| MULW A, eam              | 2+      | *13      | (b)     | word (A) $\times$ word (eam) $\rightarrow$ long (A)                                                                                                                                                                                                                                                                                                                                                                                                       | -  | -  | - | - | - | - | - | - | -   | -   |

#### Table 13 Signed Multiplication and Division Instructions (Word/Long Word) [11 Insturctions]

For an explanation of "(b)" and "(c)", refer to Table 5, "Correction Values for Number of Cycles Used to Calculate Number of Actual Cycles."

- \*1: 3 when dividing into zero, 8 or 18 when an overflow occurs, and 18 normally.

- \*2: 3 when dividing into zero, 10 or 21 when an overflow occurs, and 22 normally.

- \*3: 4 + (a) when dividing into zero, 11 + (a) or 22 + (a) when an overflow occurs, and 23 + (a) normally.

- \*4: When the dividend is positive: 4 when dividing into zero, 10 or 29 when an overflow occurs, and 30 normally. When the dividend is negative: 4 when dividing into zero, 11 or 30 when an overflow occurs, and 31 normally.

- \*5: When the dividend is positive: 4 + (a) when dividing into zero, 11 + (a) or 30 + (a) when an overflow occurs, and 31 + (a) normally.

When the dividend is negative: 4 + (a) when dividing into zero, 12 + (a) or 31 + (a) when an overflow occurs, and 32 + (a) normally.

- \*6: (b) when dividing into zero or when an overflow occurs, and  $2 \times (b)$  normally.

- \*7: (c) when dividing into zero or when an overflow occurs, and  $2 \times$  (c) normally.

- \*8: 3 when byte (AH) is zero, 12 when the result is positive, and 13 when the result is negative.

- \*9: 3 when byte (ear) is zero, 12 when the result is positive, and 13 when the result is negative.

- \*10: 4 + (a) when byte (eam) is zero, 13 + (a) when the result is positive, and 14 + (a) when the result is negative.

- \*11: 3 when word (AH) is zero, 12 when the result is positive, and 13 when the result is negative.

- \*12: 3 when word (ear) is zero, 16 when the result is positive, and 19 when the result is negative.

- \*13: 4 + (a) when word (eam) is zero, 17 + (a) when the result is positive, and 20 + (a) when the result is negative.

- Note: Which of the two values given for the number of execution cycles applies when an overflow error occurs in a DIV or DIVW instruction depends on whether the overflow was detected before or after the operation.

| Mn           | emonic           | #       | cycles      | В        | Operation                                                                  | LH     | AH | I | S      | Т | Ν | Ζ | ۷      | С | RMW |

|--------------|------------------|---------|-------------|----------|----------------------------------------------------------------------------|--------|----|---|--------|---|---|---|--------|---|-----|

| ANDL<br>ANDL | A, ear<br>A, eam | 2<br>2+ | 5<br>6+ (a) |          | long (A) $\leftarrow$ (A) and (ear)<br>long (A) $\leftarrow$ (A) and (eam) |        |    | _ | -      | - | * | * | R<br>R | - |     |

| ORL<br>ORL   | A, ear<br>A, eam | 2<br>2+ | 5<br>6+ (a) |          | long (A) $\leftarrow$ (A) or (ear)<br>long (A) $\leftarrow$ (A) or (eam)   | _<br>_ | -  | _ | _      | - | * | * | R<br>R |   |     |

| XORL<br>XORL | A, ear<br>A, eam | 2<br>2+ | 5<br>6+ (a) | 0<br>(d) | long (A) $\leftarrow$ (A) xor (ear)<br>long (A) $\leftarrow$ (A) xor (eam) | _<br>_ | -  | _ | _<br>_ |   | * | * | R<br>R |   |     |

Table 15 Logical 2 Instructions (Long Word) [6 Instructions]

For an explanation of "(a)" and "(d)", refer to Table 4, "Number of Execution Cycles for Each Form of Addressing," and Table 5, "Correction Values for Number of Cycles Used to Calculate Number of Actual Cycles."

| Table 16 | Sign Inversion | Instructions | (Byte/Word) | [6 Instructions] |

|----------|----------------|--------------|-------------|------------------|

|----------|----------------|--------------|-------------|------------------|

| Mn           | emonic     | #       | cycles      | В           | Operation                                                              | LH | AH     | I | S      | Т      | Ν   | Ζ   | ۷   | С   | RMW |

|--------------|------------|---------|-------------|-------------|------------------------------------------------------------------------|----|--------|---|--------|--------|-----|-----|-----|-----|-----|

| NEG          | А          | 1       | 2           | 0           | byte (A) $\leftarrow$ 0 – (A)                                          | Х  | _      | - | _      | _      | *   | *   | *   | *   | _   |

| NEG<br>NEG   | ear<br>eam | 2<br>2+ | 2<br>3+ (a) |             | byte (ear) $\leftarrow$ 0 – (ear)<br>byte (eam) $\leftarrow$ 0 – (eam) | -  | _<br>_ | - |        | _<br>_ | *   | *   | *   | *   | *   |

| NEGW         | А          | 1       | 2           | 0           | word (A) $\leftarrow$ 0 – (A)                                          | -  | -      | Ι | -      | -      | *   | *   | *   | *   | _   |

| NEGW<br>NEGW |            | 2<br>2+ | 2<br>3+ (a) | 0<br>2× (c) | word (ear) $\leftarrow$ 0 – (ear)<br>word (eam) $\leftarrow$ 0 – (eam) | -  | _<br>_ |   | _<br>_ | _<br>_ | * * | * * | * * | * * | *   |

For an explanation of "(a)", "(b)" and "(c)" and refer to Table 4, "Number of Execution Cycles for Each Form of Addressing," and Table 5, "Correction Values for Number of Cycles Used to Calculate Number of Actual Cycles."

| Table 17 | Absolute Value Instructions | (Byte/Word/Long | Word) [3 Insturctions] |

|----------|-----------------------------|-----------------|------------------------|

|----------|-----------------------------|-----------------|------------------------|

| Mnemonic | # | cycles | В | Operation                                | LH | AH | Ι | S | Т | Ν | Ζ | ۷ | С | RMW |

|----------|---|--------|---|------------------------------------------|----|----|---|---|---|---|---|---|---|-----|

| ABS A    | 2 | 2      | 0 | byte (A) $\leftarrow$ absolute value (A) | Ζ  | -  | - | _ | Ι | * | * | * | - | _   |

| ABSW A   | 2 | 2      | 0 | word $(A) \leftarrow absolute value (A)$ | _  | —  | _ | _ | — | * | * | * | _ | -   |

| ABSL A   | 2 | 4      | 0 | long $(A) \leftarrow absolute value (A)$ | —  | -  | - | — | - | * | * | * | — | -   |

| Table 18 | Normalize Instructions | (Long Word) [ˈ | 1 Instruction] |

|----------|------------------------|----------------|----------------|

|----------|------------------------|----------------|----------------|

| Mnem   | onic  | # | cycles | В | Operation                                                                                                          | LH | AH | I | S | Т | Ν | Ζ | ۷ | С | RMW |

|--------|-------|---|--------|---|--------------------------------------------------------------------------------------------------------------------|----|----|---|---|---|---|---|---|---|-----|

| NRML / | A, R0 | 2 | *      |   | long (A) $\leftarrow$ Shifts to the position at which "1" was set first byte (R0) $\leftarrow$ current shift count | -  | Ι  | - | - | * | _ | _ | - | - | _   |

\*: 5 when the contents of the accumulator are all zeroes, 5 + (R0) in all other cases.

| Mnemonic      | #  | cycles | В      | Operation                                                      | LH | AH | Ι | S | Т | Ν | Ζ | V | С | RMW |

|---------------|----|--------|--------|----------------------------------------------------------------|----|----|---|---|---|---|---|---|---|-----|

| RORC A        | 2  | 2      | 0      | byte (A) $\leftarrow$ Right rotation with carry                | _  | _  | - | — | _ | * | * | - | * | —   |

| ROLC A        | 2  | 2      | 0      | byte (A) $\leftarrow$ Left rotation with carry                 | -  | -  | - | - | - | * | * | - | * | -   |

| RORC ear      | 2  | 2      | 0      | byte (ear) $\leftarrow$ Right rotation with carry              | _  | _  | _ | _ | _ | * | * | _ | * | *   |

| RORC eam      | 2+ |        |        | byte (eam) $\leftarrow$ Right rotation with carry              | -  | -  | - | - | - | * | * | - | * | *   |

| ROLC ear      | 2  | 2      | 0      | byte (ear) $\leftarrow$ Left rotation with carry               | -  | -  | - | - | - | * | * | - | * | *   |

| ROLC eam      | 2+ | 3+ (a) | 2× (b) | byte (eam) $\leftarrow$ Left rotation with carry               | _  | _  | _ | _ | _ |   |   | _ |   |     |

| ASR A, R0     | 2  | *1     | 0      | byte (A) $\leftarrow$ Arithmetic right barrel shift (A, R0)    | _  | _  | — | _ | * | * | * | _ | * | -   |

| LSR A, RO     | 2  | *1     | 0      | byte (A) $\leftarrow$ Logical right barrel shift (A, R0)       | -  | -  | - | - | * | * | * | - | * | -   |

| LSL A, R0     | 2  | *1     | 0      | byte (A) $\leftarrow$ Logical left barrel shift (A, R0)        | _  | _  | - | - | _ | ~ | ^ | _ | ~ | -   |

| ASR A, #imm8  | 3  | *3     | 0      | byte (A) $\leftarrow$ Arithmetic right barrel shift (A, imm8)  | _  | _  | — | _ | * | * | * | _ | * | -   |

| LSR A, #imm8  | 3  | *3     | 0      | byte (A) $\leftarrow$ Logical right barrel shift (A, imm8)     | -  | -  | - | - | * | * | * | - | * | -   |

| LSL A, #imm8  | 3  | *3     | 0      | byte (A) $\leftarrow$ Logical left barrel shift (A, imm8)      | -  | -  | - | - | - | * | * | - | * | -   |

| ASRW A        | 1  | 2      | 0      | word (A) $\leftarrow$ Arithmetic right shift (A, 1 bit)        | _  | —  | — | — | * | * | * | - | * | —   |

| LSRW A/SHRW A | 1  | 2<br>2 | 0      | word $(A) \leftarrow$ Logical right shift $(A, 1 \text{ bit})$ | -  | -  | - | - | * | R | * | - | * | -   |

| LSLW A/SHLW A | 1  | 2      | 0      | word (A) $\leftarrow$ Logical left shift (A, 1 bit)            | _  | _  | _ | _ | _ |   |   | _ |   | -   |

| ASRW A, R0    | 2  | *1     | 0      | word (A) $\leftarrow$ Arithmetic right barrel shift (A, R0)    | _  | _  | _ | _ | * | * | * | _ | * | _   |

| LSRW A, RO    | 2  | *1     | 0      | word (A) $\leftarrow$ Logical right barrel shift (A, R0)       | -  | -  | - | - | * | * | * | - | * | -   |

| LSLW A, R0    | 2  | *1     | 0      | word (A) $\leftarrow$ Logical left barrel shift (A, R0)        | _  | -  | - | - | - | ^ | ^ | _ | ^ | -   |

| ASRW A, #imm8 | 3  | *3     | 0      | word (A) $\leftarrow$ Arithmetic right barrel shift (A, imm8)  | _  | _  | _ | _ | * | * | * | _ | * | _   |

| LSRW A, #imm8 | 3  | *3     | 0      | word (A) $\leftarrow$ Logical right barrel shift (A, imm8)     | —  | -  | - | - | * | * | * | - | * | -   |

| LSLW A, #imm8 | 3  | *3     | 0      | word (A) $\leftarrow$ Logical left barrel shift (A, imm8)      | —  | —  |   | — | — | * | * | - | * | -   |

| ASRL A, R0    | 2  | *2     | 0      | long (A) $\leftarrow$ Arithmetic right shift (A, R0)           | _  | Ι  | _ | - | * | * | * | - | * | —   |

| LSRL A, R0    | 2  | *2     | 0      | long (A) $\leftarrow$ Logical right barrel shift (A, R0)       | -  | -  | - | - | * | * | * | - | * | —   |

| LSLL A, R0    | 2  | *2     | 0      | long (A) $\leftarrow$ Logical left barrel shift (A, R0)        | -  | -  | - | — | - | * | * | - | * | —   |

| ASRL A, #imm8 | 3  | *4     | 0      | long (A) $\leftarrow$ Arithmetic right shift (A, imm8)         | _  | _  | _ | _ | * | * | * | _ | * | _   |

| LSRL A, #imm8 | 3  | *4     | 0      | long (A) $\leftarrow$ Logical right barrel shift (A, imm8)     | -  | _  | _ | - | * | * | * | - | * | —   |

| LSLL A, #imm8 | 3  | *4     | 0      | long (A) $\leftarrow$ Logical left barrel shift (A, imm8)      | -  | -  | — | - | - | * | * | - | * | -   |

| Table 19 | Shift Instructions | (Byte/Word/Long Word) | [27 Instructions] |

|----------|--------------------|-----------------------|-------------------|

|----------|--------------------|-----------------------|-------------------|

For an explanation of "(a)" and "(b)", refer to Table 4, "Number of Execution Cycles for Each Form of Addressing," and Table 5, "Correction Values for Number of Cycles Used to Calculate Number of Actual Cycles."

\*1: 3 when R0 is 0, 3 + (R0) in all other cases.

\*2: 3 when R0 is 0, 4 + (R0) in all other cases.

\*3: 3 when imm8 is 0, 3 + (imm8) in all other cases.

\*4: 3 when imm8 is 0, 4 + (imm8) in all other cases.

| Mnemonic        | #  | cycles | В              | Operation                                                                | LH | AH | I | S | Т | Ν | Ζ | V | С | RMW |

|-----------------|----|--------|----------------|--------------------------------------------------------------------------|----|----|---|---|---|---|---|---|---|-----|

| BZ/BEQ rel      | 2  | *1     | 0              | Branch when (Z) = 1                                                      | _  | _  |   | Ι | _ | _ | Ι | _ |   | _   |

| BNZ/BNE rel     | 2  | *1     | 0              | Branch when $(Z) = 0$                                                    | _  | —  | _ | _ | - | — | — | — | _ | —   |

| BC/BLO rel      | 2  | *1     | 0              | Branch when $(C) = 1$                                                    | _  | —  | _ | — | - | - | — | — | — | —   |

| BNC/BHS rel     | 2  | *1     | 0              | Branch when $(C) = 0$                                                    | _  | _  | _ | — | — | — | — | — | — | —   |

| BN rel          | 2  | *1     | 0              | Branch when $(N) = 1$                                                    | _  | —  | — | — | - | — | — | — | — | —   |

| BP rel          | 2  | *1     | 0              | Branch when $(N) = 0$                                                    | _  | —  | _ | — | - | - | — | — | — | —   |

| BV rel          | 2  | *1     | 0              | Branch when $(V) = 1$                                                    | _  | —  | _ | — | - | - | _ | — | — | —   |

| BNV rel         | 2  | *1     | 0              | Branch when $(V) = 0$                                                    | _  | _  | _ | _ | - | — | — | — | — | —   |

| BT rel          | 2  | *1     | 0              | Branch when $(T) = 1$                                                    | _  | _  | _ | _ | - | — | — | — | _ | —   |

| BNT rel         | 2  | *1     | 0              | Branch when $(T) = 0$                                                    | _  | _  | _ | _ | - | — | _ | — | _ | —   |

| BLT rel         | 2  | *1     | 0              | Branch when $(V)$ xor $(N) = 1$                                          | _  | —  | _ | _ | — | - | — | — | — | —   |

| BGE rel         | 2  | *1     | 0              | Branch when $(V)$ xor $(N) = 0$                                          | _  | —  | _ | _ | — | — | — | — | _ | —   |

| BLE rel         | 2  | *1     | 0              | ((V)  xor  (N))  or  (Z) = 1                                             | _  | —  | _ | _ | - | — | _ | — | _ | —   |

| BGT rel         | 2  | *1     | 0              | $(\dot{V})$ xor $\dot{N}$ $\dot{V}$ or $\dot{Z}$ = 0                     | _  | _  | _ | _ | — | — | _ | — | _ | —   |

| BLS rel         | 2  | *1     | 0              | Branch when $(C)$ or $(Z) = 1$                                           | _  | _  | _ | _ | — | — | _ | — | _ | —   |

| BHI rel         | 2  | *1     | 0              | Branch when $(C)$ or $(Z) = 0$                                           | _  | _  | _ | _ | - | — | _ | — | _ | —   |

| BRA rel         | 2  | *1     | 0              | Branch unconditionally                                                   | —  | -  | - | - | - | - | - | — | - | -   |

| JMP @A          | 1  | 2      | 0              | word (PC) $\leftarrow$ (A)                                               | _  | _  | _ | _ | _ | _ | _ | _ | _ | _   |

| JMP addr16      | 3  | 2      | 0              | word (PC) $\leftarrow$ addr16                                            | _  | _  | _ | _ | - | _ | _ | _ | _ | —   |

| JMP @ear        | 2  | 3      | 0              | word (PC) $\leftarrow$ (ear)                                             | _  | _  | _ | _ | — | _ | _ | — | _ | —   |

| JMP @eam        | 2+ | 4+ (a) | (c)            | word (PC) $\leftarrow$ (eam)                                             | _  | _  | _ | _ | — | _ | _ | — | _ | —   |

| JMPP @ear *3    | 2  | 3      | )<br>O         | word (PC) $\leftarrow$ (ear), (PCB) $\leftarrow$ (ear +2)                | _  | _  | _ | _ | — | — | _ | — | _ | —   |

| JMPP @eam *3    | 2+ | 4+ (a) | (d)            | word (PC) $\leftarrow$ (eam), (PCB) $\leftarrow$ (eam +2)                | _  | _  | _ | _ | — | _ | _ | — | _ | —   |

| JMPP addr24     | 4  | 3      | )<br>O         | word (PC) $\leftarrow$ ad24 0 to 15                                      | _  | _  | _ | _ | — | _ | _ | — | _ | —   |

|                 |    |        |                | (PCB) ← ad24 16 to 23                                                    |    |    |   |   |   |   |   |   |   |     |

| CALL @ear *4    | 2  | 4      | (c)            | word (PC) $\leftarrow$ (ear)                                             | _  | _  | _ | _ | — | _ | _ | — | _ | —   |

| CALL @eam *4    | 2+ | 5+ (a) | $2 \times (c)$ | word (PC) $\leftarrow$ (eam)                                             | _  | _  | _ | _ | — | _ | _ | — | _ | —   |

| CALL addr16 *5  | 3  | 5      | (c)            | word (PC) $\leftarrow$ addr16                                            | _  | —  | _ | _ | - | — | _ | — | _ | —   |

| CALLV #vct4 *5  | 1  | 5      | $2 \times (c)$ | Vector call linstruction                                                 | _  | _  | _ | _ | — | _ | _ | — | _ | _   |

| CALLP @ear *6   | 2  | 7      | $2 \times (c)$ | word (PC) $\leftarrow$ (ear) 0 to 15,                                    | _  | _  | _ | _ | - | _ | _ | — | _ | _   |

|                 |    |        | . ,            | $(PCB) \leftarrow (ear) \ 16 \ to \ 23$                                  |    |    |   |   |   |   |   |   |   |     |

| CALLP @eam *6   | 2+ | 8+ (a) | *2             | word (PC) $\leftarrow$ (eam) 0 to 15,                                    | —  | -  | _ | _ | - | - | — | _ | — | -   |

|                 |    |        |                | (PCB) ← (eam) 16 to 23                                                   |    |    |   |   |   |   |   |   |   |     |

| CALLP addr24 *7 | 4  | 7      | 2× (c)         | word (PC) $\leftarrow$ addr 0 to 15,<br>(PCB) $\leftarrow$ addr 16 to 23 | -  | -  | - | - | - | - | - | - | - | -   |

| Table 20 | Branch 1 Instructions | [31 Instructions] |

|----------|-----------------------|-------------------|

|----------|-----------------------|-------------------|

For an explanation of "(a)", "(c)" and "(d)", refer to Table 4, "Number of Execution Cycles for Each Form of Addressing," and Table 5, "Correction Values for Number of Cycles Used to Calculate Number of Actual Cycles."

- \*1: 3 when branching, 2 when not branching.

- \*2: 3 × (c) + (b)

- \*3: Read (word) branch address.

- \*4: W: Save (word) to stack; R: Read (word) branch address.

- \*5: Save (word) to stack.