Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Purchase URL               | https://www.e-xfl.com/product-detail/infineon-technologies/mb90224pf-gt-370e1 |

|----------------------------|-------------------------------------------------------------------------------|

| Supplier Device Package    | 120-QFP (28x28)                                                               |

| Package / Case             | 120-BQFP                                                                      |

| Mounting Type              | Surface Mount                                                                 |

| Operating Temperature      | -40°C ~ 105°C (TA)                                                            |

| Oscillator Type            | External                                                                      |

| Data Converters            | A/D 16x10b                                                                    |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 5.5V                                                                     |

| RAM Size                   | 4.5K x 8                                                                      |

| EEPROM Size                | -                                                                             |

| Program Memory Type        | Mask ROM                                                                      |

| Program Memory Size        | 96KB (96K x 8)                                                                |

| Number of I/O              | 102                                                                           |

| Peripherals                | POR, PWM, WDT                                                                 |

| Connectivity               | EBI/EMI, UART/USART                                                           |

| Speed                      | 16MHz                                                                         |

| Core Size                  | 16-Bit                                                                        |

| Core Processor             | F <sup>2</sup> MC-16F                                                         |

| Product Status             | Obsolete                                                                      |

| Details                    |                                                                               |

| Pin no.<br>QFP* | Pin name     | Circuit type | Function                                                                                                                                                                                                                                                                                                             |

|-----------------|--------------|--------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 12 to 16        | INT3 to INT7 | С            | External interrupt request input pins When external interrupts are enabled, these inputs may be used suddenly at any time; therefore, it is necessary to stop output by other functions on these pins, except when using them for output deliberately.                                                               |

| 78              | 78 P50 C     |              | General-purpose I/O port This function is valid in single-chip mode and when the CLK output specification is disabled.                                                                                                                                                                                               |

|                 | CLK          |              | CLK output pin This function is valid in modes where the external bus is enabled and the CLK output specification is enabled.                                                                                                                                                                                        |

| 79              | P51          | С            | General-purpose I/O port This function is valid in single-chip mode or when the ready function is disabled.                                                                                                                                                                                                          |

|                 | RDY          |              | Ready input pin This function is valid in modes where the external bus is enabled and the ready function is enabled.                                                                                                                                                                                                 |

| 80              | P52          | С            | General-purpose I/O port This function is valid in single-chip mode or when the hold function is disabled.                                                                                                                                                                                                           |

|                 | HAK          |              | Hold acknowledge output pin This function is valid in modes where the external bus is enabled and the hold function is enabled.                                                                                                                                                                                      |

| 81              | P53          | С            | General-purpose I/O port This function is valid in single-chip mode or external bus mode and when the hold function is disabled.                                                                                                                                                                                     |

|                 | HRQ          |              | Hold request input pin This function is valid in modes where the external bus is enabled and the hold function is enabled. During this operation, the input may be used suddenly at any time; therefore, it is necessary to stop output by other fuctions on this pin, except when using it for output deliberately. |

| 82              | P54          | С            | General-purpose I/O port This function is valid in single-chip mode, when the external bus is in 8-bit mode, or when WRH pin output is disabled.                                                                                                                                                                     |

|                 | WRH          |              | Write strobe output pin for the high-order 8 bits of the data bus This function is valid in modes where the external bus is enabled, the external bus is in 16-bit mode, and WRH pin output is enabled.                                                                                                              |

| 83              | P55          | С            | General-purpose I/O port This function is valid in single-chip mode or when $\overline{WRL}$ pin output is disabled.                                                                                                                                                                                                 |

|                 | WRL          |              | Write strobe output pin for the low-order 8 bits of the data bus This function is valid in modes where the external bus is enabled and WRL pin output is enabled.                                                                                                                                                    |

<sup>\*:</sup> FPT-120P-M03, FPT-120C-C02

#### (Continued)

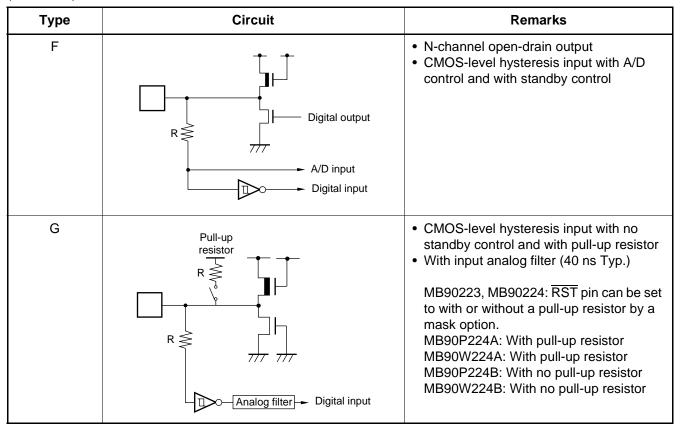

☐ ⊢ : P-type transistor ☐ ⊢ : N-type transistor

Note: The pull-up and pull-down resistors are always connected, regardless of the state.

#### 3. EPROM Programmer Socket Adapter and Recommended Programmer Manufacturer

| Part No.                                                |                 |                                                    | MB90P224B          |

|---------------------------------------------------------|-----------------|----------------------------------------------------|--------------------|

| Package                                                 | QFP-120         |                                                    |                    |

| Compatible sock<br>Sun Hayato Co.,                      | -               |                                                    | ROM-120QF-32DP-16F |

| Recommended programmer manufacturer and programmer name | Advantest corp. | R4945A<br>(main unit)<br>+<br>R49451A<br>(adapter) | Recommended        |

Inquiry: Sun Hayato Co., Ltd.: TEL: (81)-3-3986-0403

FAX: (81)-3-5396-9106

Advantest Corp.: TEL: Except JAPAN (81)-3-3930-4111

#### 4. Erase Procedure

Data written in the MB90W224A/W224B is erased (from "0" to "1") by exposing the chip to ultraviolet rays with a wavelength of 2,537 Å through the translucent cover.

Recommended irradiation dosage for exposure is 10 Wsec/cm<sup>2</sup>. This amount is reached in 15 to 20 minutes with a commercial ultraviolet lamp positioned 2 to 3 cm above the package (when the package surface illuminance is  $1200 \, \mu \text{W/cm}^2$ ).

If the ultraviolet lamp has a filter, remove the filter before exposure. Attaching a mirrored plate to the lamp increases the illuminance by a factor of 1.4 to 1.8, thus shortening the required erasure time. If the translucent part of the package is stained with oil or adhesive, transmission of ultraviolet rays is degraded, resulting in a longer erasure time. In that case, clean the translucent part using alcohol (or other solvent not affecting the package).

The above recommended dosage is a value which takes the guard band into consideration and is a multiple of the time in which all bits can be evaluated to have been erased. Observe the recommended dosage for erasure; the purpose of the guard band is to ensure erasure in all temperature and supply voltage ranges. In addition, check the life span of the lamp and control the illuminance appropriately.

Data in the MB90W224A/W224B is erased by exposure to light with a wavelength of 4,000 Å or less.

Data in the device is also erased even by exposure to fluorescent lamp light or sunlight although the exposure results in a much lower erasure rate than exposure to 2,537 Å ultraviolet rays. Note that exposure to such lights for an extended period will therefore affect system reliability. If the chip is used where it is exposed to any light with a wavelength of 4,000 Å or less, cover the translucent part, for example, with a protective seal to prevent the chip from being exposed to the light.

Exposure to light with a wavelength of 4,000 to 5,000 Å or more will not erase data in the device. If the light applied to the chip has a very high illuminance, however, the device may cause malfunction in the circuit for reasons of general semiconductor characteristics. Although the circuit will recover normal operation when exposure is stopped, the device requires proper countermeasures for use in a place exposed continuously to such light even though the wavelength is 4,000 Å or more.

| Address | Register                         | Register name | Access | Resouce name             | Initial value |

|---------|----------------------------------|---------------|--------|--------------------------|---------------|

| 001F28н | OCU compare lower-order data     | CPR06L        |        |                          | 0000000       |

| 001F29н | register 06                      | CPRUOL        | R/W    | Output                   | 0000000       |

| 001F2Aн | OCU compare higher-order data    | CPR06         | IN/ VV | compare 12               | 0000000       |

| 001F2Bн | register 06                      | CFR00         |        |                          | 0000000       |

| 001F2Cн | OCU compare lower-order data     | CPR07L        |        |                          | 0000000       |

| 001F2Dн | register 07                      | CFRUIL        | R/W    | Output                   | 0000000       |

| 001F2Ен | OCU compare higher-order data    | CPR07         | IN/ VV | compare 13               | 0000000       |

| 001F2Fн | register 07                      | CPRUI         |        |                          | 0000000       |

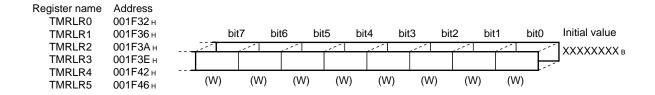

| 001F30н | 16-bit timer register 0          | TMR0          | R      |                          | XXXXXXX       |

| 001F31н | To-bit timer register o          | TIVIKU        | K      | 16-bit reload            | XXXXXXX       |

| 001F32н | 16 hit relead register 0         | TMRLR0        | W      | timer 0                  | XXXXXXX       |

| 001F33н | - 16-bit reload register 0       | TIVIRLE       | VV     |                          | XXXXXXX       |

| 001F34н | 10 hit times a register 1        | TMR1          | 6      |                          | XXXXXXX       |

| 001F35н | 16-bit timer register 1          | TIVIKT        | R      | 16-bit reload<br>timer 1 | XXXXXXX       |

| 001F36н | 16 hit times relead register 1   | TMRLR1        | W      |                          | XXXXXXX       |

| 001F37н | - 16-bit timer reload register 1 |               |        |                          | XXXXXXX       |

| 001F38н | 16 hit timer register 2          | TMR2          | R      | 16-bit reload            | XXXXXXX       |

| 001F39н | 16-bit timer register 2          | IIVIKZ        |        |                          | XXXXXXX       |

| 001F3Ан | 16 hit times relead register 2   | TMDI DO       | 107    | timer 2                  | XXXXXXX       |

| 001F3Вн | 16-bit timer reload register 2   | TMRLR2        | W      |                          | XXXXXXX       |

| 001F3Сн | 16 hit timer register 2          | TMD2          | D      |                          | XXXXXXX       |

| 001F3Dн | - 16-bit timer register 3        | TMR3          | R      | 16-bit reload            | XXXXXXX       |

| 001F3Ен | 10 hit times relead register 2   | TMDI Do       | 107    | timer 3                  | XXXXXXX       |

| 001F3Fн | 16-bit timer reload register 3   | TMRLR3        | W      |                          | XXXXXXX       |

| 001F40н | 40 hit time an arrivate at 4     | TMD 4         |        |                          | XXXXXXX       |

| 001F41н | 16-bit timer register 4          | TMR4          | R      | 16-bit reload            | XXXXXXX       |

| 001F42н | 16 bit timer relead register 4   | TMDI D4       | \^/    | timer 4                  | XXXXXXXX      |

| 001F43н | - 16-bit timer reload register 4 | TMRLR4        | W      |                          | XXXXXXXX      |

| 001F44н | 16 hit timer register 5          | TMDE          | D.     |                          | XXXXXXX       |

| 001F45н | - 16-bit timer register 5        | ister 5 TMR5  | R      | 16-bit reload            | XXXXXXXX      |

| 001F46н | 40 hit times relead to a list of | TMDIDE        | 107    | timer 0                  | XXXXXXX       |

| 001F47н | 16-bit timer reload register 5   | TMRLR5        | W      |                          | XXXXXXX       |

# ■ INTERRUPT SOURCES AND INTERRUPT VECTORS/INTERRUPT CONTROL REGISTERS

| Interrupt source                                                  | El <sup>2</sup> OS<br>support | In  | terrup | t vector            | Interrupt control register |         |  |

|-------------------------------------------------------------------|-------------------------------|-----|--------|---------------------|----------------------------|---------|--|

| ·                                                                 | Support                       | N   | Ο.     | Address             | ICR                        | Address |  |

| Reset                                                             | ×                             | #08 | 08н    | FFFFDCH             | _                          | _       |  |

| INT9 instruction                                                  | ×                             | #09 | 09н    | FFFFD8 <sub>H</sub> | _                          | _       |  |

| Exception                                                         | ×                             | #10 | ОАн    | FFFFD4 <sub>H</sub> | _                          | _       |  |

| External interrupt #0                                             | Δ                             | #11 | 0Вн    | FFFFD0 <sub>H</sub> | ICR00                      | 0000В0н |  |

| External interrupt #1                                             | Δ                             | #12 | 0Сн    | FFFFCCH             | ICIXOO                     | ООООВОН |  |

| External interrupt #2                                             | Δ                             | #13 | 0Дн    | FFFFC8 <sub>H</sub> | ICR01                      | 0000В1н |  |

| Input capture 0                                                   | Δ                             | #14 | 0Ен    | FFFFC4 <sub>H</sub> | ICKUI                      | ООООБТН |  |

| PWC0 count completed/overflow                                     | Δ                             | #15 | 0Гн    | FFFFC0 <sub>H</sub> | ICR02                      | 000000  |  |

| PWC1 count completed/overflow/input capture 1                     | Δ                             | #16 | 10н    | FFFFBCH             | ICR02                      | 0000В2н |  |

| PWC2 count completed/overflow/input capture 2                     | Δ                             | #17 | 11н    | FFFFB8 <sub>H</sub> | ICR03                      | 0000ВЗн |  |

| PWC3 count completed/overflow/input capture 3                     | Δ                             | #18 | 12н    | FFFFB4 <sub>H</sub> | ICRUS                      | 0000B3H |  |

| 24-bit timer, overflow                                            | Δ                             | #19 | 13н    | FFFFB0 <sub>H</sub> |                            | 0000В4н |  |

| 24-bit timer, intermediate bit/timebase timer, interval interrupt | Δ                             | #20 | 14н    | FFFFACH             | ICR04                      |         |  |

| Compare 0                                                         | Δ                             | #21 | 15н    | FFFFA8 <sub>H</sub> | ICR05                      | 0000В5н |  |

| Compare 1                                                         | Δ                             | #22 | 16н    | FFFFA4 <sub>H</sub> | 101103                     | 0000B3H |  |

| Compare 2                                                         | Δ                             | #23 | 17н    | FFFFA0 <sub>H</sub> | ICR06                      | 0000В6н |  |

| Compare 3                                                         | Δ                             | #24 | 18н    | FFFF9C <sub>H</sub> | ICIXOO                     |         |  |

| Compare 4/6                                                       | Δ                             | #25 | 19н    | FFFF98 <sub>H</sub> | ICR07                      | 0000В7н |  |

| Compare 5/7                                                       | Δ                             | #26 | 1Ан    | FFFF94 <sub>H</sub> | ICIXO7                     | 0000Б7н |  |

| 16-bit timer 0/1/2, overflow/PPG0                                 | Δ                             | #27 | 1Вн    | FFFF90 <sub>H</sub> | ICR08                      | 0000В8н |  |

| 16-bit timer 3/4/5, overflow/PPG1                                 | Δ                             | #28 | 1Сн    | FFFF8C <sub>H</sub> | ICIXOO                     | ООООВОН |  |

| 10-bit A/D converter count completed                              |                               | #29 | 1Dн    | FFFF88 <sub>H</sub> | ICR09                      | 0000В9н |  |

| UART1 transmission completed                                      | Δ                             | #31 | 1Fн    | FFFF80 <sub>H</sub> | ICR10                      | 0000ВАн |  |

| UART1 reception completed                                         | Δ                             | #32 | 20н    | FFFF7C <sub>H</sub> | ICKTO                      | UUUUDAH |  |

| UART0 (ch.1) transmission completed                               | Δ                             | #33 | 21н    | FFFF78 <sub>H</sub> | ICR11                      | 0000ВВн |  |

| UART0 (ch.2) transmission completed                               | Δ                             | #34 | 22н    | FFFF74 <sub>H</sub> | ICIXII                     | ООООВЬН |  |

| UART0 (ch.1) reception completed                                  | 0                             | #35 | 23н    | FFFF70 <sub>H</sub> | ICR12                      | 000080  |  |

| UART0 (ch.2) reception completed                                  | Δ                             | #36 | 24н    | FFFF6C <sub>H</sub> | IUKIZ                      | 0000ВСн |  |

| UART0 (ch.0) transmission completed                               | 0                             | #37 | 25н    | FFFF68 <sub>H</sub> | ICR13                      | 0000ВДн |  |

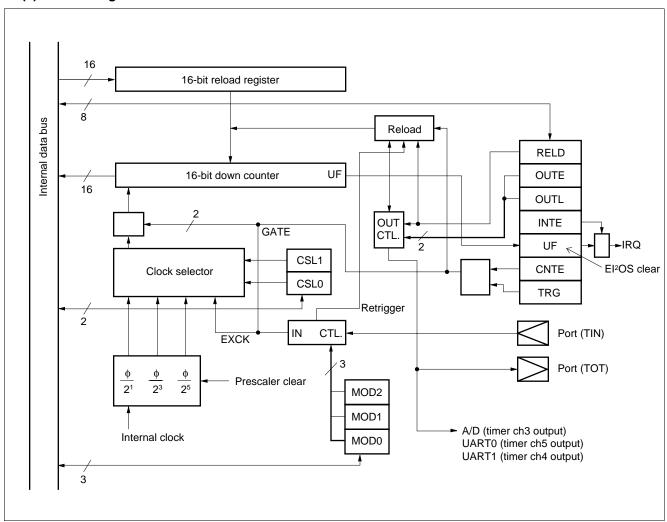

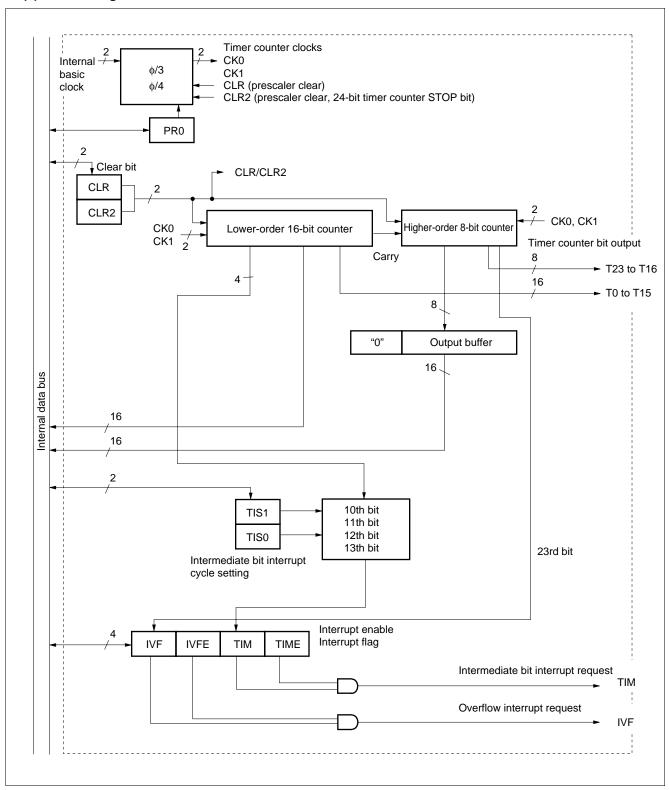

#### (2) Block Diagram

#### (2) Block Diagram

| Parameter         | Symbol                       | Pin name     | Condition     |   | Value |      | Unit  | Remarks      |

|-------------------|------------------------------|--------------|---------------|---|-------|------|-------|--------------|

| Farameter         | Symbol                       | Fili liaille | Min. Typ      |   | Тур.  | Max. | Oilit | Remarks      |

| Analog power      | IA                           | AVcc         | fc = 16 MHz*9 | _ | 3     | 7    | mA    |              |

| supply voltage    | oply voltage I <sub>AH</sub> | AVCC         | _             | _ | _     | 5*6  | μΑ    | At stop mode |

| Input capacitance | Cin                          | *7           | _             |   | 10    | _    | pF    |              |

- \*1: Hysteresis input pins

- RST, HST, P00 to P07, P10 to P17, P20 to P27, P30 to P37, P40 to P47, P50 to P57, P60 to P67, P80 to P87, P90 to P97, PA0 to PA7, PB0 to PB7, PC0 to PC5

- \*2: Ouput pins

P00 to P07, P10 to P17, P20 to P27, P30 to P37, P40 to P47, P50 to P57, P70 to P77, P80 to P87, PA0 to PA7, PB0 to PB7, PC0 to PC5

- \*3: Output pins

P00 to P07, P10 to P17, P20 to P27, P30 to P37, P40 to P47, P50 to P57, P60 to P67, P70 to P77, P80 to P87, P90 to P97, PA0 to PA7, PB0 to PB7, PC0 to PC5

- \*4: A list of availabilities of pull-up/pull-down resistors

| Pin name | MB90223/224                                              | MB90P224A/W224A             | MB90P224B/W224B |

|----------|----------------------------------------------------------|-----------------------------|-----------------|

| RST      | Availability of pull-up resistors is optionally defined. | Pull-up resistors available | Unavailable     |

| MD1      | Pull-up resistors available                              | Unavailable                 | Unavailable     |

| MD0, MD2 | Pull-up resistors available                              | Unavailable                 | Unavailable     |

- \*5: Vcc = +5.0 V, Vss = 0.0 V,  $TA = +25^{\circ}C$ , Fc = 16 MHz

- \*6: The current value applies to the CPU stop mode with A/D converter inactive (Vcc = AVcc = AVRH = +5.5 V).

- \*7: Other than Vcc, Vss, AVcc and AVss

- \*8: Measurement condition of power supply current; external clock pin and output pin are open. Measurement condition of Vcc; see the table above mentioned.

- \*9: Fc = 12 MHz for MB90223

#### 4. AC Characteristics

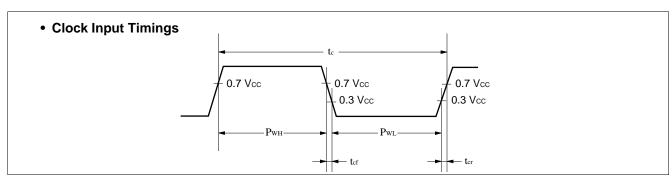

#### (1) Clock Timing Standards

Single-chip mode MB90223/224/P224B/W224B : ( $Vcc = +4.5 \text{ to } +5.5 \text{ V}, Vss = 0.0 \text{ V}, T_A = -40^{\circ}\text{C to } +105^{\circ}\text{C}$ )

MB90P224A/W224A :  $(Vcc = +4.5 \text{ to } +5.5 \text{ V}, Vss = 0.0 \text{ V}, T_A = -40^{\circ}\text{C to } +85^{\circ}\text{C})$

External bus mode :  $(Vcc = +4.5 \text{ to } +5.5 \text{ V}, Vss = 0.0 \text{ V}, T_A = -40^{\circ}\text{C to } +70^{\circ}\text{C})$

| Doromotor                        | Symbol          | mbol Pin Condition Win. Typ. Max |        |        | Unit | Remarks            |       |                                                |

|----------------------------------|-----------------|----------------------------------|--------|--------|------|--------------------|-------|------------------------------------------------|

| Parameter                        | Symbol          |                                  |        | Min.   | Тур. | Max.               | Offic | Remarks                                        |

| Clock frequency                  | Fc              | X0, X1                           | , X1 — |        | _    | 16                 | MHz   | MB90224/<br>P224A/P224B<br>MB90W224A/<br>W224B |

|                                  |                 |                                  |        | 10     | _    | 12                 | MHz   | MB90223                                        |

| Clock cycle time                 | tc              | X0, X1                           | _      | 62.5   | _    | 100                | ns    | MB90224/<br>P224A/P224B<br>MB90W224A/<br>W224B |

|                                  |                 |                                  |        | 83.4   | _    | 100                | ns    | MB90223                                        |

| Input clock pulse width          | Pwh<br>PwL      | X0                               | _      | 0.4 tc | _    | 0.6 t <sub>c</sub> | ns    | Equivalent to 60% duty ratio                   |

| Input clock rising/falling times | t <sub>cr</sub> | X0                               | _      | _      | _    | 8                  | ns    | tor + tof                                      |

$$tc = 1/fc$$

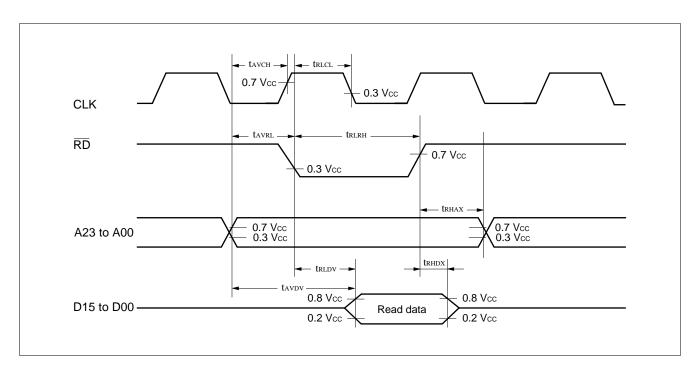

#### (5) Bus Read Timing

$(Vcc = +4.5 \text{ V to } +5.5 \text{ V}, \text{ Vss} = 0.0 \text{ V}, \text{ TA} = -40^{\circ}\text{C to } +70^{\circ}\text{C})$

| Parameter                                                  | Symbol        | Pin name          | Condition           | Va          | lue           | Unit  | Remarks |

|------------------------------------------------------------|---------------|-------------------|---------------------|-------------|---------------|-------|---------|

| Farameter                                                  | Symbol        | Fili Ilalile      | Condition           | Min.        | Max.          | Oilit | Nemarks |

| Valid address $\rightarrow \overline{RD} \downarrow time$  | <b>t</b> avrl | A23 to A00        |                     | tcyc/2 - 20 | _             | ns    |         |

| RD pulse width                                             | trlrh         | RD                |                     | tcyc - 25   | _             | ns    |         |

| $\overline{RD} \downarrow \to Valid$ data input            | <b>t</b> RLDV |                   |                     | _           | tcyc - 30     | ns    |         |

| $\overline{RD} \uparrow \to Data$ hold time                | <b>t</b> RHDX | D15 to D00        | Load                | 0           | _             | ns    |         |

| $\hbox{Valid address} \rightarrow \hbox{Valid data input}$ | <b>t</b> avdv |                   | condition:<br>80 pF | _           | 3 tcyc/2 - 40 | ns    |         |

| $\overline{RD} \!\uparrow \! 	o \! Address$ valid time     | <b>t</b> RHAX | A23 to A00        | ου με               | tcyc/2 - 20 | _             | ns    |         |

| Valid address → CLK ↑ time                                 | <b>t</b> avch | A23 to A00<br>CLK |                     | tcyc/2 - 25 | _             | ns    |         |

| $\overline{RD} \downarrow \to CLK \downarrow time$         | <b>t</b> RLCL | RD, CLK           |                     | tcyc/2 - 25 | _             | ns    |         |

#### ■ INSTRUCTION SET (412 INSTRUCTIONS)

Table 1 Explanation of Items in Table of Instructions

| Item      | Explanation                                                                                                                                                                                                                                                                                                                                                                                                         |

|-----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Mnemonic  | Upper-case letters and symbols: Represented as they appear in assembler Lower-case letters: Replaced when described in assembler. Numbers after lower-case letters: Indicate the bit width within the instruction.                                                                                                                                                                                                  |

| #         | Indicates the number of bytes.                                                                                                                                                                                                                                                                                                                                                                                      |

| ~         | Indicates the number of cycles. See Table 4 for details about meanings of letters in items.                                                                                                                                                                                                                                                                                                                         |

| В         | Indicates the correction value for calculating the number of actual cycles during execution of instruction.  The number of actual cycles during execution of instruction is summed with the value in the "cycles" column.                                                                                                                                                                                           |

| Operation | Indicates operation of instruction.                                                                                                                                                                                                                                                                                                                                                                                 |

| LH        | Indicates special operations involving the bits 15 through 08 of the accumulator.  Z: Transfers "0".  X: Extends before transferring.  —: Transfers nothing.                                                                                                                                                                                                                                                        |

| АН        | Indicates special operations involving the high-order 16 bits in the accumulator.  *: Transfers from AL to AH.  —: No transfer.  Z: Transfers 00H to AH.  X: Transfers 00H or FFH to AH by extending AL.                                                                                                                                                                                                            |

| I         | Indicates the status of each of the following flags: I (interrupt enable), S (stack), T (sticky                                                                                                                                                                                                                                                                                                                     |

| S         | bit), N (negative), Z (zero), V (overflow), and C (carry).  *: Changes due to execution of instruction.                                                                                                                                                                                                                                                                                                             |

| Т         | —: No change.                                                                                                                                                                                                                                                                                                                                                                                                       |

| N         | S: Set by execution of instruction. R: Reset by execution of instruction.                                                                                                                                                                                                                                                                                                                                           |

| Z         |                                                                                                                                                                                                                                                                                                                                                                                                                     |

| V         |                                                                                                                                                                                                                                                                                                                                                                                                                     |

| С         |                                                                                                                                                                                                                                                                                                                                                                                                                     |

| RMW       | Indicates whether the instruction is a read-modify-write instruction (a single instruction that reads data from memory, etc., processes the data, and then writes the result to memory.).  *: Instruction is a read-modify-write instruction  —: Instruction is not a read-modify-write instruction  Note: Cannot be used for addresses that have different meanings depending on whether they are read or written. |

Table 3 Effective Address Fields

| Code                                         | Notation                                                                                                        | Address format                                                                                                | Number of bytes in address extemsion* |

|----------------------------------------------|-----------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------|---------------------------------------|

| 00<br>01<br>02<br>03<br>04<br>05<br>06<br>07 | R0 RW0 RL0 R1 RW1 (RL0) R2 RW2 RL1 R3 RW3 (RL1) R4 RW4 RL2 R5 RW5 (RL2) R6 RW6 RL3 R7 RW7 (RL3)                 | Register direct "ea" corresponds to byte, word, and long-word types, starting from the left                   |                                       |

| 08<br>09<br>0A<br>0B                         | @RW0<br>@RW1<br>@RW2<br>@RW3                                                                                    | Register indirect                                                                                             | 0                                     |

| 0C<br>0D<br>0E<br>0F                         | @ RW0 +<br>@ RW1 +<br>@ RW2 +<br>@ RW3 +                                                                        | Register indirect with post-increment                                                                         | 0                                     |

| 10<br>11<br>12<br>13<br>14<br>15<br>16<br>17 | @ RW0 + disp8 @ RW1 + disp8 @ RW2 + disp8 @ RW3 + disp8 @ RW4 + disp8 @ RW5 + disp8 @ RW6 + disp8 @ RW7 + disp8 | Register indirect with 8-bit displacement                                                                     | 1                                     |

| 18<br>19<br>1A<br>1B                         | @RW0 + disp16<br>@RW1 + disp16<br>@RW2 + disp16<br>@RW3 + disp16                                                | Register indirect with 16-bit displacemen                                                                     | 2                                     |

| 1C<br>1D<br>1E<br>1F                         | @RW0 + RW7<br>@RW1 + RW7<br>@PC + dip16<br>addr16                                                               | Register indirect with index Register indirect with index PC indirect with 16-bit displacement Direct address | 0<br>0<br>2<br>2                      |

<sup>\*:</sup> The number of bytes for address extension is indicated by the "+" symbol in the "#" (number of bytes) column in the Table of Instructions.

Table 4 Number of Execution Cycles for Each Form of Addressing

| Code                 | Operand                                            | (a)*                                                   |

|----------------------|----------------------------------------------------|--------------------------------------------------------|

| Code                 | Operand                                            | Number of execution cycles for each from of addressing |

| 00 to 07             | Ri<br>RWi<br>RLi                                   | Listed in Table of Instructions                        |

| 08 to 0B             | @RWj                                               | 1                                                      |

| 0C to 0F             | @RWj+                                              | 4                                                      |

| 10 to 17             | @RWi + disp8                                       | 1                                                      |

| 18 to 1B             | @RWj + disp16                                      | 1                                                      |

| 1C<br>1D<br>1E<br>1F | @RW0 + RW7<br>@RW1 + RW7<br>@PC + dip16<br>@addr16 | 2<br>2<br>2<br>1                                       |

<sup>\*: &</sup>quot;(a)" is used in the "cycles" (number of cycles) column and column B (correction value) in the Table of Instructions.

Table 5 Correction Values for Number of Cycles Used to Calculate Number of Actual Cycles

| Operand                          | (k | ))* | (0 | <b>;)</b> * | (d)*<br>long |   |  |  |  |

|----------------------------------|----|-----|----|-------------|--------------|---|--|--|--|

| Operand                          | by | /te | wo | ord         |              |   |  |  |  |

| Internal register                | +  | 0   | +  | 0           | +            | 0 |  |  |  |

| Internal RAM even address        | +  | 0   | +  | 0           | +            | 0 |  |  |  |

| Internal RAM odd address         | +  | 0   | +  | 1           | +            | 2 |  |  |  |

| Even address not in internal RAM | +  | 1   | +  | 1           | +            | 2 |  |  |  |

| Odd address not in internal RAM  | +  | 1   | +  | 3           | +            | 6 |  |  |  |

| External data bus (8 bits)       | +  | 1   | +  | 3           | +            | 6 |  |  |  |

<sup>\*: &</sup>quot;(b)", "(c)", and "(d)" are used in the "cycles" (number of cycles) column and column B (correction value) in the Table of Instructions.

Table 7 Transfer Instructions (Word) [40 Instructions]

| Mnemonic                       | #      | cycles | В   | Operation                                                      | LH | АН     | I | s | Т | N | Z | ٧ | С | RMW |

|--------------------------------|--------|--------|-----|----------------------------------------------------------------|----|--------|---|---|---|---|---|---|---|-----|

| MOVW A, dir                    | 2      | 2      | (c) | word (A) $\leftarrow$ (dir)                                    | _  | *      | _ | _ | _ | * | * | _ | _ | _   |

| MOVW A, addr16                 | 3      | 2      | (c) | word (A) ← (addr16)                                            | -  | *      | _ | _ | _ | * | * | _ | - | _   |

| MOVW A, SP                     | 1      | 2      | 0   | word (A) $\leftarrow$ (SP)                                     | -  | *      | _ | _ | _ | * | * | _ | - | _   |

| MOVW A, RWi                    | 1      | 1      | 0   | word (A) $\leftarrow$ (RWi)                                    | -  | *      | _ | _ | _ | * | * | _ | _ | _   |

| MOVW A, ear                    | 2      | 1      | 0   | word (A) $\leftarrow$ (ear)                                    | -  | *      | _ | _ | _ | * | * | _ | _ | _   |

| MOVW A, eam                    | 2+     | 2+ (a) | (c) | word $(A) \leftarrow (eam)$                                    | -  | *      | _ | _ | _ | * | * | _ | _ | _   |

| MOVW A, io                     | 2      | 2      | (c) | word (A) $\leftarrow$ (io)                                     | -  | *      | _ | _ | _ | * | * | _ | _ | _   |

| MOVW A, @A                     | 2      | 2      | (c) | word $(A) \leftarrow ((A))$                                    | -  | -<br>* | _ | _ | _ | * | * | _ | - | -   |

| MOVW A, #imm16                 | 3      | 2      | 0   | word (A) $\leftarrow$ imm16                                    | -  | *      | - | _ | _ | * | * | _ | _ | _   |

| MOVW A, @RWi+disp8             | 2      | 3      | (c) | word (A) $\leftarrow$ ((RWi) +disp8)                           | -  | *      | - | _ | _ | * | * | _ | _ | _   |

| MOVW A, @RLi+disp8             | 3      | 6      | (c) | word (A) $\leftarrow$ ((RLi) +disp8)                           | _  | *      | - | _ | _ | * | * |   | _ | _   |

| MOVW A, @SP+disp8              | 3      | 3      | (c) | word (A) $\leftarrow$ ((SP) +disp8                             |    | *      | _ | _ | _ | * | * | _ | _ | _   |

| MOVPW A, addr24                | 5      | 3      | (c) | word (A) $\leftarrow$ (addr24)                                 | _  |        | _ | _ | _ | * | * | _ | _ |     |

| MOVPW A, @A                    | 2      | 2      | (c) | word (A) $\leftarrow$ ((A))                                    | -  | _      | _ | _ | _ |   |   | _ |   |     |

| MOVW dir, A                    | 2      | 2      | (c) | word (dir) $\leftarrow$ (A)                                    | _  | _      | _ | _ | _ | * | * | _ | _ | -   |

| MOVW addr16, A                 | 3      | 2      | (c) | word (addr16) ← (A)                                            | -  | _      | _ | _ | _ | * | * | _ | - | _   |

| MOVW SP, # imm16               | 4      | 2      | 0   | word (SP) ← imm16                                              | -  | _      | _ | _ | _ | * | * | _ | - | _   |

| MOVW SP, A                     | 1      | 2      | 0   | word (SP) $\leftarrow$ (A)                                     | -  | _      | _ | _ | _ | * | * | _ | _ | _   |

| MOVW RWi, A                    | 1      | 1      | 0   | word (RWi) $\leftarrow$ (A)                                    | -  | _      | _ | _ | _ | * | * | _ | _ | _   |

| MOVW ear, A                    | 2      | 2      | 0   | word (ear) $\leftarrow$ (A)                                    | -  | _      | - | _ | _ | * | * | _ | _ | _   |

| MOVW eam, A                    | 2+     | 2+ (a) | (c) | word (eam) $\leftarrow$ (A)                                    | -  | _      | - | _ | _ | * | * | _ | _ | _   |

| MOVW io, A                     | 2      | 2      | (c) | word (io) $\leftarrow$ (A)                                     | -  | _      | - | _ | _ | * | * | _ | _ | _   |

| MOVW @RWi+disp8, A             | 2      | 3      | (c) | word ((RWi) +disp8) $\leftarrow$ (A)                           |    | _      | _ |   | _ | * | * | _ | _ | _   |

| MOVW @RLi+disp8, A             | 3      | 6      | (c) | word ((RLi) +disp8) $\leftarrow$ (A)                           | -  | -      |   | _ | _ | * | * | _ | _ | _   |

| MOVW @SP+disp8, A              | 3      | 3      | (c) | word ((SP) +disp8) $\leftarrow$ (A)                            | -  | -      | _ | _ | _ | * | * | _ | - | _   |

| MOVPW addr24, A                | 5      | 3      | (c) | word (addr24) $\leftarrow$ (A)                                 | _  | _      | _ | _ | _ | * | * | _ |   | _   |

| MOVPW @A, RWi                  | 2<br>2 | 2      | (c) | word $((A)) \leftarrow (RWi)$<br>word $(RWi) \leftarrow (ear)$ | _  | _      | _ | _ |   | * | * | _ |   | _   |

| MOVW RWi, ear<br>MOVW RWi, eam | 2+     | 2+ (a) | (c) | word (RWi) ← (ear)<br>word (RWi) ← (eam)                       |    | _      | _ | _ | _ | * | * | _ | _ | _   |

| MOVW RWI, earn                 | 2+     | 3+ (a) | 0   | word (RWI) ← (earl)<br>word (ear) ← (RWI)                      |    | _      | _ | _ | _ | * | * | _ | _ | _   |

| MOVW ear, RWi                  | 2+     | 3+ (a) | (c) | word (ear) $\leftarrow$ (RWi)                                  | _  | _      | _ | _ | _ | * | * | _ | _ | _   |

| MOVW RWi, #imm16               | 3      | 2 2    | 0   | word (Cam) ← (RWI)<br>word (RWI) ← imm16                       | _  | _      | _ | _ | _ | * | * | _ | _ | _   |

| MOVW io, #imm16                | 4      | 3      | (c) | word (io) $\leftarrow$ imm16                                   | _  | _      | _ | _ | _ | _ | _ | _ | _ | _   |

| MOVW ear, #imm16               | 4      | 2      | 0   | word (lear) ← imm16                                            | _  | _      | _ | _ | _ | * | * | _ | _ | _   |

| MOVW eam, #imm16               | 4+     | 2+ (a) | (c) | word (eam) ← imm16                                             | _  | _      | _ | _ | _ | _ | _ | _ | _ | -   |

| MOVW @AL, AH                   | 2      | 2      | (c) | word $((A)) \leftarrow (AH)$                                   | _  | _      | - | _ | _ | * | * | _ | _ | _   |

| XCHW A, ear                    | 2      | 3      | 0   | word (A) $\leftrightarrow$ (ear)                               | _  | _      | _ | _ | _ | _ | _ | _ | _ | _   |

| XCHW A, eam                    | 2+     |        |     | word (A) $\leftrightarrow$ (ear)                               | _  | _      | _ | _ | _ | _ | _ | _ | _ | _   |

| XCHW RWi, ear                  | 2      | 4      | 0   | word (RWi) $\leftrightarrow$ (ear)                             | _  | _      | _ | _ | _ | _ | _ | _ | _ | _   |

| XCHW RWi, eam                  | 2+     | -      | _   | word (RWi) $\leftrightarrow$ (eam)                             | -  | -      | _ | _ | - | _ | _ | _ | _ | -   |

Note: For an explanation of "(a)" and "(c)", refer to Table 4, "Number of Execution Cycles for Each Form of Addressing," and Table 5, "Correction Values for Number of Cycles Used to Calculate Number of Actual Cycles."

Table 9 Addition and Subtraction Instructions (Byte/Word/Long Word) [42 Instructions]

| Mnemonic                                                                                                                   | #                                                 | cycles                                                        | В                                                        | Operation                                                                                                                                                                                                                                                                                                                                                                                                          | LH                                    | АН                    | I                     | S | Т                     | N                                     | Z                 | ٧                 | С                 | RMW                             |

|----------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------|---------------------------------------------------------------|----------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------|-----------------------|-----------------------|---|-----------------------|---------------------------------------|-------------------|-------------------|-------------------|---------------------------------|

| ADD A, #imm8 ADD A, dir ADD A, ear ADD A, eam ADD ear, A ADD eam, A ADDC A ADDC A, ear ADDC A, ear ADDC A, eam ADDC A, eam | 2<br>2<br>2+<br>2<br>2+<br>1<br>2<br>2+<br>1      | 2<br>3<br>2<br>3+ (a)<br>2<br>3+ (a)<br>2<br>2<br>3+ (a)<br>3 | 0<br>(b)<br>0<br>(b)<br>0<br>2×(b)<br>0<br>0<br>(b)<br>0 | byte (A) $\leftarrow$ (A) +imm8<br>byte (A) $\leftarrow$ (A) +(dir)<br>byte (A) $\leftarrow$ (A) +(ear)<br>byte (A) $\leftarrow$ (A) +(eam)<br>byte (ear) $\leftarrow$ (ear) + (A)<br>byte (eam) $\leftarrow$ (eam) + (A)<br>byte (A) $\leftarrow$ (AH) + (AL) + (C)<br>byte (A) $\leftarrow$ (A) + (ear) + (C)<br>byte (A) $\leftarrow$ (AH) + (AL) +(C) (Decimal)                                                | Z Z Z Z Z Z Z Z Z Z Z Z Z Z Z Z Z Z Z |                       |                       |   |                       | * * * * * * *                         | * * * * * * * *   | * * * * * * * * * | * * * * * * * * * | * *                             |

| SUB A, #imm8 SUB A, dir SUB A, ear SUB A, eam SUB ear, A SUB eam, A SUBC A SUBC A, ear SUBC A, ear SUBC A, eam SUBC A      | 2<br>2<br>2<br>2+<br>2<br>2+<br>1<br>2<br>2+<br>1 | 2<br>3<br>2<br>3+ (a)<br>2<br>3+ (a)<br>2<br>2<br>3+ (a)<br>3 | 0<br>(b)<br>0<br>(b)<br>0<br>2×(b)<br>0<br>0<br>(b)<br>0 | byte (A) $\leftarrow$ (A) -imm8<br>byte (A) $\leftarrow$ (A) - (dir)<br>byte (A) $\leftarrow$ (A) - (ear)<br>byte (A) $\leftarrow$ (A) - (eam)<br>byte (ear) $\leftarrow$ (ear) - (A)<br>byte (eam) $\leftarrow$ (eam) - (A)<br>byte (A) $\leftarrow$ (AH) - (AL) - (C)<br>byte (A) $\leftarrow$ (A) - (ear) - (C)<br>byte (A) $\leftarrow$ (A) - (eam) - (C)<br>byte (A) $\leftarrow$ (AH) - (AL) - (C) (Decimal) | Z Z Z Z – Z Z Z Z Z                   |                       |                       |   |                       | * * * * * * * * * * * * * * * * * * * | * * * * * * * * * | * * * * * * * * * | * * * * * * * * * | -<br>-<br>-<br>*<br>*<br>-<br>- |

| ADDW A ADDW A, ear ADDW A, eam ADDW A, #imm16 ADDW ear, A ADDW eam, A ADDCW A, ear ADDCW A, eam                            | 1<br>2<br>2+<br>3<br>2<br>2+<br>2<br>2+           | 2<br>2<br>3+ (a)<br>2<br>2<br>3+ (a)<br>2<br>3+ (a)           | 0<br>0<br>(c)<br>0<br>0<br>2×(c)<br>0<br>(c)             | word (A) $\leftarrow$ (AH) + (AL)<br>word (A) $\leftarrow$ (A) +(ear)<br>word (A) $\leftarrow$ (A) +(eam)<br>word (A) $\leftarrow$ (A) +imm16<br>word (ear) $\leftarrow$ (ear) + (A)<br>word (eam) $\leftarrow$ (eam) + (A)<br>word (A) $\leftarrow$ (A) + (ear) + (C)<br>word (A) $\leftarrow$ (A) + (eam) + (C)                                                                                                  |                                       |                       |                       |   |                       | * * * * * * *                         | * * * * * * *     | * * * * * * * *   | * * * * * * * *   | -<br>-<br>-<br>*<br>*           |

| SUBW A SUBW A, ear SUBW A, eam SUBW A, #imm16 SUBW ear, A SUBW eam, A SUBCW A, ear SUBCW A, eam                            | 1<br>2<br>2+<br>3<br>2<br>2+<br>2<br>2+           | 2<br>2<br>3+ (a)<br>2<br>2<br>3+ (a)<br>2<br>3+ (a)           | (c)                                                      | word (A) $\leftarrow$ (AH) $-$ (AL)<br>word (A) $\leftarrow$ (A) $-$ (ear)<br>word (A) $\leftarrow$ (A) $-$ (eam)<br>word (A) $\leftarrow$ (A) $-$ imm16<br>word (ear) $\leftarrow$ (ear) $-$ (A)<br>word (eam) $\leftarrow$ (eam) $-$ (A)<br>word (A) $\leftarrow$ (A) $-$ (ear) $-$ (C)<br>word (A) $\leftarrow$ (A) $-$ (eam) $-$ (C)                                                                           |                                       | -<br>-<br>-<br>-<br>- |                       |   | -<br>-<br>-<br>-<br>- | * * * * * * *                         | * * * * * * *     | * * * * * * *     | * * * * * * * *   | -<br>-<br>-<br>*<br>*           |

| ADDL A, ear ADDL A, eam ADDL A, #imm32  SUBL A, ear SUBL A, eam SUBL A, #imm32                                             | 2<br>2+<br>5<br>2<br>2+<br>5                      | 5<br>6+ (a)<br>4<br>5<br>6+ (a)<br>4                          | 0<br>(d)<br>0<br>0<br>(d)<br>0                           | $\begin{array}{l} \text{long (A)} \leftarrow \text{(A)} + \text{(ear)} \\ \text{long (A)} \leftarrow \text{(A)} + \text{(eam)} \\ \text{long (A)} \leftarrow \text{(A)} + \text{imm32} \\ \\ \text{long (A)} \leftarrow \text{(A)} - \text{(ear)} \\ \text{long (A)} \leftarrow \text{(A)} - \text{(eam)} \\ \text{long (A)} \leftarrow \text{(A)} - \text{imm32} \\ \end{array}$                                  |                                       |                       | -<br>-<br>-<br>-<br>- |   | _<br>_<br>_<br>_<br>_ | * * * * * *                           | * * * * * *       | * * * * * *       | * * * * * *       | -<br>-<br>-<br>-                |

For an explanation of "(a)", "(b)", "(c)" and "(d)", refer to Table 4, "Number of Execution Cycles for Each Form of Addressing," and Table 5, "Correction Values for Number of Cycles Used to Calculate Number of Actual Cycles."

Table 12 Unsigned Multiplication and Division Instructions (Word/Long Word) [11 Instructions]

| Mnemonic     | #  | cycles | В   | Operation                                                                                                                                                 | LH | АН | I | S | T | N | Ζ | ٧ | С | RMW |

|--------------|----|--------|-----|-----------------------------------------------------------------------------------------------------------------------------------------------------------|----|----|---|---|---|---|---|---|---|-----|

| DIVU A       | 1  | *1     | 0   | word (AH) /byte (AL)                                                                                                                                      | _  | _  | - | - | _ | _ | _ | * | * | _   |

| DIVU A, ear  | 2  | *2     | 0   | Quotient $\rightarrow$ byte (AL) Remainder $\rightarrow$ byte (AH) word (A)/byte (ear) Quotient $\rightarrow$ byte (A) Remainder $\rightarrow$ byte (ear) | _  | _  | ı | - | ı | _ | _ | * | * | _   |

| DIVU A, eam  | 2+ | *3     | *6  | word (A)/byte (eam)                                                                                                                                       | _  | _  | _ | _ | _ | _ | _ | * | * | _   |

| DIVUW A, ear | 2  | *4     | 0   | Quotient → byte (A) Remainder → byte (eam) long (A)/word (ear) Quotient → word (A) Remainder → word (ear)                                                 | _  | _  | ı | - | - | _ | _ | * | * | _   |

| DIVUW A, eam | 2+ | *5     | *7  |                                                                                                                                                           | _  | _  | 1 | - | - | _ | _ | * | * | _   |

| MULU A       | 1  | *8     | 0   | byte (AH) $\times$ byte (AL) $\rightarrow$ word (A)                                                                                                       | _  | _  | _ | _ | _ | _ | _ | _ | _ | _   |

| MULU A, ear  | 2  | *9     | 0   | byte $(A) \times byte (ear) \rightarrow word (A)$                                                                                                         | _  | _  | _ | _ | _ | _ | _ | _ | _ | _   |

| MULU A, eam  | 2+ | *10    | (b) | byte (A) $\times$ byte (eam) $\rightarrow$ word (A)                                                                                                       | _  | _  | _ | _ | _ | _ | _ | _ | _ | _   |

| MULUW A      | 1  | *11    | 0   | word (AH) $\times$ word (AL) $\rightarrow$ long (A)                                                                                                       | _  | _  | _ | _ | _ | _ | _ | _ | _ | _   |

| MULUW A, ear | 2  | *12    | 0   | word (A) $\times$ word (ear) $\rightarrow$ long (A)                                                                                                       | _  | _  | _ | _ | _ | _ | _ | _ | _ | _   |

| MULUW A, eam | 2+ | *13    | (c) | word (A) $\times$ word (eam) $\rightarrow$ long (A)                                                                                                       | _  | _  | _ | _ | _ | _ | _ | _ | _ | _   |

For an explanation of "(b)" and "(c), refer to Table 5, "Correction Values for Number of Cycle Used to Calculate Number of Actual Cycles."

<sup>\*1: 3</sup> when dividing into zero, 6 when an overflow occurs, and 14 normally.

<sup>\*2: 3</sup> when dividing into zero, 5 when an overflow occurs, and 13 normally.

<sup>\*3: 5 + (</sup>a) when dividing into zero, 7 + (a) when an overflow occurs, and 17 + (a) normally.

<sup>\*4: 3</sup> when dividing into zero, 5 when an overflow occurs, and 21 normally.

<sup>\*5: 4 + (</sup>a) when dividing into zero, 7 + (a) when an overflow occurs, and 25 + (a) normally.

<sup>\*6: (</sup>b) when dividing into zero or when an overflow occurs, and  $2 \times (b)$  normally.

<sup>\*7: (</sup>c) when dividing into zero or when an overflow occurs, and  $2 \times$  (c) normally.

<sup>\*8: 3</sup> when byte (AH) is zero, and 7 when byte (AH) is not 0.

<sup>\*9: 3</sup> when byte (ear) is zero, and 7 when byte (ear) is not 0.

<sup>\*10:</sup> 4 + (a) when byte (eam) is zero, and 8 + (a) when byte (eam) is not 0.

<sup>\*11: 3</sup> when word (AH) is zero, and 11 when word (AH) is not 0.

<sup>\*12: 3</sup> when word (ear) is zero, and 11 when word (ear) is not 0.

<sup>\*13: 4 + (</sup>a) when word (eam) is zero, and 12 + (a) when word (eam) is not 0.

Table 14 Logical 1 Instructions (Byte, Word) [39 Instructions]

| Mn                                            | emonic                                                              | #                                            | cycles                               | В                                              | Operation                                                                                                                                                                                                                                                                                                                                            | LH                       | АН               | ı                          | S         | Т                  | N                 | Z               | ٧                | С                | RMW                   |

|-----------------------------------------------|---------------------------------------------------------------------|----------------------------------------------|--------------------------------------|------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------|------------------|----------------------------|-----------|--------------------|-------------------|-----------------|------------------|------------------|-----------------------|

| AND<br>AND<br>AND<br>AND<br>AND               | A, #imm8<br>A, ear<br>A, eam<br>ear, A<br>eam, A                    | 2<br>2<br>2+<br>2<br>2+                      | 2<br>2<br>3+ (a)<br>3<br>3+ (a)      | 0<br>0<br>(b)<br>0<br>2× (b)                   | byte (A) $\leftarrow$ (A) and imm8<br>byte (A) $\leftarrow$ (A) and (ear)<br>byte (A) $\leftarrow$ (A) and (eam)<br>byte (ear) $\leftarrow$ (ear) and (A)<br>byte (eam) $\leftarrow$ (eam) and (A)                                                                                                                                                   | _<br>_<br>_<br>_         | _<br>_<br>_<br>_ | _<br>_<br>_<br>_           |           | <br> -<br> -<br> - | * * * *           | * * * * *       | R<br>R<br>R<br>R | _<br>_<br>_<br>_ | <br><br>*<br>*        |

| OR<br>OR<br>OR<br>OR<br>OR                    | A, #imm8<br>A, ear<br>A, eam<br>ear, A<br>eam, A                    | 2<br>2+<br>2<br>2+                           | 2<br>2<br>3+ (a)<br>3<br>3+ (a)      | 0<br>0<br>(b)<br>0<br>2× (b)                   | byte (A) $\leftarrow$ (A) or imm8<br>byte (A) $\leftarrow$ (A) or (ear)<br>byte (A) $\leftarrow$ (A) or (eam)<br>byte (ear) $\leftarrow$ (ear) or (A)<br>byte (eam) $\leftarrow$ (eam) or (A)                                                                                                                                                        | <br> -<br> -<br> -<br> - | _<br>_<br>_<br>_ | _<br>_<br>_<br>_           |           |                    | *<br>*<br>*<br>*  | * * * * *       | R<br>R<br>R<br>R | _<br>_<br>_<br>_ | -<br>-<br>*<br>*      |

| XOR<br>XOR<br>XOR<br>XOR<br>XOR<br>NOT<br>NOT | A, #imm8<br>A, ear<br>A, eam<br>ear, A<br>eam, A<br>A<br>ear<br>eam | 2<br>2<br>2+<br>2<br>2+<br>1<br>2<br>2+      | 2                                    | 0                                              | byte (A) $\leftarrow$ (A) xor imm8<br>byte (A) $\leftarrow$ (A) xor (ear)<br>byte (A) $\leftarrow$ (A) xor (eam)<br>byte (ear) $\leftarrow$ (ear) xor (A)<br>byte (eam) $\leftarrow$ (eam) xor (A)<br>byte (A) $\leftarrow$ not (A)<br>byte (ear) $\leftarrow$ not (ear)<br>byte (eam) $\leftarrow$ not (eam)                                        | -<br>-<br>-<br>-<br>-    |                  | -<br>-<br>-<br>-<br>-<br>- |           |                    | * * * * * * * *   | * * * * * * *   | RRRRRRR          |                  | -<br>-<br>*<br>*<br>* |

| ANDW<br>ANDW<br>ANDW                          | A, #imm16<br>A, ear<br>A, eam                                       | 1<br>3<br>2<br>2+<br>2<br>2+                 | 2<br>2<br>3+ (a)<br>3<br>3+ (a)      | 0<br>0<br>(c)<br>0<br>2×(c)                    | word (A) $\leftarrow$ (AH) and (A)<br>word (A) $\leftarrow$ (A) and imm16<br>word (A) $\leftarrow$ (A) and (ear)<br>word (A) $\leftarrow$ (A) and (eam)<br>word (ear) $\leftarrow$ (ear) and (A)<br>word (eam) $\leftarrow$ (eam) and (A)                                                                                                            | -<br>-<br>-<br>-         |                  | -<br>-<br>-<br>-           | 1 1 1 1 1 | 11111              | * * * * * *       | * * * * * *     | R R R R R R      | -<br>-<br>-<br>- | _<br>_<br>_<br>_<br>* |

| ORW<br>ORW<br>ORW<br>ORW<br>ORW<br>ORW        | A<br>A, #imm16<br>A, ear<br>A, eam<br>ear, A<br>eam, A              | 1<br>3<br>2<br>2+<br>2<br>2+                 | 2<br>2<br>2<br>3+ (a)<br>3<br>3+ (a) | 0<br>0<br>(c)<br>0<br>2×(c)                    | word (A) $\leftarrow$ (AH) or (A)<br>word (A) $\leftarrow$ (A) or imm16<br>word (A) $\leftarrow$ (A) or (ear)<br>word (A) $\leftarrow$ (A) or (eam)<br>word (ear) $\leftarrow$ (ear) or (A)<br>word (eam) $\leftarrow$ (eam) or (A)                                                                                                                  | -<br>-<br>-<br>-         |                  | -<br>-<br>-<br>-<br>-      |           | 11111              | * * * * * *       | * * * * * *     | R R R R R        | _<br>_<br>_<br>_ | _<br>_<br>_<br>*<br>* |

| XORW<br>XORW<br>XORW                          | A, #imm16<br>A, ear<br>A, eam<br>ear, A<br>eam, A<br>A              | 1<br>3<br>2<br>2+<br>2<br>2+<br>1<br>2<br>2+ | 2                                    | 0<br>0<br>(c)<br>0<br>2×(c)<br>0<br>0<br>2×(c) | word (A) $\leftarrow$ (AH) xor (A)<br>word (A) $\leftarrow$ (A) xor imm16<br>word (A) $\leftarrow$ (A) xor (ear)<br>word (A) $\leftarrow$ (A) xor (eam)<br>word (ear) $\leftarrow$ (ear) xor (A)<br>word (eam) $\leftarrow$ (eam) xor (A)<br>word (A) $\leftarrow$ not (A)<br>word (ear) $\leftarrow$ not (ear)<br>word (eam) $\leftarrow$ not (eam) |                          |                  |                            |           |                    | * * * * * * * * * | * * * * * * * * | RRRRRRRR         |                  |                       |

For an explanation of "(a)", "(b)", "(c)" and "(d)", refer to Table 4, "Number of Execution Cycles for Each Form of Addressing," and Table 5, "Correction Values for Number of Cycles Used to Calculate Number of Actual Cycles."

Table 23

Bit Manipulation Instructions [21 Instructions]

| Mr                   | nemonic                                     | #           | cycles         | В                          | Operation                                                                                                  | LH          | АН    | I           | S      | Т           | N           | Z   | ٧           | С     | RMW         |

|----------------------|---------------------------------------------|-------------|----------------|----------------------------|------------------------------------------------------------------------------------------------------------|-------------|-------|-------------|--------|-------------|-------------|-----|-------------|-------|-------------|

| MOVB<br>MOVB<br>MOVB | A, dir:bp<br>A, addr16:bp<br>A, io:bp       | 3<br>4<br>3 | 3<br>3<br>3    | (b)<br>(b)                 | byte (A) $\leftarrow$ (dir:bp) b<br>byte (A) $\leftarrow$ (addr16:bp) b<br>byte (A) $\leftarrow$ (io:bp) b | Z<br>Z<br>Z | * *   | _<br>_<br>_ | -<br>- | -<br>-<br>- | * *         | * * | _<br>_<br>_ | _<br> | _<br>_<br>_ |

| MOVB<br>MOVB<br>MOVB | dir:bp, A<br>addr16:bp, A<br>io:bp, A       | 3<br>4<br>3 | 4<br>4<br>4    | 2× (b)<br>2× (b)<br>2× (b) | bit (dir:bp) b $\leftarrow$ (A)<br>bit (addr16:bp) b $\leftarrow$ (A)<br>bit (io:bp) b $\leftarrow$ (A)    | -<br>-<br>- | 1 1 1 | -<br>-<br>- |        | -<br>-<br>- | * *         | * * | _<br>_<br>_ |       | *<br>*<br>* |

| SETB<br>SETB<br>SETB | dir:bp<br>addr16:bp<br>io:bp                | 3<br>4<br>3 | 4<br>4<br>4    | 2× (b)<br>2× (b)<br>2× (b) | bit (dir:bp) b $\leftarrow$ 1<br>bit (addr16:bp) b $\leftarrow$ 1<br>bit (io:bp) b $\leftarrow$ 1          | -<br>-<br>- | 1 1 1 | -<br>-<br>- |        | _<br>_<br>_ | _<br>_<br>_ |     | _<br>_<br>_ |       | *<br>*<br>* |

| CLRB<br>CLRB<br>CLRB | dir:bp<br>addr16:bp<br>io:bp                | 3<br>4<br>3 | 4<br>4<br>4    | 2× (b)<br>2× (b)<br>2× (b) | bit (dir:bp) b $\leftarrow$ 0<br>bit (addr16:bp) b $\leftarrow$ 0<br>bit (io:bp) b $\leftarrow$ 0          | -<br>-<br>- | 1 1 1 | -<br>-<br>- |        | -<br>-<br>- | -<br>-<br>- |     | _<br>_<br>_ |       | *<br>*<br>* |

| BBC<br>BBC<br>BBC    | dir:bp, rel<br>addr16:bp, rel<br>io:bp, rel | 4<br>5<br>4 | *1<br>*1<br>*1 | (b)<br>(b)<br>(b)          | Branch when (dir:bp) b = 0 Branch when (addr16:bp) b = 0 Branch when (io:bp) b = 0                         | -<br>-<br>- | 1 1 1 | _<br>_<br>_ | <br>   | _<br>_<br>_ | _<br>_<br>_ | * * | _<br>_<br>_ |       | -<br>-<br>- |

| BBS<br>BBS<br>BBS    | dir:bp, rel<br>addr16:bp, rel<br>io:bp, rel | 4<br>5<br>4 | *1<br>*1<br>*1 | (b)<br>(b)<br>(b)          | Branch when (dir:bp) b = 1<br>Branch when (addr16:bp) b = 1<br>Branch when (io:bp) b = 1                   | -<br>-<br>- | 1 1 1 | _<br>_<br>_ |        | _<br>_<br>_ | _<br>_<br>_ | * * | _<br>_<br>_ |       | -<br>-<br>- |

| SBBS                 | addr16:bp, rel                              | 5           | *2             | 2× (b)                     | Branch when $(addr16:bp)b=1$ , $bit=1$                                                                     | _           | -     | _           | -      | _           | _           | *   | _           | _     | *           |

| WBTS                 | io:bp                                       | 3           | *3             | *4                         | Wait until (io:bp) b = 1                                                                                   | _           | _     | -           | _      | _           | _           | _   | _           | _     | _           |

| WBTC                 | io:bp                                       | 3           | *3             | *4                         | Wait until (io:bp) b = 0                                                                                   | _           | -     | -           | -      | _           | _           | _   | _           | -     | _           |

For an explanation of "(b)", refer to Table 5, "Correction Values for Number of Cycles Used to Calculate Number of Actual Cycles."

<sup>\*1: 5</sup> when branching, 4 when not branching

<sup>\*2: 7</sup> when condition is satisfied, 6 when not satisfied

<sup>\*3:</sup> Undefined count

<sup>\*4:</sup> Until condition is satisfied

Table 24 Accumulator Manipulation Instructions (Byte/Word) [6 Instructions]

| Mnemonic | # | cycles | В | Operation                                              | LH | АН | I | S | T | Z | Z | ٧ | С | RMW |

|----------|---|--------|---|--------------------------------------------------------|----|----|---|---|---|---|---|---|---|-----|

| SWAP     | 1 | 3      | 0 | byte (A) 0 to 7 $\leftarrow$ $\rightarrow$ (A) 8 to 15 | _  | _  | _ | _ | _ | _ | _ | _ | _ | _   |

| SWAPW    | 1 | 2      | 0 | word $(AH) \leftarrow \rightarrow (AL)$                | _  | *  | _ | _ | _ | _ | _ | _ | _ | _   |

| EXT      | 1 | 1      | 0 | Byte code extension                                    | Χ  | _  | _ | _ | _ | * | * | _ | _ | _   |

| EXTW     | 1 | 2      | 0 | Word code extension                                    | _  | Χ  | _ | _ | _ | * | * | _ | _ | _   |

| ZEXT     | 1 | 1      | 0 | Byte zero extension                                    | Ζ  | _  | _ | _ | _ | R | * | _ | _ | _   |

| ZEXTW    | 1 | 2      | 0 | Word zero extension                                    | _  | Ζ  | _ | _ | _ | R | * | _ | _ | _   |

Table 25 String Instructions [10 Instructions]

| Mnemonic     | # | cycles | В  | Operation                                            | LH | АН | I | S | T | N | Z | ٧ | С | RMW |

|--------------|---|--------|----|------------------------------------------------------|----|----|---|---|---|---|---|---|---|-----|

| MOVS/MOVSI   | 2 | *2     | *3 | Byte transfer @AH+ ← @AL+, counter = RW0             | _  | _  | _ | _ | _ | _ | _ | _ | _ | _   |

| MOVSD        | 2 | *2     | *3 | Byte transfer $@AH-\leftarrow @AL-$ , counter = RW0  | _  | -  | - | - | - | _ | - | _ | _ | _   |

| SCEQ/SCEQI   | 2 | *1     | *4 | Byte retrieval @AH+ - AL, counter = RW0              | _  | _  | _ | _ | _ | * | * | * | * | _   |

| SCEQD        | 2 | *1     | *4 | Byte retrieval @AHAL, counter = RW0                  | _  | -  | - | - | - | * | * | * | * | _   |

| FILS/FILSI   | 2 | 5m +3  | *5 | Byte filling @AH+ ← AL, counter = RW0                | _  | -  | _ | ı | _ | * | * | _ | - | _   |

| MOVSW/MOVSWI | 2 | *2     | *6 | Word transfer $@AH+ \leftarrow @AL+$ , counter = RW0 | _  | _  | _ | _ | _ | _ | _ | _ | _ | _   |

| MOVSWD       | 2 | *2     | *6 | Word transfer $@AH-\leftarrow @AL-$ , counter = RW0  | _  | -  | - | - | - | _ | - | _ | _ | -   |

| SCWEQ/SCWEQI | 2 | *1     | *7 | Word retrieval @AH+ - AL, counter = RW0              | _  | _  | _ | _ | _ | * | * | * | * | _   |

| SCWEQD       | 2 | *1     | *7 | Word retrieval @AHAL, counter = RW0                  | _  | -  | - | _ | - | * | * | * | * | _   |

| FILSW/FILSWI | 2 | 5m +3  | *8 | Word filling $@AH+ \leftarrow AL$ , counter = RW0    | _  | _  | _ | - | - | * | * | _ | _ | _   |

m: RW0 value (counter value)

<sup>\*1: 3</sup> when RW0 is 0, 2 +  $6 \times$  (RW0) for count out, and 6n + 4 when match occurs

<sup>\*2: 4</sup> when RW0 is 0, 2 +  $6 \times$  (RW0) in any other case

<sup>\*3: (</sup>b)  $\times$  (RW0)

<sup>\*4: (</sup>b)  $\times$  n

<sup>\*5: (</sup>b)  $\times$  (RW0)

<sup>\*6: (</sup>c)  $\times$  (RW0)

<sup>\*7: (</sup>c)  $\times$  n

<sup>\*8: (</sup>c) × (RW0)