Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Not For New Designs                                             |

|----------------------------|-----------------------------------------------------------------|

| Core Processor             | 8051                                                            |

| Core Size                  | 8-Bit                                                           |

| Speed                      | 25MHz                                                           |

| Connectivity               | SMBus (2-Wire/I <sup>2</sup> C), SPI, UART/USART                |

| Peripherals                | POR, PWM, WDT                                                   |

| Number of I/O              | 17                                                              |

| Program Memory Size        | 8KB (8K x 8)                                                    |

| Program Memory Type        | FLASH                                                           |

| EEPROM Size                | -                                                               |

| RAM Size                   | 768 x 8                                                         |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 3.6V                                                     |

| Data Converters            |                                                                 |

| Oscillator Type            | Internal                                                        |

| Operating Temperature      | -40°C ~ 85°C (TA)                                               |

| Mounting Type              | Surface Mount                                                   |

| Package / Case             | 20-VFQFN Exposed Pad                                            |

| Supplier Device Package    | 20-MLP (4x4)                                                    |

| Purchase URL               | https://www.e-xfl.com/product-detail/silicon-labs/c8051f331-gmr |

|                            |                                                                 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### 1.1.3. Additional Features

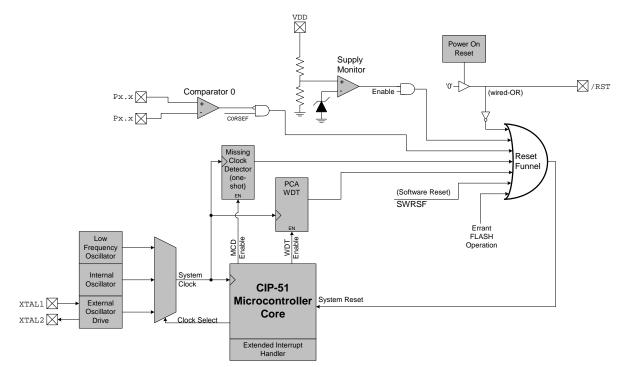

The C8051F330/1/2/3/4/5 SoC family includes several key enhancements to the CIP-51 core and peripherals to improve performance and ease of use in end applications.

The extended interrupt handler provides 14 interrupt sources into the CIP-51 (as opposed to 7 for the standard 8051), allowing numerous analog and digital peripherals to interrupt the controller. An interrupt driven system requires less intervention by the MCU, giving it more effective throughput. The extra interrupt sources are very useful when building multi-tasking, real-time systems.

Eight reset sources are available: power-on reset circuitry (POR), an on-chip  $V_{DD}$  monitor (forces reset when power supply voltage drops below  $V_{RST}$  as given in Table 10.1 on page 102), a Watchdog Timer, a Missing Clock Detector, a voltage level detection from Comparator0, a forced software reset, an external reset pin, and an illegal Flash access protection circuit. Each reset source except for the POR, Reset Input Pin, or Flash error may be disabled by the user in software. The WDT may be permanently enabled in software after a power-on reset during MCU initialization.

The internal oscillator factory calibrated to 24.5 MHz  $\pm$ 2%. This internal oscillator period may be user programmed in ~0.5% increments. An additional low-frequency oscillator is also available which facilitates low-power operation. An external oscillator drive circuit is included, allowing an external crystal, ceramic resonator, capacitor, RC, or CMOS clock source to generate the system clock. If desired, the system clock source may be switched on-the-fly between both internal and external oscillator circuits. An external oscillator can also be extremely useful in low power applications, allowing the MCU to run from a slow (power saving) source, while periodically switching to the fast (up to 25 MHz) internal oscillator as needed.

Figure 1.8. On-Chip Clock and Reset

# 3. Global Electrical Characteristics

#### **Table 3.1. Global Electrical Characteristics**

-40 to +85 °C, 25 MHz system clock unless otherwise specified.

| Parameter                                    | Conditions                                                                        | Min           | Тур    | Max   | Units  |

|----------------------------------------------|-----------------------------------------------------------------------------------|---------------|--------|-------|--------|

| Digital Supply Voltage                       |                                                                                   | $V_{RST}^{1}$ | 3.0    | 3.6   | V      |

| Digital Supply RAM Data<br>Retention Voltage |                                                                                   | _             | 1.5    | _     | V      |

| SYSCLK (System Clock)<br>(Note 2)            |                                                                                   | 0             |        | 25    | MHz    |

| T <sub>SYSH</sub> (SYSCLK High Time)         |                                                                                   | 18            | _      |       | ns     |

| T <sub>SYSL</sub> (SYSCLK Low Time)          |                                                                                   | 18            | _      | _     | ns     |

| Specified Operating<br>Temperature Range     |                                                                                   | -40           |        | +85   | °C     |

| Digital Supply Current—CPU                   | Active (Normal Mode, fetching instr                                               | uctions       | from F | lash) |        |

| I <sub>DD</sub> (Note 3)                     | V <sub>DD</sub> = 3.6 V, F = 25 MHz                                               | —             | 10.7   | 11.7  | mA     |

|                                              | V <sub>DD</sub> = 3.0 V, F = 25 MHz                                               | —             | 7.8    | 8.3   | mA     |

|                                              | V <sub>DD</sub> = 3.0 V, F = 1 MHz                                                | —             | 0.38   | —     | mA     |

|                                              | V <sub>DD</sub> = 3.0 V, F = 80 kHz                                               | _             | 31     | _     | μA     |

| I <sub>DD</sub> Supply Sensitivity (Note 3)  | F = 25 MHz                                                                        | _             | 65     |       | %/V    |

|                                              | F = 1 MHz                                                                         |               | 61     |       | %/V    |

| I <sub>DD</sub> Frequency Sensitivity        | $V_{DD}$ = 3.0 V, F $\leq$ 15 MHz, T = 25 °C                                      | _             | 0.38   | _     | mA/MHz |

| (Note 3, Note 4)                             | V <sub>DD</sub> = 3.0 V, F > 15 MHz, T = 25 °C                                    | —             | 0.21   | —     | mA/MHz |

|                                              | $V_{DD} = 3.6 \text{ V}, \text{ F} \le 15 \text{ MHz}, \text{ T} = 25 \text{ °C}$ | —             | 0.53   | —     | mA/MHz |

|                                              | V <sub>DD</sub> = 3.6 V, F > 15 MHz, T = 25 °C                                    | _             | 0.27   | _     | mA/MHz |

# 4. Pinout and Package Definitions

Table 4.1. Pin Definitions for the C8051F330/1/2/3/4/5

| Name            | Pin<br>'F330/1/2/<br>3/4/5-GM | Pin<br>'F330-GP | Туре             | Description                                                                                                                                                                                                                                  |

|-----------------|-------------------------------|-----------------|------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| V <sub>DD</sub> | 3                             | 6               |                  | Power Supply Voltage.                                                                                                                                                                                                                        |

| GND             | 2                             | 5               |                  | Ground.                                                                                                                                                                                                                                      |

| RST/            | 4                             | 7               | D I/O            | Device Reset. Open-drain output of internal POR or $V_{DD}$ monitor. An external source can initiate a system reset by driving this pin low for at least 10 $\mu$ s.                                                                         |

| C2CK            |                               |                 | D I/O            | Clock signal for the C2 Debug Interface.                                                                                                                                                                                                     |

| P2.0/           | 5                             | 8               | D I/O            | Port 3.0. See Section 14 for a complete description.                                                                                                                                                                                         |

| C2D             |                               |                 | D I/O            | Bi-directional data signal for the C2 Debug Interface.                                                                                                                                                                                       |

| P0.0/           | 1                             | 4               | D I/O or<br>A In | Port 0.0. See <b>Section 14</b> for a complete description.                                                                                                                                                                                  |

| VREF            |                               |                 | A In             | External VREF input. See <b>Section 7</b> for a complete descrip-<br>tion.                                                                                                                                                                   |

| P0.1            | 20                            | 3               | D I/O or<br>A In | Port 0.1. See Section 14 for a complete description.                                                                                                                                                                                         |

| IDA0            |                               |                 | AOut             | IDA0 Output. See Section 6 for a complete description.                                                                                                                                                                                       |

| P0.2/           | 19                            | 2               | D I/O or<br>A In | Port 0.2. See <b>Section 14</b> for a complete description.                                                                                                                                                                                  |

| XTAL1           |                               |                 | A In             | External Clock Input. This pin is the external oscillator return for a crystal or resonator. See <b>Section 13</b> for a complete description.                                                                                               |

| P0.3/           | 18                            | 1               | D I/O or<br>A In | Port 0.3. See Section 14 for a complete description.                                                                                                                                                                                         |

| XTAL2           |                               |                 | A I/O or<br>D In | External Clock Output. For an external crystal or resonator, this pin is the excitation driver. This pin is the external clock input for CMOS, capacitor, or RC oscillator configurations. See <b>Section 13</b> for a complete description. |

| P0.4            | 17                            | 20              | D I/O or<br>A In | Port 0.4. See <b>Section 14</b> for a complete description.                                                                                                                                                                                  |

| P0.5            | 16                            | 19              | D I/O or<br>A In | Port 0.5. See Section 14 for a complete description.                                                                                                                                                                                         |

# 5. 10-Bit ADC (ADC0, C8051F330/2/4 only)

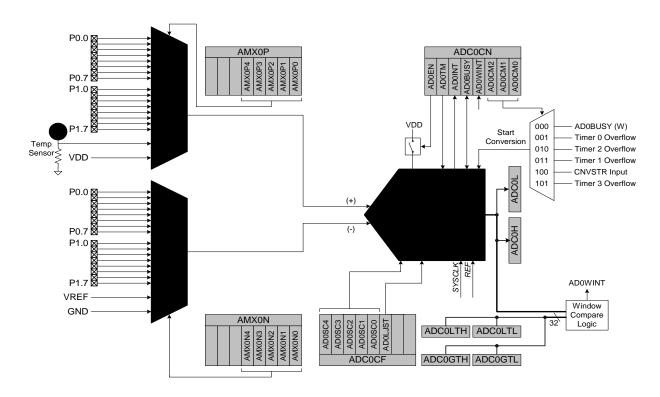

The ADC0 subsystem for the C8051F330/2/4 consists of two analog multiplexers (referred to collectively as AMUX0) with 16 total input selections, and a 200 ksps, 10-bit successive-approximation-register ADC with integrated track-and-hold and programmable window detector. The AMUX0, data conversion modes, and window detector are all configurable under software control via the Special Function Registers shown in Figure 5.1. ADC0 operates in both Single-ended and Differential modes, and may be configured to measure Ports0-1, the Temperature Sensor output, or  $V_{DD}$  with respect to Ports0-1 or GND. The ADC0 subsystem is enabled only when the AD0EN bit in the ADC0 Control register (ADC0CN) is set to logic 1. The ADC0 subsystem is in low power shutdown when this bit is logic 0.

# 5.1. Analog Multiplexer

AMUX0 selects the positive and negative inputs to the ADC. Any of the following may be selected as the positive input: Ports0-1, the on-chip temperature sensor, or the positive power supply ( $V_{DD}$ ). Any of the following may be selected as the negative input: Ports0-1,  $V_{REF}$ , or GND. When GND is selected as the negative input, ADC0 operates in Single-ended Mode; all other times, ADC0 operates in Differential Mode. The ADC0 input channels are selected in the AMX0P and AMX0N registers as described in SFR Definition 5.1 and SFR Definition 5.2.

The conversion code format differs between Single-ended and Differential modes. The registers ADC0H and ADC0L contain the high and low bytes of the output conversion code from the ADC at the completion of each conversion. Data can be right-justified or left-justified, depending on the setting of the AD0LJST. When in Single-ended Mode, conversion codes are represented as 10-bit unsigned integers. Inputs are

| R/W      | R/W                                                                                                                                                                                      | R/W               | R/W                          | R/W           | R/W            | R/W           | R/W           | Reset Value  |  |  |  |  |  |

|----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------|------------------------------|---------------|----------------|---------------|---------------|--------------|--|--|--|--|--|

| AD0EN    | AD0TM                                                                                                                                                                                    | AD0INT            | AD0BUSY                      | AD0WINT       | AD0CM2         | AD0CM1        | AD0CM0        | 00000000     |  |  |  |  |  |

| Bit7     | Bit6                                                                                                                                                                                     | Bit5              | Bit4                         | Bit3          | Bit2           | Bit1          | Bit0          | SFR Address: |  |  |  |  |  |

|          |                                                                                                                                                                                          |                   |                              |               |                | (bit addr     | essable)      | 0xE8         |  |  |  |  |  |

| Bit7:    | AD0EN: ADC0 Enable Bit.<br>0: ADC0 Disabled. ADC0 is in low-power shutdown.                                                                                                              |                   |                              |               |                |               |               |              |  |  |  |  |  |

| Bit6:    | 1: ADC0 Enabled. ADC0 is active and ready for data conversions.<br>AD0TM: ADC0 Track Mode Bit.<br>0: Normal Track Mode: When ADC0 is enabled, tracking is continuous unless a conversion |                   |                              |               |                |               |               |              |  |  |  |  |  |

| Bit5:    | is in progres<br>1: Low-powe                                                                                                                                                             | s.<br>er Track Mo | ode: Trackir                 | ng Defined by | y AD0CM2-      |               |               |              |  |  |  |  |  |

|          | AD0INT: AD<br>0: ADC0 has<br>1: ADC0 has                                                                                                                                                 | s not complete    | leted a data<br>d a data cor | conversion    |                | ast time AD   | 0INT was c    | leared.      |  |  |  |  |  |

| Bit4:    | AD0BUSY: /<br>Read:                                                                                                                                                                      |                   |                              |               |                |               |               |              |  |  |  |  |  |

|          | 0: ADC0 cor<br>to logic 1 on                                                                                                                                                             | the falling       | edge of AD                   | 0BUSY.        | on is not cu   | rrently in pr | ogress. AD    | 0INT is set  |  |  |  |  |  |

|          | 1: ADC0 cor<br>Write:                                                                                                                                                                    | nversion is       | in progress                  |               |                |               |               |              |  |  |  |  |  |

|          | 0: No Effect.                                                                                                                                                                            |                   |                              |               |                |               |               |              |  |  |  |  |  |

|          | 1: Initiates A                                                                                                                                                                           |                   |                              |               |                |               |               |              |  |  |  |  |  |

| Bit3:    | ADOWINT: A                                                                                                                                                                               |                   | •                            | •             | -              |               | . ()          |              |  |  |  |  |  |

|          | 0: ADC0 Win<br>1: ADC0 Win                                                                                                                                                               |                   |                              |               |                | ed since this | s flag was la | ast cleared. |  |  |  |  |  |

| Bits2–0: | AD0CM2-0:                                                                                                                                                                                |                   |                              |               |                |               |               |              |  |  |  |  |  |

|          | When AD0T                                                                                                                                                                                |                   |                              |               |                |               |               |              |  |  |  |  |  |

|          | 000: ADC0 (                                                                                                                                                                              |                   |                              |               |                | 0BUSY.        |               |              |  |  |  |  |  |

|          | 001: ADC0 0<br>010: ADC0 0                                                                                                                                                               |                   |                              |               |                |               |               |              |  |  |  |  |  |

|          | 010: ADC0 0                                                                                                                                                                              |                   |                              |               |                |               |               |              |  |  |  |  |  |

|          | 100: ADC0 0                                                                                                                                                                              |                   |                              |               |                | CNVSTR.       |               |              |  |  |  |  |  |

|          | 101: ADC0 o                                                                                                                                                                              | conversion        | initiated on                 | overflow of   | Timer 3.       |               |               |              |  |  |  |  |  |

|          | 11x: Reserve                                                                                                                                                                             |                   |                              |               |                |               |               |              |  |  |  |  |  |

|          | When AD0T<br>000: Trackin<br>version.                                                                                                                                                    |                   | on write of '                | 1' to AD0BU   | SY and las     | ts 3 SAR cl   | ocks, follow  | ved by con-  |  |  |  |  |  |

|          | 001: Trackin sion.                                                                                                                                                                       | g initiated       | on overflow                  | of Timer 0 a  | ind lasts 3 \$ | SAR clocks    | , followed b  | y conver-    |  |  |  |  |  |

|          | 010: Trackin sion.                                                                                                                                                                       | g initiated       | on overflow                  | of Timer 2 a  | ind lasts 3 \$ | SAR clocks    | , followed b  | y conver-    |  |  |  |  |  |

|          | 011: Trackin sion.                                                                                                                                                                       | g initiated o     | on overflow                  | of Timer 1 a  | nd lasts 3 S   | SAR clocks    | , followed b  | y conver-    |  |  |  |  |  |

|          | 100: ADC0 t<br>CNVSTR ed                                                                                                                                                                 | •                 | when CNV                     | STR input is  | logic low; c   | conversion s  | starts on ris | ing          |  |  |  |  |  |

|          | 101: Trackin sion.                                                                                                                                                                       |                   | on overflow                  | of Timer 3 a  | ind lasts 3 \$ | SAR clocks    | , followed b  | y conver-    |  |  |  |  |  |

|          | 11x: Reserve                                                                                                                                                                             | ed.               |                              |               |                |               |               |              |  |  |  |  |  |

## SFR Definition 5.6. ADC0CN: ADC0 Control

# C8051F330/1/2/3/4/5

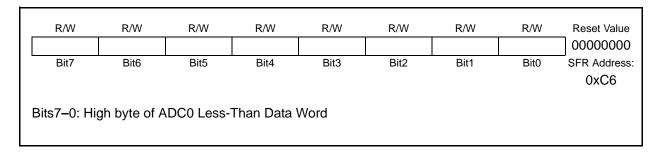

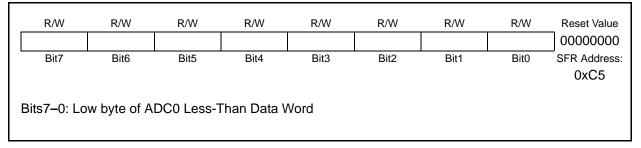

# SFR Definition 5.9. ADC0LTH: ADC0 Less-Than Data High Byte

# SFR Definition 5.10. ADC0LTL: ADC0 Less-Than Data Low Byte

# Table 7.1. Voltage Reference Electrical Characteristics $V_{DD}$ = 3.0 V; -40 to +85 °C unless otherwise specified.

| Parameter                       | Conditions                                    | Min  | Тур  | Max             | Units  |  |  |  |  |  |  |

|---------------------------------|-----------------------------------------------|------|------|-----------------|--------|--|--|--|--|--|--|

| Internal Reference (REFBE = 1)  |                                               |      |      |                 |        |  |  |  |  |  |  |

| Output Voltage                  | 25 °C ambient                                 | 2.38 | 2.44 | 2.50            | V      |  |  |  |  |  |  |

| VREF Short-Circuit Current      |                                               | —    |      | 10              | mA     |  |  |  |  |  |  |

| VREF Temperature<br>Coefficient |                                               | —    | 15   | —               | ppm/°C |  |  |  |  |  |  |

| Load Regulation                 | Load = 0 to 200 µA to AGND                    |      | 0.5  |                 | ppm/µA |  |  |  |  |  |  |

| VREF Turn-on Time 1             | 4.7 μF tantalum, 0.1 μF ceramic<br>bypass     |      | 2    |                 | ms     |  |  |  |  |  |  |

| VREF Turn-on Time 2             | 0.1 µF ceramic bypass                         |      | 20   | _               | μs     |  |  |  |  |  |  |

| VREF Turn-on Time 3             | no bypass cap                                 |      | 10   |                 | μs     |  |  |  |  |  |  |

| Power Supply Rejection          |                                               |      | 140  | —               | ppm/V  |  |  |  |  |  |  |

|                                 | External Reference (REFBE = 0                 | )    |      |                 | I      |  |  |  |  |  |  |

| Input Voltage Range             |                                               | 0    |      | V <sub>DD</sub> | V      |  |  |  |  |  |  |

| Input Current                   | Sample Rate = 200 ksps; VREF = 3.0 V          |      | 12   |                 | μA     |  |  |  |  |  |  |

|                                 | Power Specifications                          |      |      |                 |        |  |  |  |  |  |  |

| ADC Bias Generator              | BIASE = '1' or AD0EN = '1' or<br>IOSCEN = '1' | _    | 100  | _               | μA     |  |  |  |  |  |  |

| Reference Bias Generator        | REFBE = '1' or TEMPE = '1' or<br>IDA0EN = '1' | —    | 40   | —               | μA     |  |  |  |  |  |  |

## **Table 9.3. Special Function Registers**

SFRs are listed in alphabetical order. All undefined SFR locations are reserved

| Register | Address | Description                       | Page |

|----------|---------|-----------------------------------|------|

| ACC      | 0xE0    | Accumulator                       | 85   |

| ADC0CF   | 0xBC    | ADC0 Configuration                | 49   |

| ADC0CN   | 0xE8    | ADC0 Control                      | 50   |

| ADC0GTH  | 0xC4    | ADC0 Greater-Than Compare High    | 51   |

| ADC0GTL  | 0xC3    | ADC0 Greater-Than Compare Low     | 51   |

| ADC0H    | 0xBE    | ADC0 High                         | 49   |

| ADC0L    | 0xBD    | ADC0 Low                          | 49   |

| ADC0LTH  | 0xC6    | ADC0 Less-Than Compare Word High  | 52   |

| ADC0LTL  | 0xC5    | ADC0 Less-Than Compare Word Low   | 52   |

| AMX0N    | 0xBA    | AMUX0 Negative Channel Select     | 48   |

| AMX0P    | 0xBB    | AMUX0 Positive Channel Select     | 47   |

| В        | 0xF0    | B Register                        | 85   |

| CKCON    | 0x8E    | Clock Control                     | 183  |

| CLKSEL   | 0xA9    | Clock Select                      | 121  |

| CPT0CN   | 0x9B    | Comparator0 Control               | 67   |

| CPT0MD   | 0x9D    | Comparator0 Mode Selection        | 69   |

| CPT0MX   | 0x9F    | Comparator0 MUX Selection         | 68   |

| DPH      | 0x83    | Data Pointer High                 | 83   |

| DPL      | 0x82    | Data Pointer Low                  | 83   |

| EIE1     | 0xE6    | Extended Interrupt Enable 1       | 91   |

| EIP1     | 0xF6    | Extended Interrupt Priority 1     | 92   |

| EMI0CN   | 0xAA    | External Memory Interface Control | 111  |

| FLKEY    | 0xB7    | Flash Lock and Key                | 109  |

| FLSCL    | 0xB6    | Flash Scale                       | 109  |

| IDA0CN   | 0xB9    | Current Mode DAC0 Control         | 59   |

| IDA0H    | 0x97    | Current Mode DAC0 High            | 59   |

| IDA0L    | 0x96    | Current Mode DAC0 Low             | 60   |

| IE       | 0xA8    | Interrupt Enable                  | 89   |

| IP       | 0xB8    | Interrupt Priority                | 90   |

| IT01CF   | 0xE4    | INT0/INT1 Configuration           | 93   |

| OSCICL   | 0xB3    | Internal Oscillator Calibration   | 114  |

| OSCICN   | 0xB2    | Internal Oscillator Control       | 114  |

| OSCLCN   | 0xE3    | Low-Frequency Oscillator Control  | 115  |

| R/W               | R/W                                                                                          | R/W                                                                      | R/W                                                                  | R/W            | R            | R/W          | R/W        | Reset Value          |

|-------------------|----------------------------------------------------------------------------------------------|--------------------------------------------------------------------------|----------------------------------------------------------------------|----------------|--------------|--------------|------------|----------------------|

| WEAKP             | UD XBARE                                                                                     | T1E                                                                      | T0E                                                                  | ECIE           | -            | PCA          | OME        | 00000000             |

| Bit7              | Bit6                                                                                         | Bit5                                                                     | Bit4                                                                 | Bit3           | Bit2         | Bit1         | Bit0       | SFR Address:<br>0xE2 |

| Bit7:             | WEAKPUD: F<br>0: Weak Pullu<br>1: Weak Pullu                                                 | ps enabled                                                               | (except fo                                                           |                | e I/O are co | onfigured as | s analog i | nput).               |

| Bit6:             | XBARE: Cros<br>0: Crossbar d<br>1: Crossbar e                                                | sbar Enable<br>isabled.                                                  |                                                                      |                |              |              |            |                      |

| Bit5:             | T1E: T1 Enab<br>0: T1 unavaila<br>1: T1 routed to                                            | able at Port                                                             | pin.                                                                 |                |              |              |            |                      |

| Bit4:             | T0E: T0 Enab<br>0: T0 unavaila<br>1: T0 routed to                                            | le<br>able at Port                                                       | pin.                                                                 |                |              |              |            |                      |

| Bit3:             | ECIE: PCA0 E<br>0: ECI unavai<br>1: ECI routed                                               | External Co<br>lable at Por                                              | t pin.                                                               | Enable         |              |              |            |                      |

| Bit2:<br>Bits1–0: | Unused. Read<br>PCA0ME: PC<br>00: All PCA I/<br>01: CEX0 rou<br>10: CEX0, CE<br>11: CEX0, CE | d = 0b. Writ<br>A Module I/<br>O unavailat<br>ted to Port<br>X1 routed t | e = don't ca<br>⁄O Enable I<br>ble at Port p<br>pin.<br>to Port pins | Bits.<br>bins. |              |              |            |                      |

#### 14.3. General Purpose Port I/O

Port pins that remain unassigned by the Crossbar and are not used by analog peripherals can be used for general purpose I/O. Ports2–0 are accessed through corresponding special function registers (SFRs) that are both byte addressable and bit addressable. When writing to a Port, the value written to the SFR is latched to maintain the output data value at each pin. When reading, the logic levels of the Port's input pins are returned regardless of the XBRn settings (i.e., even when the pin is assigned to another signal by the Crossbar, the Port register can always read its corresponding Port I/O pin). The exception to this is the execution of the read-modify-write instructions that target a Port Latch register as the destination. The read-modify-write instructions when operating on a Port SFR are the following: ANL, ORL, XRL, JBC, CPL, INC, DEC, DJNZ and MOV, CLR or SETB, when the destination is an individual bit in a Port SFR. For these instructions, the value of the register (not the pin) is read, modified, and written back to the SFR.

| R/W<br>P0.7 | R/W<br>P0.6                                                                                            | R/W<br>P0.5 | R/W<br>P0.4 | R/W<br>P0.3 | R/W<br>P0.2 | R/W<br>P0.1 | R/W<br>P0.0 | Reset Value  |  |  |  |  |  |

|-------------|--------------------------------------------------------------------------------------------------------|-------------|-------------|-------------|-------------|-------------|-------------|--------------|--|--|--|--|--|

| Bit7        | Bit6                                                                                                   | Bit5        | Bit4        | Bit3        | Bit2        | Bit1        | Bit0        | SFR Address: |  |  |  |  |  |

|             |                                                                                                        |             |             |             |             | (bit addr   | essable)    | 0x80         |  |  |  |  |  |

| Bits7–0:    | P0.7 P0.6 P0.5 P0.4 P0.3 P0.2 P0.1 P0.0 1111111   Bit7 Bit6 Bit5 Bit4 Bit3 Bit2 Bit1 Bit0 SFR Address: |             |             |             |             |             |             |              |  |  |  |  |  |

# SFR Definition 14.3. P0: Port0

## SFR Definition 14.4. P0MDIN: Port0 Input Mode

| R/W      | R/W                                                                            | R/W                               | R/W                          | R/W          | R/W                         | R/W                  | R/W         | Reset Value  |

|----------|--------------------------------------------------------------------------------|-----------------------------------|------------------------------|--------------|-----------------------------|----------------------|-------------|--------------|

| Bit7     | Bit6                                                                           | Bit5                              | Bit4                         | Bit3         | Bit2                        | Bit1                 | Bit0        | SFR Address: |

| Biti     | Бію                                                                            | Bito                              | DI(4                         | ЫІЗ          | DILZ                        | Biti                 | Bito        | 0xF1         |

| Bits7–0: | Analog Input<br>Port pins con<br>receiver disa<br>0: Correspon<br>1: Correspon | ifigured as<br>bled.<br>ding P0.n | analog inpu<br>pin is config | its have the | ir weak pull<br>analog inpu | up, digital c<br>it. | lriver, and | digital      |

130

#### 15.3.2. Clock Low Extension

SMBus provides a clock synchronization mechanism, similar to I2C, which allows devices with different speed capabilities to coexist on the bus. A clock-low extension is used during a transfer in order to allow slower slave devices to communicate with faster masters. The slave may temporarily hold the SCL line LOW to extend the clock low period, effectively decreasing the serial clock frequency.

#### 15.3.3. SCL Low Timeout

If the SCL line is held low by a slave device on the bus, no further communication is possible. Furthermore, the master cannot force the SCL line high to correct the error condition. To solve this problem, the SMBus protocol specifies that devices participating in a transfer must detect any clock cycle held low longer than 25 ms as a "timeout" condition. Devices that have detected the timeout condition must reset the communication no later than 10 ms after detecting the timeout condition.

When the SMBTOE bit in SMB0CF is set, Timer 3 is used to detect SCL low timeouts. Timer 3 is forced to reload when SCL is high, and allowed to count when SCL is low. With Timer 3 enabled and configured to overflow after 25 ms (and SMBTOE set), the Timer 3 interrupt service routine can be used to reset (disable and re-enable) the SMBus in the event of an SCL low timeout.

#### 15.3.4. SCL High (SMBus Free) Timeout

The SMBus specification stipulates that if the SCL and SDA lines remain high for more that 50 µs, the bus is designated as free. When the SMBFTE bit in SMB0CF is set, the bus will be considered free if SCL and SDA remain high for more than 10 SMBus clock source periods. If the SMBus is waiting to generate a Master START, the START will be generated following this timeout. Note that a clock source is required for free timeout detection, even in a slave-only implementation.

#### 15.4. Using the SMBus

The SMBus can operate in both Master and Slave modes. The interface provides timing and shifting control for serial transfers; higher level protocol is determined by user software. The SMBus interface provides the following application-independent features:

- Byte-wise serial data transfers

- Clock signal generation on SCL (Master Mode only) and SDA data synchronization

- Timeout/bus error recognition, as defined by the SMB0CF configuration register

- START/STOP timing, detection, and generation

- Bus arbitration

- Interrupt generation

- Status information

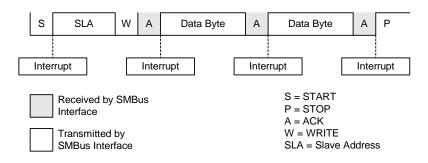

SMBus interrupts are generated for each data byte or slave address that is transferred. When transmitting, this interrupt is generated after the ACK cycle so that software may read the received ACK value; when receiving data, this interrupt is generated before the ACK cycle so that software may define the outgoing ACK value. See **Section "15.5. SMBus Transfer Modes" on page 146** for more details on transmission sequences.

Interrupts are also generated to indicate the beginning of a transfer when a master (START generated), or the end of a transfer when a slave (STOP detected). Software should read the SMB0CN (SMBus Control register) to find the cause of the SMBus interrupt. The SMB0CN register is described in **Section "15.4.2. SMB0CN Control Register" on page 143**; Table 15.4 provides a quick SMB0CN decoding reference.

Figure 15.5. Typical Master Transmitter Sequence

|                | Valu                               | es F                | Read | b                   |                                                              |                                                                                                 |     | /alue<br>Vritte |   |

|----------------|------------------------------------|---------------------|------|---------------------|--------------------------------------------------------------|-------------------------------------------------------------------------------------------------|-----|-----------------|---|

| Mode           | Status<br>Vector                   | Current SMbus State |      | Current SMbus State | Typical Response Options                                     | STA                                                                                             | STo | ACK             |   |

|                | 1110                               | 0                   | 0    | х                   | A master START was generated.                                | Load slave address + R/W into SMB0DAT.                                                          | 0   | 0               | Х |

|                |                                    | 0                   | 0    | 0                   | A master data or address byte                                | Set STA to restart transfer.                                                                    | 1   | 0               | Х |

| er             |                                    | Ŭ                   | Ū    | Ŭ                   | was transmitted; NACK received.                              | Abort transfer.                                                                                 | 0   | 1               | Х |

| nsmitte        |                                    |                     |      |                     | -                                                            | Load next data byte into SMB0DAT.                                                               | 0   | 0               | Х |

| r Tra          | Master Transmitter<br>0011<br>0012 |                     |      |                     |                                                              | End transfer with STOP.                                                                         | 0   | 1               | Х |

| Maste          |                                    | 0                   | 0    | 1                   | A master data or address byte was transmitted; ACK received. | End transfer with STOP and start another transfer.                                              | 1   | 1               | Х |

|                |                                    |                     |      |                     |                                                              | Send repeated START.                                                                            | 1   | 0               | Х |

|                |                                    |                     |      |                     |                                                              | Switch to Master Receiver<br>Mode (clear SI without writ-<br>ing new data to SMB0DAT).          | 0   | 0               | Х |

|                |                                    |                     |      |                     | -                                                            | Acknowledge received byte;<br>Read SMB0DAT.                                                     | 0   | 0               | 1 |

|                |                                    |                     |      |                     |                                                              | Send NACK to indicate last byte, and send STOP.                                                 | 0   | 1               | 0 |

|                |                                    |                     |      |                     |                                                              | Send NACK to indicate last<br>byte, and send STOP fol-<br>lowed by START.                       | 1   | 1               | 0 |

| ceiver         |                                    |                     |      |                     |                                                              | Send ACK followed by repeated START.                                                            | 1   | 0               | 1 |

| aster Receiver | 1000                               | 1                   | 0    | х                   | A master data byte was received;<br>ACK requested.           | Send NACK to indicate last<br>byte, and send repeated<br>START.                                 | 1   | 0               | 0 |

| Ma             |                                    |                     |      |                     |                                                              | Send ACK and switch to<br>Master Transmitter Mode<br>(write to SMB0DAT before<br>clearing SI).  | 0   | 0               | 1 |

|                |                                    |                     |      |                     |                                                              | Send NACK and switch to<br>Master Transmitter Mode<br>(write to SMB0DAT before<br>clearing SI). | 0   | 0               | 0 |

Table 15.4. SMBus Status Decoding

# C8051F330/1/2/3/4/5

|                   | Valu             | es I  | Read    | ł   |                                                                                       |                                                                                     |            | /alue<br>Vritte |     |   |

|-------------------|------------------|-------|---------|-----|---------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------|------------|-----------------|-----|---|

| Mode              | Status<br>Vector | ACKRQ | ARBLOST | ACK | Current SMbus State                                                                   | Typical Response Options                                                            | STA        | STo             | ACK |   |

| Ŀ                 |                  | 0     | 0       | 0   | A slave byte was transmitted;<br>NACK received.                                       | No action required (expect-<br>ing STOP condition).                                 | 0          | 0               | Х   |   |

| Slave Transmitter | 0100 0           | 0     | 0       | 1   | A slave byte was transmitted;<br>ACK received.                                        | Load SMB0DAT with next data byte to transmit.                                       | 0          | 0               | Х   |   |

| 'e Trar           |                  | 0     | 1       | х   | A Slave byte was transmitted;<br>error detected.                                      | No action required (expect-<br>ing Master to end transfer).                         | 0          | 0               | Х   |   |

| Slav              | 0101             | 0     | x       | x   | An illegal STOP or bus error was detected while a Slave Transmission was in progress. | Clear STO.                                                                          | 0          | 0               | Х   |   |

|                   |                  | 1     | 0       | x   | A slave address was received;                                                         | Acknowledge received address.                                                       | 0          | 0               | 1   |   |

|                   |                  | 1     |         | ^   | ACK requested.                                                                        | Do not acknowledge received address.                                                | 0          | 0               | 0   |   |

|                   | 0010             |       |         |     |                                                                                       | Acknowledge received address.                                                       | 0          | 0               | 1   |   |

|                   |                  | 1     | 1       | х   | Lost arbitration as master; slave address received; ACK                               | Do not acknowledge received address.                                                | 0          | 0               | 0   |   |

|                   |                  |       |         |     | requested.                                                                            | Reschedule failed transfer;<br>do not acknowledge received<br>address.              | 1          | 0               | 0   |   |

| er                | 0010             | 0     | 1       | х   | Lost arbitration while attempting a                                                   | Abort failed transfer.                                                              | 0          | 0               | Х   |   |

| ceive             | 0010             | Ŭ     |         |     | repeated START.                                                                       | Reschedule failed transfer.                                                         | 1          | 0               | Х   |   |

| Slave Receiver    |                  | 1     | 1       | х   | Lost arbitration while attempting a STOP.                                             | No action required (transfer complete/aborted).                                     | 0          | 0               | 0   |   |

| Sla               | 0001             | 0001  | 0       | 0   | x                                                                                     | A STOP was detected while<br>addressed as a Slave Transmitter<br>or Slave Receiver. | Clear STO. | 0               | 0   | Х |

|                   |                  | 0     | 1       | x   | Lost arbitration due to a detected                                                    | Abort transfer.                                                                     | 0          | 0               | Х   |   |

|                   |                  | Ŭ     |         |     | STOP.                                                                                 | Reschedule failed transfer.                                                         | 1          | 0               | Х   |   |

|                   |                  | 1     | 0       | x   | A slave byte was received; ACK                                                        | Acknowledge received byte;<br>Read SMB0DAT.                                         | 0          | 0               | 1   |   |

|                   | 0000             |       |         |     | requested.                                                                            | Do not acknowledge received byte.                                                   | 0          | 0               | 0   |   |

|                   |                  | 1     | 1       | х   | Lost arbitration while transmitting                                                   | Abort failed transfer.                                                              | 0          | 0               | 0   |   |

|                   |                  |       |         |     | a data byte as master.                                                                | Reschedule failed transfer.                                                         | 1          | 0               | 0   |   |

Table 15.4. SMBus Status Decoding

#### 17.2. SPI0 Master Mode Operation

A SPI master device initiates all data transfers on a SPI bus. SPI0 is placed in master mode by setting the Master Enable flag (MSTEN, SPI0CN.6). Writing a byte of data to the SPI0 data register (SPI0DAT) when in master mode writes to the transmit buffer. If the SPI shift register is empty, the byte in the transmit buffer is moved to the shift register, and a data transfer begins. The SPI0 master immediately shifts out the data serially on the MOSI line while providing the serial clock on SCK. The SPIF (SPI0CN.7) flag is set to logic 1 at the end of the transfer. If interrupts are enabled, an interrupt request is generated when the SPIF flag is set. While the SPI0 master transfers data to a slave on the MOSI line, the addressed SPI slave device simultaneously transfers the contents of its shift register to the SPI master on the MISO line in a full-duplex operation. Therefore, the SPIF flag serves as both a transmit-complete and receive-data-ready flag. The data byte received from the slave is transferred MSB-first into the master's shift register. When a byte is fully shifted into the register, it is moved to the receive buffer where it can be read by the processor by reading SPI0DAT.

When configured as a master, SPI0 can operate in one of three different modes: multi-master mode, 3-wire single-master mode, and 4-wire single-master mode. The default, multi-master mode is active when NSS-MD1 (SPI0CN.3) = 0 and NSSMD0 (SPI0CN.2) = 1. In this mode, NSS is an input to the device, and is used to disable the master SPI0 when another master is accessing the bus. When NSS is pulled low in this mode, MSTEN (SPI0CN.6) and SPIEN (SPI0CN.0) are set to 0 to disable the SPI master device, and a Mode Fault is generated (MODF, SPI0CN.5 = 1). Mode Fault will generate an interrupt if enabled. SPI0 must be manually re-enabled in software under these circumstances. In multi-master systems, devices will typically default to being slave devices while they are not acting as the system master device. In multi-master mode, slave devices can be addressed individually (if needed) using general-purpose I/O pins. Figure 17.2 shows a connection diagram between two master devices in multiple-master mode.

3-wire single-master mode is active when NSSMD1 (SPI0CN.3) = 0 and NSSMD0 (SPI0CN.2) = 0. In this mode, NSS is not used, and is not mapped to an external port pin through the crossbar. Any slave devices that must be addressed in this mode should be selected using general-purpose I/O pins. Figure 17.3 shows a connection diagram between a master device in 3-wire master mode and a slave device.

4-wire single-master mode is active when NSSMD1 (SPI0CN.3) = 1. In this mode, NSS is configured as an output pin, and can be used as a slave-select signal for a single SPI device. In this mode, the output value of NSS is controlled (in software) with the bit NSSMD0 (SPI0CN.2). Additional slave devices can be addressed using general-purpose I/O pins. Figure 17.4 shows a connection diagram for a master device in 4-wire master mode and two slave devices.

# C8051F330/1/2/3/4/5

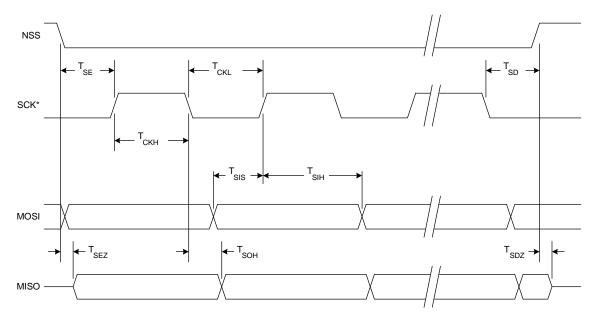

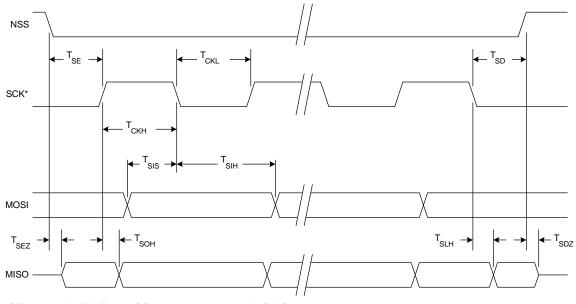

\* SCK is shown for CKPOL = 0. SCK is the opposite polarity for CKPOL = 1.

\* SCK is shown for CKPOL = 0. SCK is the opposite polarity for CKPOL = 1.

# Figure 17.11. SPI Slave Timing (CKPHA = 1)

# 18. Timers

Each MCU includes four counter/timers: two are 16-bit counter/timers compatible with those found in the standard 8051, and two are 16-bit auto-reload timer for use with the ADC, SMBus, or for general purpose use. These timers can be used to measure time intervals, count external events and generate periodic interrupt requests. Timer 0 and Timer 1 are nearly identical and have four primary modes of operation. Timer 2 and Timer 3 offer 16-bit and split 8-bit timer functionality with auto-reload

| Timer 0 and Timer 1 Modes:        | Timer 2 Modes:                    | Timer 3 Modes:                    |  |  |

|-----------------------------------|-----------------------------------|-----------------------------------|--|--|

| 13-bit counter/timer              | 16-bit timer with auto-reload     | 16-bit timer with auto-reload     |  |  |

| 16-bit counter/timer              |                                   |                                   |  |  |

| 8-bit counter/timer with auto-    |                                   |                                   |  |  |

| reload                            | Two 8-bit timers with auto-reload | Two 8-bit timers with auto-reload |  |  |

| Two 8-bit counter/timers (Timer 0 |                                   |                                   |  |  |

| only)                             |                                   |                                   |  |  |

Timers 0 and 1 may be clocked by one of five sources, determined by the Timer Mode Select bits (T1M–T0M) and the Clock Scale bits (SCA1–SCA0). The Clock Scale bits define a pre-scaled clock from which Timer 0 and/or Timer 1 may be clocked (See SFR Definition 18.3 for pre-scaled clock selection).

Timer 0/1 may then be configured to use this pre-scaled clock signal or the system clock. Timer 2 and Timer 3 may be clocked by the system clock, the system clock divided by 12, or the external oscillator clock source divided by 8.

Timer 0 and Timer 1 may also be operated as counters. When functioning as a counter, a counter/timer register is incremented on each high-to-low transition at the selected input pin (T0 or T1). Events with a frequency of up to one-fourth the system clock frequency can be counted. The input signal need not be periodic, but it should be held at a given level for at least two full system clock cycles to ensure the level is properly sampled.

#### 18.1. Timer 0 and Timer 1

Each timer is implemented as a 16-bit register accessed as two separate bytes: a low byte (TL0 or TL1) and a high byte (TH0 or TH1). The Counter/Timer Control register (TCON) is used to enable Timer 0 and Timer 1 as well as indicate status. Timer 0 interrupts can be enabled by setting the ET0 bit in the IE register (Section **\*9.3.5. Interrupt Register Descriptions**" on page **89**); Timer 1 interrupts can be enabled by setting the ET1 bit in the IE register (Section **9.3.5**). Both counter/timers operate in one of four primary modes selected by setting the Mode Select bits T1M1–T0M0 in the Counter/Timer Mode register (TMOD). Each timer can be configured independently. Each operating mode is described below.

#### 18.1.1. Mode 0: 13-bit Counter/Timer

Timer 0 and Timer 1 operate as 13-bit counter/timers in Mode 0. The following describes the configuration and operation of Timer 0. However, both timers operate identically, and Timer 1 is configured in the same manner as described for Timer 0.

The TH0 register holds the eight MSBs of the 13-bit counter/timer. TL0 holds the five LSBs in bit positions TL0.4–TL0.0. The three upper bits of TL0 (TL0.7–TL0.5) are indeterminate and should be masked out or ignored when reading. As the 13-bit timer register increments and overflows from 0x1FFF (all ones) to 0x0000, the timer overflow flag TF0 (TCON.5) is set and an interrupt will occur if Timer 0 interrupts are enabled.

| R/W      | R/W                                                                                                | R/W        | R/W                                          | R/W                            | R/W          | R/W       | R/W  | Reset Value         |  |

|----------|----------------------------------------------------------------------------------------------------|------------|----------------------------------------------|--------------------------------|--------------|-----------|------|---------------------|--|

| GATE1    | C/T1                                                                                               | T1M1       | T1M0                                         | GATE0                          | C/T0         | T0M1      | T0M0 | 0000000             |  |

| Bit7     | Bit6                                                                                               | Bit5       | Bit4                                         | Bit3                           | Bit2         | Bit1      | Bit0 | SFR Address<br>0x89 |  |

| Bit7:    | GATE1: T                                                                                           | imer 1 Gat | e Control.                                   |                                |              |           |      |                     |  |

|          | 0: Timer 1 enabled when $TR1 = 1$ irrespective of /INT1 logic level.                               |            |                                              |                                |              |           |      |                     |  |

|          | 1: Timer 1 enabled only when TR1 = 1 AND /INT1 is active as defined by bit IN1PL in regis          |            |                                              |                                |              |           |      |                     |  |

|          | ter IT01CF (see SFR Definition 9.11).                                                              |            |                                              |                                |              |           |      |                     |  |

| Bit6:    | C/T1: Counter/Timer 1 Select.                                                                      |            |                                              |                                |              |           |      |                     |  |

|          | 0: Timer Function: Timer 1 incremented by clock defined by T1M bit (CKCON.3).                      |            |                                              |                                |              |           |      |                     |  |

|          | 1: Counter Function: Timer 1 incremented by high-to-low transitions on external input pin          |            |                                              |                                |              |           |      |                     |  |

|          | (T1).                                                                                              |            |                                              |                                |              |           |      |                     |  |

| Bits5–4: |                                                                                                    |            | 1 Mode Selec                                 |                                |              |           |      |                     |  |

|          | These bits                                                                                         | select the | e Timer 1 opera                              | ation mode.                    |              |           |      |                     |  |

|          | T1M1                                                                                               | T1M0       | Mode                                         |                                |              |           | 1    |                     |  |

|          | 0                                                                                                  | 0          | Мос                                          | Mode 0: 13-bit counter/timer   |              |           |      |                     |  |

|          | 0                                                                                                  | 1          | Mode 1: 16-bit counter/timer                 |                                |              |           |      |                     |  |

|          | 1                                                                                                  | 0          | Mode 2: 8-bit counter/timer with auto-reload |                                |              |           |      |                     |  |

|          | 1                                                                                                  | 1          | Mode 3: Timer 1 inactive                     |                                |              |           |      |                     |  |

| Bit3:    | CATEO: Timer O Cote Control                                                                        |            |                                              |                                |              |           |      |                     |  |

|          | GATE0: Timer 0 Gate Control.<br>0: Timer 0 enabled when TR0 = 1 irrespective of /INT0 logic level. |            |                                              |                                |              |           |      |                     |  |

|          | 1: Timer 0 enabled when $TR0 = 1$ AND /INT0 is active as defined by bit IN0PL in regis-            |            |                                              |                                |              |           |      |                     |  |

|          | ter IT01CF (see SFR Definition 9.11).                                                              |            |                                              |                                |              |           |      |                     |  |

| Bit2:    | C/T0: Counter/Timer Select.                                                                        |            |                                              |                                |              |           |      |                     |  |

|          | 0: Timer Function: Timer 0 incremented by clock defined by T0M bit (CKCON.2).                      |            |                                              |                                |              |           |      |                     |  |

|          | 1: Counter Function: Timer 0 incremented by high-to-low transitions on external input pin          |            |                                              |                                |              |           |      |                     |  |

|          | (T0).                                                                                              |            |                                              |                                |              |           |      |                     |  |

| Bits1–0: | T0M1–T0M0: Timer 0 Mode Select.                                                                    |            |                                              |                                |              |           |      |                     |  |

|          | These bits select the Timer 0 operation mode.                                                      |            |                                              |                                |              |           |      |                     |  |

|          | T0M1                                                                                               | T0M0       | Mode                                         |                                |              |           |      |                     |  |

|          | 0                                                                                                  | 0          | Mod                                          | e 0: 13-bit c                  | ounter/time  | r         |      |                     |  |

|          | 0                                                                                                  | 1          | Mod                                          | e 1: 16-bit c                  | ounter/time  | r         |      |                     |  |

|          | 0                                                                                                  | -          |                                              |                                |              |           |      |                     |  |

|          | 1                                                                                                  | 0          | Mode 2: 8-b                                  | it counter/tin                 | ner with aut | to-reload |      |                     |  |

|          | -                                                                                                  | 0          |                                              | it counter/tin<br>3: Two 8-bit |              |           |      |                     |  |

|          | 1                                                                                                  | -          |                                              |                                |              |           |      |                     |  |

# SFR Definition 18.2. TMOD: Timer Mode

182

Note that the 8-bit offset held in PCA0CPH2 is compared to the upper byte of the 16-bit PCA counter. This offset value is the number of PCA0L overflows before a reset. Up to 256 PCA clocks may pass before the first PCA0L overflow occurs, depending on the value of the PCA0L when the update is performed. The total offset is then given (in PCA clocks) by Equation 19.6, where PCA0L is the value of the PCA0L register at the time of the update.

$Offset = (256 \times PCA0CPL2) + (256 - PCA0L)$

#### Equation 19.6. Watchdog Timer Offset in PCA Clocks

The WDT reset is generated when PCA0L overflows while there is a match between PCA0CPH2 and PCA0H. Software may force a WDT reset by writing a '1' to the CCF2 flag (PCA0CN.2) while the WDT is enabled.

#### 19.3.2. Watchdog Timer Usage

To configure the WDT, perform the following tasks:

- Disable the WDT by writing a '0' to the WDTE bit.

- Select the desired PCA clock source (with the CPS2–CPS0 bits).

- Load PCA0CPL2 with the desired WDT update offset value.

- Configure the PCA Idle mode (set CIDL if the WDT should be suspended while the CPU is in Idle mode).

- Enable the WDT by setting the WDTE bit to '1'.

- Write a value to PCA0CPH2 to reload the WDT.

The PCA clock source and Idle mode select cannot be changed while the WDT is enabled. The watchdog timer is enabled by setting the WDTE or WDLCK bits in the PCA0MD register. When WDLCK is set, the WDT cannot be disabled until the next system reset. If WDLCK is not set, the WDT is disabled by clearing the WDTE bit.

The WDT is enabled following any reset. The PCA0 counter clock defaults to the system clock divided by 12, PCA0L defaults to 0x00, and PCA0CPL2 defaults to 0x00. Using Equation 19.6, this results in a WDT timeout interval of 256 PCA clock cycles, or 3072 system clock cycles. Table 19.4 lists some example timeout intervals for typical system clocks.