Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Not For New Designs                                             |

|----------------------------|-----------------------------------------------------------------|

| Core Processor             | 8051                                                            |

| Core Size                  | 8-Bit                                                           |

| Speed                      | 25MHz                                                           |

| Connectivity               | SMBus (2-Wire/I <sup>2</sup> C), SPI, UART/USART                |

| Peripherals                | POR, PWM, WDT                                                   |

| Number of I/O              | 17                                                              |

| Program Memory Size        | 4KB (4K x 8)                                                    |

| Program Memory Type        | FLASH                                                           |

| EEPROM Size                | -                                                               |

| RAM Size                   | 768 x 8                                                         |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 3.6V                                                     |

| Data Converters            | -                                                               |

| Oscillator Type            | Internal                                                        |

| Operating Temperature      | -40°C ~ 85°C (TA)                                               |

| Mounting Type              | Surface Mount                                                   |

| Package / Case             | 20-VFQFN Exposed Pad                                            |

| Supplier Device Package    | 20-QFN (4x4)                                                    |

| Purchase URL               | https://www.e-xfl.com/product-detail/silicon-labs/c8051f333-gmr |

|                            |                                                                 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| 18.2.2.8-bit Timers with Auto-Reload     |     |

|------------------------------------------|-----|

| 18.3.Timer 3                             | 189 |

| 18.3.1.16-bit Timer with Auto-Reload     | 189 |

| 18.3.2.8-bit Timers with Auto-Reload     | 190 |

| 19. Programmable Counter Array           | 193 |

| 19.1.PCA Counter/Timer                   |     |

| 19.2.Capture/Compare Modules             |     |

| 19.2.1.Edge-triggered Capture Mode       |     |

| 19.2.2.Software Timer (Compare) Mode     |     |

| 19.2.3.High-Speed Output Mode            |     |

| 19.2.4.Frequency Output Mode             |     |

| 19.2.5.8-Bit Pulse Width Modulator Mode  |     |

| 19.2.6.16-Bit Pulse Width Modulator Mode | 201 |

| 19.3.Watchdog Timer Mode                 | 201 |

| 19.3.1.Watchdog Timer Operation          |     |

| 19.3.2.Watchdog Timer Usage              |     |

| 19.4.Register Descriptions for PCA       |     |

| 20. C2 Interface                         |     |

| 20.1.C2 Interface Registers              |     |

| 20.2.C2 Pin Sharing                      | 211 |

| 5                                        |     |

| Figure 10.2. Power-On and VDD Monitor Reset Timing                             | . 98 |

|--------------------------------------------------------------------------------|------|

| 11. Flash Memory                                                               |      |

| Figure 11.1. Flash Program Memory Map                                          | 105  |

| 12. External RAM                                                               |      |

| 13. Oscillators                                                                |      |

| Figure 13.1. Oscillator Diagram                                                |      |

| Figure 13.2. External 32.768 kHz Quartz Crystal Oscillator Connection Diagram. | 119  |

| 14. Port Input/Output                                                          |      |

| Figure 14.1. Port I/O Functional Block Diagram                                 |      |

| Figure 14.2. Port I/O Cell Block Diagram                                       |      |

| Figure 14.3. Crossbar Priority Decoder with No Pins Skipped                    |      |

| Figure 14.4. Crossbar Priority Decoder with Crystal Pins Skipped               | 126  |

| 15. SMBus                                                                      |      |

| Figure 15.1. SMBus Block Diagram                                               |      |

| Figure 15.2. Typical SMBus Configuration                                       |      |

| Figure 15.3. SMBus Transaction                                                 |      |

| Figure 15.4. Typical SMBus SCL Generation                                      |      |

| Figure 15.5. Typical Master Transmitter Sequence                               |      |

| Figure 15.6. Typical Master Receiver Sequence                                  |      |

| Figure 15.7. Typical Slave Receiver Sequence                                   | 149  |

| Figure 15.8. Typical Slave Transmitter Sequence                                | 150  |

| 16.UART0                                                                       |      |

| Figure 16.1. UARTO Block Diagram                                               |      |

| Figure 16.2. UARTO Baud Rate Logic                                             |      |

| Figure 16.3. UART Interconnect Diagram                                         |      |

| Figure 16.4. 8-Bit UART Timing Diagram                                         |      |

| Figure 16.5. 9-Bit UART Timing Diagram                                         |      |

| Figure 16.6. UART Multi-Processor Mode Interconnect Diagram                    | 157  |

| 17. Enhanced Serial Peripheral Interface (SPI0)                                | 400  |

| Figure 17.1. SPI Block Diagram                                                 |      |

| Figure 17.2. Multiple-Master Mode Connection Diagram                           | 166  |

| Figure 17.3. 3-Wire Single Master and 3-Wire Single Slave Mode                 |      |

| Connection Diagram166                                                          |      |

| Figure 17.4. 4-Wire Single Master Mode and 4-Wire Slave Mode                   |      |

| Connection Diagram166                                                          | 400  |

| Figure 17.5. Master Mode Data/Clock Timing                                     | 168  |

| Figure 17.6. Slave Mode Data/Clock Timing (CKPHA = 0)                          |      |

| Figure 17.7. Slave Mode Data/Clock Timing (CKPHA = 1)                          |      |

| Figure 17.8. SPI Master Timing (CKPHA = 0)                                     |      |

| Figure 17.9. SPI Master Timing (CKPHA = 1)                                     |      |

| Figure 17.10. SPI Slave Timing (CKPHA = 0)                                     | 174  |

| Figure 17.11. SPI Slave Timing (CKPHA = 1)                                     | 1/4  |

| 18. Timers                                                                     | 470  |

| Figure 18.1. T0 Mode 0 Block Diagram                                           |      |

| Figure 18.2. T0 Mode 2 Block Diagram                                           | 179  |

## List of Registers

| SFR | Definition 5.1. AMX0P: AMUX0 Positive Channel Select         | 47 |

|-----|--------------------------------------------------------------|----|

| SFR | Definition 5.2. AMX0N: AMUX0 Negative Channel Select         | 48 |

| SFR | Definition 5.3. ADC0CF: ADC0 Configuration                   | 49 |

| SFR | Definition 5.4. ADC0H: ADC0 Data Word MSB                    | 49 |

| SFR | Definition 5.5. ADC0L: ADC0 Data Word LSB                    | 49 |

| SFR | Definition 5.6. ADC0CN: ADC0 Control                         | 50 |

| SFR | Definition 5.7. ADC0GTH: ADC0 Greater-Than Data High Byte    | 51 |

| SFR | Definition 5.8. ADC0GTL: ADC0 Greater-Than Data Low Byte     | 51 |

| SFR | Definition 5.9. ADC0LTH: ADC0 Less-Than Data High Byte       | 52 |

| SFR | Definition 5.10. ADC0LTL: ADC0 Less-Than Data Low Byte       | 52 |

|     | Definition 6.1. IDA0CN: IDA0 Control                         |    |

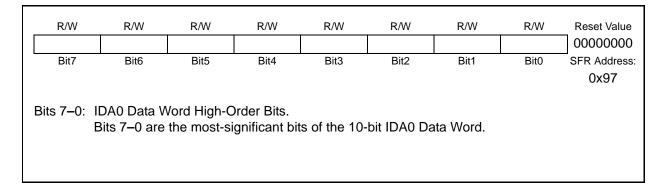

|     | Definition 6.2. IDA0H: IDA0 Data Word MSB                    |    |

|     | Definition 6.3. IDA0L: IDA0 Data Word LSB                    |    |

|     | Definition 7.1. REF0CN: Reference Control                    |    |

|     | Definition 8.1. CPT0CN: Comparator0 Control                  |    |

|     | Definition 8.2. CPT0MX: Comparator0 MUX Selection            |    |

|     | Definition 8.3. CPT0MD: Comparator0 Mode Selection           |    |

|     | Definition 9.1. DPL: Data Pointer Low Byte                   |    |

|     | Definition 9.2. DPH: Data Pointer High Byte                  |    |

|     | Definition 9.3. SP: Stack Pointer                            |    |

| SFR | Definition 9.4. PSW: Program Status Word                     | 84 |

|     | Definition 9.5. ACC: Accumulator                             |    |

|     | Definition 9.6. B: B Register                                |    |

|     | Definition 9.7. IE: Interrupt Enable                         |    |

|     | Definition 9.8. IP: Interrupt Priority                       |    |

|     | Definition 9.9. EIE1: Extended Interrupt Enable 1            |    |

|     | Definition 9.10. EIP1: Extended Interrupt Priority 1         |    |

| SFR | Definition 9.11. IT01CF: INT0/INT1 Configuration             | 93 |

|     | Definition 9.12. PCON: Power Control                         |    |

|     | Definition 10.1. VDM0CN: VDD Monitor Control                 |    |

| SFR | Definition 10.2. RSTSRC: Reset Source                        | 01 |

| SFR | Definition 11.1. PSCTL: Program Store R/W Control            | 80 |

|     | Definition 11.2. FLKEY: Flash Lock and Key                   |    |

|     | Definition 11.3. FLSCL: Flash Scale                          |    |

|     | Definition 12.1. EMI0CN: External Memory Interface Control   |    |

|     | Definition 13.1. OSCICL: Internal H-F Oscillator Calibration |    |

|     | Definition 13.2. OSCICN: Internal H-F Oscillator Control     |    |

|     | Definition 13.3. OSCLCN: Internal L-F Oscillator Control     |    |

|     | Definition 13.4. OSCXCN: External Oscillator Control         |    |

|     | Definition 13.5. CLKSEL: Clock Select                        |    |

|     | Definition 14.1. XBR0: Port I/O Crossbar Register 0          |    |

|     | Definition 14.2. XBR1: Port I/O Crossbar Register 1          |    |

| SFR | Definition 14.3. P0: Port0                                   | 30 |

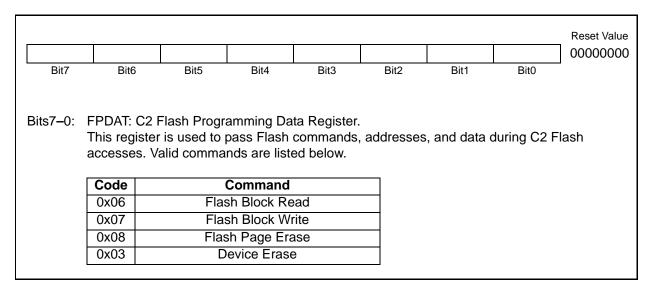

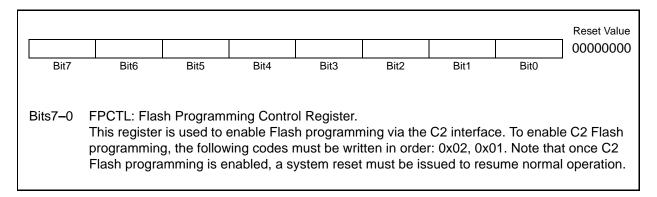

| C2 Register Definition 20.4. FPCTL: C2 Flash Programming Cor | trol |

|--------------------------------------------------------------|------|

| C2 Register Definition 20.5. FPDAT: C2 Flash Programming Dat | a    |

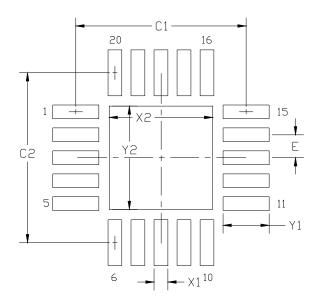

Figure 4.3. QFN-20 Recommended PCB Land Pattern

| Dimension | Min  | Max  |  |  |  |

|-----------|------|------|--|--|--|

| C1        | 3.70 |      |  |  |  |

| C2        | 3.70 |      |  |  |  |

| E         | 0.50 |      |  |  |  |

| X1        | 0.20 | 0.30 |  |  |  |

| Dimension | Min  | Max  |

|-----------|------|------|

| X2        | 2.15 | 2.25 |

| Y1        | 0.90 | 1.00 |

| Y2        | 2.15 | 2.25 |

#### Notes:

General

- 1. All dimensions shown are in millimeters (mm) unless otherwise noted.

- 2. Dimensioning and Tolerancing is per the ANSI Y14.5M-1994 specification.

- 3. This Land Pattern Design is based on the IPC-7351 guidelines.

#### Solder Mask Design

4. All metal pads are to be non-solder mask defined (NSMD). Clearance between the solder mask and the metal pad is to be  $60 \ \mu m$  minimum, all the way around the pad.

#### Stencil Design

- **5.** A stainless steel, laser-cut and electro-polished stencil with trapezoidal walls should be used to assure good solder paste release.

- 6. The stencil thickness should be 0.125 mm (5 mils).

- 7. The ratio of stencil aperture to land pad size should be 1:1 for all perimeter pins.

- **8.** A 2x2 array of 0.95 mm openings on a 1.1 mm pitch should be used for the center pad to assure the proper paste volume (71% Paste Coverage).

Card Assembly

- **9.** A No-Clean, Type-3 solder paste is recommended.

- **10.** The recommended card reflow profile is per the JEDEC/IPC J-STD-020 specification for Small Body Components.

measured from '0' to VREF x 1023/1024. Example codes are shown below for both right-justified and left-justified data. Unused bits in the ADC0H and ADC0L registers are set to '0'.

| Input Voltage    | Right-Justified ADC0H:ADC0L<br>(AD0LJST = 0) | Left-Justified ADC0H:ADC0L<br>(AD0LJST = 1) |

|------------------|----------------------------------------------|---------------------------------------------|

| VREF x 1023/1024 | 0x03FF                                       | 0xFFC0                                      |

| VREF x 512/1024  | 0x0200                                       | 0x8000                                      |

| VREF x 256/1024  | 0x0100                                       | 0x4000                                      |

| 0                | 0x0000                                       | 0x0000                                      |

When in Differential Mode, conversion codes are represented as 10-bit signed 2's complement numbers. Inputs are measured from –VREF to VREF x 511/512. Example codes are shown below for both right-justified and left-justified data. For right-justified data, the unused MSBs of ADC0H are a sign-extension of the data word. For left-justified data, the unused LSBs in the ADC0L register are set to '0'.

| Input Voltage   | Right-Justified ADC0H:ADC0L<br>(AD0LJST = 0) | Left-Justified ADC0H:ADC0L<br>(AD0LJST = 1) |

|-----------------|----------------------------------------------|---------------------------------------------|

| VREF x 511/512  | 0x01FF                                       | 0x7FC0                                      |

| VREF x 256/512  | 0x0100                                       | 0x4000                                      |

| 0               | 0x0000                                       | 0x0000                                      |

| –VREF x 256/512 | 0xFF00                                       | 0xC000                                      |

| –VREF           | 0xFE00                                       | 0x8000                                      |

**Important Note About ADC0 Input Configuration:** Port pins selected as ADC0 inputs should be configured as analog inputs, and should be skipped by the Digital Crossbar. To configure a Port pin for analog input, set to '0' the corresponding bit in register PnMDIN (for n = 0,1). To force the Crossbar to skip a Port pin, set to '1' the corresponding bit in register PnSKIP (for n = 0,1). See **Section "14. Port Input/Output" on page 123** for more Port I/O configuration details.

### 5.2. Temperature Sensor

The typical temperature sensor transfer function is shown in Figure 5.2. The output voltage ( $V_{TEMP}$ ) is the positive ADC input when the temperature sensor is selected by bits AMX0P4–0 in register AMX0P.

| R/W       | R/W                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | R/W                                                                                                                                                                                                                           | R/W                                                                                                                                                                      | R                                                                                                                                        | R                       | R/W  | R/W  | Reset Value  |

|-----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------|-------------------------|------|------|--------------|

| IDA0EN    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | IDA0CM                                                                                                                                                                                                                        |                                                                                                                                                                          | -                                                                                                                                        | -                       | IDA0 | OMD  | 01110010     |

| Bit7      | Bit6                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | Bit5                                                                                                                                                                                                                          | Bit4                                                                                                                                                                     | Bit3                                                                                                                                     | Bit2                    | Bit1 | Bit0 | SFR Address: |

|           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                                                                                                               |                                                                                                                                                                          |                                                                                                                                          |                         |      |      | 0xB9         |

| Bits 3–2: | IDA0EN: IDA<br>0: IDA0 Disa<br>1: IDA0 Enal<br>IDA0CM[2:0<br>000: DAC ou<br>010: DAC ou<br>010: DAC ou<br>100: DAC ou<br>101: DAC ou<br>101: DAC ou<br>111: DAC ou | ibled.<br>bled.<br>]: IDA0 Upd<br>itput update<br>itput update<br>itput update<br>itput update<br>itput update<br>itput update<br>itput update<br>itput update<br>ad = 00b. W<br>:0]: IDA0 Ou<br>ull-scale ou<br>ull-scale ou | es on Timer<br>es on Timer<br>es on Timer<br>es on Timer<br>es on rising<br>es on falling<br>es on any ed<br>s on write t<br>drite = don't<br>utput Mode<br>tput current | 0 overflow.<br>1 overflow.<br>2 overflow.<br>3 overflow.<br>edge of CN<br>edge of CNV<br>dge of CNV<br>o IDA0H.<br>care.<br>Select bits. | VSTR.<br>IVSTR.<br>STR. |      |      |              |

## SFR Definition 6.1. IDA0CN: IDA0 Control

## SFR Definition 6.2. IDA0H: IDA0 Data Word MSB

program memory space for non-volatile data storage. Refer to **Section "11. Flash Memory" on page 103** for further details.

| Mnemonic          | Description                              | Bytes | Clock<br>Cycles |

|-------------------|------------------------------------------|-------|-----------------|

|                   | Arithmetic Operations                    |       |                 |

| ADD A, Rn         | Add register to A                        | 1     | 1               |

| ADD A, direct     | Add direct byte to A                     | 2     | 2               |

| ADD A, @Ri        | Add indirect RAM to A                    | 1     | 2               |

| ADD A, #data      | Add immediate to A                       | 2     | 2               |

| ADDC A, Rn        | Add register to A with carry             | 1     | 1               |

| ADDC A, direct    | Add direct byte to A with carry          | 2     | 2               |

| ADDC A, @Ri       | Add indirect RAM to A with carry         | 1     | 2               |

| ADDC A, #data     | Add immediate to A with carry            | 2     | 2               |

| SUBB A, Rn        | Subtract register from A with borrow     | 1     | 1               |

| SUBB A, direct    | Subtract direct byte from A with borrow  | 2     | 2               |

| SUBB A, @Ri       | Subtract indirect RAM from A with borrow | 1     | 2               |

| SUBB A, #data     | Subtract immediate from A with borrow    | 2     | 2               |

| INC A             | Increment A                              | 1     | 1               |

| INC Rn            | Increment register                       | 1     | 1               |

| INC direct        | Increment direct byte                    | 2     | 2               |

| INC @Ri           | Increment indirect RAM                   | 1     | 2               |

| DEC A             | Decrement A                              | 1     | 1               |

| DEC Rn            | Decrement register                       | 1     | 1               |

| DEC direct        | Decrement direct byte                    | 2     | 2               |

| DEC @Ri           | Decrement indirect RAM                   | 1     | 2               |

| INC DPTR          | Increment Data Pointer                   | 1     | 1               |

| MUL AB            | Multiply A and B                         | 1     | 4               |

| DIV AB            | Divide A by B                            | 1     | 8               |

| DA A              | Decimal adjust A                         | 1     | 1               |

|                   | Logical Operations                       |       |                 |

| ANL A, Rn         | AND Register to A                        | 1     | 1               |

| ANL A, direct     | AND direct byte to A                     | 2     | 2               |

| ANL A, @Ri        | AND indirect RAM to A                    | 1     | 2               |

| ANL A, #data      | AND immediate to A                       | 2     | 2               |

| ANL direct, A     | AND A to direct byte                     | 2     | 2               |

| ANL direct, #data | AND immediate to direct byte             | 3     | 3               |

| ORL A, Rn         | OR Register to A                         | 1     | 1               |

| ORL A, direct     | OR direct byte to A                      | 2     | 2               |

| ORL A, @Ri        | OR indirect RAM to A                     | 1     | 2               |

| ORL A, #data      | OR immediate to A                        | 2     | 2               |

| ORL direct, A     | OR A to direct byte                      | 2     | 2               |

| ORL direct, #data | OR immediate to direct byte              | 3     | 3               |

| XRL A, Rn         | Exclusive-OR Register to A               | 1     | 1               |

| XRL A, direct     | Exclusive-OR direct byte to A            | 2     | 2               |

| XRLA, @Ri         | Exclusive-OR indirect RAM to A           | 1     | 2               |

## Table 9.1. CIP-51 Instruction Set Summary

#### Notes on Registers, Operands and Addressing Modes:

**Rn** - Register R0–R7 of the currently selected register bank.

@Ri - Data RAM location addressed indirectly through R0 or R1.

**rel** - 8-bit, signed (two's complement) offset relative to the first byte of the following instruction. Used by SJMP and all conditional jumps.

**direct** - 8-bit internal data location's address. This could be a direct-access Data RAM location (0x00–0x7F) or an SFR (0x80–0xFF).

#data - 8-bit constant

#data16 - 16-bit constant

bit - Direct-accessed bit in Data RAM or SFR

**addr11** - 11-bit destination address used by ACALL and AJMP. The destination must be within the same 2 kB page of program memory as the first byte of the following instruction.

**addr16** - 16-bit destination address used by LCALL and LJMP. The destination may be anywhere within the 8 kB program memory space.

There is one unused opcode (0xA5) that performs the same function as NOP. All mnemonics copyrighted © Intel Corporation 1980.

### 9.2. Memory Organization

The memory organization of the CIP-51 System Controller is similar to that of a standard 8051. There are two separate memory spaces: program memory and data memory. Program and data memory share the same address space but are accessed via different instruction types. The CIP-51 memory organization is shown in Figure 9.2

| R/W      | R/W                                                                                                     | R/W                                                                                                                                                | R/W                              | R/W                                                                                                  | R/W           | R/W         | R             | Reset Value   |  |  |  |  |

|----------|---------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------|------------------------------------------------------------------------------------------------------|---------------|-------------|---------------|---------------|--|--|--|--|

| CY       | AC                                                                                                      | F0                                                                                                                                                 | RS1                              | RS0                                                                                                  | OV            | F1          | PARITY        | 00000000      |  |  |  |  |

| Bit7     | Bit6                                                                                                    | Bit5                                                                                                                                               | Bit4                             | Bit3                                                                                                 | Bit2          | Bit1        | Bit0          | SFR Address   |  |  |  |  |

|          |                                                                                                         |                                                                                                                                                    |                                  |                                                                                                      |               | (bit add    | dressable)    | 0xD0          |  |  |  |  |

| Bit7:    | CY: Carry                                                                                               | Flag.                                                                                                                                              |                                  |                                                                                                      |               |             |               |               |  |  |  |  |

|          |                                                                                                         |                                                                                                                                                    | he last arithmet                 |                                                                                                      |               |             |               | a borrow      |  |  |  |  |

|          |                                                                                                         |                                                                                                                                                    | ared to logic 0 l                | oy all other                                                                                         | arithmetic    | operations  | 3.            |               |  |  |  |  |

| Bit6:    | AC: Auxilia                                                                                             |                                                                                                                                                    |                                  |                                                                                                      |               |             |               |               |  |  |  |  |

|          |                                                                                                         |                                                                                                                                                    | ne last arithmeti                |                                                                                                      |               |             |               |               |  |  |  |  |

|          |                                                                                                         | raction) the                                                                                                                                       | e high order nib                 | ble. It is cle                                                                                       | eared to log  | ic 0 by all | other arithm  | ietic opera-  |  |  |  |  |

| D:46.    | tions.                                                                                                  | 'l.a. a. O                                                                                                                                         |                                  |                                                                                                      |               |             |               |               |  |  |  |  |

| Bit5:    | F0: User F                                                                                              | •                                                                                                                                                  | able several s                   | waaa flaa                                                                                            | fan           |             |               |               |  |  |  |  |

| Bits4–3: |                                                                                                         |                                                                                                                                                    | able, general pu<br>Bank Select. | irpose nag                                                                                           | for use und   | aer soltwa  | re control.   |               |  |  |  |  |

| DII54-3. |                                                                                                         | •                                                                                                                                                  | ich register ban                 | k is used d                                                                                          | uring rogic   | or accore   | 00            |               |  |  |  |  |

|          | THESE DIIS                                                                                              | Select WII                                                                                                                                         | ich register ban                 |                                                                                                      | uning regisi  | er access   | 65.           |               |  |  |  |  |

|          | RS1                                                                                                     | RS0                                                                                                                                                | Register Bank                    | Addr                                                                                                 | ess           |             |               |               |  |  |  |  |

|          | 0                                                                                                       | 0                                                                                                                                                  | 0                                | 0x00–                                                                                                | 0x07          |             |               |               |  |  |  |  |

|          | 0                                                                                                       | 1                                                                                                                                                  | 1                                | 0x08–                                                                                                | 0x0F          |             |               |               |  |  |  |  |

|          | 1                                                                                                       | 0                                                                                                                                                  | 2                                | 0x10–                                                                                                | 0x17          |             |               |               |  |  |  |  |

|          | 1                                                                                                       | 1                                                                                                                                                  | 3                                | 0x18–                                                                                                | 0x1F          |             |               |               |  |  |  |  |

| Bit2:    | OV: Overfl                                                                                              |                                                                                                                                                    |                                  |                                                                                                      |               |             |               |               |  |  |  |  |

| DILZ.    |                                                                                                         | •                                                                                                                                                  | der the followin                 | a circumet                                                                                           | ancos.        |             |               |               |  |  |  |  |

|          |                                                                                                         | <ul><li>This bit is set to 1 under the following circumstances:</li><li>An ADD, ADDC, or SUBB instruction causes a sign-change overflow.</li></ul> |                                  |                                                                                                      |               |             |               |               |  |  |  |  |

|          | • A MUL instruction results in an overflow (result is greater than 255).                                |                                                                                                                                                    |                                  |                                                                                                      |               |             |               |               |  |  |  |  |

|          |                                                                                                         | • A DIV instruction causes a divide-by-zero condition.                                                                                             |                                  |                                                                                                      |               |             |               |               |  |  |  |  |

|          | The OV bit is cleared to 0 by the ADD, ADDC, SUBB, MUL, and DIV instructions in all other               |                                                                                                                                                    |                                  |                                                                                                      |               |             |               |               |  |  |  |  |

|          | cases.                                                                                                  |                                                                                                                                                    | ,                                | , -,                                                                                                 | , -           | ,           |               |               |  |  |  |  |

| Bit1:    | F1: User F                                                                                              | lag 1.                                                                                                                                             |                                  |                                                                                                      |               |             |               |               |  |  |  |  |

| Ditt.    |                                                                                                         | 0                                                                                                                                                  | able, general pu                 | irpose flag                                                                                          | for use und   | der softwa  | re control.   |               |  |  |  |  |

| Ditt.    | This is a bit-addressable, general purpose flag for use under software control.<br>PARITY: Parity Flag. |                                                                                                                                                    |                                  |                                                                                                      |               |             |               |               |  |  |  |  |

|          | PARITY: F                                                                                               | arity Flag.                                                                                                                                        |                                  | This bit is set to logic 1 if the sum of the eight bits in the accumulator is odd and cleared if the |               |             |               |               |  |  |  |  |

|          |                                                                                                         | , ,                                                                                                                                                | 1 if the sum of t                | he eight bi                                                                                          | ts in the acc | cumulator   | is odd and cl | leared if the |  |  |  |  |

| Bit0:    |                                                                                                         | set to logic                                                                                                                                       | 1 if the sum of t                | he eight bi                                                                                          | ts in the acc | cumulator   | is odd and c  | leared if th  |  |  |  |  |

### SFR Definition 9.4. PSW: Program Status Word

#### 13.3.1. External Crystal Example

If a crystal or ceramic resonator is used as an external oscillator source for the MCU, the circuit should be configured as shown in Figure 13.1, Option 1. The External Oscillator Frequency Control value (XFCN) should be chosen from the Crystal column of the table in SFR Definition 13.4 (OSCXCN register). For example, an 11.0592 MHz crystal requires an XFCN setting of 111b and a 32.768 kHz Watch Crystal requires an XFCN setting of 001b. After an external 32.768 kHz oscillator is stabilized, the XFCN setting can be switched to 000 to save power. It is recommended to enable the missing clock detector before switching the system clock to any external oscillator source.

When the crystal oscillator is first enabled, the oscillator amplitude detection circuit requires a settling time to achieve proper bias. Introducing a delay of 1 ms between enabling the oscillator and checking the XTLVLD bit will prevent a premature switch to the external oscillator as the system clock. Switching to the external oscillator before the crystal oscillator has stabilized can result in unpredictable behavior. The recommended procedure is:

- Step 1. Force XTAL1 and XTAL2 to a low state. This involves enabling the Crossbar and writing '0' to port latches P0.2 and P0.3.

- Step 2. Configure XTAL1 and XTAL2 as analog inputs using register P0MDIN.

- Step 3. Enable the external oscillator.

- Step 4. Wait at least 1 ms.

- Step 5. Poll for XTLVLD => '1'.

- Step 6. Enable the Missing Clock Detector.

- Step 7. Switch the system clock to the external oscillator.

**Important Note on External Crystals:** Crystal oscillator circuits are quite sensitive to PCB layout. The crystal should be placed as close as possible to the XTAL pins on the device. The traces should be as short as possible and shielded with ground plane from any other traces which could introduce noise or interference.

Rev. 1.7

### 15.1. Supporting Documents

It is assumed the reader is familiar with or has access to the following supporting documents:

- 1. The I2C-Bus and How to Use It (including specifications), Philips Semiconductor.

- 2. The I2C-Bus Specification—Version 2.0, Philips Semiconductor.

- 3. System Management Bus Specification—Version 1.1, SBS Implementers Forum.

#### 15.2. SMBus Configuration

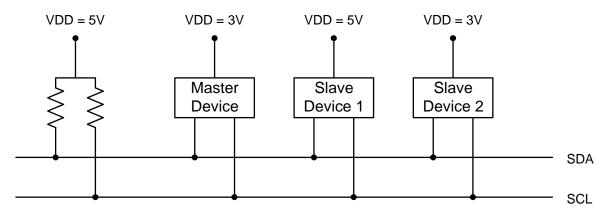

Figure 15.2 shows a typical SMBus configuration. The SMBus specification allows any recessive voltage between 3.0 V and 5.0 V; different devices on the bus may operate at different voltage levels. The bi-directional SCL (serial clock) and SDA (serial data) lines must be connected to a positive power supply voltage through a pullup resistor or similar circuit. Every device connected to the bus must have an open-drain or open-collector output for both the SCL and SDA lines, so that both are pulled high (recessive state) when the bus is free. The maximum number of devices on the bus is limited only by the requirement that the rise and fall times on the bus not exceed 300 ns and 1000 ns, respectively.

Figure 15.2. Typical SMBus Configuration

### 15.3. SMBus Operation

Two types of data transfers are possible: data transfers from a master transmitter to an addressed slave receiver (WRITE), and data transfers from an addressed slave transmitter to a master receiver (READ). The master device initiates both types of data transfers and provides the serial clock pulses on SCL. The SMBus interface may operate as a master or a slave, and multiple master devices on the same bus are supported. If two or more masters attempt to initiate a data transfer simultaneously, an arbitration scheme is employed with a single master always winning the arbitration. Note that it is not necessary to specify one device as the Master in a system; any device who transmits a START and a slave address becomes the master for the duration of that transfer.

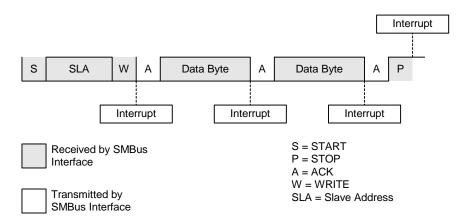

A typical SMBus transaction consists of a START condition followed by an address byte (Bits7–1: 7-bit slave address; Bit0: R/W direction bit), one or more bytes of data, and a STOP condition. Each byte that is received (by a master or slave) must be acknowledged (ACK) with a low SDA during a high SCL (see Figure 15.3). If the receiving device does not ACK, the transmitting device will read a NACK (not acknowledge), which is a high SDA during a high SCL.

| Bit     | Set by Hardware When:                                                                                                                                                                                                                                                                                   | Cleared by Hardware When:                                                                                                                      |

|---------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------|

| MASTER  | • A START is generated.                                                                                                                                                                                                                                                                                 | <ul><li>A STOP is generated.</li><li>Arbitration is lost.</li></ul>                                                                            |

| TXMODE  | <ul> <li>START is generated.</li> <li>SMB0DAT is written before the start of an SMBus frame.</li> </ul>                                                                                                                                                                                                 | <ul> <li>A START is detected.</li> <li>Arbitration is lost.</li> <li>SMB0DAT is not written before the<br/>start of an SMBus frame.</li> </ul> |

| STA     | <ul> <li>A START followed by an address byte is received.</li> </ul>                                                                                                                                                                                                                                    | <ul> <li>Must be cleared by software.</li> </ul>                                                                                               |

| STO     | <ul> <li>A STOP is detected while addressed as a slave.</li> <li>Arbitration is lost due to a detected STOP.</li> </ul>                                                                                                                                                                                 | <ul> <li>A pending STOP is generated.</li> </ul>                                                                                               |

| ACKRQ   | <ul> <li>A byte has been received and an ACK<br/>response value is needed.</li> </ul>                                                                                                                                                                                                                   | After each ACK cycle.                                                                                                                          |

| ARBLOST | <ul> <li>A repeated START is detected as a MASTER<br/>when STA is low (unwanted repeated START).</li> <li>SCL is sensed low while attempting to gener-<br/>ate a STOP or repeated START condition.</li> <li>SDA is sensed low while transmitting a '1'<br/>(excluding ACK bits).</li> </ul>             | • Each time SI is cleared.                                                                                                                     |

| ACK     | <ul> <li>The incoming ACK value is low<br/>(ACKNOWLEDGE).</li> </ul>                                                                                                                                                                                                                                    | <ul> <li>The incoming ACK value is high (NOT<br/>ACKNOWLEDGE).</li> </ul>                                                                      |

| SI      | <ul> <li>A START has been generated.</li> <li>Lost arbitration.</li> <li>A byte has been transmitted and an ACK/NACK received.</li> <li>A byte has been received.</li> <li>A START or repeated START followed by a slave address + R/W has been received.</li> <li>A STOP has been received.</li> </ul> | <ul> <li>Must be cleared by software.</li> </ul>                                                                                               |

## Table 15.3. Sources for Hardware Changes to SMB0CN

#### 15.5.3. Slave Receiver Mode

Serial data is received on SDA and the clock is received on SCL. When slave events are enabled (INH = 0), the interface enters Slave Receiver Mode when a START followed by a slave address and direction bit (WRITE in this case) is received. Upon entering Slave Receiver Mode, an interrupt is generated and the ACKRQ bit is set. Software responds to the received slave address with an ACK, or ignores the received slave address with a NACK. If the received slave address is ignored, slave interrupts will be inhibited until the next START is detected. If the received slave address is acknowledged, zero or more data bytes are received. Software must write the ACK bit after each received byte to ACK or NACK the received byte. The interface exits Slave Receiver Mode after receiving a STOP. Note that the interface will switch to Slave Transmitter Mode if SMB0DAT is written while an active Slave Receiver. Figure 15.7 shows a typical Slave Receiver sequence. Two received data bytes are shown, though any number of bytes may be received. Notice that the 'data byte transferred' interrupts occur **before** the ACK cycle in this mode.

Figure 15.7. Typical Slave Receiver Sequence

### Table 16.1. Timer Settings for Standard Baud Rates Using the Internal 24.5 MHz Oscillator

|                              | Frequency: 24.5 MHz          |                      |                                  |                       |                                                 |                  |                                  |  |  |

|------------------------------|------------------------------|----------------------|----------------------------------|-----------------------|-------------------------------------------------|------------------|----------------------------------|--|--|

|                              | Target<br>Baud Rate<br>(bps) | Baud Rate<br>% Error | Oscilla-<br>tor Divide<br>Factor | Timer Clock<br>Source | SCA1–SCA0<br>(pre-scale<br>select) <sup>1</sup> | T1M <sup>1</sup> | Timer 1<br>Reload<br>Value (hex) |  |  |

|                              | 230400                       | -0.32%               | 106                              | SYSCLK                | XX <sup>2</sup>                                 | 1                | 0xCB                             |  |  |

|                              | 115200                       | -0.32%               | 212                              | SYSCLK                | XX                                              | 1                | 0x96                             |  |  |

|                              | 57600                        | 0.15%                | 426                              | SYSCLK                | XX                                              | 1                | 0x2B                             |  |  |

| from<br>Jsc.                 | 28800                        | -0.32%               | 848                              | SYSCLK/4              | 01                                              | 0                | 0x96                             |  |  |

| SYSCLK fror<br>Internal Osc. | 14400                        | 0.15%                | 1704                             | SYSCLK/12             | 00                                              | 0                | 0xB9                             |  |  |

|                              | 9600                         | -0.32%               | 2544                             | SYSCLK/12             | 00                                              | 0                | 0x96                             |  |  |

|                              | 2400                         | -0.32%               | 10176                            | SYSCLK/48             | 10                                              | 0                | 0x96                             |  |  |

| Sy<br>Int                    | 1200                         | 0.15%                | 20448                            | SYSCLK/48             | 10                                              | 0                | 0x2B                             |  |  |

|                              | SCA1–SCA0 and                | d T1M bit definit    | tions can be fo                  | ound in Section 1     | 18 <b>.</b> 1.                                  |                  |                                  |  |  |

2. X = Don't care.

#### Table 16.2. Timer Settings for Standard Baud Rates Using an External 25.0 MHz Oscillator

|                              |                              |                      |                                  | quency: 25.0 N        | 10-                                             |                  |                                  |

|------------------------------|------------------------------|----------------------|----------------------------------|-----------------------|-------------------------------------------------|------------------|----------------------------------|

|                              | Target<br>Baud Rate<br>(bps) | Baud Rate<br>% Error | Oscilla-<br>tor Divide<br>Factor | Timer Clock<br>Source | SCA1–SCA0<br>(pre-scale<br>select) <sup>1</sup> | T1M <sup>1</sup> | Timer 1<br>Reload<br>Value (hex) |

|                              | 230400                       | -0.47%               | 108                              | SYSCLK                | ХХ <b>2</b>                                     | 1                | 0xCA                             |

|                              | 115200                       | 0.45%                | 218                              | SYSCLK                | XX                                              | 1                | 0x93                             |

|                              | 57600                        | -0.01%               | 434                              | SYSCLK                | XX                                              | 1                | 0x27                             |

| from<br>Osc.                 | 28800                        | 0.45%                | 872                              | SYSCLK/4              | 01                                              | 0                | 0x93                             |

| from<br>Osc.                 | 14400                        | -0.01%               | 1736                             | SYSCLK / 4            | 01                                              | 0                | 0x27                             |

| SYSCLK I<br>External C       | 9600                         | 0.15%                | 2608                             | EXTCLK / 8            | 11                                              | 0                | 0x5D                             |

| 'SC<br>tter                  | 2400                         | 0.45%                | 10464                            | SYSCLK / 48           | 10                                              | 0                | 0x93                             |

| уñ                           | 1200                         | -0.01%               | 20832                            | SYSCLK / 48           | 10                                              | 0                | 0x27                             |

| F                            | 57600                        | -0.47%               | 432                              | EXTCLK / 8            | 11                                              | 0                | 0xE5                             |

| SYSCLK from<br>Internal Osc. | 28800                        | -0.47%               | 864                              | EXTCLK / 8            | 11                                              | 0                | 0xCA                             |

|                              | 14400                        | 0.45%                | 1744                             | EXTCLK / 8            | 11                                              | 0                | 0x93                             |

|                              | 9600                         | 0.15%                | 2608                             | EXTCLK / 8            | 11                                              | 0                | 0x5D                             |

| Notes:                       |                              |                      |                                  |                       |                                                 |                  |                                  |

1. SCA1–SCA0 and T1M bit definitions can be found in **Section 18.1**.

2. X = Don't care.

| Table 16.5. Timer Settings for Standard Baud Rates Using an External 11.0592 MHz |

|----------------------------------------------------------------------------------|

| Oscillator                                                                       |

|                              | Frequency: 11.0592 MHz       |                      |                                  |                       |                                                 |                  |                                  |  |  |

|------------------------------|------------------------------|----------------------|----------------------------------|-----------------------|-------------------------------------------------|------------------|----------------------------------|--|--|

|                              | Target<br>Baud Rate<br>(bps) | Baud Rate<br>% Error | Oscilla-<br>tor Divide<br>Factor | Timer Clock<br>Source | SCA1–SCA0<br>(pre-scale<br>select) <sup>1</sup> | T1M <sup>1</sup> | Timer 1<br>Reload<br>Value (hex) |  |  |

|                              | 230400                       | 0.00%                | 48                               | SYSCLK                | XX <b>2</b>                                     | 1                | 0xE8                             |  |  |

|                              | 115200                       | 0.00%                | 96                               | SYSCLK                | XX                                              | 1                | 0xD0                             |  |  |

|                              | 57600                        | 0.00%                | 192                              | SYSCLK                | XX                                              | 1                | 0xA0                             |  |  |

| from<br>Osc.                 | 28800                        | 0.00%                | 384                              | SYSCLK                | XX                                              | 1                | 0x40                             |  |  |

| Ő                            | 14400                        | 0.00%                | 768                              | SYSCLK / 12           | 00                                              | 0                | 0xE0                             |  |  |

| SYSCLK<br>External (         | 9600                         | 0.00%                | 1152                             | SYSCLK / 12           | 00                                              | 0                | 0xD0                             |  |  |

| SC<br>ter                    | 2400                         | 0.00%                | 4608                             | SYSCLK / 12           | 00                                              | 0                | 0x40                             |  |  |

| ы<br>Х<br>Х                  | 1200                         | 0.00%                | 9216                             | SYSCLK / 48           | 10                                              | 0                | 0xA0                             |  |  |

|                              | 230400                       | 0.00%                | 48                               | EXTCLK / 8            | 11                                              | 0                | 0xFD                             |  |  |

| c. D                         | 115200                       | 0.00%                | 96                               | EXTCLK / 8            | 11                                              | 0                | 0xFA                             |  |  |

| < fre                        | 57600                        | 0.00%                | 192                              | EXTCLK / 8            | 11                                              | 0                | 0xF4                             |  |  |

| al                           | 28800                        | 0.00%                | 384                              | EXTCLK / 8            | 11                                              | 0                | 0xE8                             |  |  |

| SYSCLK from<br>Internal Osc. | 14400                        | 0.00%                | 768                              | EXTCLK / 8            | 11                                              | 0                | 0xD0                             |  |  |

| S∖<br>Int                    | 9600                         | 0.00%                | 1152                             | EXTCLK / 8            | 11                                              | 0                | 0xB8                             |  |  |

| Notes:<br>1. S               | SCA1-SCA0 and                | d T1M bit definit    | tions can be fo                  | ound in Section       | 18.1.                                           |                  |                                  |  |  |

**2.** X = Don't care.

#### Table 16.6. Timer Settings for Standard Baud Rates Using an External 3.6864 MHz Oscillator

|                              | Frequency: 3.6864 MHz        |                        |                                  |                       |                                                 |                  |                                 |  |  |

|------------------------------|------------------------------|------------------------|----------------------------------|-----------------------|-------------------------------------------------|------------------|---------------------------------|--|--|

|                              | Target<br>Baud Rate<br>(bps) | Baud<br>Rate%<br>Error | Oscilla-<br>tor Divide<br>Factor | Timer Clock<br>Source | SCA1–SCA0<br>(pre-scale<br>select) <sup>1</sup> | T1M <sup>1</sup> | Timer 1<br>Reload<br>Value (hex |  |  |

|                              | 230400                       | 0.00%                  | 16                               | SYSCLK                | XX <b>2</b>                                     | 1                | 0xF8                            |  |  |

|                              | 115200                       | 0.00%                  | 32                               | SYSCLK                | XX                                              | 1                | 0xF0                            |  |  |

|                              | 57600                        | 0.00%                  | 64                               | SYSCLK                | XX                                              | 1                | 0xE0                            |  |  |

| from<br>Osc.                 | 28800                        | 0.00%                  | 128                              | SYSCLK                | XX                                              | 1                | 0xC0                            |  |  |

|                              | 14400                        | 0.00%                  | 256                              | SYSCLK                | XX                                              | 1                | 0x80                            |  |  |

| SYSCLK<br>External (         | 9600                         | 0.00%                  | 384                              | SYSCLK                | XX                                              | 1                | 0x40                            |  |  |

| SC                           | 2400                         | 0.00%                  | 1536                             | SYSCLK / 12           | 00                                              | 0                | 0xC0                            |  |  |

| Ϋ́́                          | 1200                         | 0.00%                  | 3072                             | SYSCLK / 12           | 00                                              | 0                | 0x80                            |  |  |

|                              | 230400                       | 0.00%                  | 16                               | EXTCLK/8              | 11                                              | 0                | 0xFF                            |  |  |

| E .                          | 115200                       | 0.00%                  | 32                               | EXTCLK / 8            | 11                                              | 0                | 0xFE                            |  |  |

| < fror<br>Osc.               | 57600                        | 0.00%                  | 64                               | EXTCLK/8              | 11                                              | 0                | 0xFC                            |  |  |

| SYSCLK from<br>Internal Osc. | 28800                        | 0.00%                  | 128                              | EXTCLK/8              | 11                                              | 0                | 0xF8                            |  |  |

|                              | 14400                        | 0.00%                  | 256                              | EXTCLK/8              | 11                                              | 0                | 0xF0                            |  |  |

|                              | 9600                         | 0.00%                  | 384                              | EXTCLK / 8            | 11                                              | 0                | 0xE8                            |  |  |

1. SCA1–SCA0 and T1M bit definitions can be found in **Section 18.1**.

2. X = Don't care.

### 17.3. SPI0 Slave Mode Operation

When SPI0 is enabled and not configured as a master, it will operate as a SPI slave. As a slave, bytes are shifted in through the MOSI pin and out through the MISO pin by a master device controlling the SCK signal. A bit counter in the SPI0 logic counts SCK edges. When 8 bits have been shifted through the shift register, the SPIF flag is set to logic 1, and the byte is copied into the receive buffer. Data is read from the receive buffer by reading SPI0DAT. A slave device cannot initiate transfers. Data to be transferred to the master device is pre-loaded into the shift register by writing to SPI0DAT. Writes to SPI0DAT are double-buffered, and are placed in the transmit buffer first. If the shift register is empty, the contents of the transmit buffer will immediately be transferred into the shift register. When the shift register already contains data, the SPI will load the shift register with the transmit buffer's contents after the last SCK edge of the next (or current) SPI transfer.

When configured as a slave, SPI0 can be configured for 4-wire or 3-wire operation. The default, 4-wire slave mode, is active when NSSMD1 (SPI0CN.3) = 0 and NSSMD0 (SPI0CN.2) = 1. In 4-wire mode, the NSS signal is routed to a port pin and configured as a digital input. SPI0 is enabled when NSS is logic 0, and disabled when NSS is logic 1. The bit counter is reset on a falling edge of NSS. Note that the NSS signal must be driven low at least 2 system clocks before the first active edge of SCK for each byte transfer. Figure 17.4 shows a connection diagram between two slave devices in 4-wire slave mode and a master device.

3-wire slave mode is active when NSSMD1 (SPI0CN.3) = 0 and NSSMD0 (SPI0CN.2) = 0. NSS is not used in this mode, and is not mapped to an external port pin through the crossbar. Since there is no way of uniquely addressing the device in 3-wire slave mode, SPI0 must be the only slave device present on the bus. It is important to note that in 3-wire slave mode there is no external means of resetting the bit counter that determines when a full byte has been received. The bit counter can only be reset by disabling and re-enabling SPI0 with the SPIEN bit. Figure 17.3 shows a connection diagram between a slave device in 3-wire slave mode and a master device.

### 17.4. SPI0 Interrupt Sources

When SPI0 interrupts are enabled, the following four flags will generate an interrupt when they are set to logic 1:

All of the following bits must be cleared by software.

- 1. The SPI Interrupt Flag, SPIF (SPI0CN.7) is set to logic 1 at the end of each byte transfer. This flag can occur in all SPI0 modes.

- 2. The Write Collision Flag, WCOL (SPI0CN.6) is set to logic 1 if a write to SPI0DAT is attempted when the transmit buffer has not been emptied to the SPI shift register. When this occurs, the write to SPI0DAT will be ignored, and the transmit buffer will not be written. This flag can occur in all SPI0 modes.

- 3. The Mode Fault Flag MODF (SPI0CN.5) is set to logic 1 when SPI0 is configured as a master, and for multi-master mode and the NSS pin is pulled low. When a Mode Fault occurs, the MSTEN and SPIEN bits in SPI0CN are set to logic 0 to disable SPI0 and allow another master device to access the bus.

- 4. The Receive Overrun Flag RXOVRN (SPI0CN.4) is set to logic 1 when configured as a slave, and a transfer is completed and the receive buffer still holds an unread byte from a previous transfer. The new byte is not transferred to the receive buffer, allowing the previously received data byte to be read. The data byte which caused the overrun is lost.

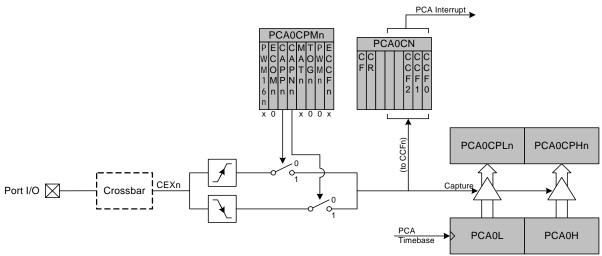

### 19.2.1. Edge-triggered Capture Mode

In this mode, a valid transition on the CEXn pin causes the PCA to capture the value of the PCA counter/timer and load it into the corresponding module's 16-bit capture/compare register (PCA0CPLn and PCA0CPHn). The CAPPn and CAPNn bits in the PCA0CPMn register are used to select the type of transition that triggers the capture: low-to-high transition (positive edge), high-to-low transition (negative edge), or either transition (positive or negative edge). When a capture occurs, the Capture/Compare Flag (CCFn) in PCA0CN is set to logic 1 and an interrupt request is generated if CCF interrupts are enabled. The CCFn bit is not automatically cleared by hardware when the CPU vectors to the interrupt service routine, and must be cleared by software. If both CAPPn and CAPNn bits are set to logic 1, then the state of the Port pin associated with CEXn can be read directly to determine whether a rising-edge or falling-edge caused the capture.

Figure 19.4. PCA Capture Mode Diagram

**Note:** The CEXn input signal must remain high or low for at least 2 system clock cycles to be recognized by the hardware.

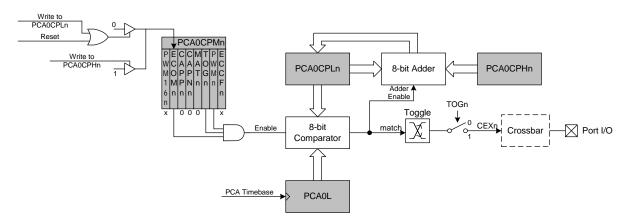

#### 19.2.4. Frequency Output Mode

Frequency Output Mode produces a programmable-frequency square wave on the module's associated CEXn pin. The capture/compare module high byte holds the number of PCA clocks to count before the output is toggled. The frequency of the square wave is then defined by Equation 19.3.

$$F_{CEXn} = \frac{F_{PCA}}{2 \times PCA0CPHn}$$

Note: A value of 0x00 in the PCA0CPHn register is equal to 256 for this equation.

### Equation 19.3. Square Wave Frequency Output